西安交大计算机组成_实验十cpu

- 格式:docx

- 大小:438.30 KB

- 文档页数:33

西安交通大学计算机组成原理实验报告姓名:***班级:物联网**学号:实验一存储器的访问与实现一、实验目的1、理解计算机主存储器的分类及作用;2、掌握ROM、RAM的读写方法。

二、实验原理存储器按存取方式分,可分为随机存储器和顺序存储器。

如果存储器中的任何存储单元的内容都可随机存取,称为随机存储器,计算机中的主存储器都是随机存储器。

如果存储器只能按某种顺序存取,则称为顺序存储器,磁带是顺序存储器,磁盘是半顺序存储器,它们的特点是存储容量大,存取速度慢,一般作为外部存储器使用。

如果按存储器的读写功能分,有些存储器的内容是固定不变的,即只能读出不能写入,这种存储器称为只读存储器(ROM);既能读出又能写入的存储器,称为随机读写存储器(RAM)。

实际上真正的ROM基本上不用了,用的是光可擦除可编程的ROM(EPROM)和电可擦除可编程的ROM(EEPROM)。

EEPROM用的越来越多,有取代EPROM之势,比如容量很大的闪存(FLASH)现在用的就很广泛,常说的U盘就是用FLASH做的。

按信息的可保存性分,存储器可分为非永久性记忆存储器和永久性记忆存储器。

ROM、EPROM、EEPROM都是永久记忆存储器,它们断电后存储内容可保存。

RAM则是非永久性记忆存储器,断电后存储器中存储的内容丢失。

随机读写存储器类型随机存储器按其元件的类型来分,有双极存储器和MOS存储器两类。

在存取速度和价格两方面,双极存储器比MOS存储器高,故双极存储器主要用于高速的小容量存储体系。

在MOS存储器中,根据存储信息机构的原理不同,又分为静态随机存储器(SRAM)和动态随机存储器(DRAM)。

静态随机存储器采用双稳态触发器来保存信息,只要不断电,信息就不会丢失;动态随机存储器利用记忆电容来保存信息,使用时只有不断地给电容充电才能使信息保持。

静态随机存储器的集成度较低,功耗也较大;动态随机存储器的集成度较高,功耗低。

现在计算机中,内存容量较大,常由动态随机存储器构成。

习题参考答案习题一1.第一代计算机的主要部件是由(电子管和继电器)构成的。

2.未来全新的计算机技术主要指(光子计算机),(生物计算机)和(量子计算机)。

3.按照Flynn分类法,计算机可以分为(单指令流单数据流),(单指令流多数据),(多指令流单数据流)和(多指令流多数据流)4种类型。

4.计算机系统主要由(硬件系统)和(软件系统)组成。

5.说明以下计算机中的部件是属于主机系统、软件系统、还是属于外部设备。

(1)CPU (主机系统)(2)内存条(主机系统)(3)网卡(主机系统)(4)键盘和鼠标(外设)(5)显示器(外设)(6)Windows操作系统(软件系统)6.控制芯片组是主板的的核心部件,它由(北桥芯片)部分和(南桥芯片)部分组成。

7.在计算机系统中设计Cache的主要目的是(提高存去速度)。

8.计算机各部件传输信息的公共通路称为总线,一次传输信息的位数称为总线的(宽度)。

9.PCIE属于(系统)总线标准,而SATA则属于(硬盘接口或外设)标准。

10.在微机输入输出控制系统中,若控制的外部设备是发光二极管,最好选用的输入输出方法是(程序控制)方式;若控制的对象是高速设备,则应选则(DMA)控制方式。

11.操作系统的基本功能包括(处理器管理或进程管理)、(文件管理)、(存储器管理)、(设备管理)和用户接口。

12.虚拟存储器由(主内存)和(磁盘)构成,由操作系统进行管理。

13.CPU从外部设备输入数据需要通过(输入接口),向外设输出数据则需要通过(输出接口)。

14.简述CPU从外部设备输入数据和向外设输出数据的过程。

请参见教材第18页关于输入输出过程的描述。

15.普适计算的主要特点是(是一种无处不在的计算模式)。

习题二1.在计算机内,一切信息的存取、传输和处理都是以(二进制码)形式进行的。

2.在微机中,信息的最小单位是(bit)。

3.在计算机中,1K字节表示的二进制位数是(1024×8bit)。

《计算机系统结构课内实验》实验报告第一次实验:记分牌算法和Tomasulo算法第二次实验:cache性能分析班级:物联网21姓名:李伟东学号:2120509011日期:2015.5.21第一次实验:记分牌算法和Tomasulo算法一、实验目的及要求1. 掌握DLXview模拟器的使用方法;2. 进一步理解指令动态调度的基本思想,了解指令动态调度的基本过程与方法;3. 理解记分牌算法和Tomasulo算法的基本思想,了解它们的基本结构、运行过程;4. 比较分析基本流水线与记分牌算法和Tomasulo算法的性能及优缺点。

二、实验环境DLXview模拟器三、实验内容1.用DLX汇编语言编写代码文件*.s(程序中应包括指令的数据相关、控制相关以及结构相关),以及相关的初始化寄存器文件*.i和数据文件*.d;2.观察程序中出现的数据相关、控制相关、结构相关,并指出三种相关的指令组合;四、实验步骤将自己编写的程序*.s、*.i、*.d装载到DLXview模拟器上,(1)分别用基本流水线、记分牌算法和Tomasulo算法模拟,针对每一种模拟做如下分析:①统计程序的执行周期数和流水线中的暂停时钟周期数;②改变功能部件数目重新模拟,观察并记录性能的改变;③改变功能部件延迟重新模拟,观察并记录性能的改变;论述功能部件数目、功能部件延迟对性能的影响。

(2)记录运行记分牌算法时的功能部件状态表和指令状态表;(3)记录运行Tomasulo算法时的指令状态表和保留站信息;五、实验结果1)基本流水线原始即加法延迟2,乘法延迟5,实验结果显示该段程序运行了11个时钟周期增加了一个除法器。

加法器延迟2,乘法器延迟5,除法器延迟19。

实验结果显示该段程序运行了11个时钟周期。

增加除法器对程序的执行无影响。

加法器延迟2,乘法器延迟6,无除法器。

实验结果显示该段程序运行了12个时钟周期乘法器的延迟对程序执行有有影响。

加法器延迟1,乘法器延迟5。

实验报告实验课程:电子系统设计与实践学生姓名:高君宇学号:2110505112专业班级:计算机15班2013年11月25日一、实验目的电子系统设计实验是计算机专业面向计算机综合应用设计的一个重要的实践环节。

主要以嵌入式单片机开发系统为主要实验平台,以此平台为基础,通过对单片机应用系统的开发设计训练,对外围接口电路的组成设计和应用编程技术训练,使学生能够掌握实现一个小型完整计算机应用系统从硬件电路设计到软件程序开发的设计过程,激发学生的创新兴趣,为以后的创新项目设计打好坚实基础。

本实验课程为独立开设的选修实验课程。

本实验课程的主要目的是让学生通过一个新型嵌入式单片机为核心的应用系统设计,掌握微型计算机硬件系统结构基本原理,软件开发编程方法,外围接口电路的组成和应用编程技术,以及电子系统设计的相关技术。

通过课程实践训练,能够让学生独立实现一个完整的计算机应用系统设计。

实验任务分为基本实验和综合应用设计实验两部分。

基本实验部分让学生学习单片机系统的基本硬件组成原理和软件程序设计方法;综合设计实验要求学生根据题目需求自行设计系统硬件组成电路,并设计实现完成相应功能的应用程序调试任务。

二、开发平台实验开发板采用技术性能优良的AVR ATmega128单片机作为核心器件,还特别设计了USB接口模块、Ethernet网络接口模块,还有MCU对外扩插槽,可为电路扩展模块提供必要的准备。

实验开发板可满足高端应用设计的要求,激发学生的创新兴趣,完成具体项目的开发设计。

学生还可以根据自己的兴趣设计制作新的目标模块实现对系统的进一步扩展。

三、实验内容(一)单片机实验系统开发环境学习1、实验目的:(1)、熟悉实验电路的结构原理、元器件名称、作用及相应的接口连接;(2)、学会使用C编译器编辑、编译、调试简单C源程序;(3)、学会使用AVR Studio集成开发软件下载调试并得到正确结果;(4)、熟悉蜂鸣器电路的编程原理。

2、实验电路原理图由图1.1所示的蜂鸣器电路可知,当BEEP引脚输出为低电平时,三极管导通,蜂鸣器鸣响;而当BEEP引脚输出为高电平时,三极管截止,蜂鸣器停止鸣响。

计算机控制专题实验一、实验目的掌握计算机控制系统各个环节的设计以与系统的组成。

通过实验使学生能够较熟练地设计计算机控制系统的各个环节和完整的系统,熟练掌握系统的调试和控制器参数的整定方法。

巩固和深化理论教学内容,培养学生的工程实践技能,综合运用所学专业知识解决实际问题的能力。

二、实验设备1.计算机一台2.数据采集卡PCI-9112卡一块,端子板LD-9188一块与电缆3.温度控制箱一套4.WindowsXP系统,Matlab软件,ADLINK软件包。

(Labview软件) 三、实验内容与要求1.了解温度控制系统的构成,熟悉各环节的工作原理。

掌握MatlabGUI 设计系统监控画面与编程方法。

2.熟练应用MatlabGUI设计系统监控画面,要求监控画面中有:1)控制系统名称“温度监控系统”与“设计人:×××”,2)显示实时温度控制曲线,横坐标为时间单位秒,纵坐标为温度,X围为0~100C°,加网格,3)数字显示实时温度,与控制输出,4)显示控制棒图,标记温度设定值,实时温度,控制输出,5)设定值温度与PID三个参数,并可以实时修改,6)可选的优化方法,7)有运行,停止,保存,结束等按钮功能。

3.设计编写采样、滤波、PID控制与优化算法等相关程序。

4.完成PID参数整定,调试出稳定的温度控制系统,观察并分析过程控制的PID整定规律。

保存最佳的整定参数与控制曲线图。

四、实验硬件与软件说明1.数字采集卡:数据采集卡PCI-9112插在主板上的PCI插槽中,包含数字信号与模拟信号两种。

模拟信号有两种模拟输入:16路单端模拟输入(A0~A15)和8路差分模拟输入(AL0~AL7/AH0~AH7),2路模拟量输出(AO1和AO2)。

引脚图见图1。

图1 16路单端模拟输入和8路差分模拟输入引脚图引脚说明:(模拟输入/输出与定时计数器)AI n—―Analog Input Channel n (single-ended)AIH n—―Analog High Input Channel n (differential)AIL n—―Analog Low Input Channel n (differential)ExtRef n—―External Reference Voltage for D/A CH nAO n—―Analog Output Channel nExtCLK—―External Clock InputExtTrig——External Trigger SignalCLK——Clock input for 8254GATE——Gate input for 8254COUT n——Signal output of Counter nV.ERF——Voltage ReferenceA.GND——Analog GroundGND——Ground实验中采用单端输入与输出,模数转换通道选用A/D的0号通道和数模转换通道选用D/A的0号通道。

Xi交通大学计算机网络原理实验报告。

计算机网络原理课计算机15名学生姓名高理科第211050512号提交日期:电子邮件实验-基于Boson Netsim软件的路由器配置实验首先,实验的目的(1)掌握路由器等设备的配置,掌握简单的组网技术。

(2)了解路由器、交换机等常见网络设备的配置方法;(3)掌握命令行模式下操作系统命令的使用;(4)掌握静态路由和动态路由的配置方法(RIP,OSPF)。

第二,实验内容本实验要求学生自己构建一个网络拓扑,需要三个以上的路由器连接两个以太网,每个以太网至少包括一个主机;完成路由器、主机等设备的配置;RIP或OSPF用于维护路由器的路由表。

3.实验步骤1:首先,连接拓扑图。

两台主机通过三台路由器相连。

步骤2:配置每台路由器的名称、端口IP地址、子网掩码、封装格式和时钟频率。

步骤3:配置每台主机的IP地址、子网掩码和路由器端口地址。

步骤4: RIP协议被配置为实现路由和IP数据包转发。

四、实验过程和结果Router1:路由器2:路由器3:PC1PC2结果:配置静态路由:R1:R2:R3:配置动态路由:r 13360 r 2: r 3:(1)命令配置终端:特权模式进入全局配置模式;主机名路由器:配置路由器名称命令;封装hdlc:封装帧(3种串行接口帧封装格式,HDLC是默认封装格式;时钟速率:设置时钟频率;无关机:要激活接口(在执行激活命令后,接口状态刚刚开始上升并再次变为下降)。

出现这种现象的原因是另一端的接口尚未配置,它仍处于非活动状态,无法从当前接口接收任何信息)Ping:互联网数据包检测器,用于测试网络连接数的程序。

(2)结果分析Ping命令将向目的地发送一条ICMP回应请求消息,并报告是否收到了所需的ICMP回应回复;通常,连续发送四个32字节的ICMP请求包,而在本实验中,发送了五个,接收了五个。

根据是否接收到回声响应和回声响应时间来判断网络的连通性。

时间:响应时间越短,TTL连接该地址的速度越快:生存期,路由跳数六、实验结果通过这次实验,我对路由器的配置过程有了更深的了解,也对网络连接的基本原理有了实际的体会,以前只在书本上看到局域网之间、广域网之间通过网桥、路由器等的连接。

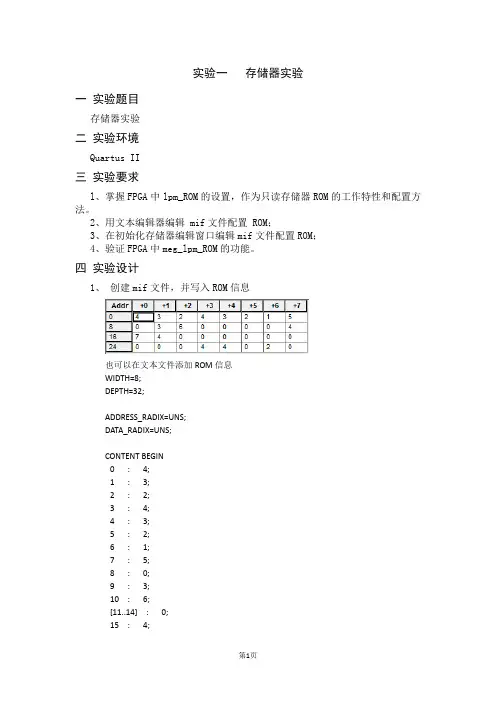

实验一存储器实验一实验题目存储器实验二实验环境Quartus II三实验要求l、掌握FPGA中lpm_ROM的设置,作为只读存储器ROM的工作特性和配置方法。

2、用文本编辑器编辑 mif文件配置 ROM;3、在初始化存储器编辑窗口编辑mif文件配置ROM;4、验证FPGA中meg_lpm_ROM的功能。

四实验设计1、创建mif文件,并写入ROM信息也可以在文本文件添加ROM信息WIDTH=8;DEPTH=32;ADDRESS_RADIX=UNS;DATA_RADIX=UNS;CONTENT BEGIN0 : 4;1 : 3;2 : 2;3 : 4;4 : 3;5 : 2;6 : 1;7 : 5;8 : 0;9 : 3;10 : 6;[11..14] : 0;15 : 4;16 : 7;17 : 4;[18..26] : 0;[27..28] : 4;29 : 0;30 : 2;31 : 0;END;2、连接电路图五实验仿真与测试六实验结果分析仿真结果从上图可以看出,电路输出了ROM中保存的数据。

七实验小结通过本次试验,我掌握了FPGA中lpm_ROM的设置,以及其作为只读存储器ROM的工作特性和配置方法。

学会了用quartus创建并设置mif文件的方法,以及用文本文档修改mif文件方法。

经过这次实验,我学会了quartus的基本使用方法,以及仿真方法。

实验二运算器组成实验一实验题目运算器组成实验二实验环境Quartus II三实验要求1.掌握简单运算器的数据传输通路。

2.验证运算功能发生器的组合功能。

3.掌握算术逻辑运算加、减、与的工作原理。

4.熟悉简单运算的数据传送通路。

5.验证实验台运算的8位加、减、与、直通功能。

6.按给定数据,完成几种指定的算术和逻辑运算。

四实验设计结合上图74181结构设计电路图如下仿真使用数据如下六实验结果分析符合74181的功能,测试通过七实验小结通过本次实验,我学习了加法器74181的使用方法,简单运算器的数据传输通路。

计算机组织与结构专题实验报告 ——实验设计总体实现学 院 电信学院指导老师 姜新宁 专业班级 计算机15 组员姓名 高君宇组员学号 2110505112邮 箱 309852008@目录一、实验目的 (3)二、实验要求 (3)三、实验原理 (3)3.1指令集: (3)3.2控制器的设计: (4)3.3通用寄存器组 (6)3.4存储器 (6)3.5总体数据通路设计: (6)四、设计思路与源代码 (7)4.1通用寄存器组regfile (9)4.2取指部分instru_fetch (9)4.3指令译码部分decoder_unit (10)4.4执行部分exe_unit (11)4.5存储器部分memory_unit (12)4.6程序包exp_cpu_components (12)4.7顶层设计实体exp_cpu (12)五、实验步骤 (13)六、实验现象 (13)七、实验心得 (16)八、程序源代码 (16)一、实验目的设计16位串行CPU,实现算术和逻辑运算指令、转移指令、访存指令、堆栈指令和控制指令。

二、实验要求根据系统的设计方案,直接利用硬件描述语言vhdl,编程完成,并调试、实现实验要完成的工作主要包括:指令系统的设计,FPGA-CPU的整体结构设计及其细化,逻辑设计的具体实现(VHDL语言程序的编写),软件模拟,以及硬件调试。

三、实验原理3.1指令集:图1-一个指令的执行流程图指令系统在整个计算机系统结构设计中处于核心的地位。

指令系统设计不仅直接关系到计算机系统硬件的设计,而且必然影响后期系统软件的设计。

1)指令类型:算数类:ADD SUB 逻辑类:AND OR寄存器访问类:SET MOV 存储器访问类:LOAD STORE条件转移类:BEQ 无条件转移类:JMP2)指令格式:字长:使用固定长度16位操作码:为方便使用及操作,规定为4位操作数:为使用多个操作数,每个操作数规定为1至3位3)指令系统依据MIPS指令集设计,指令字长为16位,整个指令系统包括了运算指令、转移指令和存储指令等三类。

西安交通大学组成专题实验报告计算机组织与结构专题实验报告 MIPS单周期处理器的设计学生姓名赵荣建专业班级计算机45班学号2140505119 指导教师姜欣宁完成日期 2021-05-09一.实验目的根据所学的CPU组成原理,自主设计一个MIPS32位的单周期处理器。

二.设计方案参照计算机组成原理教材上的MIPS32位处理器的工作原理。

1.构建数据通路取指令指令译码指令执行存储器访问结果写回取指周期:a.从指令寄存器PC输出端得到地址b.送地址到指令存储器IM地址端Ac.从指令存储器IM的数据端RD得到指令d.计算下地址:通过运算器,PC+4形成下地址,送回到PC。

2. .MIPS 寄存器集:定义了32个32位的寄存器3.MIPS三种指令格式:R-类型、I-类型和J-类型R-类型格式:* 所有指令操作吗OP都是0;特定操作由funct决定。

* 机器语言指令中,字段分配格式如上图;前两个寄存器rs、 rt是源寄存器,rd是目的寄存器。

而在汇编语言格式中,第一个寄存器是目的寄存器。

如:add $t0,$s4,$s5 #[rd]=[rs]+[rt],[t0]=[s4]+[s5]; I-类型格式:* 指令含4个字段;op, rs, rt 和 imm* 有两个寄存器操作数和一个16位立即数操作数,一些指令中,rt也可作为源寄存器。

J-类型格式:* 有一个26位立即数操作数,扩展后形成目的地址。

4.算逻单元ALU的设计<<210Add<<2JumpMemToReg4Add01ControlMemReadMemWriteBranchALUopALUsrcRegWriteIn structionMemoryPC0R1Rdata132R21RegisterFileW1WdataALU32zeroResult32AddrRdata20212DataData0321Memory3Wdata{15~0}sign32 extend2ALUcontrol6{5~0}ALU工作原理图BA321zeroALU3232Result* 两级控制:通过系统控制器(Control)3ALUoperFunc6ALUcontrol2ALUop 和运算器控制器(ALU Control)产生 ALU的控制信号:ALUoper* ALU控制信号对照表:ALUop Func(来自R型指令的func字段)操作 ALUop1 ALUop2 F5 0 0 1 1 1 1 1 0 1 × × × × × × × × × × × × F4 × × × × × × × F3 × × 0 0 0 0 1 F2 × × 0 0 1 1 0 F1 × × 0 1 0 0 1 F0 × × 0 0 0 1 0 010:ADD 110:SUB 010:ADD 110:SUB 000:AND 001: OR 111:SLT 5.单周期数据通路的构建1)构件:PC、指令存储器、寄存器文件RF和数据存储器; 2)取指令的过程:PC→IM: A/RD3)取源操作数的过程:IM:RD→RF:A1/RD1。

西安交通大学操作系统专题实验报告班级:学号:姓名:2022年4月25日目录1内核编译与系统调用 (1)1.1实验目的 (1)1.2实验内容 (1)1.3实验思想(或流程图) (1)1.4实验步骤 (1)1.5测试数据设计 (3)1.6程序运行初值及运行结果分析 (3)1.7实验总结 (4)1.7.1实验中的问题与解决过程 (4)1.7.2实验收获 (5)1.7.3意见与建议 (5)1.8附件 (5)1.8.1附件1 程序 (5)1.8.2附件2 MakeFile (8)1.8.3附件3 Readme (8)2 进程软中断与管道通信 (13)2.1实验目的 (13)2.2实验内容 (13)2.3实验思想(或流程图) (13)2.4结果分析 (15)2.5实验总结 (16)2.6源代码 (17)3 模块编程与字符设备驱动 (20)3.1实验目的 (20)3.2实验内容 (20)3.3实验总结 (21)3.4附件 (22)1内核编译与系统调用1.1实验目的掌握系统调用的设计过程,为以后设计更复杂系统奠定基础。

1.2实验内容安装Linux,熟悉Linux的操作,并编译内核,构建、使用自己的Linux内核设计系统调用:设计、添加自己的系统调用,并重新编译内核予以验证为Linux内核设计添加一个系统调用,将系统的相关信息(CPU型号、操作系统的版本号、系统中的进程等,类似于Windows的任务管理器)以文字形式列表显示于屏幕,并编写用户程序予以验证。

请参阅proc文件系统的相关说明,读取proc文件系统的相关信息,可参考实验指导书的proc编程实验1.3实验思想(或流程图)系统调用是应用程序和操作系统内核之间的功能接口,其主要目的使用户可以使用操作系统提供的有关设备管理、输入/ 输出系统、文件系统和进程控制、通信以及存储管理等方面的功能 ,而不必了解系统程序的内部结构和有关硬件细节,从而起到减轻用户负担和保护系统以及提高资源利用率的作用。

《计算机组成实验 C》课程设计适用专业:电子信息类专业专业:软件工程班级:软件一班学号:姓名:某某某指导教师:陈红梅实验学期:2014-2015 第 1 学期西南交通大学信息科学与技术学院目录简化计算机系统的设计 (2)一、实验目的 (2)二.、实验内容 (2)三.、预习要求 (2)四、实验报告 (2)1. BLOCK图 (3)2. 程序设计(纸质的版本我用手抄) (4)3. 仿真波形图 (11)4、仿真中遇到的问题: (14)五、实验感想 (15)简化计算机系统的设计一、实验目的通过学习简单的指令系统及其各指令的操作流程,用VHDL 语言实现简单的处理器模块,并通过调用存储器模块,将处理器模块和存储器模块连接形成简化的计算机系统。

二.、实验内容1. 用VHDL语言实现简单的处理器模块。

2. 调用存储器模块设计64×8的存储器模块。

3. 将简单的处理器模块和存储器模块连接形成简单的计算机系统。

4. 将指令序列存入存储器,然后分析指令执行流程。

三.、预习要求1、学习简单指令集。

2、学习各指令的操作流程。

四、实验报告1. BLOCK图2. 程序设计(纸质的版本我用手抄)CPU的设计:LIBRARY ieee;USE ieee.std_logic_1164.ALL;PACKAGE mypack ISCONSTANT idle : std_logic_vector(3 DOWNTO 0) :="0000";CONSTANT load : std_logic_vector(3 DOWNTO 0) :="0001";CONSTANT move : std_logic_vector(3 DOWNTO 0) :="0010";CONSTANT addx : std_logic_vector(3 DOWNTO 0) :="0011";CONSTANT subp : std_logic_vector(3 DOWNTO 0) :="0100";CONSTANT andp : std_logic_vector(3 DOWNTO 0) :="0101";CONSTANT orp : std_logic_vector(3 DOWNTO 0) :="0110";CONSTANT xorp : std_logic_vector(3 DOWNTO 0) :="0111";CONSTANT shrp : std_logic_vector(3 DOWNTO 0) :="1000";CONSTANT shlp : std_logic_vector(3 DOWNTO 0) :="1001";CONSTANT swap : std_logic_vector(3 DOWNTO 0) :="1010";CONSTANT jmp : std_logic_vector(3 DOWNTO 0) :="1011";CONSTANT jz : std_logic_vector(3 DOWNTO 0) :="1100";CONSTANT read : std_logic_vector(3 DOWNTO 0) :="1101";CONSTANT write : std_logic_vector(3 DOWNTO 0) :="1110";CONSTANT stop : std_logic_vector(3 DOWNTO 0) :="1111";END mypack;LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.ALL;USE WORK.mypack.ALL;------------------------cpu实体声明--------------------------------- ENTITY cpu ISPORT(reset : IN std_logic; --清零信号低有效clock : IN std_logic; --时钟信号Write_Read: OUT std_logic; --读写信号,'1'为写 M_address: OUT std_logic_vector(11 DOWNTO 0); --地址线M_data_in: IN std_logic_vector(7 DOWNTO 0); --数据输入线M_data_out: OUT std_logic_vector(7 DOWNTO 0); --数据输出线 overflow: OUT std_logic); --溢出标志END cpu;------------------------cpuRTL级行为描述-------------------------------- ARCHITECTURE RTL of cpu ISSIGNAL IR: std_logic_vector(15 DOWNTO 0); --指令寄存器 SIGNAL MDR: std_logic_vector(7 DOWNTO 0); --数据寄存器 SIGNAL MAR: std_logic_vector(11 DOWNTO 0); --地址寄存器 SIGNAL status: integer RANGE 0 TO 6; --状态寄存器BEGINstatus_change: PROCESS(reset, clock, status )BEGINIF reset = '0' THEN status <= 0 ;ELSIF clock'EVENT AND clock = '0' THENCASE status ISWHEN 0 =>status <= 1;WHEN 1 =>IF IR(15 DOWNTO 12) = Stop THENstatus <= 1;ELSEstatus <= 2;END IF;WHEN 2 =>CASE IR(15 DOWNTO 12) ISWHEN Read|Write|Jmp|Jz|Swap =>status <= 3;WHEN OTHERS =>status <= 0;END CASE;WHEN 3 =>IF IR(15 DOWNTO 12)= Swap THENstatus <= 0;ELSEstatus <= 4;END IF;WHEN 4 =>status <= 5;WHEN 5 =>CASE IR(15 DOWNTO 12) ISWHEN Read|Write =>status <= 6;WHEN OTHERS =>status <= 0;END CASE;WHEN OTHERS =>status <= 0;END CASE;ELSENULL;END IF;END PROCESS status_change;seq: PROCESS(reset,clock)VARIABLE PC:std_logic_vector(11 DOWNTO 0); --程序计数器 VARIABLE R0,R1,R2,R3: std_logic_vector(7 DOWNTO 0); --通用寄存器VARIABLE A: std_logic_vector(7 DOWNTO 0); --临时寄存器VARIABLE temp: std_logic_vector(8 DOWNTO 0); --临时变量BEGINIF(reset='0') THEN -- 清零IR <= (OTHERS=>'0');PC := (OTHERS=>'0');R0 := (OTHERS=>'0');R1 := (OTHERS=>'0');R2 := (OTHERS=>'0');R3 := (OTHERS=>'0');A := (OTHERS=>'0');MAR <= (OTHERS=>'0');MDR <= (OTHERS=>'0');ELSIF(clock'event AND clock='1') THENoverflow <= '0';CASE status ISWHEN 0=> --状态0IR <= M_data_in & "00000000"; --取指令PC := PC+1; --程序计数器加1WHEN 1=> --状态1IF (IR(15 DOWNTO 12) /= stop) THENMAR <= PC;END IF;CASE IR(15 DOWNTO 12) ISWHEN load =>R0:= "0000" & IR(11 DOWNTO 8);WHEN shlp|shrp =>CASE IR(11 DOWNTO 10) IS -- Rx to AWHEN "00"=> A:= R0;WHEN "01"=> A:= R1;WHEN "10"=> A:= R2;WHEN OTHERS => A:= R3;END CASE;WHEN Move|addx|subp|andp|orp|xorp|Swap=> CASE IR(9 DOWNTO 8) IS -- Ry to AWHEN "00"=> A:=R0;WHEN "01"=> A:=R1;WHEN "10"=> A:=R2;WHEN OTHERS=> A:=R3;END CASE;WHEN OTHERS => NULL;END CASE;WHEN 2=> --状态2CASE IR(15 DOWNTO 12) ISWHEN addx => -- Rx:= Rx + A;CASE IR(11 DOWNTO 10) ISWHEN "00"=>temp := (R0(7) & R0(7 DOWNTO 0)) + (A(7) & A(7 DOWNTO 0));R0:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);WHEN "01"=>temp :=(R1(7) & R1(7 DOWNTO 0)) + (A(7) & A(7 DOWNTO 0));R1:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);WHEN "10"=>temp :=(R2(7) & R2(7 DOWNTO 0)) + (A(7) & A(7 DOWNTO 0));R2:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);WHEN OTHERS=>temp :=(R3(7) & R3(7 DOWNTO 0)) + (A(7) & A(7 DOWNTO 0));R3:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);END CASE;WHEN subp => -- Rx:= Rx - A;CASE IR(11 DOWNTO 10) ISWHEN "00"=>temp :=(R0(7) & R0(7 DOWNTO 0)) + NOT(A(7) & A(7 DOWNTO 0)) + 1;R0:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);WHEN "01"=>temp :=(R1(7) & R1(7 DOWNTO 0)) + NOT(A(7) & A(7 DOWNTO 0)) + 1;R1:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);WHEN "10"=>temp :=(R2(7) & R2(7 DOWNTO 0)) + NOT(A(7) & A(7 DOWNTO 0)) + 1;R2:=temp(7 DOWNTO 0);overflow <= temp(8) xor temp(7);WHEN OTHERS=>temp :=(R3(7) & R3(7 DOWNTO 0)) + NOT(A(7) & A(7 DOWNTO 0)) + 1;R3:=temp(7 DOWNTO 0);overflow <= temp(8) XOR temp(7);END CASE;WHEN move =>CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:= A;WHEN "01"=> R1:= A;WHEN "10"=> R2:= A;WHEN OTHERS=> R3:= A;END CASE;WHEN shrp =>CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:= '0' & A( 7 DOWNTO 1 );WHEN "01"=> R1:= '0' & A( 7 DOWNTO 1 );WHEN "10"=> R2:= '0' & A( 7 DOWNTO 1 );WHEN OTHERS=> R3:= '0' & A( 7 DOWNTO 1 );END CASE;WHEN shlp =>CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:= A( 6 DOWNTO 0 ) & '0';WHEN "01"=> R1:= A( 6 DOWNTO 0 ) & '0';WHEN "10"=> R2:= A( 6 DOWNTO 0 ) & '0';WHEN OTHERS=> R3:= A( 6 DOWNTO 0 ) & '0';END CASE;WHEN andp => --Rx:= Rx AND A; CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:=R0 AND A;WHEN "01"=> R1:=R1 AND A;WHEN "10"=> R2:=R2 AND A;WHEN OTHERS=> R3:=R3 AND A;END CASE;WHEN orp => --Rx:= Rx OR A;CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:=R0 OR A;WHEN "01"=> R1:=R1 OR A;WHEN "10"=> R2:=R2 OR A;WHEN OTHERS=> R3:=R3 OR A;END CASE;WHEN xorp => --Rx:= Rx XOR A; CASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:=R0 XOR A;WHEN "01"=> R1:=R1 XOR A;WHEN "10"=> R2:=R2 XOR A;WHEN OTHERS=> R3:=R3 XOR A;END CASE;WHEN Swap => --Swap: Rx to Ry; CASE IR(11 DOWNTO 8) ISWHEN "0100"=> R0:=R1;WHEN "1000"=> R0:=R2;WHEN "1100"=> R0:=R3;WHEN "0001"=> R1:=R0;WHEN "1001"=> R1:=R2;WHEN "1101"=> R1:=R3;WHEN "0010"=> R2:=R0;WHEN "0110"=> R2:=R1;WHEN "1110"=> R2:=R3;WHEN "0111"=> R3:=R1;WHEN "1011"=> R3:=R2;WHEN "0011"=> R3:=R0;WHEN OTHERS=> NULL;END CASE;WHEN OTHERS => NULL;END CASE;WHEN 3=> --状态3CASE IR(15 DOWNTO 12) ISWHEN Swap=> -- Swap: A to RxCASE IR(11 DOWNTO 10) ISWHEN "00"=> R0:=A;WHEN "01"=> R1:=A;WHEN "10"=> R2:=A;WHEN OTHERS=> R3:=A;END CASE;WHEN jmp|Jz|Read|Write =>IR(7 DOWNTO 0)<= M_data_in; -- 取双字节指令的后半部分 PC := PC+1;WHEN OTHERS => NULL;END CASE;WHEN 4=> --状态4CASE IR(15 DOWNTO 12) ISWHEN jmp => -- 无条件转移指令PC := IR(11 DOWNTO 0);MAR <= IR(11 DOWNTO 0);WHEN Jz => -- 条件转移指令IF(R0="00000000") thenPC := IR(11 DOWNTO 0);MAR <= IR(11 DOWNTO 0);elseMAR <= PC;END IF;WHEN Read =>MAR <= IR(11 DOWNTO 0);WHEN Write =>MAR <= IR(11 DOWNTO 0);MDR <= R0;WHEN OTHERS => NULL;END CASE;WHEN 5 => --状态5MAR <= PC;WHEN 6 => --状态6CASE IR(15 DOWNTO 12) ISWHEN Read => R0 := M_data_in;WHEN OTHERS=> NULL;END CASE;END CASE;END IF;END process seq;comb: PROCESS (reset, status)BEGINIF (reset = '1' AND status = 5 AND IR(15 DOWNTO 12)= Write ) THEN Write_Read <= '1';ELSEWrite_Read <= '0';END IF;END PROCESS comb;M_address <= MAR;M_data_out <= MDR;END RTL;3. 仿真波形图3.1总体的仿真波形图1、我们可以看到CPU有6种工作模式,并且在不同的工作模式下实现了不同的功能。

计算机组成实验报告计算机66熊鹏飞2160500151实验十基于MIPS指令集的CPU设计一、实验目的1.综合运用Verilog进行复杂系统设计。

2.深刻理解计算机系统硬件原理。

二、实验内容1.设计一个基于MIPS指令集的CPU。

2.CPU需要包含寄存器组、RAM模块、ALU模块、指令译码模块。

3.该CPU能运行基本的汇编指令。

4.实现cache,流水线或其他现代CPU的高级功能(加分项)三、实验要求1.分析各模块的的程序结构,画出其流程图。

单周期CPU指的是一条指令的执行在一个时钟周期内完成,然后开始下一条指令的执行,即一条指令用一个时钟周期完成。

电平从低到高变化的瞬间称为时钟上升沿,两个相邻时钟上升沿之间的时间间隔称为一个时钟周期。

CPU在处理指令时,一般需要经过以下几个步骤:(1) 取指令(IF):根据程序计数器PC中的指令地址,从存储器中取出一条指令,同时,PC 根据指令字长度自动递增产生下一条指令所需要的指令地址,但遇到“地址转移”指令时,则控制器把“转移地址”送入PC,当然得到的“地址”需要做些变换才送入PC。

(2) 指令译码(ID):对取指令操作中得到的指令进行分析并译码,确定这条指令需要完成的操作,从而产生相应的操作控制信号,用于驱动执行状态中的各种操作。

(3) 指令执行(EXE):根据指令译码得到的操作控制信号,具体地执行指令动作,然后转移到结果写回状态。

(4) 存储器访问(MEM):所有需要访问存储器的操作都将在这个步骤中执行,该步骤给出存储器的数据地址,把数据写入到存储器中数据地址所指定的存储单元或者从存储器中得到数据地址单元中的数据。

(5) 结果写回(WB):指令执行的结果或者访问存储器中得到的数据写回相应的目的寄存器中。

单周期CPU,是在一个时钟周期内完成这五个阶段的处理。

2.画出模块的电路图。

3.分析电路的仿真波形,标出关键的数值。

4.记录设计和调试过程。

1.wire和reg是什么意思?——在verilog里面,变量有wire和reg两种类型,wire类型意为线,它不可储存中间结果,通过输入得出输出,类似纯函数,只要输入变化,输出立即变化,如果没有输入,自然就没有输出。

reg类型意为寄存器,它可以赋初值,可以储存中间结果,只有当满足某种条件时(比如时钟上升沿),它才会变化,其他时间会一直保持最后一次变化的值。

2.指令怎么来?——在IM组件和RW组件分别开两个寄存器数组,用来模拟指令内存和数据内存,通过文件读取,从test.txt(test文件夹中)读指令到IM的指令内存(从0开始),IM组件通过输入的IAddr(数组地址下标),得到相应的指令。

3.指令怎么变化?——在PC端,有两个外部输入:CLK和Reset。

其中PC内部有指令寄存器,每次CLK上升沿触发后,会改成新的指令,同时,当Reset=1时,指令寄存器也会置0。

4.模块和模块间怎么连接?——此时,需要一个顶层模块,相当于main函数,它会根据数据通路图,将一些下层模块的输出,连接到另一些下层模块的输入中。

5.写好的cpu怎么运行?——需要在顶层模块再添加一个测试文件,测试文件提供外部输入(CLK和Reset),然后模块就会自动运行得到相应的仿真结果。

四、实验代码及结果1. PC:CLK上升沿触发,更改指令地址`timescale 1ns /1ps//////////////////////////////////////////////////////////////////////////////////// Company: // Engineer: // // Create Date: 23:43:40 05/02/2017 // Design Name: // Module Name: PC // Project Name: // Target Devices: // Tool versions: // Description: //// Dependencies: //// Revision: // Revision 0.01 - File Created// Additional Comments:////////////////////////////////////////////////////////////////////////////////////module PC(input CLK, // 时钟input Reset, // 重置信号input PCWre, // PC是否更改,如果为0,PC不更改input [31:0] newAddress, // 新指令output reg[31:0] currentAddress // 当前指令);initial begincurrentAddress <= 0; // 非阻塞赋值endalways@(posedge CLK or posedge Reset)beginif (Reset == 1) currentAddress <= 0; // 如果重置,赋值为0elsebeginif (PCWre) currentAddress <= newAddress;else currentAddress <= currentAddress;endendendmodule输入:CLK,Reset,PCWre,newAddress输出:currentAddress解释:由于指令地址存储在寄存器里,一开始需要赋currentAddress为0。

Reset是重置信号,当为1时,指令寄存器地址重置。

PCWre的作用为保留现场,如果PCWre为0,指令地址不变。

2. InstructionMemory:储存指令,分割指令`timescale 1ns /1ps//////////////////////////////////////////////////////////////////////////////////// Company: // Engineer: // // Create Date: 00:10:27 05/03/2017 // Design Name: // Module Name: IM // Project Name: // Target Devices: // Tool versions: // Description: //// Dependencies: //// Revision: // Revision 0.01 - File Created// Additional Comments:////////////////////////////////////////////////////////////////////////////////////module InstructionMemory(input InsMemRW, // 读写控制信号,1为写,0位读input [31:0] IAddr, // 指令地址输入入口//input IDataIn, // 没用到output [5:0] op,output [4:0] rs,output [4:0] rt,output [4:0] rd,output [15:0] immediate // 指令代码分时段输出);reg[7:0] mem[0:63]; // 新建一个32位的数组用于储存指令initialbegin$readmemb("test/test.txt", mem); //读取测试文档中的指令 end// 从地址取值,然后输出assign op = mem[IAddr][7:2];assign rs[4:3] = mem[IAddr][1:0];assign rs[2:0] = mem[IAddr + 1][7:5];assign rt = mem[IAddr + 1][4:0];assign rd = mem[IAddr + 2][7:3];assign immediate[15:8] = mem[IAddr + 2];assign immediate[7:0] = mem[IAddr + 3];endmodule输入:InsMenRW,IAddr输出:op,rs,rt,rd,immediate解释:该部分为指令寄存器,通过一个64大小的8位寄存器数组来保存从文件输入的全部指令。

然后通过输入的地址,找到相应的指令,并分割成op,rs,rt,rd,immediate输出。

(由于寄存器地址+4,所以不用右移变换成真正的地址)3.RegisterFile:储存寄存器组,并根据地址对寄存器组进行读写`timescale 1ns /1ps//////////////////////////////////////////////////////////////////////////////////// Company: // Engineer: // // Create Date: 01:07:13 05/03/2017 // Design Name: // Module Name: RF // Project Name: // Target Devices: // Tool versions: // Description: //// Dependencies: //// Revision: // Revision 0.01 - File Created// Additional Comments:////////////////////////////////////////////////////////////////////////////////////module RegisterFile(input CLK, // 时钟input RegWre, // 写使能信号,为1时,在时钟上升沿写入input [4:0] rs, // rs寄存器地址输入端口input [4:0] rt, // rt寄存器地址输入端口input [4:0] WriteReg, // 将数据写入的寄存器端口,其地址来源rt或rd字段input [31:0] WriteData, // 写入寄存器的数据输入端口output [31:0] ReadData1, // rs寄存器数据输出端口output [31:0] ReadData2 // rt寄存器数据输出端口);reg [31:0] register[0:15]; // 新建16个寄存器,用于操作// 初始时,将32个寄存器全部赋值为0integer i;initialbeginfor(i = 0; i < 16; i = i + 1) register[i] <= 0;end// 读寄存器assign ReadData1 = register[rs];assign ReadData2 = register[rt];// 写寄存器always@(negedge CLK)begin// 如果寄存器不为0,并且RegWre为真,写入数据if (RegWre && WriteReg != 0) register[WriteReg] = WriteData; endendmodule输入:CLK,RegWre,rs,rt,WriteReg,WriteData输出:ReadData1,ReadData2解释:该部分为寄存器读写单元,RegWre的作用是控制寄存器是否写入。