DSPC2000汇编指令

- 格式:pdf

- 大小:692.44 KB

- 文档页数:26

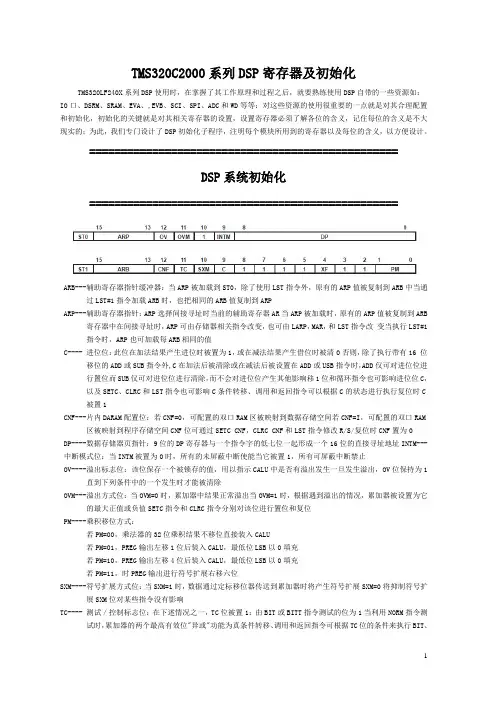

TMS320C2000系列DSP寄存器及初始化TMS320LF240X系列DSP使用时,在掌握了其工作原理和过程之后,就要熟练使用DSP自带的一些资源如:IO口、DSRM、SRAM、EVA、,EVB、SCI、SPI、ADC和WD等等;对这些资源的使用很重要的一点就是对其合理配置和初始化,初始化的关键就是对其相关寄存器的设置,设置寄存器必须了解各位的含义,记住每位的含义是不大现实的;为此,我们专门设计了DSP初始化子程序,注明每个模块所用到的寄存器以及每位的含义,以方便设计。

=================================================DSP系统初始化=================================================ARB---辅助寄存器指针缓冲器:当ARP被加载到ST0,除了使用LST指令外,原有的ARP值被复制到ARB中当通过LST#1指令加载ARB时,也把相同的ARB值复制到ARPARP---辅助寄存器指针:ARP选择间接寻址时当前的辅助寄存器AR当ARP被加载时,原有的ARP值被复制到ARB 寄存器中在间接寻址时,ARP可由存储器相关指令改变,也可由LARP,MAR,和LST指令改变当执行LST#1指令时,ARP也可加载每ARB相同的值C---- 进位位:此位在加法结果产生进位时被置为1,或在减法结果产生借位时被清0否则,除了执行带有16 位移位的ADD或SUB指令外,C在加法后被清除或在减法后被设置在ADD或USB指令时,ADD仅可对进位位进行置位而SUB仅可对进位位进行清除,而不会对进位位产生其他影响移1位和循环指令也可影响进位位C,以及SETC、CLRC和LST指令也可影响C条件转移、调用和返回指令可以根据C的状态进行执行复位时C 被置1CNF---片内DARAM配置位:若CNF=0,可配置的双口RAM区被映射到数据存储空间若CNF=I,可配置的双口RAM 区被映射到程序存储空间CNF位可通过SETC CNF,CLRC CNF和LST指令修改R/S/复位时CNF置为0 DP----数据存储器页指针:9位的DP寄存器与一个指令字的低七位一起形成一个16位的直接寻址地址INTM---中断模式位:当INTM被置为0时,所有的未屏蔽中断使能当它被置1,所有可屏蔽中断禁止OV----溢出标志位:该位保存一个被锁存的值,用以指示CALU中是否有溢出发生一旦发生溢出,OV位保持为1直到下列条件中的一个发生时才能被清除OVM---溢出方式位:当OVM=0时,累加器中结果正常溢出当OVM=1时,根据遇到溢出的情况,累加器被设置为它的最大正值或负值SETC指令和CLRC指令分别对该位进行置位和复位PM----乘积移位方式:若PM=00,乘法器的32位乘积结果不移位直接装入CALU若PM=01,PREG输出左移1位后装入CALU,最低位LSB以0填充若PM=10,PREG输出左移4位后装入CALU,最低位LSB以0填充若PM=11,时PREG输出进行符号扩展右移六位SXM----符号扩展方式位:当SXM=1时,数据通过定标移位器传送到累加器时将产生符号扩展SXM=0将抑制符号扩展SXM位对某些指令没有影响TC---- 测试/控制标志位:在下述情况之一,TC位被置1:由BIT或BITT指令测试的位为1当利用NORM指令测试时,累加器的两个最高有效位"异或"功能为真条件转移、调用和返回指令可根据TC位的条件来执行BIT、BITT、CMPR、LST和NORM指令影响TC位XF---- XF引脚状态位:该位决定XF引脚的状态SETCXF指令可对位XF进行置位,而CLRCXF指令可对其进行清0复位时XF置1SCSR1--系统控制和状态寄存器1---地址7018HD15---保留位D14---CLKSRC。

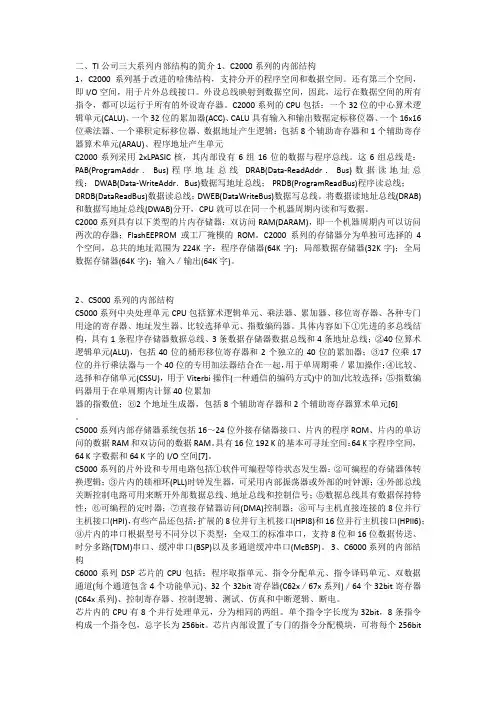

二、TI公司三大系列内部结构的简介 1、C2000系列的内部结构1,C2000系列基于改进的哈佛结构,支持分开的程序空间和数据空间。

还有第三个空间,即I/O空间,用于片外总线接口。

外设总线映射到数据空间,因此,运行在数据空间的所有指令,都可以运行于所有的外设寄存器。

C2000系列的CPU包括:一个32位的中心算术逻辑单元(CALU)、一个32位的累加器(ACC)、CALU具有输入和输出数据定标移位器、一个16x16位乘法器、一个乘积定标移位器、数据地址产生逻辑:包括8个辅助寄存器和1个辅助寄存器算术单元(ARAU)、程序地址产生单元C2000系列采用2xLPASIC核,其内部设有6组16位的数据与程序总线。

这6组总线是:PAB(ProgramAddr.Bus)程序地址总线DRAB(Data-ReadAddr.Bus)数据读地址总线; DWAB(Data-WriteAddr.Bus)数据写地址总线; PRDB(ProgramReadBus)程序读总线;DRDB(DataReadBus)数据读总线;DWEB(DataWriteBus)数据写总线。

将数据读地址总线(DRAB)和数据写地址总线(DWAB)分开,CPU就可以在同一个机器周期内读和写数据。

C2000系列具有以下类型的片内存储器:双访问RAM(DARAM),即一个机器周期内可以访问两次的存器;FlashEEPROM或工厂掩模的ROM。

C2000系列的存储器分为单独可选择的4个空间,总共的地址范围为224K字:程序存储器(64K字);局部数据存储器(32K字);全局数据存储器(64K字);输入/输出(64K字)。

2、C5000系列的内部结构C5000系列中央处理单元CPU包括算术逻辑单元、乘法器、累加器、移位寄存器、各种专门用途的寄存器、地址发生器、比较选择单元、指数编码器。

具体内容如下①先进的多总线结构,具有1条程序存储器数据总线、3条数据存储器数据总线和4条地址总线;②40位算术逻辑单元(ALU),包括40位的桶形移位寄存器和2个独立的40位的累加器;③17位乘17位的并行乘法器与一个40位的专用加法器结合在一起,用于单周期乘/累加操作;④比较、选择和存储单元(CSSU),用于Viterbi操作(一种通信的编码方式)中的加/比较选择;⑤指数编码器用于在单周期内计算40位累加器的指数值;⑥2个地址生成器,包括8个辅助寄存器和2个辅助寄存器算术单元[6]。

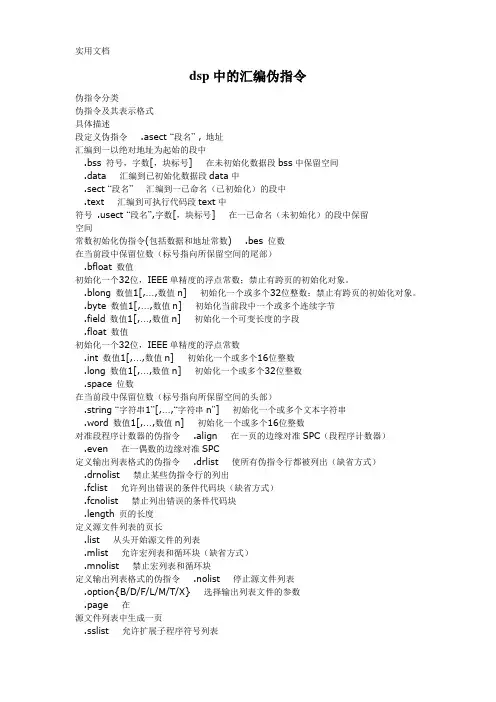

dsp中的汇编伪指令伪指令分类伪指令及其表示格式具体描述段定义伪指令 .asect “段名” , 地址汇编到一以绝对地址为起始的段中.bss 符号,字数[,块标号] 在未初始化数据段bss中保留空间.data 汇编到已初始化数据段data中.sect “段名”汇编到一已命名(已初始化)的段中.text 汇编到可执行代码段text中符号 .usect “段名”,字数[,块标号] 在一已命名(未初始化)的段中保留空间常数初始化伪指令(包括数据和地址常数) .bes 位数在当前段中保留位数(标号指向所保留空间的尾部).bfloat 数值初始化一个32位,IEEE单精度的浮点常数;禁止有跨页的初始化对象。

.blong 数值1[,…,数值n] 初始化一个或多个32位整数;禁止有跨页的初始化对象。

.byte 数值1[,…,数值n] 初始化当前段中一个或多个连续字节.field 数值1[,…,数值n] 初始化一个可变长度的字段.float 数值初始化一个32位,IEEE单精度的浮点常数.int 数值1[,…,数值n] 初始化一个或多个16位整数.long 数值1[,…,数值n] 初始化一个或多个32位整数.space 位数在当前段中保留位数(标号指向所保留空间的头部).string “字符串1”[,…,“字符串n”] 初始化一个或多个文本字符串.word 数值1[,…,数值n] 初始化一个或多个16位整数对准段程序计数器的伪指令 .align 在一页的边缘对准SPC(段程序计数器).even 在一偶数的边缘对准SPC定义输出列表格式的伪指令 .drlist 使所有伪指令行都被列出(缺省方式).drnolist 禁止某些伪指令行的列出.fclist 允许列出错误的条件代码块(缺省方式).fcnolist 禁止列出错误的条件代码块.length 页的长度定义源文件列表的页长.list 从头开始源文件的列表.mlist 允许宏列表和循环块(缺省方式).mnolist 禁止宏列表和循环块定义输出列表格式的伪指令 .nolist 停止源文件列表.option{B/D/F/L/M/T/X} 选择输出列表文件的参数.page 在源文件列表中生成一页.sslist 允许扩展子程序符号列表.ssnolist 禁止扩展子程序符号列表(缺省方式).tab 大小设置表的大小.title “字符串”在列表页头显示一个标题.width 页宽设置源文件列表的页宽外部文件定位的指伪令 .copy [“]文件名[”] 包含其他文件中的源语句.def 符号1[,…,符号n] 标明一个或多个在当前模块中定义而在其他模块中要用到的符号.global 符号1[,…,符号n] 标明一个或多个全局(外部)符号.include [“]文件名[”] 包含其他文件中的源语句.mlib [“]文件名[”] 定义宏定义库.ref符号1[,…,符号n] 标明一个或多个在另一模块中定义而在当前模块中要用到的符号条件汇编伪指令.break [确切定义的表达式] 如果条件满足,就结束.loop汇编。

dsp中的汇编伪指令伪指令分类伪指令及其表示格式具体描述段定义伪指令 .asect “段名” , 地址汇编到一以绝对地址为起始的段中.bss 符号,字数[,块标号] 在未初始化数据段bss中保留空间.data 汇编到已初始化数据段data中.sect “段名”汇编到一已命名(已初始化)的段中.text 汇编到可执行代码段text中符号 .usect “段名”,字数[,块标号] 在一已命名(未初始化)的段中保留空间常数初始化伪指令(包括数据和地址常数) .bes 位数在当前段中保留位数(标号指向所保留空间的尾部).bfloat 数值初始化一个32位,IEEE单精度的浮点常数;禁止有跨页的初始化对象。

.blong 数值1[,…,数值n] 初始化一个或多个32位整数;禁止有跨页的初始化对象。

.byte 数值1[,…,数值n] 初始化当前段中一个或多个连续字节.field 数值1[,…,数值n] 初始化一个可变长度的字段.float 数值初始化一个32位,IEEE单精度的浮点常数.int 数值1[,…,数值n] 初始化一个或多个16位整数.long 数值1[,…,数值n] 初始化一个或多个32位整数.space 位数在当前段中保留位数(标号指向所保留空间的头部).string “字符串1”[,…,“字符串n”] 初始化一个或多个文本字符串.word 数值1[,…,数值n] 初始化一个或多个16位整数对准段程序计数器的伪指令 .align 在一页的边缘对准SPC(段程序计数器).even 在一偶数的边缘对准SPC定义输出列表格式的伪指令 .drlist 使所有伪指令行都被列出(缺省方式).drnolist 禁止某些伪指令行的列出.fclist 允许列出错误的条件代码块(缺省方式).fcnolist 禁止列出错误的条件代码块.length 页的长度定义源文件列表的页长.list 从头开始源文件的列表.mlist 允许宏列表和循环块(缺省方式).mnolist 禁止宏列表和循环块定义输出列表格式的伪指令 .nolist 停止源文件列表.option{B/D/F/L/M/T/X} 选择输出列表文件的参数.page 在源文件列表中生成一页.sslist 允许扩展子程序符号列表.ssnolist 禁止扩展子程序符号列表(缺省方式).tab 大小设置表的大小.title “字符串”在列表页头显示一个标题.width 页宽设置源文件列表的页宽外部文件定位的指伪令 .copy [“]文件名[”] 包含其他文件中的源语句.def 符号1[,…,符号n] 标明一个或多个在当前模块中定义而在其他模块中要用到的符号.global 符号1[,…,符号n] 标明一个或多个全局(外部)符号.include [“]文件名[”] 包含其他文件中的源语句.mlib [“]文件名[”] 定义宏定义库.ref符号1[,…,符号n] 标明一个或多个在另一模块中定义而在当前模块中要用到的符号条件汇编伪指令 .break [确切定义的表达式] 如果条件满足,就结束.loop汇编。

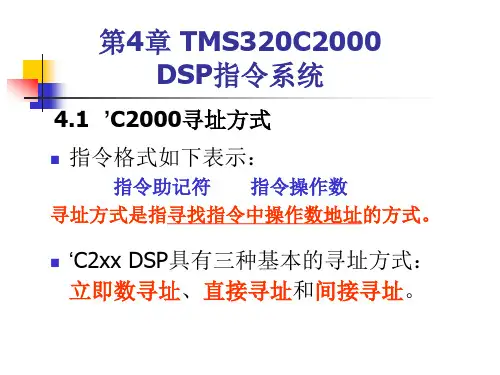

第六章 DSP的寻址方式和汇编指令当硬件执行指令时,寻找指令所指定的参与运算飞操作数的方式——寻址方式。

根据程序的要求采用不同的寻址方式,可以有效地缩短程序的运行时间和提高代码执行效率。

汇编指令是可执行指令,每一条指令对应一条机器码,用来控制处理器仲的执行部分进行各种操作。

在本章节当中将主要以基于C28x的DSP芯片为例,为读者讲解DSP的寻址方式和汇编指令系统,其中大部分内容也可适用于其他Ti公司的DSP产品。

6.1汇编语言指令集概述在学习C28x系列DSP的寻址方式和汇编指令指令之前,先来对一些基础的知识进行讲解一下先,在汇编程序当中开发人员会常常使用到许多的特殊符号和标志,它们都具有特殊的含义,在学习汇编之前读者们必须先理解这些符号和标志含义,在这里会对其中最常用最重要的操作数符号和寄存器经行详细说明。

在进行汇编讲解之前先来了解一下开发的核心——CPU。

在TMS320C2000系列中,CPU 内核为:C20x/C24x/C240x:C2xLP:C27x/C28x:C27x、C28x这些CPU的硬件结构有一定差别,指令集也不相同,但是,在C28x芯片中可以通过选择兼容特性模式,使C28xCPU与C27xCPU及C2xLPCPU具有最佳兼容性。

可通过状寄存器STl的位OBJMODE和位AMODE的组合,选定模式。

C28x芯片具有3种操作模式:1.C28x模式:在该模式中,用户可以使用C28x的所有有效特性、寻址方式和指令系统,因此,一般应使C28x芯片工作于该种模式。

2.C27x目标——兼容模式:在复位时,C28x的CPU处于C27x目标-兼容模式。

在该模式下,目标码与C27xCPU完全兼容,且它的循环—计数也与C27xCPU兼容。

3.C2xLP源——兼容模式:该模式允许用户运行C2xLP的源代码,这些源代码是用C28x代码生成工具编译生成的。

在下面的讲解当中会牵涉到模式的转换,希望读者要搞清楚每一个模式的对应关系。

DSP汇编指令引言DSP是指数字信号处理器,是一种专门用于数字信号处理的微处理器。

DSP汇编指令是在DSP芯片上执行操作的命令。

这篇文档将常见的DSP汇编指令及其使用方法。

通用指令MOVMOV是Move的缩写,指将数据从一个寄存器移动到另一个寄存器或内存地址中。

它有很多不同的格式,例如:MOV R1, #0 ; 将0存储在R1寄存器中MOV R2, R1 ; 将R1寄存器中的值复制到R2寄存器中MOV @R3, R2 ; 将R2寄存器中的值存储在R3指向的内存地址中ADD和SUBADD和SUB分别表示加法和减法运算。

它们也有不同的格式,例如:ADD R1, R2 ; 将R2寄存器中的值加到R1寄存器中ADD R1, #2 ; 将2加到R1寄存器中SUB R1, R2 ; 将R2寄存器中的值从R1寄存器中减去AND和ORAND和OR分别表示按位与和按位或运算。

它们也有不同的格式,例如:AND R1, R2 ; 将R1寄存器和R2寄存器中的值按位与后存储在R1寄存器中OR R1, R2 ; 将R1寄存器和R2寄存器中的值按位或后存储在R1寄存器中CMPCMP是Compare的缩写,用于比较两个值。

它会将两个操作数相减,并设置相关的标志位。

它的格式如下:CMP R1, R2 ; 比较R1和R2寄存器中的值跳转指令JMPJMP是Jump的缩写,用于无条件跳转到目标地址。

它的格式如下:JMP label ; 跳转到标签为label的位置JNZ和JZJNZ和JZ分别表示如果结果不为零则跳转和如果结果为零则跳转。

它们的格式如下:JNZ label ; 如果前一条CMP指令比较结果不为零,则跳转到标签为label的位置JZ label ; 如果前一条CMP指令比较结果为零,则跳转到标签为label的位置JGE和JLEJGE和JLE分别表示如果大于或等于则跳转和如果小于或等于则跳转。

它们的格式如下:JGE label ; 如果前一条CMP指令比较结果大于或等于,则跳转到标签为label的位置JLE label ; 如果前一条CMP指令比较结果小于或等于,则跳转到标签为label的位置循环指令DJNZDJNZ是Decrement and Jump if Not Zero的缩写,表示如果操作数不为零则减1并跳转到目标地址。

二、TI公司三大系列内部结构的简介 1、C2000系列的内部结构1,C2000系列基于改进的哈佛结构,支持分开的程序空间和数据空间。

还有第三个空间,即I/O空间,用于片外总线接口。

外设总线映射到数据空间,因此,运行在数据空间的所有指令,都可以运行于所有的外设寄存器。

C2000系列的CPU包括:一个32位的中心算术逻辑单元(CALU)、一个32位的累加器(ACC)、CALU具有输入和输出数据定标移位器、一个16x16位乘法器、一个乘积定标移位器、数据地址产生逻辑:包括8个辅助寄存器和1个辅助寄存器算术单元(ARAU)、程序地址产生单元C2000系列采用2xLPASIC核,其内部设有6组16位的数据与程序总线。

这6组总线是:PAB(ProgramAddr.Bus)程序地址总线DRAB(Data-ReadAddr.Bus)数据读地址总线; DWAB(Data-WriteAddr.Bus)数据写地址总线; PRDB(ProgramReadBus)程序读总线;DRDB(DataReadBus)数据读总线;DWEB(DataWriteBus)数据写总线。

将数据读地址总线(DRAB)和数据写地址总线(DWAB)分开,CPU就可以在同一个机器周期内读和写数据。

C2000系列具有以下类型的片内存储器:双访问RAM(DARAM),即一个机器周期内可以访问两次的存器;FlashEEPROM或工厂掩模的ROM。

C2000系列的存储器分为单独可选择的4个空间,总共的地址范围为224K字:程序存储器(64K字);局部数据存储器(32K字);全局数据存储器(64K字);输入/输出(64K字)。

2、C5000系列的内部结构C5000系列中央处理单元CPU包括算术逻辑单元、乘法器、累加器、移位寄存器、各种专门用途的寄存器、地址发生器、比较选择单元、指数编码器。

具体内容如下①先进的多总线结构,具有1条程序存储器数据总线、3条数据存储器数据总线和4条地址总线;②40位算术逻辑单元(ALU),包括40位的桶形移位寄存器和2个独立的40位的累加器;③17位乘17位的并行乘法器与一个40位的专用加法器结合在一起,用于单周期乘/累加操作;④比较、选择和存储单元(CSSU),用于Viterbi操作(一种通信的编码方式)中的加/比较选择;⑤指数编码器用于在单周期内计算40位累加器的指数值;⑥2个地址生成器,包括8个辅助寄存器和2个辅助寄存器算术单元[6]。

C2的指令集C2xx DSP中共有汇编语言指令88条,分成6类:①累加器、算术和逻辑指令26条如:ADD、LACC、AND②辅助寄存器和数据页面指针指令7条如:MAR、LAR等③TREG、PREG和乘法指令20条如:LT、MTY、PAC等④分支、调用指令12条如:B、BCND、INTR等⑤控制指令15条如:SPM、POP、BIT等⑥存储器和I/O操作指令8条如:BLDD、SPLK、TBLR等注:有些指令助记符是增强性指令,对应于几条简单指令(机器码),如:ADD 可完成ADD,ADDH,ADDK和ADLK等功能,这样做可使程序更简洁并易读。

累加器,算术与逻辑指令助记符指令描述指令的中英文指令字周期ABSACC的绝对值Absolute Value of Accumulator(累加器内容取绝对值11ADD 加给ACC,带0~15-bit移位,直接或间接Add to Accumulator(加入累加器)11加给ACC,带0~15-bit移位,长立即数22加给ACC,带16-bit移位,直接或间接1 1加给ACC,短立即数1 1ADDC 加给ACC,带进位,直接或间接Add to Accumulator With Carry(带进位位加至累加器)1 1ADDS加给ACC低段,带符号展开抑制,直接或间接Add to Accumulator With Sign ExtensionSuppressed(抑制符号扩展加至累加器)1 1ADDT加给ACC,由TREG决定移位,直接或间接Add to Accumulator With Shift Specifiedby TREG(按TREG寄存器内容移位后加至累加器)1 1AND ACC与数据值,直接或间接AND With Accumulator(和累加器逻辑“与”)1 1ACC与长立即数,带0~15-bit移位2 2ACC与长立即数,带16-bit移位2 2CMPLACC取补Complement Accumulator(累加器求反(补)1 1LACC 带移位0~15-bit装入ACC,直接或间接Load Accumulator With Shift(数据左移后装入累加器)1 1带移位0~15-bit装入ACC,长立即数2 2带移位16-bit装入ACC,直接或间接1 1LACL 装入ACC的低段,直接或间接Load Low Accumulator and Clear HighAccumulator(装载累加器低位并清累加器高位)1 1装入ACC的低段,短立即数1 1LACT 装入ACC,由TREG低4位(0~3bit)决定移位(0~15bit),直接或间接Load Accumulator With Shift Specifiedby TREG(按TREG规定的移位后装入累加器)1 1NEG ACC取负Negate Accumulator(累加器求负) 1 1NORMACC内容归一化,间接Normalize Contents of Accumulator(规格化累加器)1 1OR ACC或数据值,直接或间接OR With Accumulator(与累加器逻辑“或” )1 1ACC或长立即数,带0~15-bit移位2 2ACC或长立即数,带16-bit移位2 2ROLACC循环左移Rotate Accumulator Left(累加器逻辑循环左移)1 1RORACC循环右移Rotate Accumulator Right(累加器逻辑循环右移)1 1SACH 存高段ACC,带移位0~7-bit,直接或间接Store High Accumulator With Shift(移位并存储累加器高位)1 1SACL 存低段段ACC,带移位0~7-bit,直接或间接Store Low Accumulator With Shift(移位并存储累加器低位)1 1SFLACC左移Shift Accumulator Left(累加器算术左移)1 1SFRACC右移Shift Accumulator Right(累加器算术右移)1 1SUB 从ACC减,带移位0~15 - bit,直接或间接Subtract From Accumulator (从累加器减 1 1从ACC减,带移位 0~15-bit,长立即数2 2从ACC减,带移位 16- bit,1 1直接或间接从ACC减,短立即数1 1SUBB 从ACC带借位减,直接或间接Subtract From Accumulator With Borrow(带借位从累加器减1 1SUBC 条件减,直接或间接Conditional Subtract(条件减法 1 1SUBS从ACC减,抑制符号展开,直接或间接Subtract From Accumulator With SignExtension Suppressed (抑制符号扩展从累加器减1 1SUBT 从ACC减,由 TREG决定的移位( 0~15-bit),直接或间接Subtract From Accumulator With ShiftSpecified by TREG (按TREG指定的值进行移位后从累加器减1 1XOR ACC异或数据值,直接或间接Exclusive OR With Accumulator (与累加器逻辑“异或”1 1ACC异或长立即数,带0~15-bit移位2 2ACC异或长立即数,带16-bit移位2 2ZALR ACC低段置0,舎入后装入ACC高段,直接或间接Zero Low Accumulator and Load HighAccumulator With Rounding(累加器低位清零并四舍五入装载累加器高位1 1辅助寄存器指令助记符指令描述指令的中英文指令字周期ADRK 常数加给AR,短立即数Add Short-Immediate Value toAuxiliary Register(短立即数加至当前辅助寄存器1 1BANZ 当前AR非0转移,间接Branch on Auxiliary RegisterNot Zero(辅助寄存器不等于2 2零转移CMPR 当前AR与AR0比较Compare Auxiliary RegisterWith AR0 (比较当前辅助寄存器和AR0,并把比较结果放在ST1的TC位1 1LAR 从指定的数据位置装入指定的AR,直接或间接Load Auxiliary Register(装载辅助寄存器1 2常数装入指定的AR,短立即数1 2常数装入指定的AR,长立即数2 2MAR 修改当前AR和/或ARP,间接(直接时无操作)Modify Auxiliary Register(修改辅助寄存器1 1SAR 存指定的AR至指定位置,直接或间接Store Auxiliary Register(存储辅助寄存器1 1SBRK 从当前AR减去常数,短立即数Subtract Short-ImmediateValue From AuxiliaryRegister(从当前辅助寄存器减去短立即数1 1暂时寄存器(TREG)、乘积寄存器(PREG)和乘法指令助记符指令描述指令的中英文指令字周期APAC PREG加到ACC Add PREG to Accumulator(P寄存器加至累加器1 1LPH 装入PREG高位Load Product Register HighWord(装载乘积寄存器高位1 1LT 装入TREG,直接或间接Load TREG(装载TREG寄存器1 1LTA 装入TREG,累加前次乘积,直接或间接Load TREG and AccumulatePrevious Product(装载TREG寄存器并累加前次乘积1 1LTD 装入TREG,累加前次乘积,搬移数据,直接或间接Load TREG, AccumulatePrevious Product, and MoveData(装载TREG寄存器、累加前次乘积并移动数据1 1LTP 装入TREG,存PREG入ACC,直接或间接Load TREG and Store PREG inAccumulator(装载TREG寄存器并存储PREG寄存器到累计器1 1LTS 装入TREG,减去前次乘积,直接或间接Load TREG and SubtractPrevious Product(装载TREG寄存器并减去前次乘积1 1MAC 乘且累加,直接或间接Multiply and Accumulate(乘且累加2 3MACD 乘且累加,数据转移,直接或间接Multiply and Accumulate WithData Move(乘且累加并带数据移动2 3MPY TREG乘数据值,直接或间接Multiply(乘 1 1TREG乘13-bit常数,短立即数1 1MPYA 乘且累加前次乘积,直接或间接Multiply and AccumulatePrevious Product(乘且累加前次乘积1 1MPYS 乘且减去前次乘积,直接或间接Multiply and Subtract PreviousProduct(乘且减去前次乘积 1 1MPYU 乘无符号数,直接或间接Multiply Unsigned(无符号乘法 1 1 PAC PREG装入ACC Load Accumulator With ProductRegister(将乘积寄存器装入累加器1 1SPAC 从ACC减去PREG Subtract PREG FromAccumulator(从累加器减去PREG寄存器1 1 SPH 存高段PREG,直接或间接Store High PREG(存储PREG 1 1高位SPL 存高段PREG,直接或间接Store Low PREG(存储PREG低位1 1SPM 设置乘积移位方式Set PREG Output ShiftMode(设置PREG移位方式1 1SQRA 平方且累加前次乘积,直接或间接Square Value and AccumulatePrevious Product(平方并累加前次乘积1 1SQRS 平方且减去前次乘积,直接或间接Square Value and SubtractPrevious Product(平方并减去前次乘积1 1转移指令助记符指令描述指令的中英文指令字周期B 无条件转移,间接Branch Unconditionally(无条件转移 2 4 BACC 转移至ACC指定的地址Branch to Location Specified byAccumulator(按累加器内容转移1 4BANZ 当前AR非0时转移,间接;判断(AR,(AR-1→(ARBranch on Auxiliary Register NotZero(当前辅助寄存器不等于零转移 2 4BCND 条件转移Branch Conditionally(条件转移 2 4CALA 调用ACC指定位置的子程序,间接Call Subroutine at Location Specifiedby Accumulator(调用累加器低16位指定地址处的子程序2 4CALL 调用子程序,间接Call Unconditionally(无条件调用指令2 4 CC 条件调用Call Conditionally(条件转移指令 2 4 INTR 软中断Software Interrupt(软中断 1 4NMI 不可禁止的中断Nonmaskable Interrupt(不可屏蔽中断转移到程序存储器1 4 RET 从子程序返回Return From Subroutine(子程序返回 1 4 RETC 条件返回Return Conditionally(条件返回 1 4 TRAP 软件中断Software Interrupt(软件陷阱中断 1 4 控制指令助记符指令描述指令的中英文指令字周期BIT 位测试,直接或间接Test Bit(位测试 1BITT 由TREG指定的位测试,直接或间接Test Bit Specified byTREG(测试TREG寄存器规定的位1CLRC 清除C位Clear Control Bit(状态位清零1清除INTM位 1 1 清除OVM位 1 1 清除SXM位 1 1 清除TC位 1 1 清除XF位 1 1IDLE 停止执行,直至中断Idle Until Interrupt(空闲直至中断发生1LDP 装入数据页指针,直接或间接Load Data PagePointer(装载数据页指针 1装入数据页指针,短立即数1 2LST 装入状态寄存器ST0,直接或间接Load Status Register(装载状态寄存器1装入状态寄存器ST0,直接或间接1 2NOP 无操作No Operation(空操作 1POP 将堆栈顶弹出至ACC低段Pop Top of Stack to Low Accumulator(栈顶弹出至累加器的低位1POPD 将堆栈顶弹出至数据存储器,直接或间接Pop Top of Stack to DataMemory(栈顶弹出至数据存储器1PSHD 将数据存储器的值压入堆栈,直接或间接Push Data-Memory ValueOnto Stack(数据存储器值进栈1PUSH 将ACC低段压入堆栈Push Low AccumulatorOnto Stack(累加器低位进栈1RPT 重复执行下一条指令,直接或间接Repeat NextInstruction(重复执行下条指令1重复执行下一条指令,短立即数1 1SETC 设置SXM位Set Control Bit(置位 1 设置TC位 1 1设置XF位 1 1设置C位 1 1设置CNF位 1 1设置INTM位 1 1设置OVM位 1 1SPM 设置乘积移位模式Set PREG Output ShiftMode(设置PREG移位输出方式1SST 存状态寄存器ST0,直接或间接Store Status Register(存储状态寄存器1存状态寄存器ST1,直接或间接1 1I/O和存储器指令助记符指令描述指令的中英文指令字周期BLDD 数据块从数据存储器搬移至数据存储器,直接或间接,长立即数作源存储器地址Block Move From Data Memory toData Memory(数据存储器到数据存储器的块传送2 3BLPD 数据块从程序存储器搬移至数据存储器,直接或间接,长立即数作源存储器地址Block Move From Program Memoryto Data Memory(程序存储器到数据存储器的块传2 3DMOV 数据在数据存储器中搬移,直接或间接Data Move in Data Memory(在数据存储器内传送数据1 1IN 从I/O输入数据,直接或间接Input Data From Port(端口地址送数据地址总线2 2OUT 输出数据至口,直接或间接Output Data to Port(端口地址送数据地址总线2 3SPLK 存长立即数至数据存储器,直接或间接Store Long-Immediate Value to DataMemory(存储长立即数值至数据存储器2 2TBLR 读数据表,直接或间接Table Read(读表 1 3TBLW 写数据表,直接或间接 Table Write(写数据表 1 31. 指令格式(即语法)不带进位加法指令格式: ADD dma [,shift] ;直接寻址 ADD dma ,16 ;16位左移直接寻址 ADD ind [,shift [,ARn ] ] ;间接寻址 ADD ind ,16[,ARn ] ;16位左移的间接寻址 ADD #k ;短立即寻址ADD #lk [,shift ] ;长立即寻址2.操作数dma;直接寻址时,数据存储器地址低7位shift:;左移值从0 到 15(默认值为0)n;指示下一个辅助寄存器n= 0~ 7 k: ;8位短立即数值lk: ;16位短立即数值ind;选择下列7种间接寻址方式中的一种* *+ *- *0+ *0- *BR0+ *BR0-3.操作码.执行4(1 (Smem+(src→src(2 (Smem<<(TS)+(src)→src(3 (Smem<<16+(src)→dst(4 (Smem[ <<SHIFT]+(src)→dst(5 (Xmem <<SHIFT+(src)→src(6( (Xmem+ (Ymem <<16→dst(7 lk<<SHFT+(src)→dst(8 lk<<16+(src)→dst(9 (src or[dst]+(src)<<SHIFT→dst(10 (src or[dst]+(src)<<ASM→dst5.状态位指令执行受SXM和OVM的影响,指令执行结果影响C和OV 6.说明把一个16位的数加到选定的累加器中,或一个采用双数据存储器操作数寻址的操作数Xmen。

TI公司三大系列DSP芯片指令系统比较摘要:DSP技术已成为目前电子工业领域发展最迅速的技术,在各行各业的应用越来越广泛。

DSP微处理器是以数字信号来处理大量信息的器件,已成为电子工业领域增长最迅速的产品之一。

TI公司作为最早从事DSP微处理器研究的厂商之一,已经形成了三大系列的DSP芯片,在电子行业各个领域占有很大的市场份额。

本文通过对TI公司三大系列DSP芯片的简要介绍,对这三大系列芯片的指令系统进行了比较。

关键词:TI DSP芯片指令系统比较一、前言在经历整整二十年的市场拓展之后,DSP所树立的高速处理器地位不仅不可动摇,而且业已成为数字信息时代的核心引擎。

与此同时,DSP的市场正在蓬勃发展。

从TI推出业界第一颗商用DSP开始,陆续有公司设计出适合于DSP处理技术的处理器,于是DSP开始成为一种高性能处理器的名称。

TI在1982年发表一款DSP处理器名为TMS32010,其出色的性能和特性倍受业界的关注,当努力使DSP处理器每MIPS成本也降到了适合于商用的低于$10美元范围时,DSP不仅在在军事,而且在工业和商业应用中不断获得成功。

1991年TI推出的DSP批量单价首次低于$5美元而可与16 位的微处理器相媲美,但所能提供的性能却是其5至10倍。

多家公司跻身于DSP领域与TI进行市场竞争。

TI首家提供可定制DSP,称作cDSP。

cDSP 基于内核DSP的设计可使DSP具有更高的系统集成度,大加速了产品的上市时间。

同时TI瞄准DSP 电子市场上成长速度最快的领域,适时地提供各种面向未来发展的解决方案。

到九十年代中期,这种可编程的DSP器件已广泛应用于数据通信、海量存储、语音处理、汽车电子、消费类音频和视频产品等等,其中最为辉煌的成就是在数字蜂窝电话中的成功,逐渐形成了现今TI三大系列主流DSP芯片。

TI通过不断革新,推陈出新,DSP业务也一跃成为TI的最大的业务,并始终处于全球DSP市场的领导地位。