存储单元结构原理

- 格式:pdf

- 大小:1.01 MB

- 文档页数:21

动态存储器工作原理

动态存储器(DRAM)是计算机系统中常用的一种主存储器类型,其工作原理如下:

存储单元结构:

DRAM由许多存储单元组成,每个存储单元由一个电容器和一个晶体管组成。

电容器用于存储数据位,晶体管用于控制读取和写入操作。

电荷存储:

当电容器充电时,表示存储的是数据位1;电容器放电时,表示存储的是数据位0。

因此,电容器的充电状态表示了存储的数据。

数据读取:

当需要读取数据时,晶体管被打开,电荷从电容器流入读取线,通过放大和解码的过程,将电荷转换为电压信号,以供其他部件使用。

数据刷新:

由于电容器会逐渐失去电荷,需要定期刷新以保持数据的稳定性。

这是动态RAM(DRAM)与静态RAM(SRAM)的主要区别之一。

在刷新周期中,内存控制器会周期性地读取和重新写入所有存储单元,以更新其中的数据。

行选通和列选通:

DRAM中的存储单元被组织成行和列的结构。

在读取或写入特定单元时,首先需要选通相应的行和列。

行选通时,将特定行的数据放大并传递到输出线路上;列选通时,将输出线路上的数据发送给请求的设备。

预充电:

由于电容器的读取会导致电荷损失,需要在读取之前对其进行预充电操作,以确保准确读取数据。

总体而言,DRAM的工作原理是基于电容器的充放电来存储数据,通过晶体管控制数据的读取和写入操作,并通过周期性的刷新来维持数据的稳定性。

DRAM基本结构与原理(⼀)DRAM基本结构与原理(⼀)东南⼤学ASIC⼯程中⼼ matlinsas@DRAM(Dynamic Random Access Memory),即动态随机存储器,也就是我们常说的计算机内存,在现代计算机系统和SOC系统中有很重要的作⽤。

本⽂主要对DRAM中的⼀些基本原理进⾏总结,⽬的是为了更好理解DDRC(Double Data Rata DRAM controller)中的时序关系与时序参数。

⼀.DRAM基本电路结构2.1基本存储单元cell2.1.1 3T1C与1T1CDRAM基本电路结构如图所⽰:图中的基本结构单元是1T1C(1 Transistor -1 Capacitor)。

其⼯作的⼤致原理是:当Word Line选通时,晶体管导通,从⽽可以从Bit Line上读取存储在电容器上的位信息。

⽽在早期的DRAM中的基本结构却不是这样的,⽽是3T1C(3 Transistor -1 Capacitor)如下图所⽰:使⽤三个晶体管作为开关,这样设计的优点是:当读取存储在电容上的位信息时,不会影响电容上的电荷,从⽽读后不需要对单元进⾏precharge。

关于precharge的原理在下⽂会有详细介绍,这⾥我们只要了解3T1C的结构读存储器不会破坏其存储在DRAM中的信息。

但是由于1T1C的结构⽐3T1C的结构⾯积节省很多,因此现代DRAM中常⽤的还是1T1C结构。

此外由DRAM基本电路结构图,我们可以知道DRAM的信息是存储在在电容当中,⽽电容中的电荷会因为漏电流存在原因⽽逐渐漏掉,因此需要不断refresh(刷新),这也是DRAM称为动态的原因。

例如,90nm⼯艺下,DRAM的cell单元的电容量是30pf,它的漏电流是1fA,漏光的时间是随着温度的变化⽽变化的。

现在的DRAM的刷新时间⼀般是32ms或者64ms。

2.1.2 堆电容(Stacked Capacitor)与沟电容(Trench Capacitor)下⾯我们从更底层来了解DRAM存储电容,关于存储电容在现代业界也没有统⼀,仍然存在两⼤阵营,分别是堆电容(Stacked Capacitor)与沟电容(Trench Capacitor),像三星这样的⼤公司使⽤是前者。

存储器的层次结构及组成原理一、引言存储器是计算机中非常重要的组成部分,它用于存储和读取数据。

随着计算机技术的发展,存储器也在不断地升级和改进。

存储器的层次结构是指不同类型的存储器按照速度、容量和成本等方面的差异被组织成一种层次结构。

本文将介绍存储器的层次结构及其组成原理。

二、存储器的层次结构1. 存储器分类根据存取速度不同,可将存储器分为主存(RAM)、高速缓存(Cache)、二级缓存、三级缓存等多级缓存以及辅助存储器(ROM、磁盘等)。

2. 层次结构主要分为三个层次:CPU内部高速缓冲寄存器(L1 Cache)、CPU外部高速缓冲寄存器(L2 Cache)和主内存(RAM)。

3. 层次结构优点层次结构能够充分利用各种类型的硬件设备,使得计算机系统能够更加高效地运行。

在执行指令时,CPU首先从最快的L1 Cache中查找数据,如果没有找到,则会查找L2 Cache,最后才会查找主内存。

这样的层次结构设计可以大大提高CPU访问数据的速度,减少CPU等待的时间。

三、存储器的组成原理1. 静态随机存取存储器(SRAM)SRAM是一种使用静电场来存储数据的存储器。

它由多个存储单元组成,每个单元由一个触发器和两个传输门组成。

SRAM的读写速度非常快,但是它比较昂贵,并且需要更多的电源。

2. 动态随机访问存储器(DRAM)DRAM是一种使用电容来存储数据的存储器。

它由多个存储单元组成,每个单元由一个电容和一个开关组成。

DRAM比SRAM更便宜,但是读写速度相对较慢。

3. 双倍数据率SDRAM(DDR SDRAM)DDR SDRAM是一种高速内存技术,可以在每个时钟周期传输两次数据。

这使得DDR SDRAM比普通SDRAM更快。

4. 图形双倍数据率SDRAM(GDDR SDRAM)GDDR SDRAM是一种专门为图形处理器设计的高速内存技术。

它具有更高的频率和带宽,适用于处理大量图像和视频数据。

5. 闪存闪存是一种非易失性存储器,可以在断电时保存数据。

储存芯片储存原理

储存芯片的储存原理是通过将电荷存储在存储单元中来表示数据。

储存单元通常由晶体管构成,晶体管可以操作电流流动和阻断。

在动态随机存取存储器(DRAM)中,每个存储单元由一个晶体管和一个电容器组成。

当写入数据时,晶体管被打开,电荷被存储在电容器中。

电容器中的电荷代表着存储的数据,1表示有电荷,0表示无电荷。

然而,由于电容器会逐渐失去电荷,因此数据需要被周期性地刷新。

相比之下,静态随机存取存储器(SRAM)使用了更复杂的储存单元结构。

每个SRAM存储单元由6个晶体管构成,分别是两个交叉的反相器和两个传输门。

这种结构保持了数据的稳定性,只要有电源供应,数据就会一直保持在存储单元中。

除了DRAM和SRAM,还有其他类型的储存芯片,如闪存(Flash Memory)和硬盘驱动器等。

这些储存芯片的工作原理与DRAM和SRAM不完全相同,但通常也是基于电荷储存或磁性储存的原理。

总的来说,储存芯片的储存原理是通过物理机制将数据存储为电荷或磁性状态,来实现数据的长期保存和读取。

这种储存原理是现代计算机中常见的储存方式,它的可靠性和速度对于计算机系统的性能至关重要。

采用EEPROM工艺设计通用阵列逻辑器件——遇到的问题与解决方案深圳市国微电子股份有限公司裴国旭电可擦除只读存储器(EEPROM)工艺可广泛运用于各种消费产品中,像微控制器、无线电话、数字信号处理器、无线通讯设备以及诸如专用芯片设计等诸多应用设备中。

0.18μmEEPROM智能模块平台可广泛应用于快速增长的IC卡市场,如手机SIM卡、借记卡、信用卡、身份证、智能卡、USB钥匙以及其他需要安全认证或需时常更新和编写资料的应用设备中。

利用EEPROM工艺的可擦除,可重新编程的特点,用EEPROM单元组成阵列,通过对阵列单元的编程可实现芯片的不同逻辑功能。

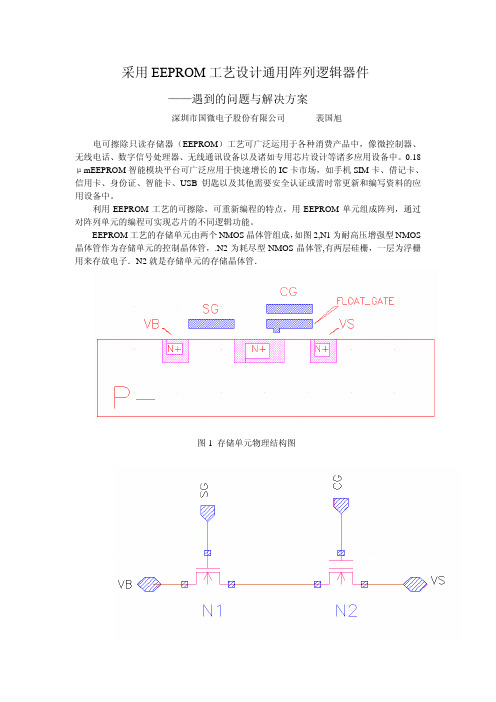

EEPROM工艺的存储单元由两个NMOS晶体管组成,如图2,N1为耐高压增强型NMOS 晶体管作为存储单元的控制晶体管,.N2为耗尽型NMOS晶体管,有两层硅栅,一层为浮栅用来存放电子.N2就是存储单元的存储晶体管.图1 存储单元物理结构图图2 存储单元电路原理图.存储单元的擦写原理(图1,图2):存储单元控制栅(CG)为16V, 存储单元选择栅(SG)为15V, 存储单元的位线端口(VB)为“0”,存储单元的源端(VS)悬空,电子由隧道窗口进入到浮栅(FLOAT_GATE)上,并保持住。

当进行读操作时,CG接“0”,由于浮栅上存有电子,N2的浮栅为负5V左右,因此关闭了耗尽型N2晶体管,达到了擦除的目的。

当CG=“0”,SG=15V,VB=16V,VS悬空时,浮栅上的电子会从隧道窗口放掉,当进行读操作时,CG 接“0”,由于浮栅上没有电子,N2的浮栅为0V左右,由于N2是耗尽型NMOS晶体管,在栅极电压为0V时也导通,达到写入目的。

在测试芯片的过程中发现可以写数据,无法擦除数据。

芯片的工作电压为5V,擦写时高压引脚(VH)输入15V电压,VH=15V信号是通过控制逻辑提供给EEPROM单元,芯片的擦除过程是把所有的EEPROM单元一次性擦除,而写入可以只写一个EEPROM单元,经过实验,只给一个EEPROM单元写“1”可以成功,将所有的EEPROM单元写“1”也可以成功。

存储器与寄存器的组成与工作原理存储器与寄存器是计算机系统中重要的组成部分,它们在数据存储和处理方面发挥着关键的作用。

本文将从存储器与寄存器的组成结构、工作原理两个方面进行介绍。

一、存储器的组成与工作原理存储器,简单来说,是用于存储和读取数据的计算机设备。

它由一系列存储单元组成,每个存储单元能够存储一定数量的数据。

根据存取方式的不同,存储器可以分为随机存储器(RAM)和只读存储器(ROM)。

1. 随机存储器(RAM)随机存储器是一种临时存储介质,具有读写功能。

它由一系列存储单元组成,每个存储单元都有一个独立的地址。

数据可以通过地址访问和存取。

随机存储器的存储单元可以分为静态随机存储器(SRAM)和动态随机存储器(DRAM)两种。

静态随机存储器(SRAM)由触发器组成,每个存储单元由6个触发器构成,能够稳定地存储数据。

它的读写速度较快,但芯片密度较低,价格较高。

动态随机存储器(DRAM)利用电容器存储数据,需要定期刷新来保持数据的有效性。

相较于SRAM,DRAM的芯片密度较高,价格也较低,但读写速度较慢。

2. 只读存储器(ROM)只读存储器是一种只能读取数据而不能写入数据的存储设备。

它通常用于存储不会改变的程序代码和固定数据。

只读存储器的存储单元由硅片上的门电路组成,数据在制造过程中被写入,不可修改。

二、寄存器的组成与工作原理寄存器是一种用于暂存和处理数据的高速存储设备。

它位于计算机的中央处理器内部,是一组用于存储指令、地址和数据的二进制单元。

寄存器的组成与存储器相比较小,但速度更快。

它由多个存储单元组成,每个存储单元能够存储一个或多个二进制位。

寄存器的位数决定了其可以存储的数据量大小。

寄存器在计算机中发挥着重要的作用,它可以用于暂存指令和数据,提高计算机的运行效率。

它还可以用于存储地址,使得计算机能够正确地访问存储器中的数据。

寄存器具有多种类型,常见的有通用寄存器、程序计数器、指令寄存器等。

通用寄存器用于存储临时数据,程序计数器用于存储下一条要执行的指令地址,指令寄存器用于存储当前正在执行的指令。

DRAM基本工作原理DRAM(Dynamic Random Access Memory)是一种常见的半导体存储器,被广泛应用于计算机系统中。

其工作原理主要包括存储单元结构、数据存取过程和刷新机制。

首先,DRAM的存储单元由一个电容和一个开关构成,电容负责存储数据,开关则决定是否读出或写入数据。

相比于SRAM(Static Random Access Memory)的存储单元结构,DRAM的存储密度更高,但读写速度较慢。

在数据存取过程中,DRAM分为读取和写入两个阶段。

首先,计算机通过地址总线将待读取或写入的数据的内存地址传输给DRAM芯片。

DRAM内部存在一组线路,它们被称为行线路和列线路。

地址总线的低位部分用于选择行线路,而高位部分则用于选择列线路。

DRAM芯片还包含了一组控制线路,用于传输控制信号。

在读取数据时,DRAM首先接收到来自地址总线的读命令。

然后,它根据行地址选择相应的行线路。

每个行线路连接到DRAM芯片上的多个存储单元,其中只有一个存储单元与所需的地址匹配。

DRAM内部会打开该存储单元的开关,从而将存储单元中的电荷传输到一个放大器中。

该放大器负责放大被读取的电荷,并输出给数据总线,供处理器使用。

在写入数据时,DRAM首先接收到来自地址总线的写命令,并将所需的数据传输到数据总线上。

DRAM执行与读取数据相同的地址选择过程,选择要写入的存储单元。

DRAM芯片的控制线路会将写命令传递给该存储单元的开关,从而将数据写入其中。

然而,DRAM还存在一个重要问题,即电容的电荷会逐渐泄漏。

因此,DRAM需要定期刷新以保持存储的数据。

刷新机制通过周期性地读取并重写内存中的数据来实现。

这一过程通常由电脑的内存控制器自动完成,以避免数据丢失。

总而言之,DRAM的基本工作原理包括存储单元结构、数据存取过程和刷新机制。

DRAM通过充电电容来存储数据,并通过开关控制读取和写入。

为了保持存储的数据,DRAM需要定期刷新。

dram 存储元存储信息的原理

DRAM(Dynamic Random Access Memory)存储元存储信息的原理是基于电容器的电荷存储。

每个存储单元由一个电容器和一个晶体管组成。

当电容器被充电时,表示存储的是1;当电容器被放电时,表示存储的是0。

DRAM的读取和写入操作都是通过电荷的传输来完成的。

在读取操作中,内存控制器向DRAM发送读取请求,DRAM将存储单元中的电荷传输到内存控制器。

在写入操作中,内存控制器向DRAM发送写入请求,DRAM将内存控制器提供的电荷存储到存储单元中。

DRAM的存储密度比较高,因为每个存储单元只需要一个电容器和一个晶体管。

然而,由于电荷存储是有限的,DRAM内存的读取速度比较慢,因为需要传输电荷。

此外,由于需要定期刷新,DRAM内存的功耗比较高。

为了提高DRAM内存的读取速度,通常会采用缓存技术。

缓存是一种高速存储器,用于存储最常用的数据。

当CPU需要访问内存时,首先会查找缓存中是否存在所需数据,如果存在,则直接从缓存中读取,否则才会从DRAM内存中读取。

以上内容仅供参考,如需更多信息,建议查阅计算机专业书籍或咨询专业人士。

NANDFLASH原理NAND FLASH 原理闪存保存数据的原理:与DRAM以电容作为存储元件不同,闪存的存储单元为三端器件,与场效应管有相同的名称:源极、漏极和栅极。

栅极与硅衬底之间有⼆氧化硅绝缘层,⽤来保护浮置栅极中的电荷不会泄漏。

采⽤这种结构,使得存储单元具有了电荷保持能⼒,就像是装进瓶⼦⾥的⽔,当你倒⼊⽔后,⽔位就⼀直保持在那⾥,直到你再次倒⼊或倒出,所以闪存具有记忆能⼒。

与场效应管⼀样,闪存也是⼀种电压控制型器件。

NAND型闪存的擦和写均是基于隧道效应,电流穿过浮置栅极与硅基层之间的绝缘层,对浮置栅极进⾏充电(写数据)或放电(擦除数据)。

⽽NOR 型闪存擦除数据仍是基于隧道效应(电流从浮置栅极到硅基层),但在写⼊数据时则是采⽤热电⼦注⼊⽅式(电流从浮置栅极到源极)。

下⾯主要介绍NAND FLASH的⼯作原理。

⼀、NAND flash的物理组成NAND Flash 的数据是以bit的⽅式保存在存储单元(memory cell),⼀般来说,⼀个单元中只能存储⼀个bit。

这些单元以8个或者16个为单位,连成bit line,形成所谓的byte(x8)/word(x16),这就是NAND Device的位宽。

这些Line会再组成页(page),以所⽤的samsumg的256M x 8 Bit K9F2G08R0A芯⽚为例:每页2112Bytes(2kbyte(Main Area)+64byte(Spare Area)),空闲区通常被⽤于ECC、耗损均衡(wear leveling)和其它软件开销功能,尽管它在物理上与其它页并没有区别。

每64个页形成⼀个块(block 128kB)。

具体⼀⽚flash上有多少个块视需要所定。

块为单位擦除数据。

按照这样的组织⽅式可以形成所谓的页为单位读写数据,⽽以块为单位擦除数据NAND flash以页为单位读写数据三类地址:Column Address:Starting Address of the Register. 翻成中⽂为列地址,地址的低8位Page Address :页地址Block Address :块地址对于NAND Flash来讲,地址和命令只能在I/O[7:0]上传递,数据宽度是8位。

存储器的工作原理一、引言存储器是计算机系统中的重要组成部份,用于存储和检索数据。

它的工作原理对于计算机的性能和功能起着至关重要的作用。

本文将详细介绍存储器的工作原理,包括存储器的组成结构、数据的存储和检索过程以及常见的存储器类型。

二、存储器的组成结构存储器主要由存储单元、地址线和数据线组成。

存储单元是存储器的最小单元,用于存储一个二进制位的数据。

地址线用于指定存储单元的地址,数据线用于传输数据。

三、数据的存储和检索过程1. 存储过程当计算机需要将数据存储到存储器中时,首先需要将数据通过数据线传输到存储器中的指定存储单元。

同时,计算机还需要通过地址线将存储单元的地址发送给存储器。

存储器根据接收到的地址,将数据存储到对应的存储单元中。

2. 检索过程当计算机需要从存储器中读取数据时,首先需要通过地址线将存储单元的地址发送给存储器。

存储器根据接收到的地址,将对应存储单元中的数据通过数据线传输给计算机。

四、常见的存储器类型1. 随机存取存储器(RAM)随机存取存储器是一种易失性存储器,它可以随机访问任意存储单元,并且读写速度较快。

RAM通常用于存储计算机运行时所需的数据和指令。

2. 只读存储器(ROM)只读存储器是一种非易失性存储器,它的数据一经写入就无法修改。

ROM中存储了计算机系统的固件和启动程序等重要信息。

3. 快取存储器(Cache)快取存储器是一种高速缓存存储器,用于加速计算机对主存储器的访问。

它通过存储最常用的数据和指令,提高了计算机的运行效率。

4. 磁盘存储器磁盘存储器是一种大容量的非易失性存储器,用于长期存储数据。

它通常用于存储操作系统、应用程序和用户数据等。

5. 光盘存储器光盘存储器是一种使用激光技术读写数据的存储器,具有较大的存储容量。

它通常用于存储音频、视频和软件等大型文件。

五、总结存储器是计算机系统中重要的组成部份,它通过存储和检索数据,为计算机的正常运行提供支持。

本文详细介绍了存储器的工作原理,包括存储器的组成结构、数据的存储和检索过程以及常见的存储器类型。