AT89S51单片机简介复习过程

- 格式:doc

- 大小:71.50 KB

- 文档页数:6

单片机第3章 AT89S51单片机的指令系统在单片机的世界里,指令系统就像是指挥单片机工作的“语言”,它决定了单片机能够完成哪些任务以及如何高效地完成这些任务。

AT89S51 单片机的指令系统丰富多样,为我们实现各种功能提供了强大的支持。

首先,让我们来了解一下指令的基本格式。

AT89S51 单片机的指令通常由操作码和操作数两部分组成。

操作码指明了要执行的操作,比如加法、减法、数据传送等;操作数则提供了操作所需的具体数据或者数据的地址。

AT89S51 单片机的指令可以分为数据传送类指令、算术运算类指令、逻辑运算类指令、控制转移类指令等几大类。

数据传送类指令是最为基础和常用的指令之一。

比如 MOV 指令,它可以实现将一个数据从一个位置传送到另一个位置。

例如 MOV A,50H ,就是将十六进制数 50H 传送到累加器 A 中。

算术运算类指令用于进行加、减、乘、除等运算。

例如 ADD A, R0 ,就是将累加器 A 的内容和寄存器 R0 的内容相加,结果存放在累加器A 中。

逻辑运算类指令则用于对数据进行与、或、异或等逻辑操作。

比如ANL A, 0FH ,就是将累加器 A 的内容和十六进制数 0FH 进行与运算。

控制转移类指令在程序的流程控制中起着关键作用。

比如JZ label ,如果累加器 A 的内容为 0 ,则程序跳转到指定的 label 处执行。

在实际编程中,我们需要根据具体的需求灵活运用这些指令。

比如,当我们要实现一个简单的加法运算时,可以使用算术运算类指令;当需要在不同的程序段之间跳转时,就需要用到控制转移类指令。

为了更好地理解和运用 AT89S51 单片机的指令系统,我们还需要了解一些指令的执行周期和寻址方式。

指令的执行周期决定了指令执行的速度。

不同的指令执行周期可能不同,这会影响程序的运行效率。

而寻址方式则决定了如何获取操作数。

AT89S51 单片机支持直接寻址、寄存器寻址、寄存器间接寻址、立即寻址等多种寻址方式。

单片机AT89S51的概述AT89S51是美国ATMEL公司生产的低功耗,高性能CMOS 8位单片机,片内含4k bytes的可系统编程的Flash只读程序存储器,器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准8051指令系统及引脚。

它集Flash程序存储器既可在线编程(ISP)也可用传统方法进行编程及通用8位微处理器于单片芯片中,ATMEL公司的功能强大,低价位AT89S51单片机可为您提供许多高性价比的应用场介,可灵活应用于各种控制领域。

主要性能参数:·与MCS-51 产品指令系统完全兼容·4k字节在线系统编程(ISP) Flash闪速存储器·1000次擦写周期·4.0---5.5V的工作电压范围·全静态工作模式:0Hz---33MHz·三级程序加密锁·128×8字节内部RAM·32个可编程I/O口线·2个16位定时/计数器·6个中断源·全双工串行UART通道·低功耗空闲和掉电模式·中断可从空闲模式唤醒系统·看门狗(WDT)及双数据指针·掉电标识和快速编程特性·灵活的在线系统编程(ISP一字节或页写模式)功能特性概述:AT89S51提供以下标准功能:4k字节Flash闪速存储器,128字节内部RAM,32个I/O口线,看门狗(WDT),两个数据指针,两个16位定时/计数器,一个5向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

同时,AT89S51可降至0Hz的静态逻辑操作,并支持两种软件可选的节电工作模式。

空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。

掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位。

引脚功能说明:·Vcc:电源电压·GND:地·P0口:P0口是一组8位漏极开路型双向I/O口,也即地址/数据总线复用口。

AT89S51单⽚机期末考试复习资料单⽚机复习资料⼀、填空题1.80C51的Po⼝作为输出端⼝时,每位能驱动 8 个SL型TTL负载。

2.当80C51引脚 ALE 信号有效时,表⽰从Po⼝稳定地送出了低8位地址。

3.⼀个机器周期等于 6 个状态周期,振荡脉冲2分频后产⽣的时钟信号的周期定义为状态周期。

4.在80C51单⽚机内部RAM中,字节地址范围是20H ~ 2FH的区域称为位寻址区,⽽字节地址范围是30H ~ 7FH的⼀段区域称为通⽤RAM区。

5.80C51系列单⽚机内部数据存储器,即内RAM中位寻址区的地址范围是 20H~2FH⼯作寄存器区的地址范围是 00H~1FH 。

内R0M中寻址区的地址范围是0000H~0FFFH 。

6.80C51有 4 个并⾏I\O⼝,其中P0~P3是准双向⼝,所以由输出转输⼊时必须先写⼊ 1 。

7.80C51串⾏接⼝有4种⼯作⽅式,这可在初始化程序中⽤软件填写特殊功能寄存器SCON 加以选择。

8.若不使⽤80C51⽚内存器引脚 EA 必须接地。

9.80C51的堆栈是软件填写堆栈指针临时在⽚内RAM 内开辟的区域。

10.80C51有4组⼯作寄存器,它们的地址范围是 00H~1FH 。

11.80C51⽚内 20H~2FH 范围内的数据存储器,既可以字节寻址⼜可以位寻址。

12.计算机的系统总线有数据总线、地址总线、控制总线。

13.80C51在物理有 4 个独⽴的存储空间。

14.程序状态标志字寄存器PSW中的PSW.7的含义是进/借位标志;PSW.0的含义是奇偶标志位。

15.通常单⽚机上电复位时PC= 0000H SP=07H,通⽤寄存器采⽤第0组,这⼀组寄存器的地址范围是从00H ~07H。

16.单⽚机的存储器设计采⽤哈佛结构,它的特点是将程序存储器空间和数据存储器空间在物理上截然分开,分别寻址。

17.单⽚机系统的复位⽅式有上电复位和⼿动按键复位两种。

18.80C51单⽚机的内部硬件结构包括了:运算器、控制器、存储器、和寄存器以及并⾏I/O⼝、串⾏⼝、中断控制系统、时钟电路、位处理器等部件,这些部件通过总线相连接。

A T89S51单片机简介

一、AT89S51单片机简介

AT89S51 为 ATMEL 所生产的可电气烧录清洗的 8051 相容单芯片,其内部程序代码容量为4KB

(一)、AT89S51主要功能列举如下:

1、为一般控制应用的 8 位单芯片

2、晶片内部具时钟振荡器(传统最高工作频率可至 12MHz)

3、内部程式存储器(ROM)为 4KB

4、内部数据存储器(RAM)为 128B

5、外部程序存储器可扩充至 64KB

6、外部数据存储器可扩充至 64KB

7、32 条双向输入输出线,且每条均可以单独做 I/O 的控制

8、5 个中断向量源

9、2 组独立的 16 位定时器Array

10、1 个全多工串行通信端口

11、8751 及 8752 单芯片具有数据

保密的功能

12、单芯片提供位逻辑运算指令

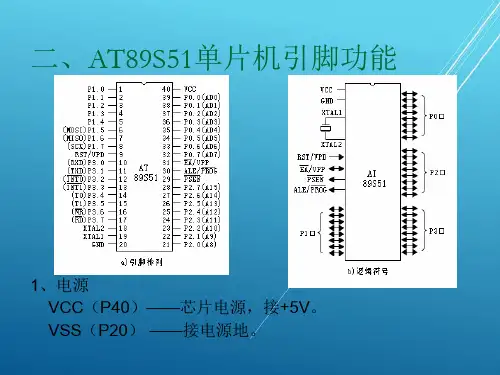

(二)、AT89S51各引脚功能介绍:

VCC:

AT89S51 电源正端输入,接+5V。

VSS:

电源地端。

XTAL1:

单芯片系统时钟的反相放大器输入端。

XTAL2:

系统时钟的反相放大器输出端,一般在设计上只要在 XTAL1 和 XTAL2 上接上一只石英振荡晶体系统就可以动作了,此外可以在两引脚与地之间加入一20PF 的小电容,可以使系统更稳定,避免噪声干扰而死机。

RESET:

AT89S51的重置引脚,高电平动作,当要对晶片重置时,只要对此引脚电平提升至高电平并保持两个机器周期以上的时间,AT89S51便能完成系统重置的各项动作,使得内部特殊功能寄存器之内容均被设成已知状态,并且至地址0000H处开始读入程序代码而执行程序。

EA/Vpp:

"EA"为英文"External Access"的缩写,表示存取外部程序代码之意,低电平动作,也就是说当此引脚接低电平后,系统会取用外部的程序代码(存于外部EPROM中)来执行程序。

因此在8031及8032中,EA引脚必须接低电平,因为其内部无程序存储器空间。

如果是使用 8751 内部程序空间时,此引脚要接成高电平。

此外,在将程序代码烧录至8751内部EPROM时,可以利用此引脚来输入21V的烧录高压(Vpp)。

ALE/PROG:

ALE是英文"Address Latch Enable"的缩写,表示地址锁存器启用信号。

AT89S51可以利用这支引脚来触发外部的8位锁存器(如74LS373),将端口0的地址总线(A0~A7)锁进锁存器中,因为AT89S51是以多工的方式送出地址及数据。

平时在程序执行时ALE引脚的输出频率约是系统工作频率的1/6,因此可以用来驱动其他周边晶片的时基输入。

此外在烧录8751程序代码时,此引脚会被当成程序规划的特殊功能来使用。

PSEN:

此为"Program Store Enable"的缩写,其意为程序储存启用,当8051被设成为读取外部程序代码工作模式时(EA=0),会送出此信号以便取得程序代码,通常这支脚是接到EPROM的OE脚。

AT89S51可以利用PSEN及RD引脚分别启用存在外部的RAM与EPROM,使得数据存储器与程序存储器可以合并在一起而共用64K的定址范围。

PORT0(P0.0~P0.7):

端口0是一个8位宽的开路汲极(Open Drain)双向输出入端口,共有8个位,P0.0表示位0,P0.1表示位1,依此类推。

其他三个I/O端口(P1、P2、

P3)则不具有此电路组态,而是内部有一提升电路,P0在当做I/O用时可以推动8个LS的TTL负载。

如果当EA引脚为低电平时(即取用外部程序代码或数据存储器),P0就以多工方式提供地址总线(A0~A7)及数据总线(D0~D7)。

设计者必须外加一锁存器将端口0送出的地址栓锁住成为A0~A7,再配合端口2所送出的A8~A15合成一完整的16位地址总线,而定址到64K的外部存储器空间。

PORT2(P2.0~P2.7):

端口2是具有内部提升电路的双向I/O端口,每一个引脚可以推动4个LS 的TTL负载,若将端口2的输出设为高电平时,此端口便能当成输入端口来使用。

P2除了当做一般I/O端口使用外,若是在AT89S51扩充外接程序存储器或数据存储器时,也提供地址总线的高字节A8~A15,这个时候P2便不能当做I/O来使用了。

PORT1(P1.0~P1.7):

端口1也是具有内部提升电路的双向I/O端口,其输出缓冲器可以推动4个LS TTL负载,同样地若将端口1的输出设为高电平,便是由此端口来输入数据。

如果是使用8052或是8032的话,P1.0又当做定时器2的外部脉冲输入脚,而P1.1可以有T2EX功能,可以做外部中断输入的触发脚位。

PORT3(P3.0~P3.7):

端口3也具有内部提升电路的双向I/O端口,其输出缓冲器可以推动4个TTL负载,同时还多工具有其他的额外特殊功能,包括串行通信、外部中断控制、计时计数控制及外部数据存储器内容的读取或写入控制等功能。

其引脚分配如下:

P3.0:RXD,串行通信输入。

P3.1:TXD,串行通信输出。

P3.2:INT0,外部中断0输入。

P3.3:INT1,外部中断1输入。

P3.4:T0,计时计数器0输入。

P3.5:T1,计时计数器1输入。

P3.6:WR:外部数据存储器的写入信号。

P3.7:RD,外部数据存储器的读取信号。