基本门电路

- 格式:ppt

- 大小:1.46 MB

- 文档页数:80

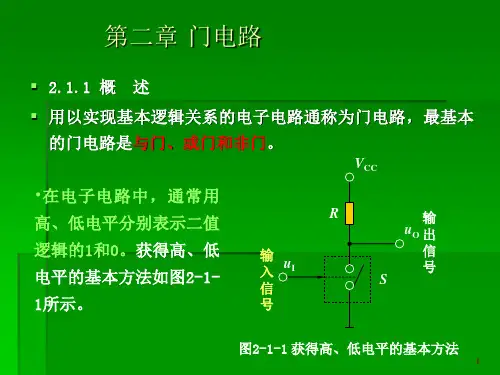

基本逻辑门电路————————————————————————————————作者:————————————————————————————————日期:第一节基本逻辑门电路1.1 门电路的概念:实现基本和常用逻辑运算的电子电路,叫逻辑门电路。

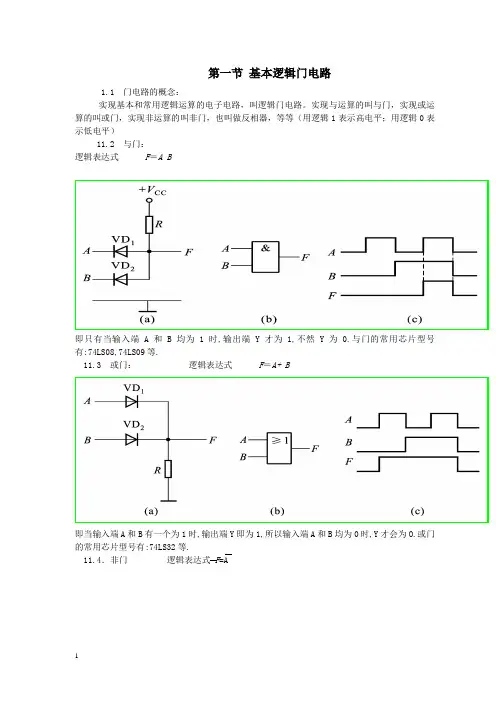

实现与运算的叫与门,实现或运算的叫或门,实现非运算的叫非门,也叫做反相器,等等(用逻辑1表示高电平;用逻辑0表示低电平)11.2 与门:逻辑表达式F=A B即只有当输入端A和B均为1时,输出端Y才为1,不然Y为0.与门的常用芯片型号有:74LS08,74LS09等.11.3 或门:逻辑表达式F=A+ B即当输入端A和B有一个为1时,输出端Y即为1,所以输入端A和B均为0时,Y才会为O.或门的常用芯片型号有:74LS32等.11.4.非门逻辑表达式F=A即输出端总是与输入端相反.非门的常用芯片型号有:74LS04,74LS05,74LS06,74LS14等.11.5.与非门 逻辑表达式 F=AB即只有当所有输入端A 和B 均为1时,输出端Y 才为0,不然Y 为1.与非门的常用芯片型号有:74LS00,74LS03,74S31,74LS132等.11.6.或非门: 逻辑表达式 F=A+B即只要输入端A 和B 中有一个为1时,输出端Y 即为0.所以输入端A 和B 均为0时,Y 才会为1.或非门常见的芯片型号有:74LS02等.11.7.同或门: 逻辑表达式F=A B+A BA F B11.8.异或门:逻辑表达式F=A B+A B=AF B11.9.与或非门:逻辑表逻辑表达式F=AB+CD AB C F D11.10.RS 触发器:电路结构把两个与非门G1、G2的输入、输出端交叉连接,即可构成基本RS 触发器,其逻辑电路如图7.2.1.(a)所示。

它有两个输入端R 、S 和两个输出端Q 、Q 。

工作原理 :基本RS 触发器的逻辑方程为:根据上述两个式子得到它的四种输入与输出的关系:1.当R=1、S=0时,则Q=0,Q=1,触发器置1。

基本门电路是由一组晶体管(或其他驱动电路)组成的简单电路,用

于处理逻辑信号。

用来实现电路中的逻辑功能,即两个输入控制一个

输出,是电子设计中最基本的电路单元,其中包括与门,非门,或和

电路,非电路等。

基本门电路通常由一个或多个晶体管和一些支持元件组成,用来将一

种电路信号(如时钟)转换为另一种(如控制信号)。

基本门电路结

构由两种晶体管组成:NPN 和 PNP 晶体管。

两种类型的晶体管都有特定的采用特定的特性,这种特性确定了驱动所需的信号电平类型,并

使栅极或集电极可用于信号输出。

基本门电路可以实现对输入信号的控制,并产生出相应的输出。

它的

基本结构可以在任何电路中使用,以控制或变换各个信号,如果要求

更大规模的逻辑电路,可以将多个门接入一个电路。

基本门电路又称为“二进制逻辑门”,因为它仅接受二进制信号。

它可

以处理简单的数字信号,或者结合其他元件来处理更复杂的数字信号。

一些基本门电路还用来处理控制信号和脉冲,这样可以控制复杂的电路,调整信号,增强信号和进行转换。

总之,基本门电路是电子设备中最主要的部分,它的大部分工作有时

不能直接见到,但却在很多高级电子系统中发挥着重要作用,并有助

于解决电子系统对控制和变换信号的问题。

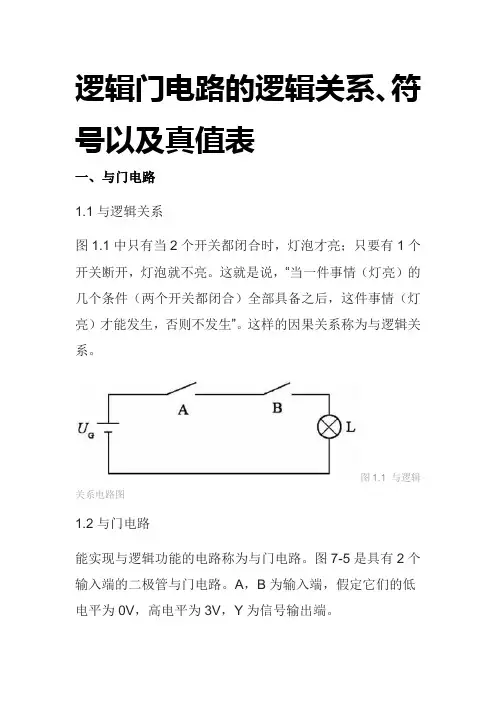

逻辑门电路的逻辑关系、符号以及真值表一、与门电路1.1与逻辑关系图1.1中只有当2个开关都闭合时,灯泡才亮;只要有1个开关断开,灯泡就不亮。

这就是说,“当一件事情(灯亮)的几个条件(两个开关都闭合)全部具备之后,这件事情(灯亮)才能发生,否则不发生”。

这样的因果关系称为与逻辑关系。

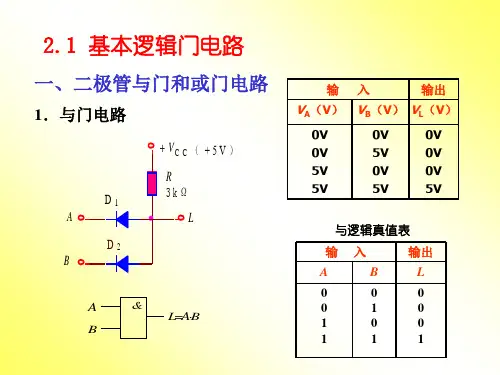

图1.1 与逻辑关系电路图1.2与门电路能实现与逻辑功能的电路称为与门电路。

图7-5是具有2个输入端的二极管与门电路。

A,B为输入端,假定它们的低电平为0V,高电平为3V,Y为信号输出端。

图1.2与门电路(1) 当A,B都处于低电平0V时,二极管VD1,VD2同时导通,Y=0V,输出低电平。

(忽略二极管的正向压降,下同)。

(2) 当A=0V,B=3V时,VD1优先导通,Y被箝位在0V,VD2反偏而截止。

(3) 当A=3V,B=0V时,VD2优先导通,Y被箝位在0V,VD1反偏而截止。

(4) 当A,B都处在高电平3V时,VD1与VD2均截止,Y 端输出高电平(即3V)。

与逻辑关系的逻辑函数表达式为Y=A*B。

表1.1是与门真值表,从真值表可以看出,与门电路的逻辑功能是“有0出0,全1出1”。

与门的逻辑符号如图1.3所示。

表1.1 与门真值表图1.3与门的逻辑符二、或门电路2.1或逻辑关系图2.1中电路由2个开关和灯泡组成。

由图可知,在决定一件事情的各种条件中,至少具备一个条件,这件事情就会发生,这种因果关系称为或逻辑关系。

图2.1 或逻辑关系电路图2.2或门电路能实现或逻辑关系的电路称为或门电路。

图2.2所示为具有2个输入端的二极管或门电路。

图2.2 或门电路真值表见表2.1,从真值表可以看出,或门的逻辑功能为“有1出1,全0出0”。

或门的逻辑符号如图2.3所示。

表2.1 或门真值表图2.3 或门逻辑符号三、非门电路(反相器)3.1非逻辑关系如图3.1开关与灯泡并联,当开关断开时,灯亮;开关闭合时,灯不亮。

这就是说,“事情(灯亮)和条件(开关)总是呈相反状态”,这种关系称为非逻辑关系。

1、基本门电路逻辑符号:1与门(And)或门(OR)非门(not)与非门(nand)或非门(nor)与或非(xor)2、Quartus II是Altera公司新一代的EDA设计工具,由该公司早先的MAXPLUSII演变而来,3、Quartus II集成开发环境的设计流程设计输入约束输入综合布局布线时序分析仿真器件编程与配置4、可编程逻辑器件PLD:低密度可编程逻辑器件(LDPLD)高密度可编程逻辑器件(HDPLD)5、EDA中文意思:电子设计自动化,由Electronic、Design、Automation。

6、HDL中文意思:硬件描述语言,由Hardware、Description、Language。

7、一个电路的HDL模块定义由:关键字module+名字开始,以endmodule结束8、一个电路的HDL模块声明由:模块名字和模块输入输出端口列表。

9、模块的端口类型有:输入端口(input)、输出端口(output)、输入/输出双向端口(inout)。

10、变量类型:wire线网型、 reg寄存器型、 memory寄存器型。

11、由持续赋值语气Assign赋值的变量必须定义:Wire类型12、在Always过程语句中被赋值变量必须定义为:reg类型13、在模块的端口声明部分如何说明总线型多位信号的位宽。

Wire[7:0] data;//说明一个8位数据总线data为wire型;Wire[31:0]adder;//说明一个32位地址总线adder为wire型。

14、wire类型变量和reg类型变量差别是什么?除了表示组合逻辑电路中的连接线,reg型变量还可以在时序电路中对应具有状态保持作用电路元件,根本区别就在于:reg型变量在定义时默认的初始值为不定值x,在设计时要求放在always过程语句内部通过过程赋值语句赋予明确的值。

如果寄存器变量没有得到新的赋值,它将一直保持原有的值不变。

15、LED数码管中分为:共阴极和共阳极。

基本门电路和中规模集成电路的基本内容一、基本门电路基本门电路是数字电路中最基本的逻辑电路,由逻辑门组成。

逻辑门是由晶体管或其他电子元件构成的电路,根据输入信号的逻辑关系产生输出信号。

常见的基本门电路有与门、或门、非门等。

1. 与门(AND Gate)与门是一种逻辑门电路,具有两个或多个输入端和一个输出端。

当所有输入端同时为高电平时,输出端才为高电平;反之,只要有一个输入端为低电平,输出端就为低电平。

与门常用符号是一个带有圆点的加号“•”,也可以用带有圆圈的字母“AND”表示。

2. 或门(OR Gate)或门是一种逻辑门电路,具有两个或多个输入端和一个输出端。

当任意一个输入端为高电平时,输出端就为高电平;只有所有输入端都为低电平时,输出端才为低电平。

或门常用符号是一个加号“+”,也可以用字母“OR”表示。

3. 非门(NOT Gate)非门是一种逻辑门电路,只有一个输入端和一个输出端。

当输入端为高电平时,输出端为低电平;当输入端为低电平时,输出端为高电平。

非门常用符号是一个小圈圈,也可以用字母“NOT”表示。

以上是最基本的三种逻辑门电路,它们可以通过组合和连接来构成更复杂的逻辑电路,实现更复杂的逻辑功能。

二、中规模集成电路中规模集成电路(Medium Scale Integrated Circuit,简称MSI)是介于小规模集成电路(SSI)和大规模集成电路(LSI)之间的一种集成电路。

MSI通常包含10到100个逻辑门电路,用于实现中等复杂的逻辑功能。

MSI的主要特点是集成度相对较高,占用空间小,功耗低,成本相对较低。

它可以实现常见的逻辑功能,如加法器、译码器、多路选择器等。

1. 加法器加法器是一种常见的中规模集成电路。

它可以实现二进制数的加法运算。

常见的加法器有半加器、全加器和并行加法器。

半加器可以对两个二进制位进行加法运算,但不考虑进位问题;全加器可以对两个二进制位和一个进位位进行加法运算;而并行加法器可以同时对多个二进制数进行加法运算。

8个基本门电路国际标

1、与门:实现逻辑“乘”运算的电路,有两个以上输入端,一个输出端(一般电路都只有一个输出端,ECL电路则有二个输出端)。

只有当所有输入端都是高电平(逻辑“1”)时,该电路输出才是高电平(逻辑“1”),否则输出为低电平(逻辑“0”)。

2、或门:实现逻辑加的电路,又称逻辑和电路,简称或门。

此电路有两个以上输入端,一个输出端。

只要有一个或几个输入端是“1”,或门的输出即为“1”。

而只有所有输入端为“0”时,输出才为“0”。

3、非门:实现逻辑代数非的功能,即输出始终和输入保持相反。

4、与非门:若当输入均为高电平1,则输出为低电平0;若输入中至少有一个为低电平0,则输出为高电平1。

与非门可以看作是与门和非门的叠加。

5、或非门:具有多端输入和单端输出的门电路。

当任一输入端(或多端)为高电平(逻辑“1”)时,输出就是低电平(逻辑“0”);只有当所有输入端都是低电平(逻辑“0”)时,输出才是高电平(逻辑“1”)。

5、EDA中文意思:电子设计自动化,由Electronic、Design、Automation。

6、HDL中文意思:硬件描述语言,由Hardware、Description、Language。

7、一个电路的HDL模块定义由:关键字module+名字开始,以endmodule结束

8、一个电路的HDL模块声明由:模块名字和模块输入输出端口。

第一节基本逻辑门电路1.1 门电路的概念:实现基本和常用逻辑运算的电子电路,叫逻辑门电路。

实现与运算的叫与门,实现或运算的叫或门,实现非运算的叫非门,也叫做反相器,等等(用逻辑1表示高电平;用逻辑0表示低电平)11.2 与门:逻辑表达式F=A B即只有当输入端A和B均为1时,输出端Y才为1,不然Y为0.与门的常用芯片型号有:74LS08,74LS09等.11.3 或门:逻辑表达式F=A+ B即当输入端A和B有一个为1时,输出端Y即为1,所以输入端A和B均为0时,Y才会为O.或门的常用芯片型号有:74LS32等.11.4.非门逻辑表达式F=A即输出端总是与输入端相反.非门的常用芯片型号有:74LS04,74LS05,74LS06,74LS14等.11.5.与非门逻辑表达式 F=AB即只有当所有输入端A和B均为1时,输出端Y才为0,不然Y为1.与非门的常用芯片型号有:74LS00,74LS03,74S31,74LS132等.11.6.或非门:逻辑表达式 F=A+B即只要输入端A和B中有一个为1时,输出端Y即为0.所以输入端A和B均为0时,Y才会为1.或非门常见的芯片型号有:74LS02等.11.7.同或门: 逻辑表达式F=A B+A BAF=1B11.8.异或门:逻辑表达式F=A B+A BFB11.9.与或非门:逻辑表逻辑表达式F=AB+CDA B C F11.10.RS 触发器:电路结构把两个与非门G1、G2的输入、输出端交叉连接,即可构成基本RS 触发器,其逻辑电路如图7.2.1.(a)所示。

它有两个输入端R 、S 和两个输出端Q 、Q 。

工作原理 :基本RS 触发器的逻辑方程为:根据上述两个式子得到它的四种输入与输出的关系:1.当R=1、S=0时,则Q=0,Q=1,触发器置1。

2.当R=0、S=1时,则Q=1,Q=0,触发器置0。

=1& ≥1如上所述,当触发器的两个输入端加入不同逻辑电平时,它的两个输出端Q和Q有两种互补的稳定状态。

第一节基本逻辑门电路1.1 门电路的概念:实现基本和常用逻辑运算的电子电路,叫逻辑门电路。

实现与运算的叫与门,实现或运算的叫或门,实现非运算的叫非门,也叫做反相器,等等(用逻辑1表示高电平;用逻辑0表示低电平)11.2 与门:逻辑表达式F=A B即只有当输入端A和B均为1时,输出端Y才为1,不然Y为0.与门的常用芯片型号有:74LS08,74LS09等.11.3 或门:逻辑表达式F=A+ B即当输入端A和B有一个为1时,输出端Y即为1,所以输入端A和B均为0时,Y才会为O.或门的常用芯片型号有:74LS32等.11.4.非门逻辑表达式F=A即输出端总是与输入端相反.非门的常用芯片型号有:74LS04,74LS05,74LS06,74LS14等.11.5.与非门逻辑表达式 F=AB即只有当所有输入端A和B均为1时,输出端Y才为0,不然Y为1.与非门的常用芯片型号有:74LS00,74LS03,74S31,74LS132等.11.6.或非门:逻辑表达式 F=A+B即只要输入端A和B中有一个为1时,输出端Y即为0.所以输入端A和B均为0时,Y才会为1.或非门常见的芯片型号有:74LS02等.11.7.同或门: 逻辑表达式F=A B+A BAFB11.8.异或门:逻辑表达式F=A B+A B=1FB11.9.与或非门:逻辑表逻辑表达式F=AB+CDABC F11.10.RS触发器:电路结构把两个与非门G1、G2的输入、输出端交叉连接,即可构成基本RS触发器,其逻辑电路如图7.2.1.(a)所示。

它有两个输入端R、S和两个输出端Q、Q。

工作原理 :基本RS触发器的逻辑方程为:根据上述两个式子得到它的四种输入与输出的关系:1.当R=1、S=0时,则Q=0,Q=1,触发器置1。

2.当R=0、S=1时,则Q=1,Q=0,触发器置0。

=1&≥1如上所述,当触发器的两个输入端加入不同逻辑电平时,它的两个输出端Q和Q有两种互补的稳定状态。

基本逻辑门电路第一节基本逻辑门电路1.1 门电路的概念:实现基本和常用逻辑运算的电子电路,叫逻辑门电路。

实现与运算的叫与门,实现或运算的叫或门,实现非运算的叫非门,也叫做反相器,等等(用逻辑1表示高电平;用逻辑0表示低电平)11.2 与门:逻辑表达式F=A B即只有当输入端A和B均为1时,输出端Y才为1,不然Y为0.与门的常用芯片型号有:74LS08,74LS09等.11.3 或门:逻辑表达式F =A+ B即当输入端A和B有一个为1时,输出端Y即为1,所以输入端A和B均为0时,Y才会为O.或门的常用芯片型号有:74LS32等.11.4.非门逻辑表达式F=A即输出端总是与输入端相反.非门的常用芯片型号有:74LS04,74LS05,74LS06,74LS14等.11.5.与非门逻辑表达式 F=ABAFB11.9.与或非门:逻辑表逻辑表达式F=AB+CD A B C FD11.10.RS 触发器:电路结构把两个与非门G1、G2的输入、输出端交叉连接,即可构成基本RS 触发器,其逻辑电路如图7.2.1.(a)所示。

它有两个输入端R 、S 和两个输出端Q 、Q 。

=1& ≥1工作原理 :基本RS触发器的逻辑方程为:根据上述两个式子得到它的四种输入与输出的关系:1.当R=1、S=0时,则Q=0,Q=1,触发器置1。

2.当R=0、S=1时,则Q=1,Q=0,触发器置0。

如上所述,当触发器的两个输入端加入不同逻辑电平时,它的两个输出端Q和Q有两种互补的稳定状态。

一般规定触发器Q端的状态作为触发器的状态。

通常称触发器处于某种状态,实际是指它的Q 端的状态。

Q=1、Q=0时,称触发器处于1态,反之触发器处于0态。

S=0,R=1使触发器置1,或称置位。

因置位的决定条件是S=0,故称S 端为置1端。

R=0,S=1时,使触发器置0,或称复位。

同理,称R端为置0端或复位端。

若触发器原来为1态,欲使之变为0态,必须令R端的电平由1变0,S端的电平由0变1。