飞思卡尔锁相环

- 格式:doc

- 大小:194.00 KB

- 文档页数:7

飞思卡尔XS128系列(一)PLL锁相环通俗点说,设置PLL锁相环就相当于超频,单片机超频的原因和PC机是一个道理。

分频的主要原因是外设需要的工作频率往往远低于CPU/MEMORY,这也和PC机南北桥的原理类似。

相对来说,PLL锁相环的设置还是比较简单的,因为东西很死,完全可以照搬。

只是大家也不要太贪,设置太高相对来说不够稳定,进行过PC机超频的应该很有体会,一般我们现在用的XS128我觉得设置在80MHz是比较合适的,相比前几届比赛用的DG128,这个频率已经蛮高的了。

还有就是SYNR,REFDV只有在CLKSEL_PLLSEL=0的情况下才能写入,不过这是系统默认状态。

多半大家可能还会有以下几点疑问:1.PLL锁相环怎么设置?答:通过写REFDV(CRG参考分频寄存器)和SYNR(CRG合成器寄存器)进行设置2.代码里while(!CRGFLG_LOCK);这句是干什么的?答:时钟校正同步3.为什么代码中会有多多少少的几句空语句?答:锁相环从设定到最后稳定还是需要一点点时间的,所以需要加几条空指令/*************************************************************************** ***********------------------------------------Code Warrior 5.0Target : MC9S12XS128Crystal: 16.000Mhz============================================本程序主要包括以下功能:设定系统工作在xxMHZ bus clock时钟下;by:庞辉**************************************************************************** *************/#include <hidef.h> /*common defines and macros*/#include <MC9S12XS128.h> /*derivative information*/#pragma LINK_INFO DERIVATIVE "mc9s12xs128"void SetBusCLK_16M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR=0x00 | 0x01; //VCOFRQ[7:6];SYNDIV[5:0]//fVCO= 2*fOSC*(SYNDIV + 1)/(REFDIV + 1)//fPLL= fVCO/(2 × POSTDIV)//fBUS= fPLL/2//VCOCLK Frequency Ranges VCOFRQ[7:6]//32MHz <= fVCO <= 48MHz 00//48MHz < fVCO <= 80MHz 01//Reserved 10//80MHz < fVCO <= 120MHz 11REFDV=0x80 | 0x01; //REFFRQ[7:6];REFDIV[5:0]//fREF=fOSC/(REFDIV + 1)//REFCLK Frequency Ranges REFFRQ[7:6]//1MHz <= fREF <= 2MHz 00//2MHz < fREF <= 6MHz 01//6MHz < fREF <= 12MHz 10//fREF > 12MHz 11//pllclock=2*osc*(1+SYNR)/(1+REFDV)=32MHz;POSTDIV=0x00; //4:0, fPLL= fVCO/(2xPOSTDIV)//If POSTDIV = $00 then fPLL is identical to fVCO (divide by one)._asm(nop); //BUS CLOCK=16M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it;CLKSEL_PLLSEL =1; //engage PLL to system;}void SetBusCLK_32M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR =0x40 | 0x03; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=64MHz; REFDV=0x80 | 0x01;POSTDIV=0x00;_asm(nop); //BUS CLOCK=32M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it;CLKSEL_PLLSEL =1; //engage PLL to system;}void SetBusCLK_40M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR =0xc0 | 0x04;REFDV=0x80 | 0x01;POSTDIV=0x00; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=80MHz;_asm(nop); //BUS CLOCK=40M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it;CLKSEL_PLLSEL =1; //engage PLL to system;}void SetBusCLK_48M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR =0xc0 | 0x05;REFDV=0x80 | 0x01;POSTDIV=0x00; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=96MHz;_asm(nop); //BUS CLOCK=48M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it;CLKSEL_PLLSEL =1; //engage PLL to system;}void SetBusCLK_64M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR =0xc0 | 0x07;REFDV=0x80 | 0x01;POSTDIV=0x00; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=128MHz; _asm(nop); //BUS CLOCK=64M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it; CLKSEL_PLLSEL =1; //engage PLL to system;}void SetBusCLK_80M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR =0xc0 | 0x09;REFDV=0x80 | 0x01;POSTDIV=0x00; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=160MHz; _asm(nop); //BUS CLOCK=80M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it; CLKSEL_PLLSEL =1; //engage PLL to system;}void SetBusCLK_88M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR =0xc0 | 0x0a;REFDV=0x80 | 0x01;POSTDIV=0x00; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=176MHz; _asm(nop); //BUS CLOCK=88M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it; CLKSEL_PLLSEL =1; //engage PLL to system;}void SetBusCLK_96M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR =0xc0 | 0x0b;REFDV=0x80 | 0x01;POSTDIV=0x00; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=192MHz; _asm(nop); //BUS CLOCK=96M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it; CLKSEL_PLLSEL =1; //engage PLL to system;}void SetBusCLK_104M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR =0xc0 | 0x0c;REFDV=0x80 | 0x01;POSTDIV=0x00; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=208MHz; _asm(nop); //BUS CLOCK=104M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it; CLKSEL_PLLSEL =1; //engage PLL to system;}void SetBusCLK_120M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR =0xc0 | 0x0d;REFDV=0x80 | 0x01;POSTDIV=0x00; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=240MHz; _asm(nop); //BUS CLOCK=120M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it; CLKSEL_PLLSEL =1; //engage PLL to system;}void main(void){EnableInterrupts;for(;;){_asm(nop);}}。

锁相环工作原理锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。

其作用是使得电路上的时钟和某一外部时钟的相位同步。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。

因此,所有板卡上各自的本地80MHz和20MHz时基的相位都是同步的,从而采样时钟也是同步的。

因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。

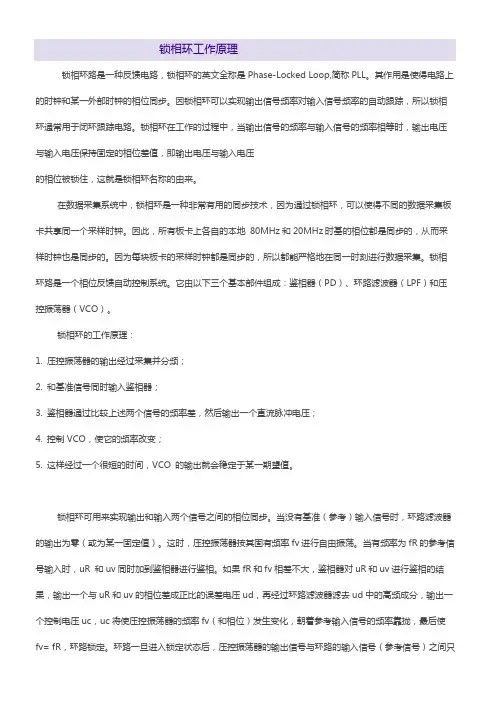

锁相环路是一个相位反馈自动控制系统。

它由以下三个基本部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。

锁相环的工作原理:1. 压控振荡器的输出经过采集并分频;2. 和基准信号同时输入鉴相器;3. 鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4. 控制VCO,使它的频率改变;5. 这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相环可用来实现输出和输入两个信号之间的相位同步。

当没有基准(参考)输入信号时,环路滤波器的输出为零(或为某一固定值)。

这时,压控振荡器按其固有频率fv进行自由振荡。

当有频率为fR的参考信号输入时,uR 和uv同时加到鉴相器进行鉴相。

如果fR和fv相差不大,鉴相器对uR和uv进行鉴相的结果,输出一个与uR和uv的相位差成正比的误差电压ud,再经过环路滤波器滤去ud中的高频成分,输出一个控制电压uc,uc将使压控振荡器的频率fv(和相位)发生变化,朝着参考输入信号的频率靠拢,最后使fv= fR,环路锁定。

环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)之间只有一个固定的稳态相位差,而没有频差存在。

锁相环(PLL)的工作原理1.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

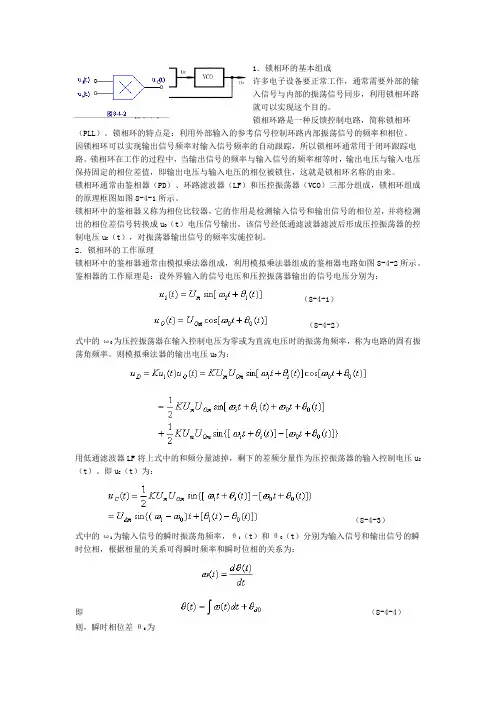

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

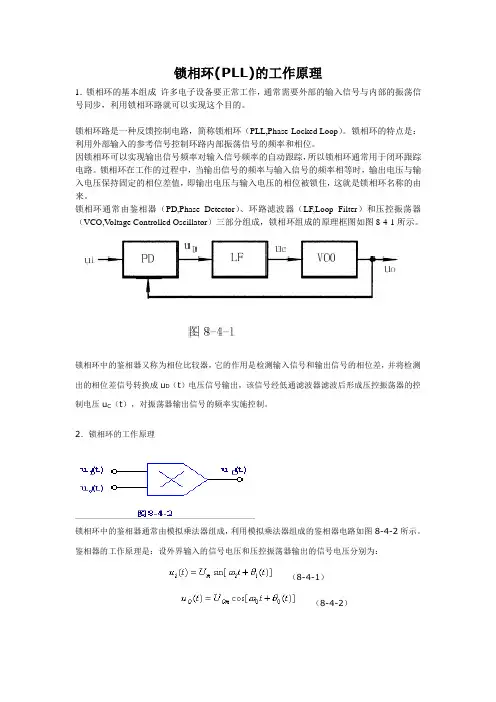

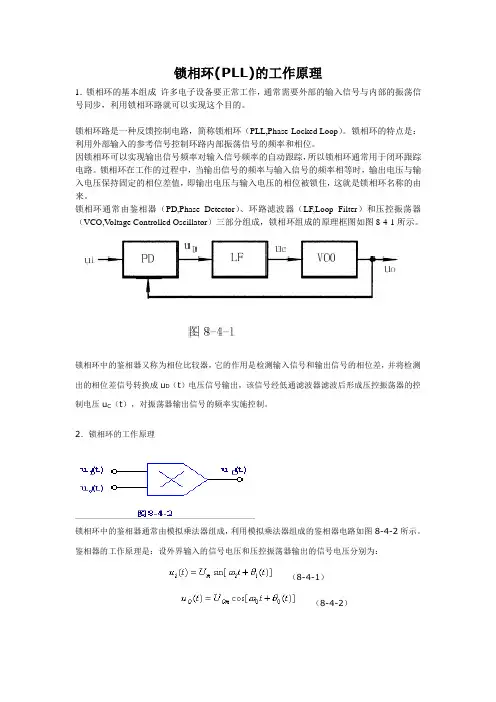

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。

即u C(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为:(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。

锁相环工作原理锁相环是一种常见的电子设备,用于调整和稳定信号的相位。

它在许多领域中都有广泛的应用,包括通信系统、雷达、无线电、光学和音频设备等。

下面将详细介绍锁相环的工作原理。

一、引言锁相环是一种反馈控制系统,它通过比较输入信号和参考信号的相位差,并根据差异来调整输出信号的相位,从而使输出信号与参考信号保持同步。

锁相环通常由相位比较器、低通滤波器、电压控制振荡器(VCO)和分频器等组成。

二、工作原理1. 相位比较器相位比较器是锁相环的核心部件之一。

它将输入信号和参考信号进行相位比较,并输出相位差。

常见的相位比较器有边沿比较器和恒幅比较器。

边沿比较器通过检测输入信号和参考信号的边沿来计算相位差,而恒幅比较器则通过比较输入信号和参考信号的幅度来计算相位差。

2. 低通滤波器相位比较器输出的相位差信号通常包含噪声和高频成份,需要经过低通滤波器进行滤波处理。

低通滤波器的作用是去除高频噪声,使得输出信号更加平滑。

3. 电压控制振荡器(VCO)VCO是锁相环中的一种振荡器,其输出频率可以通过调节输入电压来控制。

VCO的输出频率与输入电压成正比。

在锁相环中,VCO的输出频率被用作反馈信号,通过调节输入电压来实现相位的调整。

4. 分频器分频器用于将VCO的输出信号分频,以提供参考信号给相位比较器。

分频器的作用是将高频信号转换为低频信号,使得相位比较器能够更精确地进行相位比较。

三、工作流程锁相环的工作流程如下:1. 输入信号和参考信号经过相位比较器进行相位比较,得到相位差信号。

2. 相位差信号经过低通滤波器进行滤波处理,去除高频噪声。

3. 滤波后的信号作为输入电压,调节VCO的输出频率。

4. VCO的输出信号经过分频器分频后作为参考信号,再次经过相位比较器进行相位比较。

5. 反复循环上述步骤,直到输入信号和参考信号的相位差趋于稳定,锁定在一个特定的相位差值上。

6. 输出信号与参考信号保持同步,实现相位的稳定和调整。

锁相环简介:锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。

或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号中的时钟信号具有一定的相差,所以很形象地称其为锁相器。

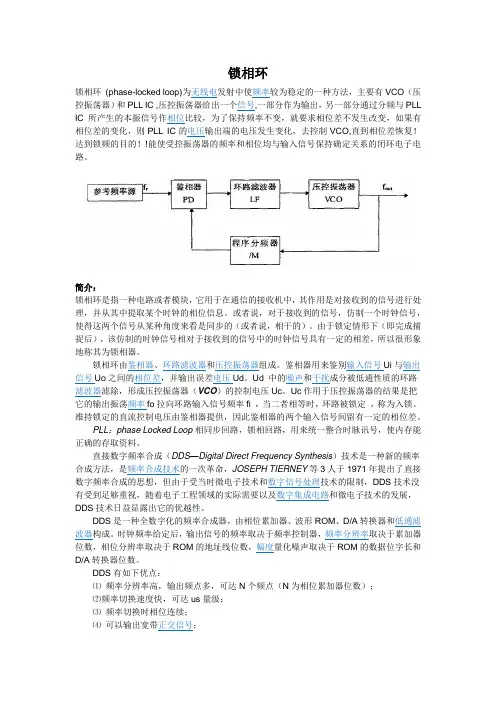

锁相环由鉴相器、环路滤波器和压控振荡器组成。

鉴相器用来鉴别输入信号Ui与输出信号Uo之间的相位差,并输出误差电压Ud。

Ud 中的噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器(VCO)的控制电压Uc。

Uc作用于压控振荡器的结果是把它的输出振荡频率fo拉向环路输入信号频率fi ,当二者相等时,环路被锁定,称为入锁。

维持锁定的直流控制电压由鉴相器提供,因此鉴相器的两个输入信号间留有一定的相位差。

PLL:phase Locked Loop 相同步回路,锁相回路,用来统一整合时脉讯号,使内存能正确的存取资料。

直接数字频率合成(DDS—Digital Direct Frequency Synthesis)技术是一种新的频率合成方法,是频率合成技术的一次革命,JOSEPH TIERNEY等3人于1971年提出了直接数字频率合成的思想,但由于受当时微电子技术和数字信号处理技术的限制,DDS技术没有受到足够重视,随着电子工程领域的实际需要以及数字集成电路和微电子技术的发展,DDS技术日益显露出它的优越性。

DDS是一种全数字化的频率合成器,由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

时钟频率给定后,输出信号的频率取决于频率控制器,频率分辨率取决于累加器位数,相位分辨率取决于ROM的地址线位数,幅度量化噪声取决于ROM的数据位字长和D/A转换器位数。

DDS有如下优点:⑴频率分辨率高,输出频点多,可达N个频点(N为相位累加器位数);⑵频率切换速度快,可达us量级;⑶频率切换时相位连续;⑷可以输出宽带正交信号;⑸输出相位噪声低,对参考频率源的相位噪声有改善作用;⑹可以产生任意波形;⑺全数字化实现,便于集成,体积小,重量轻,因此八十年代以来各国都在研制和发展各自的DDS产品,如美国QUALCOMM公司的Q2334,Q2220;STANFORD公司的STEL-1175,STEL-1180;AD公司的AD7008,AD9850,AD9854等。

锁相环的基本原理锁相环基本原理及其应用锁相环的基本原理锁相环基本原理及其应用锁相环及其应用所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL表示。

锁相环路是由鉴相器(简称PD)、环路滤波器(简称LPF或LF)和压控振荡器(简称VCO)三个部件组成闭合系统。

这是一个基本环路,其各种形式均由它变化而来PLL概念设环路输入信号v= Viomimsin(ωit+φi)环路输出信号v= Vosin(ωot+φo)——其中ωo=ωr+△ωo通过相位反馈控制,最终使相位保持同步,实现了受控频率准确跟踪基准信号频率的自动控制系统称为锁相环路。

PLL构成由鉴相器(PD)环路滤波器(LPF)压控振荡器(VCO)组成的环路。

PLL原理从捕捉过程→锁定A.捕捉过程(是失锁的)a. b.φi┈φi均是随时间变化的,经相位比较产生误差相位φe=φi-φo,也是变化的。

φe(t)由鉴相器产生误差电压v(t)=f(φde)完成相位误差—电压的变换作用。

v(t)为交流电压。

dc.v(t)经环路滤波,滤除高频分量和干扰噪声得到纯净控制电压,由VCO产生d控制角频差△ω0,使ω0随ωi变化。

B.锁定(即相位稳定)a. b.一旦锁定φe(t)=φe∞(很小常数)v(t)= V(直流电压)ddω0≡ωi输出频率恒等于输入频率(无角频差,同时控制角频差为最大△ω0max, 即ω0=ωr+△ω0max。

ωr为VCO固有振荡角频率。

)锁相基本组成和基本方程(时域)各基本组成部件鉴相器(PD)数学模式v(t)=AsinφdDe(t)相位模式环路滤波器(LPF) 数学模式v(t)=A(P) v(t)cFd相位模式压控振荡器(VCO)数学模式相位模式环路模型相位模式:指锁相环(PLL)输入相位和输出相位的反馈调节关系。

相位模型:把鉴相器,环路滤波器和压控振荡器三个部件的相位模型依次级联起来就构成锁相相位模型。

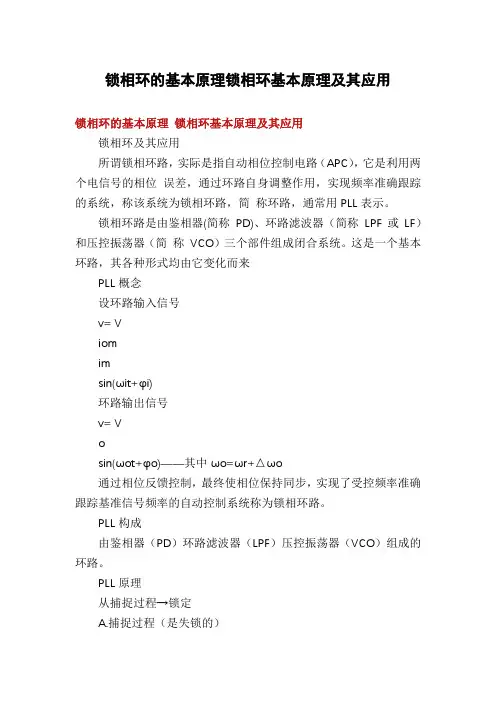

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)。

低通滤波器三部分组成,如图1所示。

压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui 与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

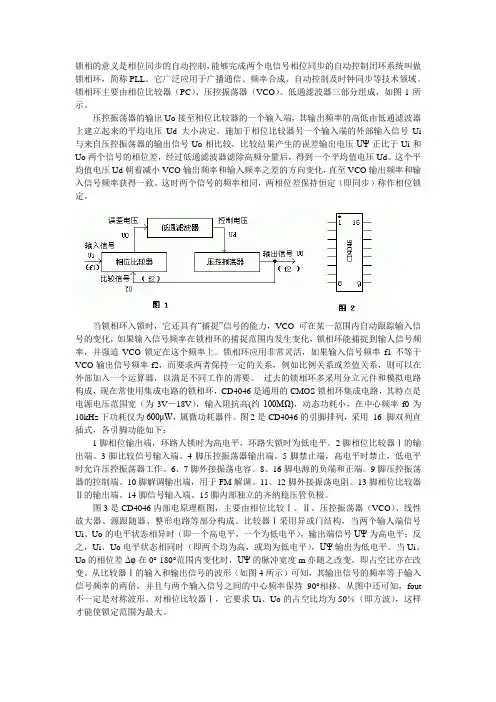

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用16 脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

锁相环原理

锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用于通信、电子设备中

的控制系统,它可以将输入信号的相位和频率锁定在特定的数值上。

锁相环由相位比较器、环路滤波器、控制电压发生器、振荡器等组成,通过这些部件的协同作用,实现了对输入信号的跟踪和控制。

下面我们将详细介绍锁相环的工作原理。

首先,锁相环的核心部件是相位比较器,它用来比较输入信号和反馈信号的相

位差,并输出一个误差信号。

这个误差信号随后被送入环路滤波器,滤波器起到平滑误差信号的作用,使得控制电压发生器的输出更加稳定。

控制电压发生器产生的电压信号会调节振荡器的频率,从而使得反馈信号的相位和频率与输入信号保持一致。

在锁相环运行过程中,当输入信号的频率发生变化时,相位比较器会检测到相

位差的变化,并产生相应的误差信号,通过环路滤波器和控制电压发生器的调节,最终使得振荡器的频率跟随输入信号的变化而变化,从而实现了频率的锁定。

同样,当输入信号的相位发生变化时,相位比较器也会产生误差信号,通过控制电压发生器调节振荡器的相位,实现相位的锁定。

除了频率和相位的锁定外,锁相环还具有频率合成、信号再生、时钟提取等功能。

通过合理设计锁相环的参数和部件,可以实现对不同频率、不同相位的信号进行跟踪和控制,从而满足各种通信和控制系统的需求。

总之,锁相环作为一种重要的控制系统,在现代通信、电子设备中得到了广泛

的应用。

它通过精密的相位比较和频率调节,实现了对输入信号的跟踪和锁定,为各种信号处理和控制提供了可靠的技术支持。

希望通过本文的介绍,读者对锁相环的工作原理有了更深入的了解。

1.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。

即u C(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。

锁相环(PLL)的工作原理1.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。

即u C(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为:(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。

锁相环锁相环,又称为锁相放大器或者锁相放大器,是一种基于反馈机制的控制系统,用于稳定和锁定两个信号的相位差。

锁相环的原理可以在许多领域中得到应用,包括通信、电子仪器、雷达等。

锁相环工作原理锁相环的核心原理是采用一个反馈环来纠正输入信号的相位差。

一般来说,锁相环由三个主要部分组成:相位比较器、低通滤波器和可变频率振荡器。

首先,锁相环将输入信号和参考信号通过相位比较器进行比较,产生一个误差信号。

相位比较器会计算两个信号之间的相位差,并且生成一个电压或电流信号,表示这个相位差。

如果输入信号和参考信号的相位差为零,那么相位比较器输出的误差信号也将为零。

接着,误差信号通过低通滤波器进行滤波处理,去除高频噪声和杂散信号。

低通滤波器可以使锁相环对于高频噪声具有良好的抑制能力,提高系统的稳定性和抗干扰性。

最后,滤波后的误差信号被送往可变频率振荡器,控制其输出的频率和相位。

可变频率振荡器会根据误差信号的大小和方向来调整输出信号的频率和相位,以减小相位差。

如果误差信号为正,则输出频率增加;如果误差信号为负,则输出频率减小。

通过不断调整输出频率和相位,锁相环可以将输入信号和参考信号的相位差保持在一个可接受的范围内。

应用领域锁相环在通信领域中有广泛的应用。

在通信系统中,锁相环可以用来确保发送和接收的信号保持同步。

例如,在无线通信中,锁相环可以用来抑制多径干扰和载波漂移,提高通信质量和稳定性。

另外,锁相环还可以用于时钟恢复和数据捕获等方面。

除了通信领域外,锁相环在电子仪器和雷达等领域也有重要的应用。

在电子仪器中,锁相环可以用来稳定和控制仪器的频率和相位。

例如,在频谱分析仪和信号发生器中,锁相环可以确保仪器输出的信号具有准确的频率和相位信息。

在雷达系统中,锁相环可以用来实现目标检测和跟踪。

通过锁相环,雷达可以准确地测量目标和干扰源之间的相对相位差,从而提高雷达测量的精度和可靠性。

总结锁相环是一种基于反馈机制的控制系统,用于稳定和锁定两个信号的相位差。

锁相环工作原理锁相环(PLL)是一种常见的控制系统,用于同步电路中的时钟和数据信号。

它的工作原理涉及到频率比较器、相位检测器、环路滤波器和振荡器等元件,通过这些元件的相互作用,锁相环可以实现信号的精准同步和稳定输出。

接下来,我们将详细介绍锁相环的工作原理。

首先,锁相环的核心部分是频率比较器,它用来比较输入信号和反馈信号的频率差异。

当两者频率不一致时,频率比较器会输出一个误差信号,这个误差信号将被送入相位检测器。

相位检测器的作用是将误差信号转换成相位差,然后送入环路滤波器。

环路滤波器用来滤除误差信号中的高频成分,同时增强低频成分,以保证锁相环的稳定性和收敛速度。

经过环路滤波器处理后的信号将被送入振荡器,振荡器的频率和相位将根据输入信号和反馈信号的比较结果进行调整,最终实现输入信号和反馈信号的同步。

除了频率比较器、相位检测器、环路滤波器和振荡器外,锁相环还包括分频器和反馈回路。

分频器用来将振荡器的输出信号分频,以生成反馈信号;反馈回路则将反馈信号送回频率比较器,形成闭环控制系统。

总的来说,锁相环的工作原理是通过不断比较输入信号和反馈信号的频率差异,将误差信号转换成相位差,经过滤波和调整后最终实现信号的同步。

它在通信、控制系统和数字信号处理等领域有着广泛的应用,能够提高系统的稳定性和抗干扰能力。

在实际应用中,锁相环的参数调节和设计是非常重要的,需要根据具体的系统要求和信号特性进行合理选择和优化。

同时,锁相环也存在一些问题,如振荡器的相位噪声、环路滤波器的稳定性等,需要在设计和实现中加以考虑和解决。

综上所述,锁相环作为一种重要的同步控制系统,在电子领域有着广泛的应用。

通过频率比较器、相位检测器、环路滤波器和振荡器等元件的相互作用,锁相环可以实现信号的精准同步和稳定输出,为各种电子设备和系统提供了可靠的时钟和数据同步功能。

锁相环基本原理1. 锁相环的基本组成锁相环主要由相位检测器、低通滤波器、振荡器(或称为VCO)、反馈路径以及参考信号等组成。

相位检测器(Phase Detector)是锁相环的核心组成部分,它将输入信号和本地参考信号进行相位比较,得出二者的相位差。

相位检测器通常分为两类:齐纳型(又称为乘法型)和延迟-环型(又称为加法型)。

其中齐纳型相位检测器在电路设计中应用较为广泛。

低通滤波器(Low Pass Filter)主要用于输出信号的平滑,也就是将振荡器产生的高频噪声滤除掉。

低通滤波器可以采用各种不同的电路形式,如RC滤波器、电感滤波器等。

振荡器(Voltage Controlled Oscillator)是产生输出信号的核心部件,它的频率和相位可以受到控制电压的影响而发生相应的改变,所以也被称为“电压控制振荡器”。

在锁相环电路中,振荡器输出的信号将被反馈到相位检测器,同时也会通过低通滤波器输出到整个系统的其它部分。

反馈路径(Feedback Path)主要负责将振荡器产生的输出信号送回到相位检测器,以便进行参考信号和输入信号的相位比较。

反馈路径通常由一些放大器、加法器、减法器、开关器等组成,既可以形成基本的积分反馈电路,也可以实现更复杂的反馈功能。

参考信号(Reference Signal)是锁相环的输入信号,它一般是由外部提供的固定频率的高精度时钟信号,也可以是从其它系统中提取出来的信号。

参考信号的精度和稳定度将直接影响到锁相环的稳定性和精度。

2. 锁相环的工作原理锁相环工作时,参考信号经过相位检测器和反馈路径后,得到的输出信号将会控制振荡器的频率和相位。

如果振荡器输出的信号与参考信号的相位相同,那么相位检测器将不会检测到相位差,在此之上,反馈路径将不再产生任何控制信号,振荡器的频率就会保持不变。

反之,如果振荡器输出的信号与参考信号的相位差存在,相位检测器会将相位差信号发送给反馈路径进行处理,反馈路径将输出一个控制信号来调整振荡器的频率和相位,以保持输出信号与参考信号同相位。

锁相环工作原理锁相环是一种常用于频率合成和时钟恢复的电路,它能够将输入信号的相位和频率与参考信号同步。

在本文中,我们将详细介绍锁相环的工作原理及其应用。

一、锁相环的基本组成部份锁相环主要由相位比较器、环路滤波器、电压控制振荡器(VCO)以及分频器组成。

1. 相位比较器(Phase Detector)相位比较器是锁相环的核心部份,其作用是将输入信号与参考信号进行相位比较,并输出一个误差信号。

常见的相位比较器有边沿比较器、乘法器和加法器等。

2. 环路滤波器(Loop Filter)环路滤波器的作用是对相位比较器输出的误差信号进行滤波和放大,以产生稳定的控制电压。

通常,环路滤波器由低通滤波器和放大器组成。

3. 电压控制振荡器(Voltage Controlled Oscillator,VCO)电压控制振荡器是一种根据输入电压的变化而改变输出频率的电路。

在锁相环中,VCO的输出频率受到环路滤波器输出的控制电压的调节。

4. 分频器(Divider)分频器将VCO的输出信号进行分频,以产生参考信号。

分频器通常使用可编程分频器,可以根据需要选择不同的分频比。

二、锁相环的工作原理锁相环的工作原理可以简单地描述为以下几个步骤:1. 初始状态锁相环的初始状态是未锁定状态,VCO的输出频率与参考信号的频率存在差异,相位比较器输出的误差信号不为零。

2. 相位比较相位比较器将输入信号与参考信号进行相位比较,产生一个误差信号。

误差信号的幅度和相位表示了输入信号与参考信号之间的差异。

3. 环路滤波误差信号经过环路滤波器进行滤波和放大,产生一个稳定的控制电压。

该控制电压的大小和极性取决于输入信号与参考信号之间的相位差。

4. 控制VCO控制电压作用于VCO,调节其输出频率。

当控制电压为正时,VCO的输出频率增加;当控制电压为负时,VCO的输出频率减小。

5. 反馈VCO的输出信号经过分频器进行分频,产生一个参考信号。

该参考信号与输入信号进行比较,形成反馈回路。

锁相环工作原理锁相环是一种常用于频率合成和时钟恢复的电路。

它通过对输入信号进行频率和相位的调整,使其与参考信号保持同步。

锁相环广泛应用于通信、雷达、测量仪器等领域。

一、基本原理锁相环由相位比较器、低通滤波器、电压控制振荡器(VCO)和分频器组成。

其工作原理如下:1. 参考信号输入:外部提供一个稳定的参考信号,作为锁相环的参考频率。

2. 相位比较:将输入信号与参考信号进行相位比较,得到相位误差信号。

3. 低通滤波:将相位误差信号经过低通滤波器滤波,得到平滑的控制电压。

4. 控制振荡器调频:将控制电压作为输入,控制电压控制振荡器的频率,实现频率的调整。

5. 分频:将控制振荡器的输出信号进行分频,得到反馈信号。

6. 反馈:将分频后的信号与输入信号进行相位比较,得到新的相位误差信号。

通过不断的相位比较、滤波和调频,锁相环可以实现输入信号与参考信号的同步。

二、工作过程锁相环的工作过程可以分为锁定和跟踪两个阶段。

1. 锁定阶段:在初始状态下,锁相环的输出与输入信号存在相位差。

相位比较器将输入信号与参考信号进行比较,得到相位误差信号。

经过低通滤波器滤波后,控制电压作用于VCO,调整其频率。

经过分频器分频后,反馈信号与输入信号再次进行相位比较,得到新的相位误差信号。

通过不断的反馈和调节,相位误差逐渐减小,最终锁定在一个稳定的值,输出信号与参考信号同步。

2. 跟踪阶段:当输入信号发生频率或者相位变化时,锁相环需要跟踪这些变化。

相位比较器检测到相位误差信号增大,低通滤波器将其平滑后,调节VCO的频率。

通过分频器反馈信号与输入信号进行相位比较,得到新的相位误差信号。

锁相环通过不断的反馈和调节,使输出信号重新与输入信号同步。

三、应用领域锁相环在许多领域中都有广泛的应用,包括但不限于以下几个方面:1. 频率合成:锁相环可以将一个稳定的参考信号与一个可调频率的振荡器相结合,生成一个具有所需频率的输出信号。

这在通信系统、雷达系统等需要精确频率合成的应用中非常重要。

锁相电路(PLL)及其应用自动相位控制(APC)电路,也称为锁相环路(PLL),它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

它是一个以相位误差为控制对象的反馈控制系统,是将参考信号与受控振荡器输出信号之间的相位进行比较,产生相位误差电压来调整受控振荡器输出信号的相位,从而使受控振荡器输出频率与参考信号频率相一致。

在两者频率相同而相位并不完全相同的情况下,两个信号之间的相位差能稳定在一个很小的范围内。

目前,锁相环路在滤波、频率综合、调制与解调、信号检测等许多技术领域获得了广泛的应用,在模拟与数字通信系统中已成为不可缺少的基本部件。

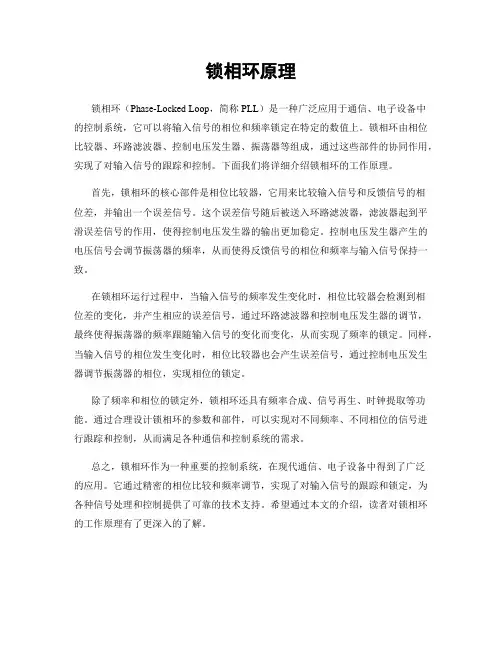

一、锁相环路的基本工作原理1.锁相环路的基本组成锁相环路主要由鉴频器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分所组成,其基本组成框图如图3-5-16所示。

图1 锁相环路的基本组成框图将图3-5-16的锁相环路与图1的自动频率控制(AFC)电路相比较,可以看出两种反馈控制的结构基本相似,它们都有低通滤波器和压控振荡器,而两者之间不同之处在于:在AFC环路中,用鉴频器作为比较部件,直接利用参考信号的频率与输出信号频率的频率误差获取控制电压实现控制。

因此,AFC系统中必定存在频率差值,没有频率差值就失去了控制信号。

所以AFC系统是一个有频差系统,剩余频差的大小取决于AFC系统的性能。

在锁相环路(PLL)系统中,用鉴相器作为比较部件,用输出信号与基准信号两者的相位进行比较。

当两者的频率相同、相位不同时,鉴相器将输出误差信号,经环路滤波器输出控制信号去控制VCO ,使其输出信号的频率与参考信号一致,而相位则相差一个预定值。

因此,锁相环路是一个无频差系统,能使VCO 的频率与基准频率完全相等,但二者间存在恒定相位差(稳态相位差),此稳态相位差经鉴相器转变为直流误差信号,通过低通滤波器去控制VCO ,使0f 与r f 同步。

2.锁相环路的捕捉与跟踪过程当锁相环路刚开始工作时,其起始时一般都处于失锁状态,由于输入到鉴相器的二路信号之间存在着相位差,鉴相器将输出误差电压来改变压控振荡器的振荡频率,使之与基准信号相一致。

备战飞思卡尔智能车大赛.开始模块总结.锁相环设置.公式: PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1),fbus=PLLCLK/2void INIT_PLL(void){CLKSEL &= 0x7f; //选用外部时钟.准备设置锁相环PLLCTL &= 0x8F; //禁止锁相环SYNR = 0xc9; //设置SYNRREFDV = 0x81; //设置REFDVPLLCTL |=0x70; //锁相环使能asm NOP; asm NOP; //两个机器周期缓冲时间while(!(CRGFLG&0x08)); //等待锁相环锁定CLKSEL |= 0x80; //设置锁相环为时钟源}飞思卡尔XS128的PLL锁相环详细设置说明——关于如何提高总线工作频率PLL锁相环就相当于超频单片机超频的原因和PC机是个一道理。

分频的主要原因是外设需要的工作频率往往远低于CPU/MEMORY这也和PC机南北桥的原理类似。

总线频率设置过程1、禁止总中断2、寄存器CLKSEL(时钟选择寄存器)的第七位置0即CLKSEL_PLLSEL=0。

选择时钟源为外部晶振OSCCLK(外接晶振频率)在PLL(锁相环)程序执行前内部总线频率为OSCCLK/23. PLLCTL_PLLON=1 打开PLL4.设置SYNR时钟合成寄存器、REFDV时钟分频寄存器、POSTDIV三个寄存器的参数5、_asm(nop) _asm(nop);加入两条空指令使锁相环稳定6、while(!(CRGFLG_LOCK==1));//时钟校正同步7、CLKSEL_PLLSEL=1; 下面详细说一下频率的计算一、时钟合成寄存器SYNR寄存器结构VCOFRQ[1:0]控制压控振动器VCO的增益默认值为00VCO的频率与VCOFRQ[1:0]对应表什么是锁相环呢?MCU的支撑电路一般需要外部时钟来给MCU提供时钟信号,而外部时钟的频率可能偏低,为了使系统更加快速稳定运行,需要提升系统所需要的时钟频率。

这就得用到锁相环了。

例如MCU用的外部晶振是16M的无源晶振,则可以通过锁相环PLL把系统时钟倍频到24M,从而给系统提供更高的时钟信号,提高程序的运行速度。

51单片机,AVR单片机内部没有锁相环电路,其系统时钟直接由外部晶振提供。

而XS128内部集成了锁相环电路,其系统时钟既可由外部晶振直接提供,也可以通过锁相环倍频后提供,当然,还有由XS128内部的时钟电路来提供(当其它来源提供的系统时钟不稳定时,内部时钟电路就起作用了,也就是自时钟模式)。

锁相环作为一个提供系统时钟的模块,是一个基本的模块,几乎每次编程序都得用到。

下面记一下怎样配置锁相环来设定想要的系统时钟。

锁相环PLL、自时钟模式和前面说的实时中断RTI、看门狗COP都属于系统时钟与复位CRG 中的模块,固前面用到的寄存器,这里有些会再用到。

在程序中配置锁相环的步骤如下:第一、禁止总中断;第二、寄存器CLKSEL的第七位置0,即CLKSEL_PLLSEL=0。

选择时钟源为外部晶振OSCCLK,在PLL程序执行前,内部总线频率为OSCCLK/2。

CLKSEL_PLLSEL=0时,系统时钟由外部晶振直接提供,系统内部总线频率=OSCCLK/2(OSCCLK 为外部晶振频率)。

CLKSEL_PLLSEL=1时,系统时钟由锁相环提供,此时系统内部总线频率=PLLCLK/2 (PLLCLK为锁相环倍频后的频率)。

第三、禁止锁相环PLL,即PLLCTL_PLLON=0。

当PLLCTL_PLLON=0时,关闭PLL电路。

当PLLCTL_PLLON=1时,打开PLL电路。

第四、根据想要的时钟频率设置SYNR和REFDV两个寄存器。

SYNR和REFDV两个寄存器专用于锁相环时钟PLLCLK的频率计算,计算公式是:PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)其中,PLLCLK为PLL模块输出的时钟频率;OSCCLK为晶振频率;SYNR、REFDV分别为寄存器SYNR、REFDV中的值。

这两个寄存器只有在PLLSEL=0时才能够写入(这里就是第二步的设置原因所在了)。

第五、打开PLL,即PLLCTL_PLLON=1。

第六、CRGFLG_LOCK位,确定PLL是否稳定。

当锁相环PLL电路输出的频率达到目标频率的足够小的误差范围内时,LOCK位置1,此时说明PLLCLK已经稳定,可以作为系统的时钟了。

该位在正常情况下为只读位。

第七、PLLCLK稳定后,允许锁相环时钟源PLLCLK为系统提供时钟,即CLKSEL_PLLSEL=1。

到这里,锁相环的设置就完毕了。

如果想更灵活地配置系统时钟,就还得用到下面的寄存器了,下面逐一说说:1、CRGFLG_LOCKIF 锁相环的中断标志位。

当系统时钟因为稳定或不稳定而导致LOCK位(上面已提到)变化时,该位置1。

此时,如果CRGINT_LOCKIE=1,则产生中断。

CRGINT_LOCKIE=1时,则允许产生锁相环锁定中断。

CRGINT_LOCKIE=0时,则不允许。

2、CLKSEL_PLLWAI是等待模式PLL停止位。

当CLKSEL_PLLWAI=1时,系统进入等待模式时,锁相环PLL停止工作。

当CLKSEL_PLLWAI=0时,系统进入等待模式时,锁相环PLL仍然工作。

下面顺便说一下与自时钟模式相关的几个寄存器:CRGFLG_SCMIF 自时钟模式中断标志位。

当SCM位变化时,该位置1。

此时,如果CRGINT_SCMIE=1,则产生中断。

CRGFLG_SCM 自时钟模式状态位。

当晶振频率不稳定时,该位置1,系统会进入自时钟模式,系统的时钟将由自时钟模式下的时钟提供。

CRGINT_SCMIE 自时钟模式中断的使能位。

当CRGINT_SCMIE=1时,允许产生自时钟模式中断。

当CRGINT_SCMIE=0时,不能产生自时钟模式中断。

PLLCTL_SCME 自时钟模式使能位。

在自时钟模式下,该位不能被清0。

PLLCTL_SCME=1时,晶振时钟失灵系统将强制进入自时钟模式。

当PLLCTL_SCME=0时,晶振失灵将导致时钟监控器复位。

下面附一条锁相环的初始化程序; void MCUInit() {DISABLE_INTERRUPTS; //(1)禁止总中断CLKSEL &= 0x7f; //(2)CLKSEL的第7位置0,选择系统时钟源为OSCCLK PLLCTL &= 0xbf; // (3)禁止PLL , PLLCTL.6(pllon)设为0;先关闭PLL SYNR = 0x01; //(4)根据需要的时钟频率设置SYNR和REFDV寄存器REFDV = 0x00; PLLCTL |= (1<<6); //(5)打开PLL , PLLCTL.6(pllon)设为1;开PLL while (( CRGFLG&0x08) == 0x00); //(6)通过判断LOCK位,//确定PLL是否稳定CLKSEL |= (1<<7); //(7)时钟频率稳定后,允许锁相环时钟源作为系统时钟源;//本句执行后:BusClock=PLLCLK/2 }什么是锁相环呢?MCU的支撑电路一般需要外部时钟来给MCU提供时钟信号,而外部时钟的频率可能偏低,为了使系统更加快速稳定运行,需要提升系统所需要的时钟频率。

这就得用到锁相环了。

例如MCU用的外部晶振是16M的无源晶振,则可以通过锁相环PLL把系统时钟倍频到24M,从而给系统提供更高的时钟信号,提高程序的运行速度。

51单片机,AVR单片机内部没有锁相环电路,其系统时钟直接由外部晶振提供。

而XS128内部集成了锁相环电路,其系统时钟既可由外部晶振直接提供,也可以通过锁相环倍频后提供,当然,还有由XS128内部的时钟电路来提供(当其它来源提供的系统时钟不稳定时,内部时钟电路就起作用了,也就是自时钟模式)。

锁相环作为一个提供系统时钟的模块,是一个基本的模块,几乎每次编程序都得用到。

下面记一下怎样配置锁相环来设定想要的系统时钟。

锁相环PLL、自时钟模式和前面说的实时中断RTI、看门狗COP都属于系统时钟与复位CRG 中的模块,固前面用到的寄存器,这里有些会再用到。

在程序中配置锁相环的步骤如下:第一、禁止总中断;第二、寄存器CLKSEL的第七位置0,即CLKSEL_PLLSEL=0。

选择时钟源为外部晶振OSCCLK,在PLL程序执行前,内部总线频率为OSCCLK/2。

CLKSEL_PLLSEL=0时,系统时钟由外部晶振直接提供,系统内部总线频率=OSCCLK/2(OSCCLK 为外部晶振频率)。

CLKSEL_PLLSEL=1时,系统时钟由锁相环提供,此时系统内部总线频率=PLLCLK/2 (PLLCLK为锁相环倍频后的频率)。

第三、禁止锁相环PLL,即PLLCTL_PLLON=0。

当PLLCTL_PLLON=0时,关闭PLL电路。

当PLLCTL_PLLON=1时,打开PLL电路。

第四、根据想要的时钟频率设置SYNR和REFDV两个寄存器。

SYNR和REFDV两个寄存器专用于锁相环时钟PLLCLK的频率计算,计算公式是:PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)其中,PLLCLK为PLL模块输出的时钟频率;OSCCLK为晶振频率;SYNR、REFDV分别为寄存器SYNR、REFDV中的值。

这两个寄存器只有在PLLSEL=0时才能够写入(这里就是第二步的设置原因所在了)。

第五、打开PLL,即PLLCTL_PLLON=1。

第六、CRGFLG_LOCK位,确定PLL是否稳定。

当锁相环PLL电路输出的频率达到目标频率的足够小的误差范围内时,LOCK位置1,此时说明PLLCLK已经稳定,可以作为系统的时钟了。

该位在正常情况下为只读位。

第七、PLLCLK稳定后,允许锁相环时钟源PLLCLK为系统提供时钟,即CLKSEL_PLLSEL=1。

到这里,锁相环的设置就完毕了。

如果想更灵活地配置系统时钟,就还得用到下面的寄存器了,下面逐一说说:1、CRGFLG_LOCKIF 锁相环的中断标志位。

当系统时钟因为稳定或不稳定而导致LOCK位(上面已提到)变化时,该位置1。

此时,如果CRGINT_LOCKIE=1,则产生中断。

CRGINT_LOCKIE=1时,则允许产生锁相环锁定中断。

CRGINT_LOCKIE=0时,则不允许。

2、CLKSEL_PLLWAI是等待模式PLL停止位。

当CLKSEL_PLLWAI=1时,系统进入等待模式时,锁相环PLL停止工作。

当CLKSEL_PLLWAI=0时,系统进入等待模式时,锁相环PLL仍然工作。