ARM7汇编指令集

- 格式:ppt

- 大小:1.66 MB

- 文档页数:146

Cortex M7 LDRH字节操作指令详解与应用随着技术的不断发展,嵌入式系统的应用范围越来越广泛。

在嵌入式系统中,对于处理器的性能和指令集的要求也越来越高。

Cortex M7处理器作为ARM在嵌入式领域的一款重要产品,其性能和功能得到了广泛的认可。

在Cortex M7的指令集中,LDRH字节操作指令是一个非常重要且常用的指令。

本文将对Cortex M7的LDRH指令进行详细的解释,并且探讨其在实际应用中的价值。

1. 什么是Cortex M7 LDRH字节操作指令?让我们先了解一下Cortex M7处理器。

Cortex M7处理器是ARM公司推出的一款32位嵌入式处理器,具有高性能、低功耗和低成本的特点,适合于广泛的嵌入式应用。

而LDRH指令则是Cortex M7处理器上的一条指令,用于从存储器中加载一个半字(16位)的数据到寄存器中。

在汇编语言中,LDRH指令的基本格式如下:```assemblyLDRH Rd, [Rn, #offset]```其中,Rd表示目标寄存器,[Rn, #offset]表示源存储器位置区域,offset表示偏移量。

通过这条指令,可以将存储器中指定位置区域的半字数据加载到目标寄存器中。

2. LDRH指令的应用场景在实际的嵌入式系统开发中,LDRH指令有着广泛的应用场景。

它可以用于处理16位数据的加载操作,适用于很多需要处理音频、图像等数据的场景。

另外,在通信协议、控制系统等领域也经常需要对16位数据进行操作,LDRH指令的使用可以简化代码结构,提高执行效率。

LDRH指令还可以用于处理16位宽的外设寄存器,如定时器、控制寄存器等,可以方便地进行数据读取和操作。

3. LDRH指令的优势与特点相比于其他方式的数据加载操作,LDRH指令有着独特的优势和特点。

它可以直接将16位的数据加载到寄存器中,无需进行额外的位移和拼接操作,简化了指令的执行流程。

LDRH指令在执行速度上有明显的优势,能够提高系统的响应速度和整体性能。

arm汇编指令作者不详,如果作者看到请与我联系...ARM指令系统特点ARM指令系统属于RISC指令系统。

标准的ARM指令每条都是32位长,有些ARM核还可以执⾏Thmub指令集,该指令集是ARM指令集的⼦集,每条指令只有16位。

1 数据类型ARM处理器⼀般⽀持下列6种数据类型:l8位有符号字节类型数据;l8位⽆符号字节类型数据;l16位有符号半字类型数据;l16位⽆符号半字类型数据;l32位有符号字类型数据;l32位⽆符号字类型数据;有些ARM处理器不⽀持半字和有符号字节数据类型。

在ARM内部,所有指令都是32操作数据。

短的数据数据类型只有在数据传送类指令中才被⽀持当1个字节数据取出后,被扩展到32位,在内部数据处理时,作为32位的什进⾏处理,并且ARM指令以字为边界。

所有Thumb指令都是16位指令时,并且以2个字节为边界。

ARM协处理器可以⽀持另外的数据类型,包括⼀套浮点数据类型,ARM的核并没有明确的⽀持。

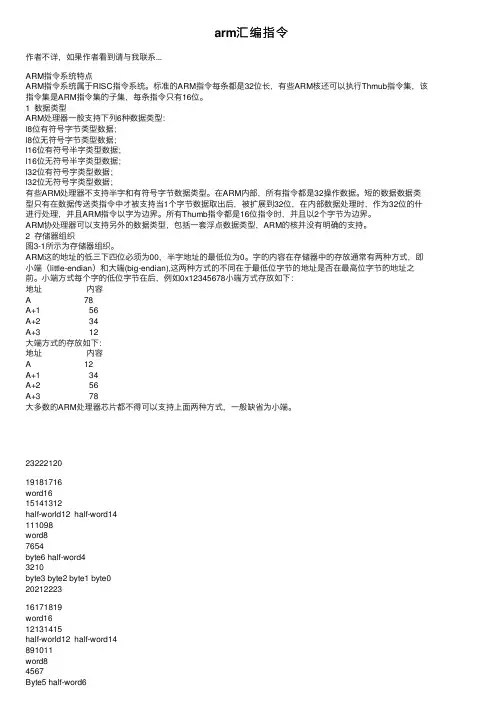

2 存储器组织图3-1所⽰为存储器组织。

ARM这的地址的低三下四位必须为00,半字地址的最低位为0。

字的内容在存储器中的存放通常有两种⽅式,即⼩端(little-endian)和⼤端(big-endian),这两种⽅式的不同在于最低位字节的地址是否在最⾼位字节的地址之前。

⼩端⽅式每个字的低位字节在后,例如0x12345678⼩端⽅式存放如下:地址内容A 78A+1 56A+2 34A+3 12⼤端⽅式的存放如下:地址内容A 12A+1 34A+2 56A+3 78⼤多数的ARM处理器芯⽚都不得可以⽀持上⾯两种⽅式,⼀般缺省为⼩端。

2322212019181716word1615141312half-world12 half-word14111098word87654byte6 half-word43210byte3 byte2 byte1 byte02021222316171819word1612131415half-world12 half-word14891011word84567Byte5 half-word6Byte0 byte1 byte2 byte3(a)⼩端存储器组织(b)⼤端存储器组织图3-1 存储器组织3 ARM指令特点1.每条指令的多功能ARM指令⼀个重要的特点是它所有的指令都带有条件,例如⽤户可以测试某个寄存器的什但是直到下次使⽤同⼀条件进⾏测试时,才能有条件的执⾏这些指令。

ARM汇编伪指令ARM条件码CPSR位[31:24]为条件位域,用f表示;位[23:16]为状态位域,用s表示;位[15:8] 为扩展位域,用x表示;位[7:0] 为控制位域,用c表示;与指令MSR相关关于移位中断向量表APCS寄存器使用约定Load and Store指令LDR R0,[R1] ;将存储器地址为R1的字数据读入寄存器R0。

LDR R0,[R1,R2] ;将存储器地址为R1+R2的字数据读入寄存器R0。

LDR R0,[R1,#8] ;将存储器地址为R1+8的字数据读入寄存器R0。

LDR R0,[R1,R2] !;将存储器地址为R1+R2的字数据读入寄存器R0,并将新地址R1+R2写入R1。

LDR R0,[R1,#8] !;将存储器地址为R1+8的字数据读入寄存器R0,并将新地址 R1+8写入R1。

LDR R0,[R1],R2 ;将存储器地址为R1的字数据读入寄存器R0,并将新地址 R1+R2写入R1。

LDR R0,[R1,R2,LSL#2]!;将存储器地址为R1+R2×4的字数据读入寄存器R0,并将新地址R1+R2×4写入R1。

LDR R0,[R1],R2,LSL#2 ;将存储器地址为R1的字数据读入寄存器R0,并将新地址R1+R2×4写入R1。

LDRB R0,[R1] ;将存储器地址为R1的字节数据读入寄存器 R0,并将R0的高24 位清零。

LDRB R0,[R1,#8] ;将存储器地址为R1+8的字节数据读入寄存器R0,并将 R0的高24位清零。

LDRH R0,[R1] ;将存储器地址为R1的半字数据读入寄存器 R0,并将R0的高16位清零。

LDRH R0,[R1,#8] ;将存储器地址为R1+8的半字数据读入寄存器R0,并将R0 的高16位清零。

LDRH R0,[R1,R2] ;将存储器地址为R1+R2的半字数据读入寄存器R0,并将 R0的高16位清零。

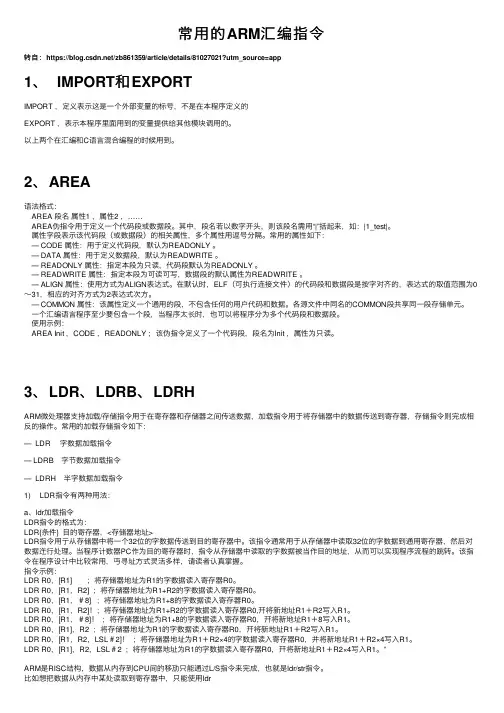

常⽤的ARM汇编指令转⾃:https:///zb861359/article/details/81027021?utm_source=app1、 IMPORT和EXPORTIMPORT ,定义表⽰这是⼀个外部变量的标号,不是在本程序定义的EXPORT ,表⽰本程序⾥⾯⽤到的变量提供给其他模块调⽤的。

以上两个在汇编和C语⾔混合编程的时候⽤到。

2、AREA语法格式:AREA 段名属性1 ,属性2 ,……AREA伪指令⽤于定义⼀个代码段或数据段。

其中,段名若以数字开头,则该段名需⽤“|”括起来,如:|1_test|。

属性字段表⽰该代码段(或数据段)的相关属性,多个属性⽤逗号分隔。

常⽤的属性如下:— CODE 属性:⽤于定义代码段,默认为READONLY 。

— DATA 属性:⽤于定义数据段,默认为READWRITE 。

— READONLY 属性:指定本段为只读,代码段默认为READONLY 。

— READWRITE 属性:指定本段为可读可写,数据段的默认属性为READWRITE 。

— ALIGN 属性:使⽤⽅式为ALIGN表达式。

在默认时,ELF(可执⾏连接⽂件)的代码段和数据段是按字对齐的,表达式的取值范围为0~31,相应的对齐⽅式为2表达式次⽅。

— COMMON 属性:该属性定义⼀个通⽤的段,不包含任何的⽤户代码和数据。

各源⽂件中同名的COMMON段共享同⼀段存储单元。

⼀个汇编语⾔程序⾄少要包含⼀个段,当程序太长时,也可以将程序分为多个代码段和数据段。

使⽤⽰例:AREA Init ,CODE ,READONLY ; 该伪指令定义了⼀个代码段,段名为Init ,属性为只读。

3、LDR、LDRB、LDRHARM微处理器⽀持加载/存储指令⽤于在寄存器和存储器之间传送数据,加载指令⽤于将存储器中的数据传送到寄存器,存储指令则完成相反的操作。

常⽤的加载存储指令如下:— LDR 字数据加载指令— LDRB 字节数据加载指令— LDRH 半字数据加载指令1) LDR指令有两种⽤法:a、ldr加载指令LDR指令的格式为:LDR{条件} ⽬的寄存器,<存储器地址>LDR指令⽤亍从存储器中将⼀个32位的字数据传送到⽬的寄存器中。

ARM7TDMI-S(Rev 4)技术参考手册第1章介绍这一章介绍ARMTDMI-S处理器包含以下小节z 关于ARM7TDMI-S 处理器z ARM7TDMI-S结构z ARM7TDMI-S模块内核和功能框图z ARM7TDMI-S指令集汇总z Rev 3a和Rev 4之间的差异1.1 关于ARM7TDMI-S处理器ARM7TDMI-S处理器是ARM通用32位微处理器家族的成员之一ARM处理器具有优异的性能但功耗却很低使用门的数量也很少ARM结构是基于精简指令集计算机(RISC)原理而设计的指令集和相关的译码机制比复杂指令集计算机要简单得多这样的简化实现了z 高的指令吞吐量z 出色的实时中断响应z 小的高性价比的处理器宏单元1.1.1指令流水线ARM7TDMI-S处理器使用流水线来增加处理器指令流的速度这样可使几个操作同时进行并使处理和存储器系统连续操作流水线使用3个阶段因此指令分3个阶段执行z 取指z 译码z 执行3阶段流水线如图1-1所示ARM ThumbPC PC 指令从存储器中取出PC-4 PC-2 对指令使用的寄存器进行译码PC-8 PC-4 从寄存器组中读出寄存器执行移位和ALU操作寄存器写回到寄存器组图1-1 指令流水线注程序计数器(PC)指向被取指的指令而不是指向正在执行的指令在正常操作过程中在执行一条指令的同时对下一条指令进行译码并将第三条指令从存储器中取出1.1.2 存储器访问ARM7TDMI-S处理器使用了冯诺依曼Von Neumann结构指令和数据共用一条32位总线只有装载存储和交换指令可以对存储器中的数据进行访问数据可以是8位字节16位半字或者32位字字必须分配为占用4字节而半字必须分配为占用2字节1.1.3 存储器接口ARM7TDMI-S处理器的存储器接口可以使潜在的性能得到实现这样减少了存储器的使用对速度有严格要求的控制信号使用流水线这样使系统控制功能以标准的低功耗逻辑实现这些控制信号使许多片内和片外存储器技术所支持的快速突发访问模式得到充分利用ARM7TDMI-S处理器的存储器周期有4种基本类型z 内部周期z 非连续的周期z 连续的周期z 协处理器寄存器传输周期1.2 ARM7TDMI-S的结构ARM7TDMI-S处理器有两个指令集z 32位ARM指令集z 16位Thumb指令集ARM7TDMI-S处理器使用了ARM结构v4T关于ARM和Thumb指令集的详细信息请参阅ARM 体系结构参考手册1.2.1 指令压缩传统的微处理器结构对于指令和数据有相同的带宽因此和16位结构相比32位结构处理32位数据具有更高的性能并且在寻址更大的地址空间时要有效得多16位结构比32位结构具有更高的代码密度并且超过32位结构50%的性能Thumb在32位结构上实现了16位的指令集这样可提供z 比16位结构更高的性能z 比32位结构更高的代码密度1.2.2 Thumb指令集Thumb指令集是最通用的ARM指令的子集Thumb指令长度为16位每条指令都对应一条32位ARM 指令它对处理器模型有相同的效果Thumb指令使用标准的ARM寄存器配置进行操作这样ARM和Thumb状态之间具有极好的互用性在执行方面Thumb具有32位内核所有的优点z 32位地址空间z 32位寄存器z 32位移位器和算术逻辑单元(ALU)z 32位存储器传输Thumb因此提供了长的分支范围强大的算术操作和巨大的地址空间Thumb代码仅为ARM代码规模的65%但其性能却相当于连接到16位存储器系统的ARM处理器性能的160%因此Thumb使ARM7TDMI-S处理器非常适用于那些只有有限的存储器带宽并且代码密度很高的嵌入式应用16位Thumb和32位ARM指令集使设计者极大的灵活性使他们可以根据各自应用的需求在子程序一级上实现对性能或者代码规模的优化例如应用中的快速中断和DSP算法可使用完全的ARM指令集编写并使用Thumb代码连接1.3 ARM7TDMI-S 模块内核和功能框图ARM7TDMI-S 处理器结构内核和功能框图见下z ARM7TDMI-S 模块见图1-2 z ARM7TDMI-S 内核见图1-3z ARM7TDMI-S 功能框图见图1-4WDATA[31:RDATA[31:图1-2 ARM7TDMI-S 模块注数据总线上没有双向路径图1-2对这些作了简化C L KC L KE N C FG B IGEND nIRQ nF IQ nRE S E T AB O R T C P CPDBG DBG TRANS[1:0]PROT[1:0]S I ZE[1:0]WRITE LOCK WDAT A[31:0]RDAT A[31:0]ADDR [31:0]态寄存器地址增加器增加器总线筒形移位器指令管线读数据寄存器图1-3 ARM7TDMI-S 内核Embe de dICE-RT图1-4 ARM7TDMI-S功能框图1.4 ARM7TDMI-S指令集汇总该节提供了ARM和Thumb指令集的汇总z ARM指令汇总z Thumb指令汇总指令集详见ARM体系结构参考手册1.5 Rev 3a和Rev 4之间的差异ARM7TDMI-S(Rev 4)的变更见下面的章节z 增加的EmbeddedICE-RT逻辑z 改进的调试通信通道(DCC)带宽z 通过JTAG对DCC进行访问z TAP控制器ID寄存器z 更加有效的多路传输1.5.1 增加的EmbeddedICE-RT逻辑EmbeddedICE-RT对ARM7TDMI-S(Rev 3)当中的EmbeddedICE逻辑作了改进EmbeddedICE-RT可以使您在监控模式下执行调试在监控模式下内核在遇到断点或观察点时执行异常处理并不像在暂停模式中那样进入调试状态如果内核在遇到断点或观察点时不进入调试状态它仍然可以像正常情况下一样响应硬件中断请求如果内核构成了机械系统反馈环的一部分那么在监控模式下进行调试非常有用因为如果停止内核会导致系统运转中断更详细的信息请查阅第5章调试您的系统节电当DBGEN被拉低时大部分的EmbeddedICE-RT逻辑都被禁止以实现最低功耗程序员模式的改变程序员模式的改变如下调试控制寄存器增加了两个新的位Bit4 监控模式使能使用该位来控制器件对断点或观察点的反应z 置位时内核执行指令或数据的异常中止z 当清零时内核进入调试状态Bit5 EmbeddedICE-RT禁止在更改观察点和断点时使用该位z 置位时该位禁止断点和观察点断点或观察点寄存器可以编程为新的值z 清零时新的断点或观察点值生效协处理器寄存器映射协处理器寄存器映射中的一个新的寄存器R2指示处理器是因为一个真实的中止还是因为断点或观察点而进入预取指或数据异常中止更详细的信息请参阅第5章的中止状态寄存器1.5.2 改进的调试通信通道(DCC)带宽在ARM7TDMI-S处理器(Rev 3)中读取DCC数据需要对扫描链2进行两次访问第一次访问状态位第二次访问数据本身为了改进DCC带宽在ARM7TDMI-S处理器(Rev 4)中读取数据和状态位只需要一次访问状态位包含在扫描链所读取的地址区域的最低位当中DCC控制寄存器中的状态位保持不变以确保向下兼容性更多信息参考第5章的调试通信通道一节1.5.3 通过JTAG访问DCCDCC控制寄存器可通过ARM7TDMI-S处理器(Rev 4)中的JTAG接口进行控制处理器写操作清零bit0数据读控制位更多信息请参考第5章的调试通信通道一节1.5.4 TAP控制器ID寄存器TAP控制器ID寄存器值为0x7F1F0F0F更多信息请参考第5章的ARM7TDMI-S器件标识(ID)代码寄存器一节第2章编程模型这一章讲述ARM7TDMI-S处理器的编程模型包含以下小节z 关于编程模型z 处理器操作状态z 存储器格式z 指令长度z 数据类型z 操作模式z 寄存器z 程序状态寄存器z 异常z 状态延迟z 复位2.1 关于编程模型ARM7TDMI-S处理器内核使用ARM v4T结构实现该结构包含32位ARM指令集和16位Thumb指令集在ARM体系结构参考手册中详细讲述了编程模型2.2 处理器操作状态ARM7TDMI-S处理器有两种操作状态ARM状态32位这种状态下执行的是字方式的ARM指令Thumb状态 16位半字方式的Thumb指令在Thumb状态中程序计数器PC使用bit1来选择切换半字注ARM和Thumb状态间的切换并不影响处理器模式或寄存器内容2.2.1 状态切换您可以使用BX指令将ARM7TDMI-S内核的操作状态在ARM状态和Thumb状态之间进行切换详见ARM体系结构参考手册所有的异常处理都在ARM状态中执行如果异常发生在Thumb状态中处理器会返回ARM状态在异常处理返回时自动切换回Thumb状态2.3 存储器格式ARM7TDMI-S处理器将存储器看作是一个从0开始的线性递增的字节集合z 字节0到3保存第1个存储的字z 字节4到7保存第2个存储的字z 字节8到11保存第3个存储的字ARM7TDMI-S处理器可以将存储器中的字以下列格式存储z 大端Big-endian格式z 小端Little-endian格式2.3.1 大端格式在大端格式中ARM7TDMI-S 处理器将最高位字节保存在最低地址字节最低位字节保存在最高地址字节因此存储器系统字节0连接到数据线3124843124231615870低地址字地址图2-1 字内字节的大端地址2.3.2 小端格式在小端格式中一个字当中最低地址的字节被看作是最低位字节最高地址字节被看作是最高位字节因此存储器系统字节0连接到数据线70如图2-2所示843124231615870低地址字地址图2-2 字内字节的小端地址2.4 指令长度指令长度为下面两种之一z 32位长度在ARM状态中z 16位长度在Thumb状态中2.5 数据类型ARM7TDMI-S处理器支持下列数据类型z 字32位z 半字16位z 字节8位您必须这样进行分配z 字量必须分配为占用4个字节z 半字量必须分配为占用2个字节z 字节量可放置在任何一个字节内2.6 操作模式ARM7TDMI-S处理器具有7种操作模式z 用户模式这是ARM程序通常执行的状态用于执行大多数应用程序z 快速中断FIQ模式支持数据传输或通道处理z 中断IRQ模式用于通用中断处理z 超级用户模式是操作系统一种受保护的模式z 中止模式在数据或指令预取指中止时进入该模式z 系统模式是操作系统一种特许的用户模式z 未定义模式当执行未定义的指令时进入该模式除了用户模式之外其它模式都被归为特权模式特权模式用于服务中断异常或者访问受保护的资源2.7 寄存器ARM7TDMI-S处理器总共有37个寄存器z 31个通用32位寄存器z 6个状态寄存器这些寄存器并不是在同一时间全都可以被访问的处理器状态和操作模式决定了程序员可以访问哪些寄存器2.7.1 ARM状态寄存器集在ARM状态中16个通用寄存器和1个或2个状态寄存器可在任何时候同时被访问在特权模式中与模式相关的分组寄存器可以被访问图2-3所示为每种模式所能访问的寄存器ARM状态寄存器集包含16个可直接访问的寄存器r0r15一个附加的寄存器当前程序状态寄存器CPSR包含条件代码标志和当前模式位寄存器r0r13为保存数据或地址值的通用寄存器寄存器r14和r15具有下面的特殊功能连接寄存器寄存器14作为一个子程序连接寄存器LR当执行连接分支BL指令时r14接收r15的备份在其它时候可将r14当成一个通用寄存器对应的分组寄存器r14_svc, r14_irq, r14_fiq, r14_abt和r14_und与之相似当发生中断和异常或者当中断或异常子程序中的BL 指令执行时用于保存r15的返回值程序计数器寄存器15用于保存程序计数器PC在ARM状态中r15中的bits[1:0]为0bits[31:2]包含PC值在Thumb状态中bit[0]为0bits[31:1]包含PC值在特权模式中另外一个寄存器被保存的程序状态寄存器SPSP可以被访问它包含了条件代码标志和作为异常的结果所保存的模式位此异常导致进入当前模式关于程序状态寄存器的描述见后面的章节分组寄存器有一个模式标识符用于指示它们被映射到哪个用户模式寄存器这些模式标识符如表2-1所示表2-1 寄存器模式标识符模式模式标识符用户 usr快速中断 fiq中断 irq超级用户 svc中止 abt系统 sys未定义 undFIQ 模式有7个分组寄存器分别映射到r8r14r8_fiqr14_fiq在ARM 状态中大多数FIQ 处理程序都不必保存任何寄存器用户IRQ 超级用户中止和未定义模式各有2个分组寄存器分别映射到r13和r14每种模式允许有一个专用的堆栈指针和LR图2-3所示为ARM状态寄存器ARM r0r1r2r3r4r5r6r7r8r9r10r11r12r13r14r15(PC)=状态通用寄存器和程序计数器系统和用户超级用户快速中断中断ARM 状态程序寄存器分组寄存器图2-3 ARM 状态中的寄存器结构2.7.2 Thumb 状态寄存器集Thumb 状态寄存器集时ARM 状态集的子集程序员可直接访问z 8个通用寄存器r0r7z PC z 堆栈指针SPz 连接寄存器LRz CPSR每个特权模式都有分组的SPLR 和SPSR该寄存器集如图2-4所示r0r1r2r3r4r5r6r7SP LR PC=状态通用寄存器和程序计数器系统和用户Thumb 状态程序寄存器分组寄存器Thumb图2-4 Thumb 状态中的寄存器结构2.7.3 ARM 状态寄存器和Thumb 状态寄存器之间的关系Thumb 状态寄存器与ARM 状态寄存器有如下的关系z Thumb 状态r0r7与ARM 状态r0r7相同z Thumb 状态CPSR 和SPSR 与ARM 状态CPSR 和SPSR 相同 z Thumb 状态SP 映射到ARM 状态r13 z Thumb 状态LR 映射到ARM 状态r14 z Thumb 状态PC 映射到ARM 状态PC(r15) 这些关系如图2-5所示图2-5 Thumb 寄存器在ARM 状态寄存器上的映射注寄存器r0r7为低寄存器寄存器r8r15为高寄存器2.7.4 在Thumb 状态中访问高寄存器在Thumb 状态中高寄存器r8r15不是标准寄存器集的一部分汇编语言程序员对它们的访问受到限制但可以将它们用于快速暂存可以使用MOV 指令的特殊变量将一个值从低寄存器r0r7转移到高寄存器或者从高寄存器到低寄存器CMP指令可用于比较高寄存器和低寄存器的值ADD 指令可用于将高寄存器的值与低寄存器的值相加详细信息请参考ARM体系结构参考手册2.8 程序状态寄存器ARM7TDMI-S 内核包含1个CPSR 和5个SPSR 供异常处理程序使用程序状态寄存器z 保持条件代码标志 z 控制中断的使能和禁止 z 设置处理器操作模式 位的分配如图2-6所示图2-6 程序状态寄存器格式注为了保持与将来的ARM 处理器兼容并且作为一种良好的习惯在更改CPSR 时我们强烈建议您使用读写修改的方法2.8.1 条件代码标志N, Z, C 和V 位都是条件代码标志可以通过算术和逻辑操作来设置这些位这些标志还可通过MSR和LDM 指令进行设置ARM7TDMI-S 处理器对这些位进行测试以决定是否执行一条指令在ARM 状态中所有指令都可按条件来执行在Thumb 状态中只有分支指令可条件执行更详细的信息请参考ARM 体系结构参考手册2.8.2 控制位PSR 的最低8位为控制位它们分别是z 中断禁止位 z T 位 z 模式位 当发生异常时控制位改变当处理器在一个特权模式下操作时可用软件操作这些位中断禁止位I 和F 位都是中断禁止位z 当I 位置位时IRQ 中断被禁止 z 当F 位置位时FIQ 中断被禁止T位T位反映了正在操作的状态z 当T位置位时处理器正在Thumb状态下运行z 当T位清零时处理器正在ARM状态下运行操作状态通过CPTBIT外部信号反映警告绝对不要强制改变CPSR寄存器中的T位如果这样做处理器会进入一个无法预知的状态模式位M4, M3, M2, M1和M0位M[4:0]都是模式位这些位决定处理器的操作模式见表2-2不是所有模式位的组合都定义了有效的处理器模式因此请小心不要使用表中所没有列出的组合表2-2 PSR模式位值M[4:0] 模式可见的Thumb状态寄存器可见的ARM状态寄存器10000 用户r0~r7, SP, LR, PC, CPSR r0~r14,PC, CPSR10001 FIQ r0~r7,SP_fiq,LR_fiq,PC,CPSR, SPSR_fiq r0~r7,r8_fiq~r14_fiq,PC,CPSR, SPSR_fiq 10010 IRQ r0~r7,SP_irq,LR_irq,PC,CPSR,SPSR_fiqr0~r12,r13_irq,r14_irq,PC,CPSR,SPSR_irq10011 超级用户 r0~r7,SP_svc,LR_svc,PC,CPSR,SPSR_svc r0~r12,r13_svc,r14_svc,PC,CPSR, SPSR_svc10111 中止 r0~r7,SP_abt,LR_abt,PC,CPSR,SPSR_abtr0~r12,r13_abt,r14_abt,PC,CPSR,SPSR_abt11011 未定义 r0~r7,SP_und,LR_und,PC,CPSR,SPSR_und r0~r12,r13_und,r14_und,PC,CPSR, SPSR_und11111 系统 r0~r7,SP,LR,PC,CPSR注如果将非法值写入M[4:0]中处理器将进入一个无法恢复的模式2.8.3 保留位PSR中的保留位被保留将来使用当改变PSR标志和控制位时请确认没有改变这些保留位另外请确保您的程序不依赖于包含特定值的保留位因为将来的处理器可能会将这些位设置为1或者02.9 异常只要正常的程序流被暂时中止处理器就进入异常模式例如响应一个来自外设的中断在处理异常之前ARM7TDMI-S内核保存当前的处理器状态这样当处理程序结束时可以恢复执行原来的程序如果同时发生两个或更多异常那么将按照固定的顺序来处理异常见异常优先级一节该节将会详细讲述ARM7TDMI-S处理器的异常处理z 异常入口/出口汇总z 进入异常z 退出异常2.9.1 异常入口/出口汇总表2-3所示为异常入口处变量r14所保存的PC值以及退出异常处理程序所推荐使用的指令表2-3 异常入口/出口异常或入口 返回指令 之前的状态ARM r14_x Thumb r14_x 备注BL MOV PC,R14PC+4PC+2 SWIMOVS PC,R14_svcPC+4 PC+2未定义的指令 MOVS PC,R14_und PC+4PC+2 预取指中止 SUBS PC,R14_abt,#4 PC+4 PC+4 此处PC 为BL, SWI, 未定义的指令取指或者预取中止指令的地址 FIQ SUBS PC,R14_fiq,#4 PC+4PC+4 IRQSUBS PC,R14_irq,#4 PC+4 PC+4 此处PC 为由于FIQ 或IRQ 占先而没有被执行的指令的地址数据中止SUBS PC,R14_abt,#4 PC+8PC+8此处PC 为产生数据中止的装载或保存指令的地址复位无复位时保存在r14_svc 中的值不可预知2.9.2 进入异常当处理异常时ARM7TDMI-S 内核会1.在适当的LR 中保存下一条指令的地址当异常入口来自ARM 状态ARM7TDMI-S 将下一条指令的地址复制到LR 中当前PC+4或PC+8取决于异常的类型Thumb状态ARM7TDMI-S 将PC 加偏移值PC+4或PC+8取决于异常的类型写入LR当进入异常时异常处理程序不必确定状态例如在SWI 情况下MOVS PC,r14_svc 总是返回到下一条指令而不管SWI 是在ARM 还是在Thumb 状态下执行2. 将CPSR 复制到适当的SPSR3. 根据异常将CPSR 模式强制设为某一值4. 强制PC 从相关的异常向量处对下一条指令取指ARM7TDMI-S 内核在中断异常时置位中断禁止标志这样可防止不受控制的异常嵌套注异常总是在ARM 状态中进行处理当处理器处于Thumb 状态时发生了异常在异常向量地址装入PC 时会自动切换到ARM 状态2.9.3 退出异常当异常结束时异常处理程序必须1. 将LR 中的值减去偏移量后移入PC 偏移量根据异常的类型而有所不同见表2-32. 将SPSR 的值复制回CPSR3. 清零在入口置位的中断禁止标志注恢复CPSR 的动作会将T, F 和I 位自动恢复为异常发生前的值2.9.4 快速中断请求快速中断请求(FIQ)异常支持数据转移或通道处理在ARM 状态中FIQ 模式有8个专用的寄存器可用来满足寄存器保护的需要这是上下文切换的最小开销将nFIQ 信号拉低可实现外部产生FIQ不管异常入口是来自ARM 状态还是Thumb 状态FIQ 处理程序都会通过执行下面的指令从中断返回 SUBS PC,R14_fiq,#4在一个特权模式中可通过置位CPSR 中的F 标志来禁止FIQ 异常当F 标志清零时ARM7TDMI-S 在每条指令结束时检测FIQ 同步器输出端的低电平2.9.5 中断请求中断请求IRQ异常是一个由nIRQ输入端的低电平所产生的正常中断IRQ的优先级低于FIQ对于FIQ序列它是被屏蔽的任何时候在一个特权模式下都可通过置位CPSR中的I 位来禁止IRQ,不管异常入口是来自ARM状态还是Thumb状态IRQ处理程序都会通过执行下面的指令从中断返回SUBS PC,R14_irq,#42.9.6 中止中止表示当前存储器访问不能被完成这是通过外部ABORT输入指示的不管异常入口是来自ARM 状态还是Thumb状态FIQ处理程序都会通过执行下面的指令从中断返回SUBS PC,R14_fiq,#4在存储器访问周期结束时检测中止异常有两种类型的中止z 预取指中止发生在指令预取指过程中z 数据中止发生在对数据访问时预取指中止当发生预取指中止时ARM7TDMI-S内核将预取的指令标记为无效但在指令到达流水线的执行阶段时才进入异常如果指令在流水线中因为发生分支而没有被执行中止将不会发生在处理中止的原因之后不管处于哪种处理器操作状态处理程序都会执行下面的指令SUBS PC,R14_abt,#4这个动作恢复了PC和CPSR并重试被中止的指令数据中止当发生数据中止时根据指令的类型产生不同的动作z 数据转移指令LDR,STR回写到被修改的基址寄存器中止处理程序必须注意这一点z 交还指令SWP中止好像没有被执行过一样中止必须发生在SWP指令进行读访问时z 块数据转移指令LDM,STM完成当回写被设置时基址寄存器被更新在指示出现中止后ARM7TDMI-S内核防止所有寄存器被覆盖这意味着ARM7TDMI-S内核总是会保护被中止的LDM指令中的r15总是最后一个被转移的寄存器中止的机制使指令分页的虚拟存储器系统能够被实现在这样一个系统中处理器允许产生仲裁地址当某一地址的数据无法访问时存储器管理单元MMU通知产生了中止中止处理程序必须找出中止的原因使请求的数据可以被访问并重新执行被中止的指令应用程序不必知道可用存储器的数量也不必知道它的被中止时所处的状态在修复产生中止的原因后不管处于哪种处理器操作状态处理程序都必须执行下面的返回指令SUBS PC,R14_abt,#8这个动作恢复了PC和CPSR并重试被中止的指令2.9.7 软件中断指令软件中断(SWI)用于进入超级用户模式通常用于请求一个特定的超级用户函数SWI处理程序通过执行下面的指令返回MOVS PC,R14_svc这个动作恢复了PC和CPSR并返回到SWI之后的指令SWI处理程序读取操作码以提取SWI函数编号2.9.8 未定义的指令当ARM7TDMI-S处理器遇到一条系统内任何协处理器都无法处理的指令时ARM7TDMI-S内核执行未定义指令陷阱软件可使用这一机制通过仿真未定义的协处理器指令来扩展ARM指令集注ARM7TDMI-S处理器完全遵循ARM结构v4T可以捕获所有分类未被定义的指令位格式在防止失败的指令后捕获处理器执行下面的指令MOVS PC,R14_und这个动作恢复了PC和CPSR并返回到未定义指令之后的指令关于未定义指令更详细的信息请参考ARM体系结构参考手册2.9.9 异常向量表2-4所示位异常向量地址在表中I和F表示先前的值表2-4 异常向量地址异常进入时的模式进入时I的状态进入时F的状态0x00000000 复位超级用户禁止禁止0x00000004 未定义指令未定义 I F 0x00000008 软件中断超级用户禁止 F 0x0000000C 中止预取指中止 I F 0x00000010 中止数据中止 I F 0x00000014 保留保留0x00000018 IRQ IRQ 禁止 F 0x0000001C FIQ FIQ 禁止禁止2.9.10 异常优先级当多个异常同时发生时一个固定的优先级系统决定它们被处理的顺序1. 复位最高优先级2. 数据中止3. FIQ4. IRQ5. 预取指中止6. 未定义指令7. SWI最低优先级有些异常不能一起发生z 未定义的指令和SWI异常互斥它们分别对应于当前指令的一个特定非重叠译码z 当FIQ使能并且在发生FIQ的同时产生了一个数据中止ARM7TDMI-S内核进入数据中止处理程序然后立即转到FIQ向量从FIQ的正常返回使数据中止处理程序恢复执行数据中止的优先级必须高于FIQ以确保数据转移错误不会被漏过必须将异常入口的时间增加到系统中最坏情况下FIQ的延迟时间2.10 中断延迟中断延迟被描述为z 最大中断延迟z 最小中断延迟2.10.1 最大中断延迟当FIQ使能时最坏情况下FIQ的延迟时间包含z Tsyncmax请求通过同步器的最长时间Tsyncmax为2个处理器周期z Tldm最长的指令执行需要的时间最长的指令是装载包括PC在内所有寄存器的LDM指令Tldm在零等待状态系统中的执行时间为20个周期z Texc数据中止入口的时间Texc为3个周期z Tfiq FIQ入口的时间Tfiq为2个周期因此总的延迟时间为27个周期在系统使用40MHz处理器时钟时略微小于0.7微妙在此时间结束后ARM7TDMI-S执行位于0x1c处的指令最大的IRQ延迟时间与之相似但必须考虑到这样一个事实即有更高优先级的FIQ可能会因为仲裁的时间而延迟IRQ处理程序的进入2.10.2 最小中断延迟最小中断延迟FIQ或IRQ的最小中断延迟是请求通过同步器的时间Tsyncmin加上Tfiq4个处理器周期2.11 复位当nRESET信号被拉低时ARM7TDMI-S处理器放弃正在执行的指令当nRESET信号再次变为高电平时nRESET处理器1. 强制M[4:0]变为b10011超级用户模式2. 置位CPSR中的I和F位3. 清零CPSR中的T位4. 强制PC从地址0x00开始对下一条指令进行取指5. 返回到ARM状态并恢复执行在复位后除PC和CPSR之外的所有寄存器的值都不确定。

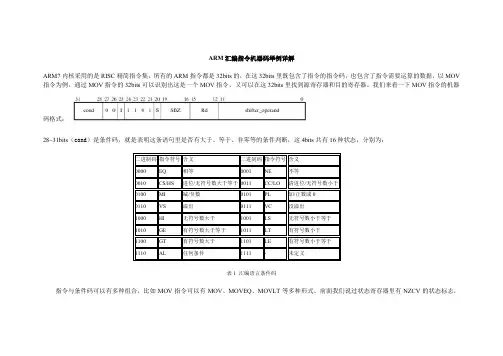

ARM汇编指令机器码举例详解

ARM7内核采用的是RISC精简指令集,所有的ARM指令都是32bits的,在这32bits里既包含了指令的指令码,也包含了指令需要运算的数据,以MOV 指令为例,通过MOV指令的32bits可以识别出这是一个MOV指令,又可以在这32bits里找到源寄存器和目的寄存器。

我们来看一下MOV指令的机器

码格式:

28~31bits(cond)是条件码,就是表明这条语句里是否有大于、等于、非零等的条件判断,这4bits共有16种状态,分别为:

表 1 汇编语言条件码

指令与条件码可以有多种组合,比如MOV指令可以有MOV、MOVEQ、MOVLT等多种形式。

前面我们说过状态寄存器里有NZCV的状态标志,

当执行一条指令时,芯片就会将这条指令的条件码与状态寄存器中的状态标志做比较,如果状态寄存器中的状态标志满足这条指令的条件码时,则执行这条语句,如果不满足则不执行这条指令。

状态寄存器中的状态标志是受某些指令影响的,因此在使用有条件码的

指令进行判断前,必然会有其它指令配合使用,先修改状态寄存器中的状态标志。

ARM指令集和汇编语言程序姓名:何瑞平学号:201120928专业:电路与系统本章主要介绍以下内容:一、ARM寻址方式包含9种:立即数寻址寄存器寻址寄存器移位寻址寄存器间接寻址基址变址寻址相对寻址多寄存器寻址块拷贝寻址堆栈寻址寻址空间:51系列是16位地址总线,寻址空间为:215 。

ARM系列为32位地址总线,寻址空间为:2311.1立即数寻址在立即数寻址中,操作数本身直接在指令中给出,取出指令也就获得了操作数,这个操作数也称为立即数。

例:ADD R0,R1,#5;R0=R1+5MOV R0,#0x55;R0=0x55其中:操作数5,0x55就是立即数,立即数在指令中要以“#”为前缀,后面跟实际数值。

十进制立即数表达举例:#0005、#01234;十六进制立即数表达举例:#0x0005、#0x0FFFF;1.2寄存器寻址在寄存器寻址方式下,寄存器的值即为操作数,寄存器本身就是操作数地址。

在51系列单片机中,可寻址的寄存器是当前工作寄存器R0~R7,A、B和DPTR。

在ARM系列的任一个模式,都有R0~R14、PC、CPSR。

例:ADD R0,R1,R2 ;R0=R1+R2MOV R0,R1 ; R0=R11.3寄存器移位寻址寄存器移位寻址是ARM 特有的寻址方式,其操作数由寄存器的数值做相应移位而得到。

移位的方式在指令中以助记符的形式给出,而移位的位数可用立即数或寄存器寻址方式表示。

例:ADD R0,R1,R2,ROR #5;R0=R1+R2循环右移5位 MOV R0,R1,LSL R3;R0=R1逻辑左移R3位移位操作在ARM 指令集中不作为单独的指令使用,ARM 指令集共有5种位移操作。

1.4 ARM 指令集的5种位移操作1.4.1 LSL (Logical Shift Lef )逻辑左移 :向左移位,左侧移出的位丢失;右端空出位补0;注:最后一个左移出的位存放于状态寄存器CPSR 的C 位中。

ARM指令集详解ARM可以用两套指令集:ARM指令集和Thumb指令集。

本文介绍ARM指令集。

在介绍ARM指令集之前,先介绍指令的格式。

1 指令格式(1)基本格式<opcode>{<cond>}{S} <Rd>,<Rn>{,<opcode2>}其中,<>内的项是必须的,{}内的项是可选的,如<opcode>是指令助记符,是必须的,而{<cond>}为指令执行条件,是可选的,如果不写则使用默认条件AL(无条件执行)。

opcode 指令助记符,如LDR,STR 等cond 执行条件,如EQ,NE 等S 是否影响CPSR 寄存器的值,书写时影响CPSR,否则不影响Rd 目标寄存器Rn 第一个操作数的寄存器operand2 第二个操作数指令格式举例如下:LDR R0,[R1] ;读取R1 地址上的存储器单元内容,执行条件ALBEQ DATAEVEN ;跳转指令,执行条件EQ,即相等跳转到DATAEVENADDS R1,R1,#1 ;加法指令,R1+1=R1 影响CPSR 寄存器,带有SSUBNES R1,R1,#0xD;条件执行减法运算(NE),R1-0xD=>R1,影响CPSR 寄存器,带有S(2)第2个操作数在ARM 指令中,灵活的使用第2个操作数能提高代码效率,第2个操作数的形式如下:#immed_8r常数表达式,该常数必须对应8 位位图,即常数是由一个8 位的常数循环移位偶数位得到。

合法常量0x3FC、0、0xF0000000、200、0xF0000001等都是合法常量。

非法常量0x1FE、511、0xFFFF、0x1010、0xF0000010等都是非法常量。

常数表达式应用举例如下:MOV R0,#1 ;R0=1AND R1,R2,#0x0F ;R2 与0x0F,结果保存在R1LDR R0,[R1],#-4 ;读取R1 地址上的存储器单元内容,且R1=R1-4Rm寄存器方式,在寄存器方式下操作数即为寄存器的数值。

1 ARM指令英文全称及功能描述V2.0作者:满光明2019年4月9日转载请支持原创,保留此页信息,否则将追究责任前言我在工作前买了一本关于ARM指令的书籍,当时出于方便记忆理解的考量,整理了ARM指令,并且加入了英文的全称。

了解了英文的全称,能够好的帮助记忆和理解。

百度网盘里分享出来的ARM 指令英文全称我看了一下都是我当年整理的版本,但他们把作者的名字去掉了。

几年过去了,ARM技术取得了巨大的进步,ARM以其低功耗、低成本、高性能的优势抢占了移动市场。

相信在不远的未来,ARM会普遍运行在个人电脑和服务器上。

在可穿戴、边缘计算等前沿领域ARM拥有无与伦比的优势。

作为一个技术控,工作以来我一直从事ARM相关的开发工作,计算机领域需要学习的东西太多,但很多基础知识都是相通的。

我也希望能把自己这么多年的技术积累拿出来分享给即将走上硬件开发、底层驱动开发的同仁们本篇仍然以介绍ARM架构以及ARM指令为主,在原来的基础上重新调整了指令顺序,首先介绍ARM 架构不同版本的区别,进而引出基本指令结构,最后详细列出所有指令详表,增强可读性,易于理解。

2一、ARM指令集版本历史计算机完成一定的操作通过指令来实现,不同的指令方式被称为计算机架构,目前计算机主要有两大架构阵营,一是CISC (Complex Instruction Set Computers)复杂指令集架构,另一种是RISC(Reduced Instruction Set Computers)精简指令集架构。

采用CISC架构的代表是Intel和AMD的X86指令集,采用RISC架构的代表是ARM指令集和PowerPC指令集。

ARM架构从诞生到今天从V1版本已经升级到了V8版本,各版本代表的分支型号如下表所示。

从图中可以看出,Cortex-A9 架构的CPU采用的是ARMv7的指令集,目前高性能的64位视频处理,比如Cortex-A72,采用的是ARMv8指令集。

ARM7TDMI介绍ARM7TDMI核,是从最早实现了32位地址空间编程模式的ARM6核发展而来的,可稳定地在低于5V的电源电压下可靠地工作。

增加了64位乘法指令、支持片上调试、Thumb指令集和EmbeddedICE片上断点和观察点。

ARM7TDMI是ARM公司最早为业界普遍认可且得到了广泛应用的核,特别是在手机和PDA应用中。

随着ARM技术的发展,它已是目前最低端的ARM 核。

ARM7TDMI处理器区别于其他ARM7处理器的一个重要特征是其独有的称之为Thumb的架构策略。

该策略为基本ARM 架构的扩展,由36种基于标准32位ARM指令集、但重新采用16位宽度优化编码的指令格式构成。

由于Thumb指令的宽度只为ARM指令的一半,因此能获得非常高的代码密度。

当Thumb指令被执行时,其16位的操作码被处理器解码为等效的32位标准ARM指令,然后ARM处理器核就如同执行32位的标准ARM指令一样执行16位的Thumb指令。

也即是Thumb架构为16位的系统提供了一条获得32位性能的途径。

ARM7TDMI内核既能执行32位的ARM指令集,又能执行16位的Thumb指令集,因此允许用户以子程序段为单位,在同一个地址空间使用Thumb指令集和ARM指令集混合编程,采用这种方式,用户可以在代码大小和系统性能上进行权衡,从而为特定的应用系统找到一个最佳的编程解决方案。

32位的ARM指令集由13种基本的指令类型组成,可分为如下四大类。

1)4类分支指令用于控制程序的执行流程、指令的特权等级可在ARM代码与Thumb代码之间进行切换。

2)3类数据处理指令用于操作片上的ALU、桶型移位器和乘法器,以完成在31个32位的通用寄存器之间的高速数据处理。

3)3类加载/存储指令用于控制在存储器和寄存器之间的数据传输。

一类为方便寻址进行了优化,另一类用于快速的上下文切换,第三类用于数据交换。

4)3类协处理器指令用于控制外部的协处理器,这些指令以开放统一的方式扩展用于片外功能指令集。

ARM v7指令集内容简介:在本文档的汇编语法中,用# 前缀表示立即值,用& 表示十六进制值,用% 表示二进制值,用{花括号} 表示指令中可选的设置字段或位。

下面表格中粗体的指令是核心ARM 指令,其他的是值得包含的位和片...在本文档的汇编语法中,用# 前缀表示立即值,用& 表示十六进制值,用% 表示二进制值,用{花括号} 表示指令中可选的设置字段或位。

下面表格中粗体的指令是核心ARM 指令,其他的是值得包含的位和片段、移位选项和汇编器助记码(mnemonic)... 还列出了协处理器指令。

但是用于RISC OS 机器的ARM 处理器不支持协处理器,只在一个可访问的芯片中提供了实际上的协处理器功能。

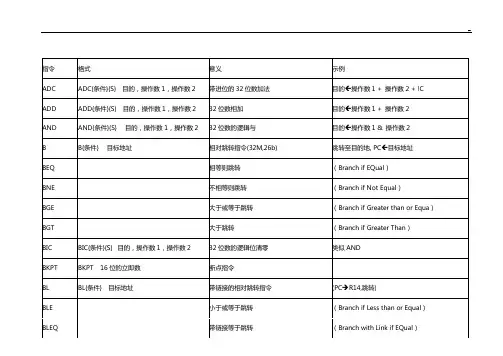

其中包括设置ARM、cache、MMU 的设施,等...指令意义最早的CPU / 注释ADC带进位的加法-ADD加法-AND逻辑与-ASL 算术左移这是一个选项,不是指令ASR 算术右移这是一个选项,不是指令B分支-BIC位清除-BL带连接的分支-BX 分支到Thumb 代码StrongARM SA1110 ?CDP 协处理器数据操作-CMN比较取负的值-CMP比较值-EOR异或两个值-LDC 装载内存到协处理器-LDM装载多个寄存器-LDR装载寄存器-LDRB装载字节到寄存器-LDRH装载半字到寄存器StrongARMLDRSB装载有符号字节到寄存器StrongARMLDRSH装载有符号半字到寄存器StrongARMLSL 逻辑左移这是一个选项,不是指令LSR 逻辑右移这是一个选项,不是指令MCR 协处理器寄存器传送-MLA带累加的乘法-MOV传送值/寄存器到一个寄存器-MRC 协处理器寄存器传送-MRS传送状态标志到一个寄存器ARM 6MSR传送一个寄存器的内容到状态标志ARM 6MUL乘法-MVN传送取负的(值) -ORR逻辑或-ROR 循环右移这是一个选项,不是指令RRX 带扩展的循环右移这是一个选项,不是指令RSB反向减法-RSC带借位的反向减法-SBC带借位的减法-SMLAL带累加的有符号长(64 位)乘法StrongARMSMULL有符号长(64 位)乘法StrongARMSTC 协处理器数据传送-STM存储多个寄存器-STR存储一个寄存器-STRB存储一个字节(从一个寄存器) -STRH存储一个半字(从一个寄存器) StrongARMSTRSB存储一个有符号字节(从一个寄存器) StrongARMSTRSH存储一个有符号半字(从一个寄存器) StrongARMSUB减法-SWI导致一个软件中断-SWP交换寄存器与内存ARM 3TEQ测试等价(概念上的EOR) -TST测试并屏蔽(概念上的AND) -UMLAL带累加的无符号长(64 位)乘法StrongARMUMULL无符号长(64 位)乘法StrongARMRISC OS 的BASIC 汇编器的伪指令ADR 得到目标的地址(4K 之内)ADRL 得到目标的地址(超过4K)ALIGN 把程序计数器设置到下个字的边界DCx 定义字节(B)、半字(W)、字(D)、字符串(S)、或浮点(F)值EQUx 定义字节(B)、半字(W)、字(D)、字符串(S)、或浮点(F)值OPT 选择汇编选项。

ARM指令集详解(超详细!带实例!)算术和逻辑指令ADC : 带进位的加法(Ad dition with C arry)ADC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2 + carryADC 将把两个操作数加起来,并把结果放置到⽬的寄存器中。

它使⽤⼀个进位标志位,这样就可以做⽐ 32 位⼤的加法。

下列例⼦将加两个 128 位的数。

128 位结果: 寄存器 0、1、2、和 3第⼀个 128 位数: 寄存器 4、5、6、和 7第⼆个 128 位数: 寄存器 8、9、10、和 11。

ADDS R0, R4, R8 ; 加低端的字ADCS R1, R5, R9 ; 加下⼀个字,带进位ADCS R2, R6, R10 ; 加第三个字,带进位ADCS R3, R7, R11 ; 加⾼端的字,带进位如果如果要做这样的加法,不要忘记设置 S 后缀来更改进位标志。

这两个指令与普通指令在对操作数的限制上有所不同:1. 给出的所有操作数、和⽬的寄存器必须为简单的寄存器。

2. 你不能对操作数 2 使⽤⽴即值或被移位的寄存器。

3. ⽬的寄存器和操作数 1 必须是不同的寄存器。

4. 最后,你不能指定 R15 为⽬的寄存器。

译注:CMP 和 CMP 是算术指令,TEQ 和 TST 是逻辑指令。

把它们归⼊⼀类的原因是它们的 S 位总是设置的,就是说,它们总是影响标志位。

CMN : ⽐较取负的值(C o m pare N egative)CMN{条件}{P} <op 1>, <op 2>status = op_1 - (- op_2)CMN 同于 CMP,但它允许你与⼩负值(操作数 2 的取负的值)进⾏⽐较,⽐如难于⽤其他⽅法实现的⽤于结束列表的 -1。

这样与 -1 ⽐较将使⽤:CMN R0, #1 ; 把 R0 与 -1 进⾏⽐较详情参照 CMP 指令。