555定时器构成的多谐振荡器_(时钟)

- 格式:pdf

- 大小:323.33 KB

- 文档页数:7

多谐振荡器是一种能产生矩形波的自激振荡器,也称矩形波发生器。

“多谐”指矩形波中除了基波成分外,还含有丰富的高次谐波成分。

多谐振荡器没有稳态,只有两个暂稳态。

在工作时,电路的状态在这两个暂稳态之间自动地交替变换,由此产生矩形波脉冲信号,常用作脉冲信号源及时序电路中的时钟信号。

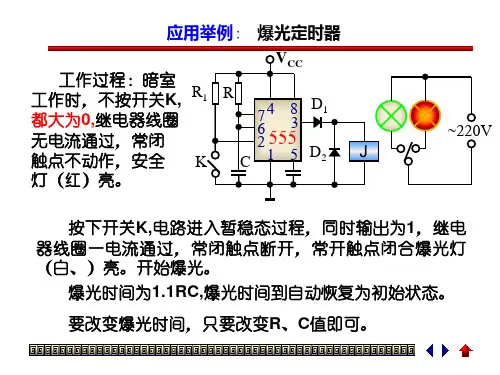

一、用555定时器构成的多谐振荡器1.电路组成:用555定时器构成的多谐振荡器电路如图6-11(a)所示:图中电容C、电阻R1和R2作为振荡器的定时元件,决定着输出矩形波正、负脉冲的宽度。

定时器的触发输入端(2脚)和阀值输入端(6脚)与电容相连;集电极开路输出端(7脚)接R1、R2相连处,用以控制电容C 的充、放电;外界控制输入端(5脚)通过0.01uF电容接地。

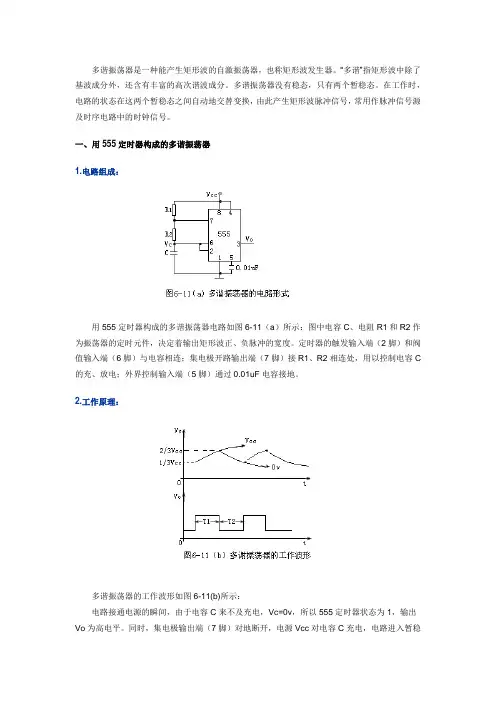

2.工作原理:多谐振荡器的工作波形如图6-11(b)所示:电路接通电源的瞬间,由于电容C来不及充电,Vc=0v,所以555定时器状态为1,输出Vo为高电平。

同时,集电极输出端(7脚)对地断开,电源Vcc对电容C充电,电路进入暂稳态I,此后,电路周而复始地产生周期性的输出脉冲。

多谐振荡器两个暂稳态的维持时间取决于RC充、放电回路的参数。

暂稳态Ⅰ的维持时间,即输出Vo的正向脉冲宽度T1≈0.7(R1+R2)C;暂稳态Ⅱ的维持时间,即输出Vo 的负向脉冲宽度T2≈0.7R2C。

因此,振荡周期T=T1+T2=0.7(R1+2R2)C,振荡频率f=1/T。

正向脉冲宽度T1与振荡周期T 之比称矩形波的占空比D,由上述条件可得D=(R1+R2)/(R1+2R2),若使R2>>R1,则D≈1/2,即输出信号的正负向脉冲宽度相等的矩形波(方波)。

二、多谐振荡器应用举例:1.模拟声响发生器:将两个多谐振荡器连接起来,前一个振荡器的输出接到后一个振荡器的复位端,后一个振荡器的输出接到扬声器上。

这样,只有当前一个振荡器输出高电平时,才驱动后一个振荡器振荡,扬声器发声;而前一个振荡器输出低电平时,导致后面振荡器复位并停止震荡,此时扬声器无音频输出。

![[数电课程设计数字电子时钟的实现] 电子时钟课程设计](https://uimg.taocdn.com/09fa58d0af45b307e9719786.webp)

[数电课程设计数字电子时钟的实现] 电子时钟课程设计课程设计报告设计题目:数字电子时钟的设计与实现班级:学号:姓名:指导教师:设计时间:摘要钟表的数字化给人们生产生活带来了极大的方便,大大的扩展了原先钟表的报时。

诸如,定时报警、按时自动打铃、时间程序自动控制等,这些,都是以钟表数字化为基础的。

功能数字钟是一种用数字电路实现时、分、秒、计时的装置,与机械时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。

从原理上讲,数字钟是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

因此,此次设计与制作数字钟就是为了了解数字钟的原理,从而学会制作数字钟,而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及使用方法。

通过此次课程设计可以进一步学习与各种组合逻辑电路与时序电路的原理与使用方法。

通过仿真过程也进一步学会了Multisim7的使用方法与注意事项。

本次所要设计的数字电子表可以满足使用者的一些特殊要求,输出方式灵活,如可以随意设置时、分、秒的输出,定点报时。

由于集成电路技术的发展,,使数字电子钟具有体积小、耗电省、计时准确、性能稳定、维护方便等优点。

关键词:数字钟,组合逻辑电路,时序电路,集成电路目录摘要 (1)第1章概述············································3第2章课程设计任务及要求·······························42.1设计任务············································42.2设计要求············································4第3章系统设计··········································63.1方案论证············································63.2系统设计············································63.2.1结构框图及说明·································63.2.2系统原理图及工作原理···························73.3单元电路设计········································83.3.1单元电路工作原理·······························83.3.2元件参数选择···································14第4章软件仿真·········································154.1仿真电路图··········································154.2仿真过程············································164.3仿真结果············································16第5章安装调试··········································175.1安装调试过程········································175.2故障分析············································17第6章结论···············································18第7章使用仪器设备清单··································19参考文献·················································19收获、体会和建议·········································20第1章概述数字集成电路的出现和飞速发展,以及石英晶体振荡器的广泛应用,使得数字钟的精度稳定度远远超过了老式的机械表,用数字电路实现对“时”、“分”、“秒”数字显示的数字钟在数字显示方面,目前已有集成的计数、译码电路,它可以直接驱动数码显示器件,也可以直接采用才COMS--LED光电组合器件,构成模块式石英晶体数字钟。

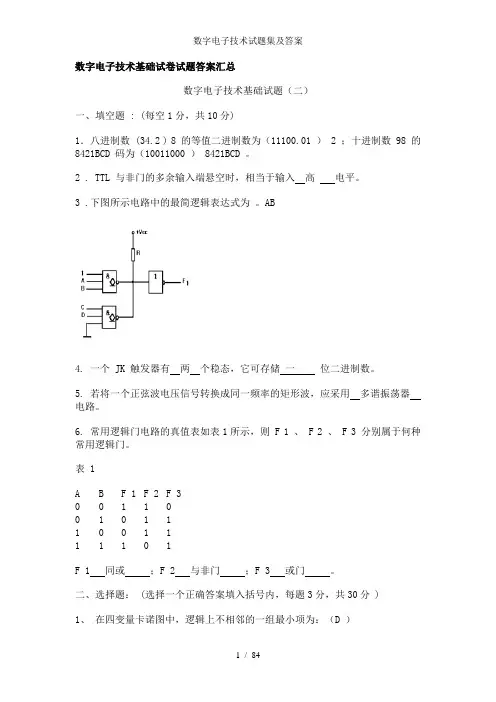

数字电子技术基础试卷试题答案汇总数字电子技术基础试题(二)一、填空题 : (每空1分,共10分)1.八进制数 (34.2 ) 8 的等值二进制数为(11100.01 ) 2 ;十进制数 98 的8421BCD 码为(10011000 ) 8421BCD 。

2 . TTL 与非门的多余输入端悬空时,相当于输入高电平。

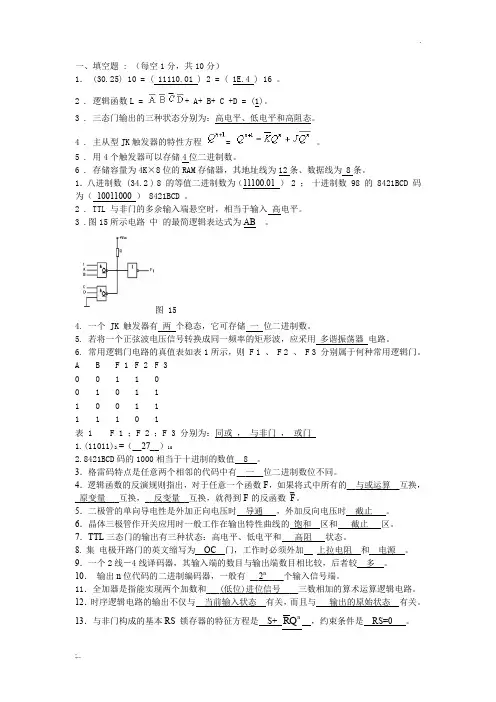

3 .下图所示电路中的最简逻辑表达式为。

AB4. 一个 JK 触发器有两个稳态,它可存储一位二进制数。

5. 若将一个正弦波电压信号转换成同一频率的矩形波,应采用多谐振荡器电路。

6. 常用逻辑门电路的真值表如表1所示,则 F 1 、 F 2 、 F 3 分别属于何种常用逻辑门。

表 1A B F 1 F 2 F 30 0 1 1 00 1 0 1 11 0 0 1 11 1 1 0 1F 1 同或;F 2 与非门;F 3 或门。

二、选择题: (选择一个正确答案填入括号内,每题3分,共30分 )1、在四变量卡诺图中,逻辑上不相邻的一组最小项为:(D )A、m 1与m 3B、m 4与m6C、m 5 与m 13D、m 2 与m 82、 L=AB+C 的对偶式为:(B )A 、 A+BC ;B 、( A+B )C ; C 、 A+B+C ;D 、 ABC ;3、半加器和的输出端与输入端的逻辑关系是(D )A、与非B、或非C、与或非D、异或4、 TTL 集成电路 74LS138 是3 / 8线译码器,译码器为输出低电平有效,若输入为 A 2 A 1 A 0 =101 时,输出:为(B )。

A . 00100000 B. 11011111 C.11110111 D. 000001005、属于组合逻辑电路的部件是(A )。

A、编码器B、寄存器C、触发器D、计数器6.存储容量为8K×8位的ROM存储器,其地址线为(C )条。

A、8B、12C、13D、147、一个八位D/A转换器的最小电压增量为0.01V,当输入代码为10010001时,输出电压为(C )V。

数字电子技术课程设计报告课程设计(大作业)报告课程名称:数字电子技术设计题目:数字秒表院系:信息技术学院班级:设计者:学号:指导教师:**设计时间:2015.12.14--2015.12. 18 信息技术学院昆明学院课程设计(大作业)任务书目录一、设计目的 (1)二、设计要求和设计指标 (1)三、设计内容 (1)3.1电子秒表工作原理 (1)3.1.1总体设计 (2)3.1.2 脉冲电路设计 (2)3.1.3总清零控制电路 (6)3.1.4时间计数单元 (6)3.1.5分频电路 (8)3.1.6码驱动及显示单元 (9)3.1.7多功能数字秒表电路的组合 (10)3.2仿真结果与分析 (12)3.2.1 时钟发生器的测试 (12)3.2.2 计数、译码、显示单元的测试 (13)3.2.3 整体测试 (13)3.2.4 电子秒表准确度的测试 (14)四、本设计改进建议 (14)五、总结 (15)六、主要参考文献 (16)一、设计目的1、学习数字电路中基本RS触发器、单稳态触发器、时钟发生器及计数、译码显示器等单元电路的综合应用。

2、学习电子秒表的调试方法。

3、秒表由五位七段LED显示器显示,其中一位显示“min”,四位显示“s”,其中显示分辨率为0.01s,计时范围为0~9分59秒99毫秒;具有清零、启动计时、暂停计时及继续计时等功能;控制开关为两个;启动(继续)/暂停计时开关和复位开关。

二、设计要求和设计指标制作一个数字秒表,将单个数字秒表组合设计成可以同时对多人进行计时的多人数字秒表。

电子秒表的工作原理就是不断输出连续脉冲给加法计数器,而加法计数器通过译码器来显示它所记忆的脉冲周期个数。

1.时钟发生器:利用石英震荡555定时器构成的多谐振荡器做时钟源,产生脉冲。

2.记数器:对时钟信号进行记数并进位,百分之一秒和十分之一秒以及个位秒之间10进制,十位秒为六进制; 本设计采用可预置的十进制同步加法计数器74LS90构成电子秒表的计数单元。

课程设计说明书课程名称:数字电子技术、模拟电子技术设计题目:循环彩灯院系:电子信息与电气工程学院学生姓名:李健学号:201002030013专业班级:通信工程2010级指导教师:翟亚芳2012年05月22日课程设计任务书循环彩灯摘要:设计制作了一个循环彩灯控制电路,该电路可以控制8个彩灯循环点亮,每个彩灯点亮时间为1秒。

控制电路主要信号发生器、计数器、译码器和输出电路几部分组成。

信号发生器是由555定时器构成的多谐振荡器;驱动电路由74LS192计数器和74LS138译码器组成;输出电路由八个发光二级管和一个300Ω的电阻和一个5V电源组成。

利用Multisim 10对设计的电路进行仿真,可以得到八个彩灯依次循环着亮,并且每个彩灯的亮灯时间为1秒。

此外要注意,74LS192发光二极管要共阳极连接。

关键词:循环彩灯;555定时器;74LS192;74LS138 ;Multisim 10电路仿真目录1. 设计背景 (1)1.1 电子技术课程设计的目的与意义 (1)1.2 电子技术课程设计的方法和步骤 (1)2. 设计方案 (2)2.1任务分析 (2)2.2方案论证 (2)3. 方案实施 (3)3.1原理图设计 (3)3.2电路仿真 (10)3.3 PCB制作 (11)3.4安装与调试 (12)4. 结果与结论 (13)5. 收获与致谢 (13)6. 参考文献 (14)7. 附件 (15)7.1电路原理图 (15)7.2 PCB布线图 (16)7.3元器件清单 (16)1. 设计背景1.1 电子技术课程设计的目的与意义电子技术是一门实践性很强的课程,加强工程训练,特别是技能的培养,对于培养设计人员的素质和能力具有十分重要的作用。

在电子信息类本科教学中,课程设计是一个重要的实践环节,它包括选择课题、电子电路设计、组装、调试和编写总结报告等实践内容。

通过课程设计要实现以下两个目标,第一学生初步掌握电子线路的设计、组装及调试方法。

第八章脉冲产生与整形在时序电路中,常常需要用到不同幅度、宽度以及具有陡峭边沿的脉冲信号。

事实上,数字系统几乎离不开脉冲信号。

获取这些脉冲信号的方法通常有两种:直接产生或者利用已有信号变换得到。

本章主要讨论常用的脉冲产生和整形电路的结构、工作原理、性能分析等,常见的脉冲电路有:单稳态触发器、施密特触发器和多谐振荡器。

第一节基本知识、重点与难点一、基本知识(一)常用脉冲产生和整形电路1. 施密特触发器(1)电路特点施密特触发器是常用的脉冲变换和脉冲整形电路。

电路主要有两个特点:一是施密特触发器是电平型触发电路;二是施密特触发器电压传输特性具有回差特性,或称滞回特性。

输入信号在低电平上升过程中,电路输出状态发生转换时对应的输入电平称为正向阈值电压U T+,输入信号在高电平下降过程中,电路状态转换对应的输入电平称为负向阈值电压U T-,U T+与U T-的差值称为回差电压ΔU T。

(2)电路构成及参数施密特触发器有多种构成方式,如:门电路构成、集成施密特触发器、555定时器构成。

主要电路参数:正向阈值电压U T+、负向阈值电压U T-和回差电压ΔU T。

(3)电路应用施密特触发器主要应用范围:波形变换、波形整形和幅度鉴别等。

2. 单稳态触发器(1)电路特点单稳态触发器特点如下:①单稳态触发器有稳态和暂稳态两个不同的工作状态;②在外加触发信号的作用下,触发器可以从稳态翻转到暂稳态,暂稳态维持一段时间,自动返回原稳态;③暂稳态维持时间的长短取决于电路参数R和C。

(2)电路构成及参数单稳态触发器有多种构成方式,如:门电路构成的积分型单稳态触发器、门电路构成的微分型单稳态触发器、集成单稳态触发器、555定时器构成的单稳态触发器等。

主要电路参数:暂稳态的维持时间t w、恢复时间t re 、分辨时间t d、输出脉冲幅度U m。

(3)电路应用单稳态触发器主要应用范围:定时、延时、脉冲波形整形等。

3. 多谐振荡器多谐振荡器是一种自激振荡器,接通电源后,就可以自动产生矩形脉冲,是数字系统中产生脉冲信号的主要电路。

555定时器介绍:555 定时器是一种模拟和数字功能相结合的中规模集成器件。

一般用双极性工艺制作的称为555,用CMOS 工艺制作的称为7555,除单定时器外,还有对应的双定时器556/7556。

555 定时器的电源电压范围宽,可在4.5V~16V 工作,7555 可在3~18V 工作,输出驱动电流约为200mA,因而其输出可与TTL、CMOS 或者模拟电路电平兼容。

555 定时器成本低,性能可靠,只需要外接几个电阻、电容,就可以实现多谐振荡器、单稳态触发器及施密特触发器等脉冲产生与变换电路。

它也常作为定时器广泛应用于仪器仪表、家用电器、电子测量及自动控制等方面。

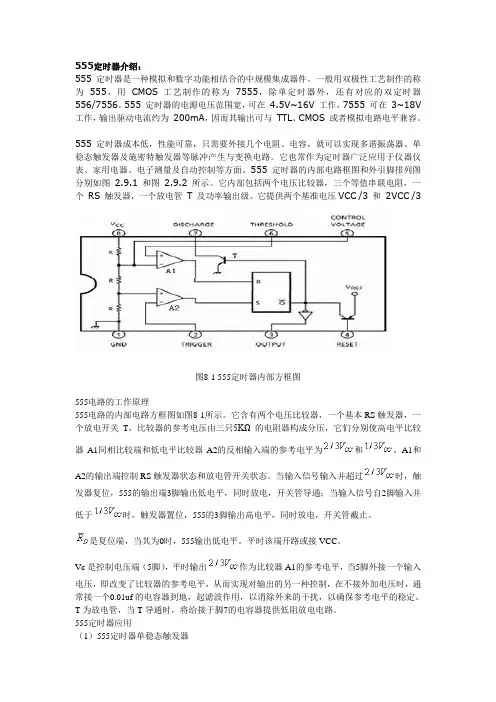

555 定时器的内部电路框图和外引脚排列图分别如图 2.9.1 和图 2.9.2 所示。

它内部包括两个电压比较器,三个等值串联电阻,一个RS 触发器,一个放电管T 及功率输出级。

它提供两个基准电压VCC /3 和2VCC /3图8-1 555定时器内部方框图555电路的工作原理555电路的内部电路方框图如图8-1所示。

它含有两个电压比较器,一个基本RS触发器,一个放电开关T,比较器的参考电压由三只5KΩ的电阻器构成分压,它们分别使高电平比较器A1同相比较端和低电平比较器A2的反相输入端的参考电平为和。

A1和A2的输出端控制RS触发器状态和放电管开关状态。

当输入信号输入并超过时,触发器复位,555的输出端3脚输出低电平,同时放电,开关管导通;当输入信号自2脚输入并低于时,触发器置位,555的3脚输出高电平,同时放电,开关管截止。

是复位端,当其为0时,555输出低电平。

平时该端开路或接VCC。

Vc是控制电压端(5脚),平时输出作为比较器A1的参考电平,当5脚外接一个输入电压,即改变了比较器的参考电平,从而实现对输出的另一种控制,在不接外加电压时,通常接一个0.01uf的电容器到地,起滤波作用,以消除外来的干扰,以确保参考电平的稳定。

T为放电管,当T导通时,将给接于脚7的电容器提供低阻放电电路。

555定时器组成的振荡器晶体振荡器的作用是产生时间标准信号。

数字钟的精度,主要取决于时间标准信号的频率及其稳定度。

因此,一般采用石英晶体振荡器经过分频后获得时间标准信号。

也可采用由门电路或555定时器构成的多谐振荡器作为时间标准信号源。

555定时器可以实现模拟和数字两项功能。

1.可产生精确的时间延迟和振荡,内部有3个5kΩ的电阻分压器,故称555。

2.电源电压电流范围宽,双极型:5~16V ;CMOS :3~18V 。

3.可以提供与TTL 及CMOS 数字电路兼容的接口电平。

4.可输出一定的功率,可驱动微电机、指示灯、扬声器等。

5.应用:脉冲波形的产生与变换、仪器与仪表、测量与控制、家用电气与电子玩具等领域。

6.TTL 单定时器型号的最后3位数字为555,双定时器的为556;CMOS 单定时器的最后4位数为7555,双定时器的为7556。

它们的逻辑功能和外部引线排列完全相同。

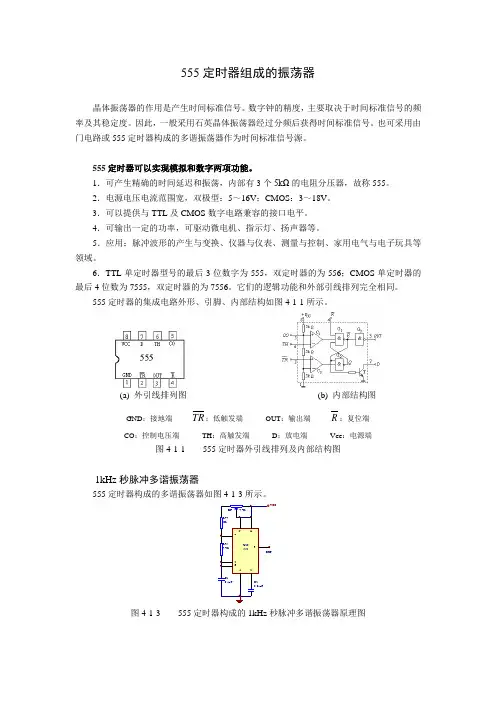

555定时器的集成电路外形、引脚、内部结构如图4-1-1所示。

(a) 外引线排列图 (b) 内部结构图GND :接地端TR :低触发端 OUT :输出端 R :复位端CO :控制电压端 TH :高触发端 D :放电端 V CC :电源端图4-1-1 555定时器外引线排列及内部结构图1kHz 秒脉冲多谐振荡器555定时器构成的多谐振荡器如图4-1-3所示。

图4-1-3 555定时器构成的1kHz 秒脉冲多谐振荡器原理图该振荡器的工作原理是:接通V CC 后,V CC 经R 44和R 45对C 1充电。

当u c 上升到CC V 32时,u o =0,T 导通,C 1通过R 45和T 放电,u c 下降。

当u c 下降到CC V 31时,u o 又由0变为1,T 截止,V CC 又经R 44和R 45对C 1充电。

如此重复上述过程,在输出端u o 产生了连续的矩形脉冲。

振荡频率和占空比的估算:1.电容C 充电时间:145441)(7.0C R R t P += 2.电容C 放电时间:14527.0C R t P = 3.电路谐振频率f 的估算:振荡周期为:14544)2(7.0C R R T += 振荡频率为:1454414544)2(43.1)2(7.011C R R C R R T f +≈+==4.占空比D :45444544145441454412)2(7.0)(7.0R R R R C R R C R R T t D p ++=++==图4-1-6为555定时器构成叮咚门铃原理图。

555定时器的工作原理555定时器是一种常用的集成电路元件,它可以在电子电路中实现定时功能。

在很多电子设备中,我们都可以看到它的身影,比如闹钟、计时器、蜂鸣器等。

那么,555定时器是如何工作的呢?接下来,我们就来详细了解一下。

首先,我们需要了解555定时器的基本结构。

555定时器由比较器、触发器、RS触发器、输出级等部分组成。

它有8个引脚,分别是控制电压引脚(VCC)、复位引脚(RST)、输出引脚(OUT)、触发引脚(TRG)、控制电压引脚(CV)、放电引脚(DIS)、电源引脚(GND)和触发引脚(THR)。

通过这些引脚,我们可以控制555定时器的工作状态。

在工作时,555定时器可以分为单稳态和多谐振两种工作模式。

在单稳态工作模式下,当触发引脚接收到低电平信号时,输出引脚会产生一个脉冲信号,持续时间由外部电路决定。

而在多谐振工作模式下,555定时器可以产生周期性的方波信号,频率和占空比也由外部电路决定。

在实际应用中,我们可以通过改变外部电路的参数,比如电阻和电容的数值,来调整555定时器的工作状态。

这样,我们就可以实现不同的定时功能,比如延时、脉冲产生、频率调整等。

除此之外,555定时器还具有很好的稳定性和可靠性。

它可以在较宽的电压范围内工作,而且温度稳定性也很好。

因此,它在各种环境下都能够正常工作,具有很高的实用价值。

总的来说,555定时器是一种功能强大、应用广泛的集成电路元件。

通过合理的外部电路设计,我们可以实现各种定时功能,满足不同场合的需求。

它的稳定性和可靠性也使得它成为了电子电路设计中的重要组成部分。

希望通过本文的介绍,读者们对555定时器的工作原理有了更深入的了解。

一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( 11110.01 ) 2 = ( 1E.4 ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = (1)。

3 . 三态门输出的三种状态分别为:高电平、低电平和高阻态。

4 . 主从型JK 触发器的特性方程 = 。

5 . 用4个触发器可以存储4位二进制数。

6 . 存储容量为4K×8位的RAM 存储器,其地址线为12条、数据线为 8条。

1.八进制数 (34.2 ) 8 的等值二进制数为(11100.01 ) 2 ; 十进制数 98 的 8421BCD 码为( 10011000 ) 8421BCD 。

2 . TTL 与非门的多余输入端悬空时,相当于输入 高电平。

3 .图15所示电路 中 的最简逻辑表达式为AB 。

图 154. 一个 JK 触发器有 两 个稳态,它可存储 一 位二进制数。

5. 若将一个正弦波电压信号转换成同一频率的矩形波,应采用 多谐振荡器 电路。

6. 常用逻辑门电路的真值表如表1所示,则 F 1 、 F 2 、 F 3 分别属于何种常用逻辑门。

A B F 1 F 2 F 30 0 1 1 00 1 0 1 11 0 0 1 11 1 1 0 1表 1 F 1 ;F 2 ;F 3 分别为:同或 , 与非门 , 或门1.(11011)2 =(__27__)102.8421BCD 码的1000相当于十进制的数值 8 。

3.格雷码特点是任意两个相邻的代码中有__一__位二进制数位不同。

4.逻辑函数的反演规则指出,对于任意一个函数F ,如果将式中所有的__与或运算__互换,_原变量___互换,__反变量__互换,就得到F 的反函数 F 。

5.二极管的单向导电性是外加正向电压时 导通 ,外加反向电压时 截止 。

6.晶体三极管作开关应用时一般工作在输出特性曲线的 饱和 区和 截止 区。

7.TTL 三态门的输出有三种状态:高电平、低电平和 高阻 状态。

555定时器构成的多谐振荡器制作人:张展培 Ap0305136冼志敏 Ap0305129 黄云 Ap0305114555定时器是一种模拟电路和数字电路相结合的中规模集成器件,它性能优良,适用范围很广,外部加接少量的阻容元件可以很方便地组成单稳态触发器和多谐振荡器,以及不需外接元件就可组成施密特触发器。

因此集成555定时被广泛应用于脉冲波形的产生与变换、测量与控制等方面。

本实验根据555定时器的功能强以及其适用范围广的特点,设计实验研究它的内部特性和简单应用。

一、原理1、555定时器内部构造555定时器是一种模拟电路和数字电路相结合的中规模集成电路,其内部构造如图〔A 〕及管脚排列如图〔B 〕所示。

它由分压器、比拟器、根本R--S 触发器和放电三极管等局部组成。

分压器由三个5K 的等值电阻串联而成。

分压器为比拟器1A 、2A 提供参考电压,比拟器1A 的参考电压为23cc V ,加在同相输入端,比拟器2A 的参考电压为13cc V ,加在反相输入端。

比拟器由两个构造一样的集成运放1A 、2A 组成。

高电平触发信号加在1A 的反相输入端,与同相输入端的参考电压比拟后,其结果作为根本R--S 触发器_D R 端的输入信号;低电平触发信号加在2A 的同相输入端,与反相输入端的参考电压比拟后,其结果作为根本R —S 触发器_D S 端的输入信号。

根本R--S 触发器的输出状态受比拟器1A 、2A 的输出端控制。

2、多谐振荡器工作原理由555定时器组成的多谐振荡器如图(C)所示,其中R 1、R 2和电容C 为外接元件。

其工作波如图(D)所示。

设电容的初始电压c U =0,t =0时接通电源,由于电容电压不能突变,所以高、低触发端TH V =TL V =0<13VCC,比拟器A1输出为高电平,A2输出为低电平,即_1D R =,_0D S =〔1表示高电位,0表示低电位〕,R S -触发器置1,定时器输出01u =此时_0Q =,定时器内部放电三极管截止,电源cc V 经1R ,2R 向电容C充电,c u 逐渐升高。

由555定时器构成的多谐振荡器一、介绍多谐振荡器多谐振荡器是一种可以产生多种频率信号的电路,它通常由一个或多个谐振电路和一个信号源组成。

在电子工程中,多谐振荡器被广泛应用于各种电路中,例如音频放大器、射频发射机、数字时钟等。

其中,由555定时器构成的多谐振荡器是一种简单且易于实现的方案。

二、555定时器简介555定时器是一种经典的集成电路芯片,它由美国公司Signetics(现为Philips)于1971年推出。

该芯片主要用于计时和脉冲生成等应用中。

555定时器具有简单可靠、稳定性好、工作温度范围广等优点,在模拟电路和数字电路中均有广泛应用。

三、由555定时器构成的多谐振荡器原理1. 555定时器基本工作原理在了解由555定时器构成的多谐振荡器之前,首先需要了解555定时器的基本工作原理。

555定时器主要由两个比较器和一个RS触发器组成。

当输入信号超过某个阈值(Vth)时,第一个比较器的输出为高电平;当输入信号低于另一个阈值(Vtl)时,第二个比较器的输出为低电平。

当两个比较器的输出状态改变时,RS触发器的状态也会改变,从而控制输出端口的电平状态。

2. 多谐振荡器原理多谐振荡器通常由一个或多个谐振电路和一个信号源组成。

其中,谐振电路是指由一个电容和一个电感组成的并联或串联回路。

当该回路处于共振状态时,它可以产生特定频率的信号。

在由555定时器构成的多谐振荡器中,通过改变RC元件(即电容和电阻)的数值来改变共振频率。

具体来说,当555定时器处于稳定状态时(即输出端口为高电平或低电平),RC元件开始充放电。

当充放电时间达到某个阈值(Tth)时,555定时器会自动将输出端口反转,并且开始进行下一次充放电过程。

因此,在不同RC元件数值下,555定时器可以产生不同频率的信号。

四、实现方法1. 单频率多谐振荡器单频率多谐振荡器是指只能产生一种固定频率的多谐振荡器。

在该电路中,555定时器的输出端口通过一个RC元件和一个二极管连接到输入端口,从而形成一个正反馈回路。

555定时器的应用与原理介绍555定时器介绍:555 定时器是一种模拟和数字功能相结合的中规模集成器件。

一般用双极性工艺制作的称为555,用CMOS 工艺制作的称为7555,除单定时器外,还有对应的双定时器556/7556。

555 定时器的电源电压范围宽,可在 4.5V~16V 工作,7555 可在3~18V 工作,输出驱动电流约为200mA,因而其输出可与TTL、CMOS 或者模拟电路电平兼容。

555 定时器成本低,性能可靠,只需要外接几个电阻、电容,就可以实现多谐振荡器、单稳态触发器及施密特触发器等脉冲产生与变换电路。

它也常作为定时器广泛应用于仪器仪表、家用电器、电子测量及自动控制等方面。

555 定时器的内部电路框图和外引脚排列图分别如图 2.9.1 和图 2.9.2 所示。

它内部包括两个电压比较器,三个等值串联电阻,一个RS 触发器,一个放电管T 及功率输出级。

它提供两个基准电压VCC /3 和2VCC /3图8-1 555定时器内部方框图<555定时器内部结构图>555电路的工作原理555电路的内部电路方框图如图8-1所示。

它含有两个电压比较器,一个基本RS触发器,一个放电开关T,比较器的参考电压由三只5KΩ的电阻器构成分压,它们分别使高电平比较器A1同相比较端和低电平比较器A2的反相输入端的参考电平为和。

A1和A2的输出端控制RS触发器状态和放电管开关状态。

当输入信号输入并超过时,触发器复位,555的输出端3脚输出低电平,同时放电,开关管导通;当输入信号自2脚输入并低于时,触发器置位,555的3脚输出高电平,同时放电,开关管截止。

是复位端,当其为0时,555输出低电平。

平时该端开路或接VCC。

Vc是控制电压端(5脚),平时输出作为比较器A1的参考电平,当5脚外接一个输入电压,即改变了比较器的参考电平,从而实现对输出的另一种控制,在不接外加电压时,通常接一个0.01uf的电容器到地,起滤波作用,以消除外来的干扰,以确保参考电平的稳定。

任务8.1定时器555延时电路设计习题解答一、测试(一)判断题1. 单稳态触发器有两个稳态。

答案:F解题:1个稳定状态.2. 多谐振荡器有两个稳态。

答案:F解题:无稳定状态3. 施密特触发器有两个稳态。

答案:T解题:施密特触发器有两个稳态。

4. 555定时器要构成施密特触发器,只要将低电平触发端和高电平触发端连在一起。

答案:T解题:555定时器要构成施密特触发器,只要将低电平触发端和高电平触发端连在一起。

5. 在555定时器内部电路中,当内部两比较器输出都为高电平时,电路输出状态翻转。

答案:F解题:在555定时器内部电路中,当两比较器输出都为高电平时,电路输出状态不变。

相当于内部RS触发器输入两无效信号。

6. 单稳态触发器又称为单稳态电路,它是只有一种稳定状态的电路。

如果没有外界信号触发,它就始终保持在稳定状态不变。

答案:T解题:单稳态触发器又称为单稳态电路,它是只有一种稳定状态的电路。

如果没有外界信号触发,它就始终保持在稳定状态不变。

7. 单稳态触发器它有稳态和暂稳态两个不同的工作状态;在外界触发信号作用下,电路能由稳态翻转到暂稳态,在暂稳态维持一段时间以后,电路会自动返回到稳态;暂稳态的持续时间的长短取决于外界触发信号的长短。

答案:F解题:单稳态触发器它有稳态和暂稳态两个不同的工作状态;在外界触发信号作用下,电路能由稳态翻转到暂稳态,在暂稳态维持一段时间以后,电路会自动返回到稳态;暂稳态的持续时间的长短取决于电路电路本身的参数,与触发脉冲无关。

8. 多谐振荡器是产生矩形脉冲信号的自激振荡器。

它不需要输入信号,接通电源就可以自动输出矩形脉冲信号。

答案:T解题:多谐振荡器是产生矩形脉冲信号的自激振荡器。

它不需要输入信号,接通电源就可以自动输出矩形脉冲信号。

9. 在555定时器组成的多谐振荡器电路中,输出波形的周期主要由电容的充放电时间常数决定。

解题:在555定时器组成的多谐振荡器电路中,输出波形的周期主要由电容的充放电时间常数决定。