数字视频接口——DVI 1.0

- 格式:doc

- 大小:109.00 KB

- 文档页数:5

DVI 接口技术的简单介绍

就目前的市场销售情况来说,液晶显示器(LCD)的销售额已经超过了传统的CRT 显示器(不过由于液晶显示器的单价较高,具体的销售数量(台)还没有超过CRT)。

目前人们选择液晶显示器一方面是看重该产品的节能性,一方面看重其体积小、占地少。

目前销售的液晶显示器普遍都具有两种接口,DVI(数字视频接口)和模拟接口(D 型15 针)。

由于液晶采用的是一种纯数字的设备,那幺直接通过DVI 接口输入数字信号当然会更好,而通过D 型15 针接口就显得有些不明智了(RAMDAC 将数字信号转为模拟信号,再将模拟信号传入液晶显示器,最后通过液晶显示器内部再次转为数字信号)。

在CRT 占据天下时模拟接口自然没有什幺问题,不过在液晶大行其道的今天就显得有些不合时宜了。

实际上,笔记本电脑在很久以前就开始通过LVDS(低电压微分信号)传送器、接收器实现全数字显示了。

而目前使用越来越多的数字接口(DVI)是由DDWG(Digital Display Working Group)开发的。

对于模拟接口的显示器,我们都知道它和PC 连接时需要进行手动调节才能得到好的图象;而对于采用DVI 接口的显示器,尽管其承诺无需调节。

DisplayPort接口关于DisplayPort标准:Displayport接口视频电子标准协会Video Electronics Standards Association(VESA)公布了DisplayPort显示接口标准的最终版本:DisplayPort 1.0。

作为DVI的继任者,DisplayPort将在传输视频信号的同时加入对高清音频信号传输的支持,同时支持更高的分辨率和刷新率。

根据设计,DisplayPort既支持外置显示连接,也支持内置显示连接。

VESA希望笔记本厂商不仅使用DisplayPort连接独立显示器,也能使用它来直接连接液晶显示屏和主板,方便笔记本的升级。

为此,DisplayPort接口也设计得非常小巧,既方便笔记本的使用,也允许显卡配置多个接口。

DisplayPort 1.0规格支持单通道、单向、四线路连接,数据传输率10.8Gbps,足以传送未经压缩的视频和相关音频,同时还支持1Mbps的双向辅助通道,供设备控制之用,此外还支持8位和10位颜色。

在数据传输上,DisplayPort使用了“micro-packetised”格式。

VESA还表示,DisplayPort具备高度的可扩展性,可以在今后不断加入更多新内容。

与消费电子领域内的HDCP类似,DisplayPort也可以通过128位AES加密实现对HD视频数据的拷贝保护。

事实上,VESA也盯紧了消费电子市场,声称DisplayPort同样可以很方便地连接电视、DVD播放器等设备。

VESA在一年前左右开始开发DisplayPort,而之后不久,特别利益组织(SIG)提出了UDI(通用显示界面),可以同时兼容HDMI和DVI,而这一点正是DisplayPort所缺乏的。

不过,UDI虽然可以通过HDMI支持HDCP反盗版系统,但就像DVI,或者说不像HDMI 和DisplayPort,它不支持音频信号传输。

UDI 1.0预计本季度完成。

关于HDMI与DVI的介绍针对市场上部分高端平板显示产品使用了一种新型音视频接口:HDMI接口,如我们的LS10、LS09、PP09等系列机芯均已配备了HDMI接口。

现将HDMI接口简单介绍如下:HDMI(全称:High Definition Multimedia Interface,高清晰多媒体接口)是世界首个支持在单线缆上传输不经压缩的全数字高清晰度视频、多声道音频和智能格式与控制命令数据的数字接口。

HDMI组织由八家领先的消费类电子产品制造商:HITACHI,Panasonic,Philips,SONY,Thomson,Toshiba和Silicon,lmage共同发起。

HDMI组织于2002 年12月发布了技术规范HDMI V1.0,并于2005年8月将其升级至最新版本HDMI V1.2。

DVI(全称:Digital Visual lnterface,:数字视频接口),由DDWG(数字显示工作组)于1999年4月提出的。

DVI接口协议问世的最初目的是为了解决PC与数字显示器之间的无压缩数据传输问题,它利用一个或者两个TMDS信号传输通道,可传输2048X1536P(60HZ)的数字视频信号。

目前DVI接口协议已经得到了PC制造业的广泛支持,但在以高清晰数字电视为代表新兴消费领域却力不从心,难以胜任。

主要原因在于:1、DVI接口不包括音频信号通道,系统的音频信号必须由其它接口传输。

2、DVI接口只能传输数字色度分量信号(R/G/B)和同步信号,不支持具有更佳效果的数字色差分量(Y/Cb/Cr)的传输。

3、传输距离方面,DVI接口协议中没有明确的规定,普遍认为15米是最长限度,这在许多应用中显得捉襟见肘。

4、DVI接口的体积较大,使用不方便5、DVI接口具有单TDMS链路和双TDMS链路两种可选结构,且没有成熟的兼容性测试机构,不同设备间的适应性较差,降低了设备的易用性。

基于上述理由DVI最终不能被新兴的消费应用所采纳。

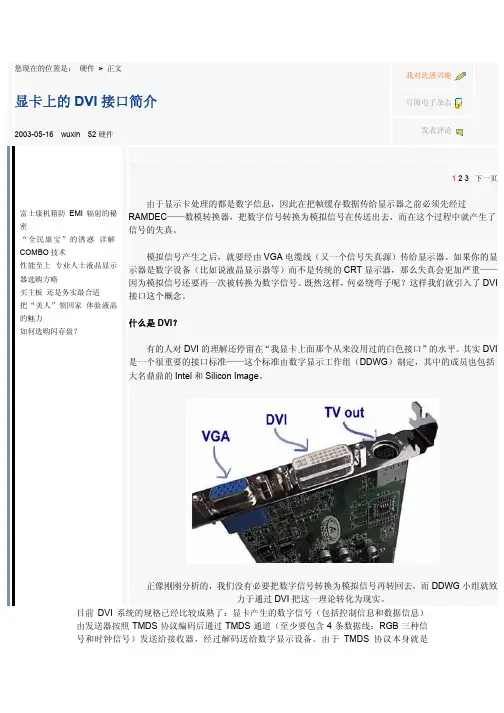

您现在的位置是: 硬件 > 正文 显卡上的DVI 接口简介2003-05-16■wuxin ■52硬件 我对此感兴趣订阅电子杂志发表评论富士康机箱防EMI 辐射的秘密“全民康宝”的诱惑 详解COMBO 技术性能至上 专业人士液晶显示器选购方略买主板 还是务实最合适 把“美人”领回家 体验液晶的魅力如何选购闪存盘?1 2 3 下一页 由于显示卡处理的都是数字信息,因此在把帧缓存数据传给显示器之前必须先经过RAMDEC ——数模转换器,把数字信号转换为模拟信号在传送出去,而在这个过程中就产生了信号的失真。

模拟信号产生之后,就要经由VGA 电缆线(又一个信号失真源)传给显示器。

如果你的显示器是数字设备(比如说液晶显示器等)而不是传统的CRT 显示器,那么失真会更加严重——因为模拟信号还要再一次被转换为数字信号。

既然这样,何必绕弯子呢?这样我们就引入了DVI 接口这个概念。

什么是DVI ? 有的人对DVI 的理解还停留在“我显卡上面那个从来没用过的白色接口”的水平。

其实DVI 是一个很重要的接口标准——这个标准由数字显示工作组(DDWG )制定,其中的成员也包括大名鼎鼎的Intel 和Silicon Image 。

正像刚刚分析的,我们没有必要把数字信号转换为模拟信号再转回去,而DDWG 小组就致力于通过DVI 把这一理论转化为现实。

目前DVI 系统的规格已经比较成熟了:显卡产生的数字信号(包括控制信息和数据信息)由发送器按照TMDS 协议编码后通过TMDS 通道(至少要包含4条数据线:RGB 三种信号和时钟信号)发送给接收器,经过解码送给数字显示设备。

由于TMDS 协议本身就是Silicon Image制定的算法,因此Silicon Image制造的发送器和接收器自然是最佳选择。

DVI 1.0标准的原理图根据DVI标准,一条TMDS通道可以达到165MHz的工作频率和10-bit接口,也就是可以提供1.65Gbps的带宽,这足以应付1920*1080/60Hz的显示要求。

SCART plug & connector: CENELEC (ComitéEuropéen de Normalisation Electrotechnique) EN 50 049-1 / IEC 933-1Pin No. Signal Inter Conne-ction Pin No.1 Audio right channel output (0.5 Vrms, < 1K ohms) 22 Audio right channel input (0.5 Vrms, > 10K ohms) 13 Audio left channel output (0.5 Vrms, < 1K ohms) 64 Audio ground 45 Blue signal ground 56 Audio left channel input (0.5 Vrms, > 10K ohms) 37 Blue signal I/O (0.7 Vp-p, 75 ohms) 78 Function switching I/O (L: < 2V, H: > 10V, 10K ohms) 89 Green signal ground 910 Intercommunication data line No. 1 1011 Green signal I/O (0.7 Vp-p, 75 ohms) 1112 Intercommunication data line No. 2 1213 Red signal ground 1314 Blanking signal ground 1415 Red signal I/O (0.7 Vp-p, 75 ohms) 1516 Blanking signal I/O (L: < 0.4V, H: >1.0V, 75 ohms) 1617 Composite video signal ground 1818 Blanking signal ground 1719 Composite video signal output (1 Vp-p, 75 ohms, sync: negative) 2020 Composite video signal input (1 Vp-p, 75 ohms, sync: negative) 1921 Plug shield (common ground) 21此主题相关图片如下:EIAJ RGB plug & connector: EIAJ TTC-003Outlook of plug and connector including pin assignment are the same as SCART plug and connect orPin No. Signal Inter Conne-ction Pin No.1 Audio left channel input (0.40 mVrms, > 47K ohms) 12 Audio left channel output (0.40 mVrms, > 10K ohms) 23 Audio ground 34 Audio ground 45 Audio right channel input (0.40 mVrms, > 47K ohms) 66 Audio right channel output (0.40 mVrms, > 10K ohms) 57 Video ground 78 Video ground 89 CVBS input (1 Vp-p, 75 ohms, sync: negative) 1010 CVBS output (1 Vp-p, 75 ohms, sync: negative) 911 AV control input 1112 Ym input (switch for R, G & B signal to half tone level, L: < 0.4,H: > 1.0, 75 ohms) 1213 Red signal ground 1314 Ground 1415 Red signal I/O (0.7 Vp-p, 75 ohms) 1516 Ys input (switch for R, G & B signal from/to internal and external,L: < 0.4, H: > 1.0, 75 ohms) 1617 Green signal ground 1718 Blue signal ground 1819 Green signal I/O (0.7 Vp-p, 75 ohms) 1920 Blue signal I/O (0.7 Vp-p, 75 ohms) 2021 Plug shield 21S-connector: EIAJ CP-1211, IEC 84(s)80Pin No. Signal1 Luminance (Y) signal ground2 Chrominance (C) signal ground3 Luminance (Y) signal I/O (1 Vp-p, 75 ohms, sync: negative)4 Chrominance (C) signal I/O (burst: 0.286 Vp-p, 75 ohms)S1 and S2 connectorPin No. S1 connector S2 connector1 Luminance (Y) signal ground Luminance (Y) signal ground2 Chrominance (C) signal ground Chrominance (C) signal ground3 Luminance (Y) signal I/O (1 Vp-p, 75 ohms, sync: negative) Luminance (Y) signal I/O (1 Vp-p, 7 5 ohms, sync: negative)4 Chrominance (C) signal I/O (burst: 0.286 Vp-p, 75 ohms)Squeeze control input:+ 5V DC / >100KW Chrominance (C) signal I/O (burst: 0.286 Vp-p, 75 ohms)Squeeze control input:+ 5V DC / >100KWLetterbox control input:+ 2.2V DC / >100KWEIAJ D-connector D1/2/3/4/5: EIAJ RC-5237Pin No. Signal1 Y signal I/O (+700 mV & sync: +/-300 mV *1, 75 ohms)2 Y_GND3 PB (+/- 350 mV, 75 ohms)4 PB_GND5 PR (+/- 350 mV, 75 ohms)6 PR_GND7 Reserved line 18 Line 1 (0V: 525 lines, 2.2V: 750 lines, 5V: 1125 lines)9 Line 2 (0V: 59.94i / 60i, 2.2V: -, 5V: 59.94p / 60p)10 Reserved line 211 Line 3 (0V: 4:3, 2.2V: 4:3 letter box, 5V: 16:9)12 Plug insert detect GND13 Reserved line 314 Plug insert detect (output: 10K ohms, input: >100K ohms)hooks Shell GND*1: for 1125i and 750p. -300mV for 525p/525i, superimposed in Y signal Note: Indication for video signal format (i: interlace, p: progressive)D1: 525iD2: 525i, 525pD3: 525i, 525p, 1125iD4: 525i, 525p, 1125i, 750pD5: 525i, 525p, 1125i, 750p, 1125pVESA DFP connector: VESA (Video Electronics Standards Association) Digital Flat Panel (DFP) Sta ndardPin No. Signal Name Signal1 TX1+ TMDS positive differential output, channel 12 TX1- TMDS negative differential output, channel 13 SHLD1 Shield for TMDS channel 14 SHLDC Shield for TMDS clock5 TXC+ TMDS positive differential output, reference clock6 TXC- TMDS negative differential output, reference clock7 GND Logic Ground8 +5V Logic +5V DC Supply from the Host9 No Connect No Connection10 No Connect No Connection11 TX2+ TMDS positive differential output, channel 212 TX2- TMDS negative differential output, channel 213 SHLD2 Shield for TMDS channel 214 SHLD0 Shield for TMDS channel 015 TX0+ TMDS positive differential output, channel 016 TX0- TMDS negative differential output, channel 017 No Connect No Connection18 HPD Hot Plug Detection (+5V DC to Host)19 DDC_DAT DDC2B Data20 DDC_CLK DDC2B ClockTMDSTM: Transition Minimized Differential SignalingDDC: Display Data ChannelDDC2B: Simplest of the DDC modes defined in the VESA DDC standard此主题相关图片如下:VESA P&D connector: Plug and Display Standard (P&DTM)Pin No. SignalPin No. Signal1 TMDS Data2 + 16 USB data +2 TMDS Data2 - 17 USB data -3 TMDS Data return 18 1394 outer sahield (optional) & Charge Power return4 Unused 19 1394 Vg5 Unused 20 1394 Vp6 Unused 21 TMDS Data0 +7 TMDS Clock return 22 TMDS Data0 -8 Charge power + 23 TMDS Data return9 1394 pair A, data - 24 Unused10 1394 pair A, data + 25 DDC return11 TMDS Data1 + 26 DDC data (SDA)12 TMDS Data1 - 27 DDC clock (SCL)13 TMDS Data return 28 +5V DC14 TMDS Clock + 29 1394 pair B, clock +15 TMDS Clock - 30 1394 pair B, clock -(TMDS: Trademark of Silicon Image, USB: universal serial bus, DDC: display data channel, SDA: s erial data, SCL: serial clock)此主题相关图片如下:IEEE 1394-1995:Pin No. Signal Name Signal Inter ConnectionInter Connection with i-Link1 VP Cable power 12 VG Cable ground 23 TPB* Strobe on receive, data on transmit (differential pair) 5 14 TPB 6 25 TPA* Strobe on receive, data on transmit (differential pair) 3 36 TPA 4 4i-Link: 4-pin type IEEE 1394-1995Pin No. Signal Name Signal Inter ConnectionInter Connection with 1394-19951 TPB* Strobe on receive, data on transmit (differential pair) 3 52 TPB 4 63 TPA* Strobe on receive, data on transmit (differential pair) 1 34 TPA 2 4此主题相关图片如下:VGA (15-pin Dsub connector: for analog interface of PC monitorPin No. SignalPin No. Signal1 Red video input 9 No pin2 Green video input 10 Digital ground3 Blue video input 11* Monitor ID 0 / Ground4 Monitor ID 2 / Ground 12* Monitor ID 1 / Serial data line (SDA)5* Digital ground / Self test 13 Horizontal sync / H+V6 Red video ground 14 Vertical sync (VCLK for DDC)7 Green video ground 15* Reserved / Data clock line (DCL)8 Blue video ground串口通信基本接线方法目前较为常用的串口有9针串口(DB9)和25针串口(DB25),通信距离较近时(<12m),可以用电缆线直接连接标准RS232端口(RS422,RS485较远),若距离较远,需附加调制解调器(MODEM)。

DVI接口的英文全称是Digital Visual Interface,其标准是1999年由Silicon Image、Intel、Compaq、IBM、HP、NEC、Fujitsu等公司共同组成数字显示工作组DDWG(Digital Display Working Group)推出的数字显示接口.目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的D/A(数字/模拟)转换器转变为R、G、B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

(CRT: PC to CRT: D/A)对于模拟显示设备,如模拟CRT显示器,信号被直接送到相应的处理电路,驱动控制显像管生成图像。

而对于LCD、DLP等数字显示设备,显示设备中需配置相应的A/D(模拟/数字)转换器,将模拟信号转变为数字信号。

在经过D/A和A/D2次转换后,不可避免地造成了一些图像细节的损失。

(PC to VGA: D/A, VGA to LCD:A/D)DVI标准由DDWG于1994年4月正式推出,它的基础是Silicon Image公司的PanalLink接口技术,PanalLink 接口技术采用的是最小化传输差分信号(Transition Minimized Differential Signaling,TMDS)作为基本电气连接。

计算机中生成的图像信息传送到显示处理单元(显卡)中,经处理并编码成数据信号,数据信号中包含了一些像素信息、同步信息以及一些控制信息,信息通过3个通道输出。

同时还有一个通道用来传送使发送和接收端同步的时钟信号。

每一个通道中数据以差分信号方式传输,因此每一个通道需要2根传输线。

由于采用差分信号传输,数据发送和接收中识别的都是压差信号,因此传输线缆长度对信号影响较小,可以实现远距离的数据传输。

在接收端对接收到的数据进行解码,并处理生成图像信息供数字显示设备显示。

液晶电视接收机 DVI视频接口及显示规范1、范围本部分规定了液晶电视接收设备中视频DVI(Digital Visual Interface)信号外部接口互连的电特性标称值和机械配接要求。

本部分适用于液晶电视接收设备间标准清晰度电视模拟视频信号的连接。

2、术语及定义DVI全称为Digital Visual InterfaceTMDS(Transition MinimizedDifferential Signaling) 最小化传输差分信号; DVI接口利用T.M.D.S.链路将像素数据进行最小变换直流平衡编码,实现了高速实时数字显示数据传输.3、DVI概述及工作原理与标准3.3.1、DVI有DVI1.0和DVI2.0两种标准,其中DVI1.0仅用了其中的一组信号传输信道,传输图像的最高像素时钟为165M(1600RGB*1200@60Hz,UXGA),信道中的最高信号传输码流为1.65GHz。

DVI2.0则用了全部的两组信号传输信道,传输图像的最高像素时钟为330M,每组信道中的最高信号传输码流也为1.65GHz。

在显示设备中,目前还没有DVI2.0的应用,因此本文所讨论的DVI都是指DVI1.0标准。

连接规定及电气性能要求如表1所示。

3.3.2、DVI是基于TMDS(Transition Minimized Differential Signaling,转换最小差分信号)技术来传输数字信号,TMDS运用先进的编码算法把8bit数据(R、G、B中的每路基色信号)通过最小转换编码为10bit数据(包含行场同步信息、时钟信息、数据DE、纠错等),经过DC平衡后,采用差分信号传输数据,它和LVDS、TTL相比有较好的电磁兼容性能,可以用低成本的专用电缆实现长距离、高质量的数字信号传输。

TMDS技术的连接传输结构如图1所示。

图13.3.3 DVI数字信号传输有单连接(Single Link)和双连接(Dual Link)两种方式,对于单连接,仅用图1所示的1/2、 9/10、17/18脚传输,它的传输速率可达4.9Gbps,双连接可达9.9Gbps。

DisplayPort接口关于DisplayPort标准:Displayport接口视频电子标准协会Video Electronics Standards Association(VESA)公布了DisplayPort显示接口标准的最终版本:DisplayPort 1.0。

作为DVI的继任者,DisplayPort将在传输视频信号的同时加入对高清音频信号传输的支持,同时支持更高的分辨率和刷新率。

根据设计,DisplayPort既支持外置显示连接,也支持内置显示连接。

VESA希望笔记本厂商不仅使用DisplayPort连接独立显示器,也能使用它来直接连接液晶显示屏和主板,方便笔记本的升级。

为此,DisplayPort接口也设计得非常小巧,既方便笔记本的使用,也允许显卡配置多个接口。

DisplayPort 1.0规格支持单通道、单向、四线路连接,数据传输率10.8Gbps,足以传送未经压缩的视频和相关音频,同时还支持1Mbps的双向辅助通道,供设备控制之用,此外还支持8位和10位颜色。

在数据传输上,DisplayPort使用了“micro-packetised”格式。

VESA还表示,DisplayPort具备高度的可扩展性,可以在今后不断加入更多新内容。

与消费电子领域内的HDCP类似,DisplayPort也可以通过128位AES加密实现对HD视频数据的拷贝保护。

事实上,VESA也盯紧了消费电子市场,声称DisplayPort同样可以很方便地连接电视、DVD播放器等设备。

VESA在一年前左右开始开发DisplayPort,而之后不久,特别利益组织(SIG)提出了UDI(通用显示界面),可以同时兼容HDMI和DVI,而这一点正是DisplayPort所缺乏的。

不过,UDI虽然可以通过HDMI支持HDCP反盗版系统,但就像DVI,或者说不像HDMI 和DisplayPort,它不支持音频信号传输。

UDI 1.0预计本季度完成。

数字视频接口标准与高宽带数字内容保护规范一一--DVI.HDMI and HDCP内容简介“本文介绍了目前流行的各类数字平板显示器和HDTV上普遍配置的数字视频接口(DVI)和高清晰度数字多媒体接口(HDMI)这两个标准接口的国际规范,并详细的描述了这两种接口所包含的HDCP规范,最后还给出了HDCP规范在DVI接口上的应用原理。

关键字:数字视频接口,高清晰度数字多媒体接口,最小化传输差分信号,平板显示器,高宽带内容保护,密钥,数模转换电路,模数转换电路,接口。

Key Words:DVI,HDMI,TMDS,HDCP, FPD,Secret Keys, A/D, D/A, Interface一、概述:在以PDP,DLP,LCD—TV等为代表的数字显示器件开始进入日常生活的时候,传统的音视频输入输出接口,显然已经不能适应现今越来越多的各种各样数字音视频播放设备与数字式显示接收设备的连接,取而代之的将是全新的数字音视频接口规范.在进行数字音视频产品研发的同时,对信号接口的应用研究同样是研发工作中一项不可回避的任务.’二、DVI接口:很长时间以来,大多数计算机与外部显示设备都是通过模拟VGA接口相连的。

计算机内部以数字形式生成的图形,图像信号要经过显卡中的D/A转换电路,转换成模拟的R.G.B三原色和行,场同步信号,才能被模拟显示设备(主要是CRT显示器)所显示。

当计算机与数字显示终端相连接时,显卡中已经D/A转换过的模拟信号需要再经过A/D电路转换成数字信号,才能被数字显示终端所显示。

在经过D/A和A/D两次转换后,计算机输出的信号不可避免的会造成许多图像细节的损失并相应增加设备的制造成本。

针对计算机与数字显示终端的连接接口,1998年由Silicon Iamge.Inter.Compaq.IBM.HP.NEC.Fujitsa等公司共同成立了数字显示工作组DDWG,并于1999年4月推出了数字视频接口标准DVI。

音视频常见接口视频接口:1、HDMI—高清接口、数字接口、可传音频最长可以传输30米,建议在7.5米以内。

高清晰度多媒体接口(英文:High Defini tion Multimedia In terface ,HDMI)是一种数字化视频/音频接口技术,最高数据传输速度为5Gbps。

为家庭影音常用接口。

2002年12月9日正式发布了HDMI 1.0版标准,目前为1.4a版。

2、DVI—高清接口、模拟/数字接口、不可传音频5M以内DV( Digital Visual In terface),即数字视频接口。

它是1999 年由DDWG( Digital Display Worki ng Group,数字显示工作组)推出的接口标准。

DVI-D只能接收数字信号DVI-I可同时兼容模拟和数字信号DVf-l (DVI Digital & Analog) Single Link 单逋道DVI-I DVM (DVI Digital & Analog)Dua^Link 双通DVI~| DVI^D (DVI Digital) Single Link 单通道DVI-DDVID (pvrOigitaQ Dual Link 双通道DVI-0SuperVGA, HDl5d Analog only 模拟接口VGA3、AV—标清接口、模拟接口AV接口又称(RCA算是出现比较早的一种接口,它由红、白、黄三种颜色的线组成,其中黄线为视频传输线,红色和白色则是负责左右声道的声音传输。

syv 75-5是300米?4、S-Video —标清接口、模拟接口无信号衰减最大长度是 1.8M全称是Separate Video,也称为SUPER VIDEO。

只是一种增强型AV 端子。

S端子也是非常常见的接口,其全称是Separate Video,也称为SUPER VIDEO S指的是“ SEPARAT分离)”,它将亮度和色度分离输出,避免了混合视讯讯号输出时亮度和色度的相互干扰。

数字视频接口——DVI 1.0数字视频接口——DVI 1.0摘要:介绍了新型数字视频接口的发展背景和技术优势,详细分析了DVI1.0的通信协议、T.M.D.S.的链路构成、信号特性、编码及解码算法,特别针对实际应用,分析了DVI接口的时钟构成,最后就显示相关的DDC、EDID、HPD等协议进行了简单介绍。

关键词:数字视频接口(DVI)最小变换差分信号(T.M.D.S.)信号编码锁相环1背景介绍二十一世纪刚刚显现第一缕曙光,正当人们享受着以摩尔定律递增的高速微处理器时,一种新型的视频接口技术将带给人们更加绚丽多彩的视觉感受。

这就是业界刚刚发展起来的DVI?DigitalVisualInterface?数字视频接口技术。

随着以LCD为代表的数字平板显示技术的飞速发展,DVI必将迅速成为计算机显示的标准视频接口。

随着对绿色显示观念的倡导,CRT显示已由球面发展到柱面,又从柱面发展到纯平显示,人们对屏幕刷新率和图像几何失真要求愈来愈高,传统模拟VGA视频接口+CRT或LCD显示器的图像显示能力越来越捉襟见肘。

制造成本的不断降低,使LCD等平板显示技术已逐步取代传统的CRT显示器成为PC机显示器的主流。

由于要与传统的VGA模拟接口兼容,其内部不得不内置一级ADC?数模转换?及PLL?锁相环?电路,将模拟的视频信号转化成数字信号再进行显示,还要进一步针对CRT显示的值进行校正,得到适合LCD象素特性的灰度信号。

这样一系列中间环节的转换,加上模拟传输环节中难以抑制的噪声干扰问题,使得此类平板显示的图像信息丢失,并随着分辨率和场频的提高而加重。

以LCD、PDP、LED、OLED等为代表的平板显示(包括数字投影仪)的蓬勃发展,对数字视频接口技术提出了迫切要求。

DVI数字视频接口就是在这种趋势下产生的。

DVI由Intel、SiliconImage、Compaq、FujitsuLimited、Hewlett-PackardCompany、IBM、NEC合作提出的一种数字视频接口标准,很好地解决了上述问题,而且还兼容了传统的VGA接口,是目前极具发展前途的一种PC机视频接口标准。

DVI数字显示接口标准简介数字显示接口(Digital Visual Interface,DVI)是一种适应数字平板显示器飞速发展而产生的显示接口。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的D/A(数字/模拟)转换器转变为R、G、B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

对于模拟显示设备,如CRT显示器,信号被直接送到相应的处理电路,驱动控制显像管生成图像。

而对于LCD、DLP等数字显示设备,显示设备中需配置相应的A/D(模拟/数字)转换器,将模拟信号转变为数字信号。

在经过D/A和A/D两次转换后,不可避免地造成了一些图像细节的损失。

在DVI之前也存在一些数字接口标准,但都未能成为工业标准。

目前便携系统中采用低电压差分信令(Low Voltage Differential Signaling,LVDS)数字接口连接液晶显示屏,但是这一技术不太适合桌面显示器。

其他数字接口,如数字平板标准(Digital Flat Panel,DFP)、视频电子标准协会的即插即显标准(VESA(r)Plug and Display)、以及OpenLDI标准也未能被业界普遍接受。

相反,DVI标准有望成为平板显示的标准数字接口,这是由Silicon Image、Intel、Compaq、IBM等公司共同组成的数字显示工作组(Digital Display Working Group,DDWG)于1999年4月推出的数字显示接口标准。

TMDSDVI标准的基础是Silicon Image公司的PanelLink接口技术,这是一种高速串行接口,采用的是跃变最小化差分信令(Transition Minimized Differential Signaling,TMDS)传送数据到监视器。

TMDO通过“on”和“off”状态间的跃变来传送数据,采用布尔异或(XOR)或者异非或(XNOR)操作这一先进的编码算法来最小化跃变,以避免额外的电磁干扰(EMI)对电缆的影响,并附加了平衡直流(DC)信号的操作。

DVI数字视频接口简介图片:DVI是Digital Visual Interface 的缩写,全称是数字视频介面。

DVI是个非常重要的数字视频新标准,这个标准是由数字视频工作组(Digital Display Working Group,简称DDWG)推出的,其中的主要成员包括电脑和数字视频业界的领导者Intel和Silicon Image。

传统的视频接口都是模拟方式的复合视频(Video)、S视频(S-Video)、色差(Y/Cr/Cb)和VGA等形态,对于目前日益增多的DVD、PC、HDTV等数字视频信号传输来说,必然会带来数模转换过程的损失和传输失真,也不利于发挥数字电视和DLP、LCD等点阵显示设备的优势,DDWG从成立开始就致力于显示设备的数字化,DVI就是由DDWG所发展的数字视频传输介面。

DVI的数据传输采用TMDS协议,由Silicon Image所开发,业界也称之为Panel Link,主要这种传输协议当初的目的就是针对各种新型的平面数字显示新器件而设计。

正因为如此,Silicon Image 的IC芯片也更为常见。

按照DVI的规格要求,一个TMDS链路要包含三个数据通道(RGB)和一个时钟控制通道组成。

依照DVI的规格,一个TMDS链路能够工作在165MHz。

这样一个10位的TMDS链路就可以提供1.65Gb带宽,足以满足一台数字液晶显示器1920 x 1080分辨率下60Hz 刷新率的需要。

显示器最大分辨率取决于显示分辨率需要的带宽及显卡输出功效。

为保持规格的灵活性,DVI可以使用第二条TMDS链路。

第二条TMDS链路必须和第一条的操作周期相同,即要得到2Gb 带宽的话,每条TMDS链路的操作周期就都为100MHz (100MHz x 2 x 10位)。

正是由于拥有高带宽优势,DVI才比其它公司提出的解决方案更具备成为业界规范的潜力。

DVI 还具备一个极少使用的性能优势,它的规格允许在其信号端口上支持所有的模拟和数字接口。

普及DP/HDMI/DVI显示器接口详解目前游戏竞技玩家,专业制图用户越来越多,这就导致了各大应用设备也不断的提高。

用户对画面显示效果也同样高了不少,特别是影音用户和游戏玩家,他们对画质的要求要求都非常高,就目前的现状来看,画质的水平也有不同的分化,这就要说接口的作用了,今天笔者就为大家讲一个近期最热的三种接口,也是现在对画质要求有一定特点的用户进行一下解析。

DP/HDMI/DVI接口DP/HDMI/DVI有什么区别?HDMI的英文全称是“High Definition Multimedia Interface”,中文的意思是高清晰度多媒体接口。

HDMI接口可以提供高达5Gbps的数据传输带宽,可以传送无压缩的音频信号及高分辨率视频信号。

同时无需在信号传送前进行数/模或者模/数转换,可以保证最高质量的影音信号传送。

应用HDMI的好处是,只需要一条HDMI线,便可以同时传送影音信号,而不像现在需要多条线材来连接。

同时,由于无需进行数/模或者模/数转换,能取得更高的音频和视频传输质量。

DVI(Digital Video Interface),即数字视频接口。

是基于TMDS(Transition Minimized Differential Signaling),转换最小差分信号)技术来传输数字信号,TMDS运用先进的编码算法把8bit数据(R、G、B中的每路基色信号)通过最小转换编码为10bit数据(包含行场同步信息、时钟信息、数据DE、纠错等),经过DC平衡后,采用差分信号传输数据,它和LVDS、TTL相比有较好的电磁兼容性能,可以用低成本的专用电缆实现长距离、高质量的数字信号传输。

数字视频接口(DVI)是一种国际开放的接口标准,在PC、DVD、高清晰电视(HDTV)、高清晰投影仪等设备上有广泛的应用。

DP接口即DisplayPort接口,DisplayPort是由视频电子标准协会(VESA)发布的显示接口。

数字视频接口——DVI 1.0摘要:介绍了新型数字视频接口的发展背景和技术优势,详细分析了DVI1.0的通信协议、T.M.D.S.的链路构成、信号特性、编码及解码算法,特别针对实际应用,分析了DVI接口的时钟构成,最后就显示相关的DDC、EDID、HPD等协议进行了简单介绍。

关键词:数字视频接口(DVI)最小变换差分信号(T.M.D.S.)信号编码锁相环1背景介绍二十一世纪刚刚显现第一缕曙光,正当人们享受着以摩尔定律递增的高速微处理器时,一种新型的视频接口技术将带给人们更加绚丽多彩的视觉感受。

这就是业界刚刚发展起来的DVI DigitalVisualInterface 数字视频接口技术。

随着以LCD为代表的数字平板显示技术的飞速发展,DVI必将迅速成为计算机显示的标准视频接口。

随着对绿色显示观念的倡导,CRT显示已由球面发展到柱面,又从柱面发展到纯平显示,人们对屏幕刷新率和图像几何失真要求愈来愈高,传统模拟VGA视频接口+CRT或LCD显示器的图像显示能力越来越捉襟见肘。

制造成本的不断降低,使LCD等平板显示技术已逐步取代传统的CRT显示器成为PC机显示器的主流。

由于要与传统的VGA模拟接口兼容,其内部不得不内置一级ADC 数模转换 及PLL 锁相环 电路,将模拟的视频信号转化成数字信号再进行显示,还要进一步针对CRT显示的值进行校正,得到适合LCD象素特性的灰度信号。

这样一系列中间环节的转换,加上模拟传输环节中难以抑制的噪声干扰问题,使得此类平板显示的图像信息丢失,并随着分辨率和场频的提高而加重。

以LCD、PDP、LED、OLED等为代表的平板显示(包括数字投影仪)的蓬勃发展,对数字视频接口技术提出了迫切要求。

DVI数字视频接口就是在这种趋势下产生的。

DVI由Intel、SiliconImage、Compaq、FujitsuLimited、Hewlett-PackardCompany、IBM、NEC合作提出的一种数字视频接口标准,很好地解决了上述问题,而且还兼容了传统的VGA接口,是目前极具发展前途的一种PC机视频接口标准。

本文的目的在于使读者迅速掌握DVI的通信协议,从接口提取视频信息,摆脱对计算机内部复杂的硬件原理的研究,使DVI接口的高质量数字视频信息可以按用户的要求进行开发利用。

2DVI接口构成DVI接口利用最小变换差分信号—T.M.D.S. TransitionMinimizedDifferentialSignal 作为基本电气链接信号。

T.M.D.S.链路主要用于将图像数据传送到显示器。

DVI接口协议允许使用双T.M.D.S.链路结构,从而可以支持超大分辨率的显示设备。

T.M.D.S.通过先进的编码算法将8bit的象素数据转换成10bit的最小变换信号,削弱了传输电缆中交叉电磁干扰EMI,并且这种直流平衡的编码信号更有利于光纤传输。

另外这种先进的编码算法可以为接收端提供时钟恢复信号,并允许在较远距离传输时(一般小于5m)信号有较大的抖动误差。

2.1DVI体系结构要求DVI作为一种面向计算机开发的视频接口,要与现有的操作系统、硬件平台兼容,还要与以前的接口标准保持一定的兼容性。

图1是DVI接口T.M.D.S.的逻辑链路结构。

DVI支持即插即用功能(PlugandPlay)。

在系统启动时,DVI提供最低分辨率VGA640×480模式 系统通过DDC2B协议访问显示器,获得显示器对象素格式的支持情况,通过EDID数据获得关于显示器型号和现实能力的信息。

这些内容都是显示器制造商在显示器内部固化的一段数据,通过DDC DisplayDataChannel 向主机系统提供自身信息。

系统启动后会自动加载图形显示控制器(即显卡)的驱动程序。

根据用户提出的显示要求,即屏幕的分辨率、色深、刷新率,结合由DDC获得关于显示器的信息,确定T.M.D.S.的启用情况。

DVI的单T.M.D.S.只提供24bit色深,当用户要求的色深超过24bit时,并且系统已经确认显卡和显示器都支持双链路T.M.D.S.。

此时系统会启动双T.M.D.S.链路,链路0 数据通道0~2 传输24bit信息,其它颜色信息由链路1(数据通道3~5)传输;当用户的分辨率和刷新率要求超出单T.M.D.S.链路的传输能力时 单T.M.D.S.链路的最高象素传输频率为165MHz ,系统会启动链路1,链路0用来传输奇数象素信息,链路1用来传输偶数象素信息,并定义显示器上每一行的第一个象素为象素1,奇数象素。

由于双T.M.D.S.链路共用一条时钟回路,所以双链路工作时,链路的时钟频率为象素数据带宽的一半。

当然,DVI接口同样也支持热插拔(HotPlugDetection)和显示器电源管理等技术 还有对传统的模拟VGA的兼容等问题。

这些只是DVI作为一种接口标准必须做到的兼容性问题,并不代表DVI本质的先进性。

有关这些体系要求问题可参阅参考文献 1~3 。

2.2T.M.D.S.协议详解DVI接口的先进性体现在它可以将海量的显示信息高速地传送到显示器中去,T.M.D.S.先进的编码算法是其强大能力得以实现的根本。

下面将详细解释T.M.D.S.协议中与实际应用紧密相关的几个问题。

为了便于理解作以下规定:输入到编码器或由解码器输出的象素数据称为象素数据 PixelData ;由发送器送出的或输入到接收器的编码数据称为码元 Character 。

请注意:在DVI接口协议中并没有规定输入或输出的象素数据是串行的还是并行的,输入输出的数据格式留给芯片制造厂商灵活掌握,用户应根据自己的实际情况选用芯片型号。

2.2.1链路结构T.M.D.S.链路结构见图2。

图3是单链路T.M.D.S.结构图。

双链路结构与单链路很相似。

每个链路的发送器(Transmitter)中包含三个完全相同编码器(Encoder),每个编码器驱动一条串行T.M.D.S.通道(Channel)。

输入到每个编码器的数据包括8bit象素数据和2bit控制信号(见图3)。

在DE(DataEnable)信号的控制下,编码器在任何合法时钟驱动下,分别将象素数据和控制数据编码并由发送器将编码后的码元串行发送到T.M.D.S.链路上。

在DE有效期间(DE=1)对象素数据进行编码发送,在DE无效期间(DE=0)对控制数据进行编码发送。

无论是对二者中的哪一项进行编码,由编码器输出的都是串行的10bit码元,并且最低有效位先送出。

图3 单链路T.M.D.S.结构2.2.2时钟与同步问题时钟与同步是DVI信号处理过程中至关重要的一环。

以显卡中图形处理器提供的象素时钟(PixelClock)为参考时钟,在整个信号收发过程中,会存在三组不同频率的时钟信号,这三组时钟信号通过锁相环电路(PLL)进行同步控制。

从图3可知,以象素时钟的速度输入到编码器的8bit象素数据被变换成10bit的T.M.D.S.码元,在T.M.D.S.通道内串行传输。

所以T.M.D.S.码元要以10倍象素的时钟频率进行码元传输。

在接收端,若要正确判断所接收的码元就需要用高于码时钟 CharacterClock 的频率对输入信号进行采样,所以又存在一个采样时钟 SamplingClock 。

例如:TI公司提供的DVI接收芯片 6 采用4倍过采样技术对输入信号采样,在XGA分辨率(1024×768)、60Hz刷新率的情况下,象素时钟为65MHz,则T.M.D.S.码元时钟将为650MHz,采样时钟将达到2.6GHz。

T.M.D.S.的先进编码算法使得串行输出的码元流中包含了码元同步信息,利用PLL技术使接收器和解码器可以在串行的码元流中正确测定码元边界、解码象素数据。

在T.M.D.S.输出的编码中,代表象素数据的编码包含了5次或5次以下的变化信息,而代表控制信号的编码包含了7次以上的变换信息。

这些含有高变化信息的编码在显示的消隐时期内被送出。

解码器可以唯一确定地识别这些高变换码,PLL可以利用这些确定的信号作为相位校正的参考信号。

2.2.3T.M.D.S.编码与解码算法深入理解、灵活运用并实现这些先进的算法是芯片制造厂商最关心的问题。

本文从使用者的角度出发,以实用为原则对编码及解码算法进行分析。

从图3中可以看出,实际应用时最关心的行同步、场同步信号作为控制信息在蓝基色 Blue 7 0 被编码器编码发送;其他通道的控制信号CTL 0 3 或CTL 0 9 都应接逻辑0,其中CTL0可以提供用户使用,但有严格使用条件,非不得不用的情况下推荐接逻辑0。

T.M.D.S.的每一条通道都由连续输出的10bit串行编码驱动。

在显示的消隐 5 DE=0 时间段内编码器输出四个特定编码,详见图4,也就是前面所说的可被解码器唯一确定识别的四个编码。

在DE=1时编码过程分为两个阶段,第一阶段对8bit的象素数据进行最小变换生成9bit的最小变化码,其中最低有效位与象素数据的最低有效位相同,第9位为变换方式标志位:0表示对象素数据进行异或非 XNOR 变换,1表示进行异或 XOR 变换;第二阶段生成10bit的直流平衡码:如果上一次编码传输了过多的1且将要传输编码中1比0多,则将此次编码的低8位取反并在第10位置1,否则,将不作处理,直接传输。

每一条T.M.D.S.链路中含有与3个编码器对应的3个解码器。

T.M.D.S.的解码算法相对简单一些。

由于在消隐时间内传输了特定的四个编码,解码器可以判断DE的逻辑状态,若DE=0,则直接将对应的控制信号组合状态送出。

若DE=1,则根据第10位的情况决定低8位是否进行取反,根据第9位的信息决定对编码进行的变化方式:为1,进行XOR(异或)变换 为0,进行XNOR(异或非)变换。

在象素数据有效期间,行、场同步以及控制信息CTLX均保持恒定。

通过上述解码过程,行同步和场同步信号由蓝基色通道解调出来,结合另外两个通道解调出来的绿基色和红基色,就可以进行视频信息的数字方式显示了。

图5是T.M.D.S.的链路时序关系,其中tB是对消隐信号持续时间的要求,要求tB≥128Tpixel Tpixel为象素时钟周期。

tE和tR分别是编码和解码延迟时间,一般小于64Tpixel。

图5 T.M.D.S.的链路时序关系3DVI接口应用指南DVI接口提供了强大的数据传输率,其链路工作频率很高,所以对器件的供电电压、连接电缆的特性阻抗以及终端接插件的电气特性都有非常严格和详细的规定。

这些都是DVI相关器件厂商要严格遵循的技术指标。

表1给出了实际应用最为关心的五个工作参数,其他参数的详细解释见文献。

表2给出了DVI接口插头信号线的定义。

其中的DDC通道用于设备制造商向主机提供产品信息,这使DVI接口应用锦上添花。