chp5触发器

- 格式:ppt

- 大小:1.50 MB

- 文档页数:1

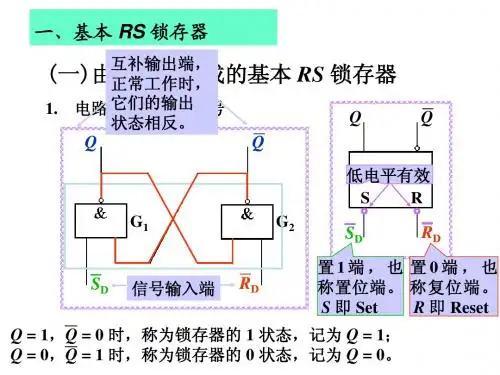

锁存器、触发器和寄存器分析触发器:flipflop,锁存器:latch,寄存器:register锁存器在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器.由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。

由于一个触发器能够存储一位二进制码,所以把n个触发器的时钟端口连接起来就能构成一个存储n位二进制码的寄存器。

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

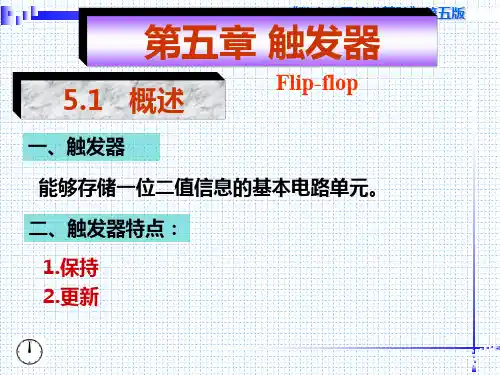

触发器触发器是边沿敏感的存储单元,数据存储的动作有某一信号的上升或者下降沿进行同步的。

在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器.由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。

由于一个触发器能够存储一位二进制码,所以把n个触发器的时钟端口连接起来就能构成一个存储n位二进制码的寄存器。

寄存器用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。

其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。

寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。

触发器是在时钟的沿进行数据的锁存的,而锁存器是用电平使能来锁存数据的。

所以触发器的Q输出端在每一个时钟沿都会被更新,而锁存器只能在使能电平有效器件才会被更新。

有一些教科书里的触发器实际是锁存器。

在FPGA设计中建议如果不是必须那么应该尽量使用触发器而不是锁存器。

钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器,钟控D触发器在使能情况下输出随输入变化,边沿触发器只有在边沿跳变的情况下输出才变化。

两个D锁存器可以构成一个D触发器,归根到底还是dff是边沿触发的,而latch是电平触发的。

锁存器的输出对输入透明的,输入是什么,输出就是什么,这就是锁存器不稳定的原因,而触发器是由两个锁存器构成的一个主从触发器,输出对输入是不透明的,必须在时钟的上升/下降沿才会将输入体现到输出,所以能够消除输入的毛刺信号。

555构成的电路(经典)作者:电子学习在线网来源:本站整理发布时间:2008-10-5 10:10:04 发布人:admin减小字体增大字体脉冲信号产生◆555构成的振荡器电路下图(a)为555定时器电路构成的振荡器电路,其中R A、R B、C为一个定时器件,其输出的波形为一个方波,其输出高电平的时间宽度为:T1=0.7(R A+R B)CT2=0.7R B C其总的输出方波的周期为:T=T1+T2=0.7(R A+2R B)C在上面的方波中其高电平的时间无法与低电平的时间相同,这是因为两个时间相同时,电阻RA就必须为0,这是不允许的(你可以自行分析一下)。

为了得到高、低电平时间相同(通常用占空比来表示,即占空比为50%)的方波,可通过对电路进行一些改进就可以了,图(b)就是改进型电路。

从上面可以看出由555构成的振荡器电路相当简单,但由于采用的是阻容器件作为定时器件的,其频率的稳定性不高,一般仅能用于报警器电路或频率稳定性要求不高的场合。

为了得到更高的频率稳定的性一般采用石英晶体振荡器电路。

◆CMOS石英晶体振荡器电路石英晶体一种具有较高频率稳定性的选频器件,广泛用于通信、定时等频率要求高的场合,下图(a)为石英晶体的符号用频率特性曲线,从特性曲线可以看出其具有较高的品质因素。

图(b)为CMOS石英晶体振荡器的典型电路,第一个非门与晶体、电阻、电容构成振荡电路,其输出接近为一个正弦波,第二个CMOS非门起到一个整形作用,将非方波整形为一个理想的方波。

在这里须强调的是,通常人们将晶体与晶振两个名词混淆,其实这是两个完全不同的两个东西,晶体是一个器件,通常为扁平封装或圆柱形金属封装的两脚踏实地器件,而晶振是一个电路,如上面的电路就是晶振,在电子器件商店也有一种四脚封装的晶振电路,其四个脚分别为:电源、地线、输出、空脚。

在使用和采购时一定要注意这两个的区别,否则会闹出笑话。

单稳态电路单稳态电路的特点在前面的触发器电路中,当输入时钟有效边沿时输出发生变化,这时输入无论如何变化,其输出保持稳定,其输出状态既可以是0,也可以是1,这种电路有两个稳定的状态,故将触发器电路又可称为双稳态触发器电路。

d触发器5分频电路代代码d触发器5分频电路代代码d触发器5分频电路是一种常用的电子电路,可以将输入信号进行分频,常用于计数器等电路中。

下面是d触发器5分频电路的代代码:```C++void setup() {pinMode(2, INPUT);pinMode(4, OUTPUT);}void loop() {boolean state = digitalRead(2);if(state == HIGH) {digitalWrite(4, HIGH);delayMicroseconds(10);digitalWrite(4, LOW);delayMicroseconds(10);}else {digitalWrite(4, LOW);}}```此代码实现了d触发器5分频电路的功能,将输入信号分成5部分,输出到4号引脚上。

接下来,我们将针对代码进行详细解释。

代码分析首先,在setup函数中,将2号引脚设置为输入,4号引脚设置为输出:```C++pinMode(2, INPUT);pinMode(4, OUTPUT);```在loop函数中,首先读取2号引脚的输入信号:```C++boolean state = digitalRead(2);```然后,判断输入信号是否为HIGH:```C++if(state == HIGH) {// do something}else {// do something}```如果输入信号为HIGH,即代表输入信号发生了变化,需要进行分频操作。

接下来,通过digitalWrite函数控制4号引脚输出HIGH信号10微秒,然后再控制4号引脚输出LOW信号10微秒:```C++digitalWrite(4, HIGH);delayMicroseconds(10);digitalWrite(4, LOW);delayMicroseconds(10);```这个过程将重复5次,即实现了d触发器5分频的功能。