PLL时钟

- 格式:doc

- 大小:43.50 KB

- 文档页数:2

vivado pll 时钟资源single pin和global bufg 和no buffer怎么选择1. IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。

所有从全局时钟管脚输入的信号必须经过IBUFG单元,否则在布局布线时会报错。

IBUFG支持AG P、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和SSTL等多种格式的IO标准。

2. IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBU FGDS作为全局时钟输入缓冲。

IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL和ULVDS 等多种格式的IO标准。

3. BUFG是全局缓冲,它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。

4. BUFGCE是带有时钟使能端的全局缓冲。

它有一个输入I、一个使能端CE和一个输出端O。

只有当BUFGCE的使能端CE有效(高电平)时,BUFGCE才有输出。

5. BUFGMUX是全局时钟选择缓冲,它有I0和I1两个输入,一个控制端S,一个输出端O。

当S为低电平时输出时钟为I0,反之为I1。

需要指出的是BUFGMUX的应用十分灵活,I0和I1两个输入时钟甚至可以为异步关系。

6. BUFGP相当于IBUG加上BUFG。

7. BUFGDLL是全局缓冲延迟锁相环,相当于BUFG与DLL的结合。

BUFGDLL在早期设计中经常使用,用以完成全局时钟的同步和驱动等功能。

随着数字时钟管理单元(DCM)的日益完善,目前BUFGDLL的应用已经逐渐被DCM所取代。

8. DCM即数字时钟管理单元,主要完成时钟的同步、移相、分频、倍频和去抖动等。

DCM与全局时钟有着密不可分的联系,为了达到最小的延迟和抖动,几乎所有的DCM应用都要使用全局缓冲资源。

PLL锁相环时钟设定未配置锁相环时(OSCCLK_PLLSEL=0):总线频率=外部晶振频率(OSCCLK)/2配置锁相环时(OSCCLK_PLLSEL=1): 系统时钟由锁相环提供,总线频率=倍频后频率(PLLCLK)/2时钟频率计算方法Fvco=2*Fosc*(SYNDIN+1)/(REFDIV+1)Fpll=Fvco/(2*POSTDIV)当POSTDIV=0时,Fpll=FvcoFbus=Fpll/2CRGFLG_LOCK==1时,说明PLLCLK稳定,可输出。

锁相环从设定到稳定需要时间,故期间应加几条空语句。

例程:void CLK_Init(void) {CLKSEL=0x00; //选择OSCCLK为系统时钟源16M PLLCTL_PLLON=1; //开启锁相环,锁相环电路允许//频率设定80M时SYNR = 0xc0 | 0x09;REFDV = 0x80 | 0x01;POSTDIV = 0x00; // PLLCLOCK=2*osc*(1+SYNR)/(1+REFDV)=160MHz; _asm(nop);_asm(nop);while(!CRGFLG_LOCK); // 时钟频率已稳定,锁相环频率锁定CLKSEL_PLLSEL=1; //使能锁相环时钟}PWM模块PWME:PWM允许寄存器,置1时允许输出。

PWMPOL:极性寄存器。

置1时首先输出高电平。

2、3、6、7、置1时clock SB 作为时钟源,置0时clock B作为时钟源PWMCAE:居中对齐允许寄存器,只有当通道输出禁止时才能设置此寄存器置1时为居中对齐,置0时左对齐PWMSCLA:比例因子寄存器A;用于提供clock SA的比例因子Clock SA的时钟频率= clock A/(2*PWMSCLA)当PWMSCLA为0时比例因子默认为256. CLOCKSB 计算方法类似,寄存器为PWMSCLB。

PWMCNTx:通道计数寄存器,一般设置值为0x00;PWMPERx:周期寄存器;左对齐时周期计算方法:PWMxPeriod=指定时钟周期乘以PWMPERx的值居中对齐时=指定时钟周期乘PWMPERx的值再乘2;PWMDTYx:占空比寄存器。

pll 时钟相位的作用

PLL(Phase-Locked Loop,锁相环)时钟相位的作用在于:

1.调整时钟频率:通过PLL的频率合成、频率分频和频率锁定等功能,可以

将输入的时钟信号(如50MHz)转换成符合特定要求的输出时钟信号(如150MHz)。

同时,PLL能够实现时钟频率的稳定性控制和抖动降低。

2.保持时钟相位:由于时钟信号在传输过程中容易因信号衰减、干扰等原因

而发生相位偏移或漂移,PLL通过引入反馈机制,使输出时钟与输入时钟在相位上保持一致,消除了输入时钟信号的相位抖动和漂移问题,提高了时序稳定性和系统性能。

PLL到底是个啥么东西呢?——————————————————更新于20180826————————————————————————————PLL:完成两个电信号的相位同步的⾃闭环控制系统叫锁相环。

⽤电压控制延时,⽤到了VCO来实现DLL中类似的延时功能,是模拟电路。

DLL:基于数字抽样⽅式实现的,在输⼊时钟和反馈时钟之间插⼊延时,使得输⼊和反馈时钟的上升沿⼀致来实现的。

DCM:Delay Locked-Loop数字延迟锁相环,其输⼊参数包括输⼊中频率范围,输出时钟频率范围、输⼊输出时钟允许抖动范围等。

PLL和DLL都可以实现倍频、分频占空⽐调整,但是DLL的数字电路特性导致其只能是实现2、4等倍频,⽽PLL的调整范围则要⼤⼀些。

PLL在时钟综合⽅⾯要更好些,但是抗噪声能⼒相对较差,DLL在power jitter precision⽅⾯要优于PLL。

DCM⽐DLL在时钟管理控制⽅⾯功能更强⼤,包括了消除时钟延时、频率合成、相位调整等系统⽅⾯的要求DCM优点:1实现零时钟延时,消除了时间分配延时,实现了时钟闭环控制2可⽤于外部芯⽚的同步,使得内外时钟⼀体化。

DCM相对PLL⽽⾔1 DCM只⽀持90,180,270相位延迟,PLL更灵活1 DCM只⽀持2-16⼩数分频以及2倍频2 DCM数字模块占⾯积⼩,灵活,但是在噪声和jitter相对PLL⼤得多3 PLL模拟电路,输出时钟质量要⾼,但是占⽤的⾯积也⼤。

————————————————————————————————————————————————————————PLL的出现是为了解决这样⼀个问题的:就是外部输⼊的信号实际上与内部时钟振荡信号是完全不同步的,为了解决这个问题,我们想到了⽤改进⼯艺的⽅法,但实际上晶振由于⼯艺与成本原因,做不到很⾼的频率,⽽在需要⾼频应⽤时,有相应的器件VCO,实现转成⾼频,但并不稳定,故利⽤锁相环路就可以实现稳定且⾼频的时脉冲讯号。

pll的参考时钟相噪要求

PLL的参考时钟相噪要求取决于系统的具体应用和性能指标。

一般来说,对于高性能的通信系统、雷达系统等,对PLL的参考时钟相噪要求较高,通常要求其相位噪声低于-100dBc/Hz或更低。

而对于一些对性能要求不高的应用,如普通时钟发生器等,对PLL的参考时钟相噪要求较低,可能只要求达到-120dBc/Hz或更低。

PLL的参考时钟相噪主要取决于参考源的频率稳定性和噪声特性,以及PLL电路的设计和性能。

为了获得更好的性能,可以选择低噪声、高稳定的参考源,并在PLL设计中采用低噪声的放大器和滤波器等元件,以及优化PLL的环路带宽和滤波器参数等。

需要注意的是,PLL的参考时钟相噪要求并不是唯一决定系统性能的因素,还需要综合考虑其他因素,如输出信号的频率范围、频谱纯度、杂散分量等。

因此,在选择PLL时,需要根据实际需求综合考虑其各项性能指标。

Intel® Agilex™时钟和PLL用户指南针对Intel® Quartus® Prime设计套件的更新:20.3本翻译版本仅供参考,如果本翻译版本与其英文版本存在差异,则以英文版本为准。

某些翻译版本尚未更新对应到最新的英文版本,请参考英文版本以获取最新信息。

在线版本ID: 683761内容内容1. Intel® Agilex™时钟和PLL概述 (4)1.1. 时钟网络概述 (4)1.2. PLL概述 (4)2. Intel Agilex 时钟和PLL架构和功能特性 (5)2.1. 时钟网络架构和功能特性 (5)2.1.1. 时钟网络架构 (5)2.1.2. 时钟资源 (7)2.1.3. 时钟控制功能 (8)2.2. PLL架构和功能特性 (10)2.2.1. PLL功能特性 (10)2.2.2. PLL使用 (11)2.2.3. PLL位置 (12)2.2.4. PLL架构 (12)2.2.5. PLL控制信号 (13)2.2.6. PLL反馈模式 (14)2.2.7. 时钟乘法和除法 (18)2.2.8. 可编程相移 (19)2.2.9. 可编程占空比 (19)2.2.10. PLL级联 (19)2.2.11. PLL输入时钟切换 (20)2.2.12. PLL重配置和动态相移 (24)2.2.13. PLL校准 (24)3. Intel Agilex 时钟和PLL设计考量 (26)3.1. 指南:时钟切换 (26)3.2. 指南:时序收敛 (27)3.3. 指南:复位PLL (27)3.4. 指南:配置约束 (27)3.5. 指南:I/O PLL重配置 (27)3.6. 时钟约束 (28)3.7. IP核约束 (28)3.8. 指南:使用从LVDS SERDES Intel FPGA IP来的tx_outclk端口,实现f OUT_EXT≥ 300Mhz的5%占空比 (28)4. Clock Control Intel FPGA IP核 (29)4.1. Clock Control Intel FPGA IP的发布信息 (29)4.2. Clock Control IP核参数 (29)4.3. Clock Control IP核端口和信号 (30)5. IOPLL Intel FPGA IP核 (31)5.1. IOPLL Intel FPGA IP的发布信息 (31)5.2. .mif文件生成 (31)5.2.1. 生成一个新的.mif文件 (32)5.2.2. 对现有.mif文件添加配置 (32)5.3. IP-XACT文件生成 (32)内容5.3.1. 生成一个新的IP-XACT文件 (32)5.4. IOPLL IP核参数 (32)5.4.1. IOPLL IP核参数:PLL选项卡 (33)5.4.2. IOPLL IP核参数:Settings选项卡 (35)5.4.3. IOPLL IP核参数:Cascading选项卡 (36)5.4.4. IOPLL IP核参数 - Dynamic Reconfiguration选项卡 (36)5.4.5. IOPLL IP核参数 - Advanced Parameters选项卡 (37)5.5. IOPLL IP核端口和信号 (37)6. Intel FPGA IP核 (39)6.1. IOPLL Reconfig Intel FPGA IP的发布信息 (39)6.2. 实现IOPLL Reconfig IP核中的I/O PLL重配置 (40)6.2.1. IOPLL与IOPLL Reconfig IP核之间的连接 (40)6.2.2. 连接IOPLL和IOPLL Reconfig IP核 (40)6.3. IOPLL Reconfig IP核重配置模式 (41)6.3.1. .mif流重配置 (41)6.3.2. 高级模式重配置 (42)6.3.3. 时钟门控重新配置 (43)6.3.4. 动态相移重配置 (43)6.4. IOPLL Reconfig IP核中的Avalon Memory-Mapped Interface端口 (43)6.5. 地址总线核数据总线设置 (44)6.5.1. 高级模式重配置的地址总线和数据总线设置 (44)6.5.2. 针对时钟门控重配置的输出时钟和相应数据位设置 (50)6.5.3. 针对IOPLL Reconfig IP核动态相移的数据总线设置 (51)6.6. 设计实例 (51)6.6.1. 重配置选项:使用IOPLL Reconfig IP核的.mif流重配置 (52)6.6.2. 重配置选项:使用IOPLL Reconfig IP核的高级模式重配置和重新校准 (52)6.6.3. 重配置选项:使用IOPLL Reconfig IP核的时钟门控重配置 (53)7. Intel Agilex 时钟和PLL用户指南存档 (54)8. Intel Agilex 时钟和PLL用户指南文档修订历史 (55)1. Intel® Agilex™时钟和PLL概述1.1. 时钟网络概述Intel® Agilex™器件包含将信号分布到整个架构的专用资源。

关于DSP 的时钟以及PLL 问题作者:Free 文章来源:Free 点击数:995 更新时间:2009-2-121、时钟输入问题时钟输入:对于280x 系列的dsp 的时钟选择有多种,包括:晶体经过X1、X2输入:需要将CLKIN 连接到参考地,否则在用FLASH 运行程序的时候,将无法运行。

;外部时钟经过CLKIN 引脚输入:允许时钟电压是3.3V 。

需要将X1引脚接到参考地。

X2悬空。

外部时钟经过X1引脚输入。

允许时钟电压是1.8V 。

需要将CLKIN 连接到参考地,X2悬空。

2、PLL 问题PLL 作为DSP 的时钟重要组成部分,它除了提高系统内部SYSCLKOUT 的频率之外,还有一个重要的用途就是监视外部时钟是不是很好的为DSP 内部提供系统时钟。

如果系统让PLL 处于使能状态,那么就能够监视PPLSTS 寄存器中的MCLKSTS 位的状态即可。

如果MCLKSTS 被置位。

那么软件就要恰当的措施保证系统不出现事故。

这种措施包括使系统停机、使系统复位。

1、对PLL 操作需要注意的问题需要采用正确的步骤来更新PLL 控制寄存器。

当DSP 工作在“limp mode ”状态下,禁止写PLLCR 。

特别是在系统上电以后;也禁止进入HALT 节电模式。

如果没有外部时钟。

那么Watch 将失去效能。

2、各种工作模式下的时钟输入检测逻辑功能。

PLL 被旁路状态:如果PLLCR=0,那么PLL 就被旁路。

如果OSCCLK 检测到丢失,DSP 自动切换到PLL ,设置MCLKSTS 。

DSP 运行在“limp mode”频率模式下。

PLL 使能状态:除了PLLCR ≠0以外,其他的监测模式及其结果同上。

标准低功耗模式:在这种模式下,连接到CPU 的CLKIN 被停止。

如果检测到时钟消失,那么也是置位MCLKSTS ,同时产生复位。

如果工作于PLL 旁路模式下,1/2的limp 频率连接到cpu 。

3、 XCLKOUT主要是说:由于XCLKOUT 随着RESET 被激活而同时开始工作。

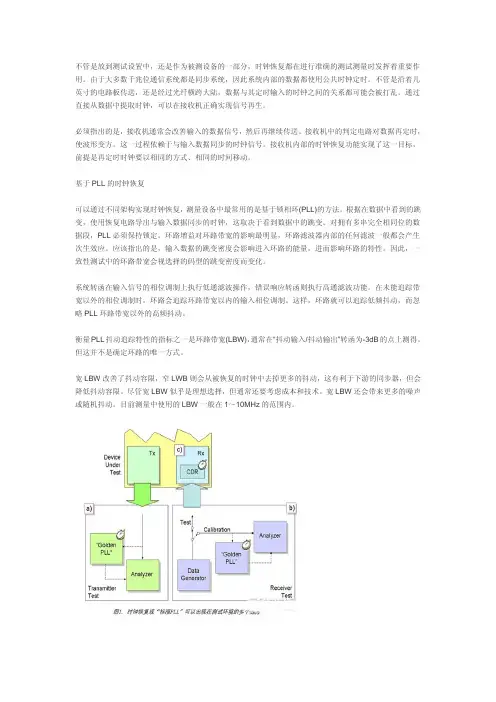

不管是放到测试设置中,还是作为被测设备的一部分,时钟恢复都在进行准确的测试测量时发挥着重要作用。

由于大多数千兆位通信系统都是同步系统,因此系统内部的数据都使用公共时钟定时。

不管是沿着几英寸的电路板传送,还是经过光纤横跨大陆,数据与其定时输入的时钟之间的关系都可能会被打乱。

通过直接从数据中提取时钟,可以在接收机正确实现信号再生。

必须指出的是,接收机通常会改善输入的数据信号,然后再继续传送。

接收机中的判定电路对数据再定时,使波形变方。

这一过程依赖于与输入数据同步的时钟信号。

接收机内部的时钟恢复功能实现了这一目标,前提是再定时时钟要以相同的方式、相同的时间移动。

基于PLL的时钟恢复可以通过不同架构实现时钟恢复,测量设备中最常用的是基于锁相环(PLL)的方法。

根据在数据中看到的跳变,使用恢复电路导出与输入数据同步的时钟,这取决于看到数据中的跳变。

对拥有多串完全相同位的数据段,PLL必须保持锁定。

环路增益对环路带宽的影响最明显,环路滤波器内部的任何滤波一般都会产生次生效应。

应该指出的是,输入数据的跳变密度会影响进入环路的能量,进而影响环路的特性。

因此,一致性测试中的环路带宽会视选择的码型的跳变密度而变化。

系统转函在输入信号的相位调制上执行低通滤波操作,错误响应转函则执行高通滤波功能。

在未能追踪带宽以外的相位调制时,环路会追踪环路带宽以内的输入相位调制。

这样,环路就可以追踪低频抖动,而忽略PLL环路带宽以外的高频抖动。

衡量PLL抖动追踪特性的指标之一是环路带宽(LBW),通常在“抖动输入/抖动输出”转函为-3dB的点上测得。

但这并不是确定环路的唯一方式。

宽LBW改善了抖动容限,窄LWB则会从被恢复的时钟中去掉更多的抖动,这有利于下游的同步器,但会降低抖动容限。

尽管宽LBW似乎是理想选择,但通常还要考虑成本和技术。

宽LBW还会带来更多的噪声或随机抖动。

目前测量中使用的LBW一般在1~10MHz的范围内。

时钟恢复的输入和输出必须指出测量中是怎样使用时钟恢复的,哪些地方会发生错误。

内置分频, 倍频电路超小型PLL时钟发生器

内置分频, 倍频电路超小型PLL时钟发生器

XC25BS8系列是能在低频输入8kHz, 4095倍的范围内倍频工作的PLL时钟发生器IC。

小型化, 同步抖动小, 实现128倍, 256倍, 512倍等高倍频。

分频电路, 相位频率比较器, 电荷泵, VCO内置,不需要复杂的滤波因子的计算,只需要加上电源和输入时钟就可简单实现时钟变换。

另外,可用于和音频DAC的LR时钟相位同步的噪声修整用的主时钟的生成等,也适用于生成各种必须和输入信号同步的同步信号。

输入端分频因子(M)可从1~2047的分频范围内进行选择;输出端分频因子(N)可从1~4095的分频范围内进行选择。

输出频率在1MHz~100MHz的范围内,输入时钟为8kHz~36MHz的标准时钟。

在内部可进行微调,在少量外置部件的条件下动作。

从CE端子输入低电平信号,可停止整个芯片动作,抑制消耗电流,此时的输。

library IEEE;use IEEE.std_logic_1164.all;USE IEEE.STD_LOGIC_TEXTIO.ALL;USE STD.TEXTIO.ALL;entity testbench isend entity testbench;architecture test_reg of testbench iscomponent mydesign isport( POWERDOWN : in std_logic;CLKA : in std_logic;LOCK : out std_logic;GLA : out std_logic);end component;signal POWERDOWN : std_logic;signal CLKA : std_logic:='0';signal LOCK, GLA : std_logic;constant ClockPeriod : TIME := 100 ns;beginUUT : mydesign port map (POWERDOWN=>POWERDOWN,CLKA=>CLKA,LOCK=>LOCK, GLA=>GLA);generate_clock : PROCESS (CLKA)BEGIN -- processCLKA <= NOT CLKA AFTER ClockPeriod/2;END PROCESS;process beginPOWERDOWN<='0';wait for 2000 ns;POWERDOWN<='1';wait for 100 ns;wait;end process;end architecture test_reg;测试结果如下图所示:由图可见,锁相环在lock信号变为高电平时生成了符合要求的输出时钟信号。

2.采用Clock & Management下的PLL-Static模块来实现输入时钟信号的相移功能(通过SmartDesign入口),Static PLL配置如下:采用上面的testbench,将其中的被调用模块名修改为此处PLL的模块名,在modelsim 环境下进行仿真,获得结果如下:从上图可见,在lock信号置高电平后,gla信号准确地在迟延90度后跟踪给定信号。

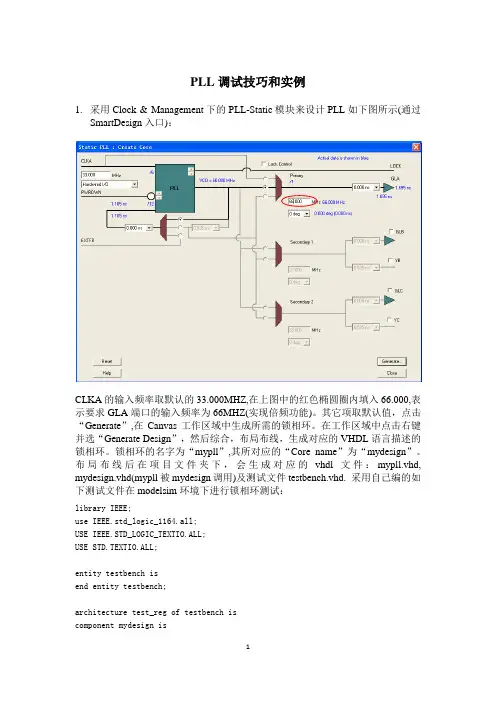

CLKA的输入频率取默认的33.000MHZ,在上图中的红色椭圆圈内填入66.000,表示要求GLA端口的输入频率为66MHZ(实现倍频功能)。

其它项取默认值,点击“Generate”,在Canvas工作区域中生成所需的锁相环。

在工作区域中点击右键并选“Generate Design”,然后综合,布局布线,生成对应的VHDL语言描述的锁相环。

锁相环的名字为“mypll”,其所对应的“Core name”为“mydesign”。

布局布线后在项目文件夹下,会生成对应的vhdl文件:mypll.vhd, mydesign.vhd(mypll被mydesign调用)及测试文件testbench.vhd. 采用自己编的如下测试文件在modelsim环境下进行锁相环测试:library IEEE;use IEEE.std_logic_1164.all;USE IEEE.STD_LOGIC_TEXTIO.ALL;USE STD.TEXTIO.ALL;entity testbench isend entity testbench;architecture test_reg of testbench iscomponent mydesign isport( POWERDOWN : in std_logic;CLKA : in std_logic;LOCK : out std_logic;GLA : out std_logic);end component;signal POWERDOWN : std_logic;signal CLKA : std_logic:='0';signal LOCK, GLA : std_logic;constant ClockPeriod : TIME := 100 ns;beginUUT : mydesign port map (POWERDOWN=>POWERDOWN,CLKA=>CLKA,LOCK=>LOCK, GLA=>GLA);generate_clock : PROCESS (CLKA)BEGIN -- processCLKA <= NOT CLKA AFTER ClockPeriod/2;END PROCESS;process beginPOWERDOWN<='0';wait for 2000 ns;POWERDOWN<='1';wait for 100 ns;wait;end process;end architecture test_reg;测试结果如下图所示:由图可见,锁相环在lock信号变为高电平时生成了符合要求的输出时钟信号。

以太网物理层芯片时钟同步PLL的设计方案在以太网中,物理层芯片(Physical Layer Interface Devices,PHY)是将各网元连接到物理介质上的关键部件。

负责完成互连参考模型(OSI)第I层中的功能,即为链路层实体之间进行位传输提供物理连接所需的机械、电气、光电转换和规程手段。

其功能包括建立、维护和拆除物理电路,实现物理层比特(bit)流的透明传输等。

物理层包括4个功能层和两个上层接口。

两个上层接口为物理介质无关层接口(MII)和物理介质相关层接口(MDI),在MII的上层是逻辑数据链路层(DLL),而MDI的下层则直接与传输介质相连。

而这些子层的正常工作都离不开一个稳定精确的时钟同步信号。

PLL在物理层芯片的时钟同步应用中,要求其输出时钟带宽覆盖范围广,电压控制频率线性度好,频谱纯度高。

在PLL设计过程中,VCO是最为关键的设计环节,其性能将直接决定PLL的设计工作质量。

近年来,VCO相位噪声得到越来越深入的研究,各种低噪声VCO结构不断涌现,文献中提到的交叉耦合电流饥饿型VCO便是其中一种。

电流饥饿是指电路单元的电流受到电流源的钳制而不能达到其应有的最大值。

本文在其基础上采用了一种有效控制电压变换电路,保证原有电路优点的同时扩展了线性度,提高抗噪声能力,有效降低了相位噪声。

1 VCO延迟单元工作原理图1所示为电流饥饿型VCO中的单级结构。

PNP管M1和NPN管M2是延迟单元的组成部分,Ictrl是用于控制电容的放电电流Id1和充电电流Id2,他们是构成环形振荡器的每一级。

Ictrl控制着流过M1管和M2管的电流,所以由M1管和M2管构成的延迟单元处于电流饥饿状态。

每一级迟单元处于电流饥饿状态。

每一级的电流都由同一个电流源所镜像,所以Id1=Id2同时电流大小由输入控制电流Ictrl控制。

反相延迟主要是2个原因:一个是RC的充电时间;另一个是反相器的预置电压。

而这2个延迟时间的产生都是可以通过调整宽长比来实现。

不同频率的pll,对参考时钟摆幅的要求

PLL(锁相环)是一种反馈电路,用于将一个电路板上的时钟相位与外部时序信号同步。

PLL的工作原理是将外部信号的相位与压控晶体振荡器(VCXO)产生的时钟信号的相位进行比较,然后调整振荡器时钟信号的相位以匹配参考信号的相位,从而实现两个信号的同相。

在PLL中,参考时钟的摆幅会对PLL的性能产生影响。

理论上,参考时钟的摆幅越大,PLL的跟踪速度和噪声抑制能力越强。

因此,对于不同频率的PLL,对参考时钟摆幅的要求可能会有所不同。

一般来说,为了获得更好的性能,建议选择摆幅较大的参考时钟。

然而,在实际应用中,PLL的性能不仅仅取决于参考时钟的摆幅,还受到其他因素的影响,如环路带宽、滤波器设计等。

因此,对于具体的PLL应用,需要根据实际需求和系统要求进行综合设计和考虑。

如果需要更深入和具体的信息,建议查阅相关的锁相环(PLL)设计和应用资料,或者咨询相关领域的专家。

fpga中pll 的反馈时钟英文回答:Phase-locked loops (PLLs) are a critical part of many FPGA designs. They are used to generate clock signals that are stable and accurate, which is essential for the proper operation of digital circuits.The feedback clock of a PLL is the clock signal that is used to compare the output of the PLL to the reference clock. This signal is used to adjust the output clock frequency and phase so that it matches the reference clock.There are a number of requirements that must be met by the feedback clock in order for the PLL to operate properly. These requirements include:The feedback clock must be stable and accurate. If the feedback clock is not stable, the PLL will not be able to generate a stable output clock. The feedback clock mustalso be accurate, meaning that its frequency and phase must be within a specified range.The feedback clock must have a low jitter. Jitter is a variation in the frequency or phase of a clock signal. Excessive jitter can cause the PLL to lose lock, which will result in the output clock becoming unstable.The feedback clock must be properly terminated. The feedback clock should be terminated with a resistor of the appropriate value to prevent reflections. Reflections can cause the PLL to lose lock or to generate a clock signal that is not stable.中文回答:PLL(锁相环)是许多 FPGA 设计的关键部分。

pll 相位裕度PLL(Phase Locked Loop)是一种用于时钟和频率控制的电路。

在设计PLL时,一个至关重要的指标是“PLL相位裕度”,它表示PLL 在不受外部噪声影响下,能够跟踪和锁定输入信号的能力。

以下是关于PLL相位裕度的详细介绍:1. 什么是PLL相位裕度?PLL相位裕度是指在输入信号频率波动时,PLL保持锁定状态的能力。

通常用频率值表示,单位为赫兹(Hz),例如10kHz。

相位裕度表示在某一个频率范围内,设备控制电路需要的最小瞬态稳定系数(Kp)。

2. 如何计算PLL相位裕度?PLL相位裕度通常由两个因素决定————开环带宽和相位裕度余量。

在实际应用中,开环带宽是由VCO调节范围和LOOP滤波器带宽决定的。

相位裕度余量是指在输入信号频率变化时,PLL仍能维持稳定状态的裕量。

计算相位裕度通常使用Bode图方法。

首先,我们需要测量VCO 频率范围和LOOP滤波器带宽。

然后,我们需要绘制出开环增益与相位响应曲线的Bode图。

在此基础上,我们可以计算系统系统的相位裕度余量。

3. 如何提高PLL相位裕度?为了提高PLL相位裕度,在设计和调试过程中,我们可以采用以下几种方法:a. 增加LOOP滤波器的带宽LOOP滤波器的带宽影响了PLL的相位裕度。

因此,我们可以通过增加LOOP滤波器的带宽来提高PLL的相位裕度。

但是要注意,增大LOOP滤波器的带宽可能会带来额外的相位噪声。

b. 修改相位裕度余量相位裕度余量说明PLL的稳定性和精度。

一般情况下,我们能够通过修改相位裕度余量来提高PLL的相位裕度。

具体而言,我们可以通过增加相位裕度余量来提高PLL的稳定性。

c. 设计合适的VCOVCO的调节范围影响PLL的相位裕度。

因此,为了提高PLL的相位裕度,我们需要设计合适的VCO。

通常来说,我们可以通过减小VCO 的调整范围来提高PLL的相位裕度。

4. 总结在PLL的设计和调试过程中,相位裕度是一个至关重要的指标。

什么是PLL

2007-01-18 16:53 1580人阅读评论(0) 收藏举报PLL 是Phase-Locked Loop(锁相环)的缩写。

什么是锁相环?锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。

或者说,对于接收

到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号

中的时钟信号具有一定的相差,所以很形象地称其为锁相器。

而一般情形下,这种锁相环的三个组成部分和相应的运作机理是:

1 鉴相器:用于判断锁相器所输出的时钟信号和接收信号中的时钟的相差的幅度;

2 可调相/调频的时钟发生器器:用于根据鉴相器所输出的信号来适当的调节锁相器

内部的时钟输出信号的频率或者相位,使得锁相器完成上述的固定相差功能;

3 环路滤波器:用于对鉴相器的输出信号进行滤波和平滑,大多数情形下是一个低通

滤波器,用于滤除由于数据的变化和其他不稳定因素对整个模块的影响。

从上可以看出,大致有如下框图:

┌─────┐┌─────┐┌───────┐

→─┤鉴相器├─→─┤环路滤波器├─→─┤受控时钟发生器├→┬─→

└──┬──┘└─────┘└───────┘│

↑↓

└──────────────────────────┘

可见,是一个负反馈环路结构,所以一般称为锁相环(PLL: Phase Locking Loop)

锁相环有很多种类,可以是数字的也可以是模拟的也可以是混合的,可以用于恢复载波

也可以用于恢复基带信号时钟。

PLL时钟是什么

为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。

PLL用于振荡器中的反馈技术。

锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。

PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。

因此,所有板卡上各自的本地80MHz和20MHz时基的相位都是同步的,从而采样时钟也是同步的。

因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。

通过锁相环同步多块板卡的采样时钟所需要的编程技术会根据您所使用的硬件板卡的不同而不同。

对于基于PCI总线的产品(M系列数据采集卡,PCI数字化仪等),所有的同步都是通过RTSI总线上的时钟和触发线来实现的;这时,其中一块版板卡会作为主卡并且输出其内部时钟,通过RTSI线,其他从板卡就可以获得这个用于同步的时钟信号,对于基于PXI总线的产品,则通过将所有板卡的时钟于PXI内置的10MHz背板时钟同步来实现锁相环同步的。