《EDA》第五章03_1

- 格式:ppt

- 大小:541.50 KB

- 文档页数:52

第五章状态机在VHDL中的实现利用VHDL设计的许多实用逻辑系统中,有许多是可以利用有限状态机的设计方法来描述和实现的。

无论与基于VHDL的其它设计方案相比,还是与可完成相似功能的CPU相比,状态机都有其无可比拟的优越性。

状态机设计与分类的传统理论是根据状态机的输出输入关系,将其分为所谓Mealy型和Moore型两类状态机。

然而,面对多种多样的实际应用要求,可以有更多种类,结构类型和功能特点的状态机。

Mealy型和Moore型两类状态机区别就在于:Mealy型系统的输出不仅受系统当前状态的控制,而且受输入控制信号状态的控制;Moore型系统的输出仅受当前系统状态的控制。

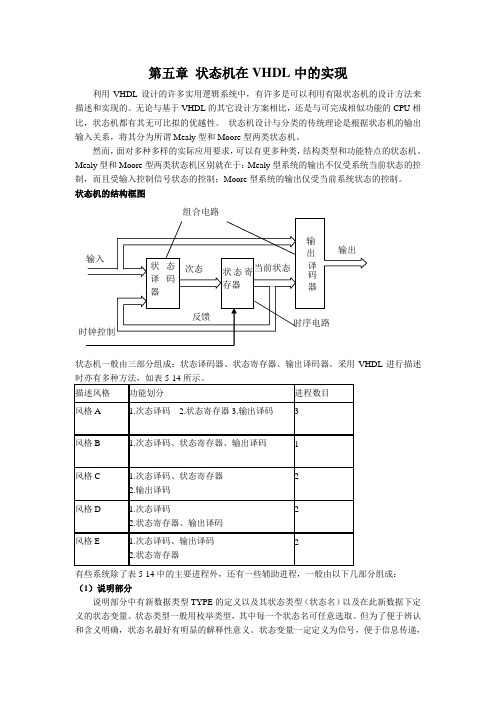

状态机的结构框图状态机一般由三部分组成:状态译码器、状态寄存器、输出译码器。

采用VHDL进行描述有些系统除了表5-14中的主要进程外,还有一些辅助进程,一般由以下几部分组成:(1)说明部分说明部分中有新数据类型TYPE的定义以及其状态类型(状态名)以及在此新数据下定义的状态变量。

状态类型一般用枚举类型,其中每一个状态名可任意选取。

但为了便于辨认和含义明确,状态名最好有明显的解释性意义。

状态变量一定定义为信号,便于信息传递,说明部分放在结构体的定义语句区即ARCHITECTURE和BEGIN之间。

例如:ARCHITECTURE ...ISTYPE states IS (st0,st1,st2,st3); --定义新的数据类型和状态名SIGNAL current_state,next_state:states;--定义状态变量...BEGIN...;(2)主控时序进程主控时序进程完成状态转移的功能。

状态机是随外部时钟信号,以同步时序方式工作的,因此,状态机中必须包含一个对工作时钟信号敏感的进程,作为状态机的“驱动泵”。

状态机的下一个状态(包括再次进入本状态)仅仅取决于时钟信号的到来。

根据实际情况来决定,此进程中也可以放置一些同步清零或置位方面的控制信号。

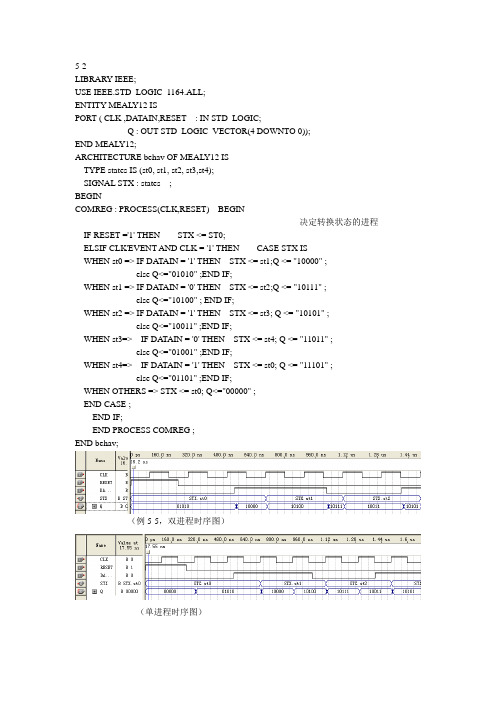

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MEALY12 ISPORT ( CLK ,DA TAIN,RESET : IN STD_LOGIC;Q : OUT STD_LOGIC_VECTOR(4 DOWNTO 0));END MEALY12;ARCHITECTURE behav OF MEALY12 ISTYPE states IS (st0, st1, st2, st3,st4);SIGNAL STX : states ;BEGINCOMREG : PROCESS(CLK,RESET) BEGIN--决定转换状态的进程IF RESET ='1' THEN STX <= ST0;ELSIF CLK'EVENT AND CLK = '1' THEN CASE STX ISWHEN st0 => IF DA TAIN = '1' THEN STX <= st1;Q <= "10000" ;else Q<="01010" ;END IF;WHEN st1 => IF DA TAIN = '0' THEN STX <= st2;Q <= "10111" ;else Q<="10100" ; END IF;WHEN st2 => IF DA TAIN = '1' THEN STX <= st3; Q <= "10101" ;else Q<="10011" ;END IF;WHEN st3=> IF DA TAIN = '0' THEN STX <= st4; Q <= "11011" ;else Q<="01001" ;END IF;WHEN st4=> IF DA TAIN = '1' THEN STX <= st0; Q <= "11101" ;else Q<="01101" ;END IF;WHEN OTHERS => STX <= st0; Q<="00000" ;END CASE ;END IF;END PROCESS COMREG ;END behav;(例5-5,双进程时序图)(单进程时序图)要求一:表达的是moore型状态机,特点是输出仅为当前状态的函数。

1.试说明实体端口模式BUFFER和INOUT的不同之处?答:BUFFER端口:缓冲模式,具有读功能的输出模式,即信号输出到实体外部,但同时也在内部反馈使用,不允许作为双向端口使用.而INOUT端口:双向模式,即信号的流通是双向的,既可以对此端口赋值,也可以通过此端口读入数据.2.VHDL的数据对象有哪几种?它们之间有什么不同?答:VHDL的数据对象有三种:信号、变量、常量. 它们之间的的区别如下:信号赋值至少有δ延时,而变量和常量没有;信号除当前值外,有许多相关信息,变量只有当前值,常量的值在设计实体中始终不变;进程对信号敏感而对变量及常量不敏感;信号可以是多个进程的全局信号,变量只在定义它们的顺序域可见,而常量的使用范围取决于它被定义的位置;信号是硬件连线的抽象描述信号赋值,赋值符号 <= 而变量和常量的赋值符号 :=。

3。

说明下列各定义的意义:SIGNAL a , b ,c :BIT :='0’;CONSTANT TIME1 ,TIME2 : TIME : 20ns ;VARIABLE x , y , z :STD_LOGIC :=’x’;答:错误!定义3个位数据类型的信号a、b、c,它们取值为0;○2定义2个时间数据类型的常量TIME1、TIME2,它们值为20ns;错误!定义3个标准逻辑位 STD_LOGIC数据类型的变量x、y、z,它们的值是强未知的。

4。

什么是重载函数?重载运算符有何用处?如何调用重载运算符函数?答:为了方便各种不同数据类型间的运算,VHDL允许用户对原有的基本操作符重新定义,赋予新的含义和功能,从而建立一种新的操作符,这就是重载操作符,定义这种操作符的函数成为重载函数。

重载运算符的作用是为了方便各种不同的数据类型间的运算。

要调用重载运算符函数,先要在程序包中进行函数体的定义,调用的格式如下:x <=函数名(参数1,参数2,····)参数个数和类型与所定义的函数要保持一致。