FPGA原理图方式设计流程图

- 格式:doc

- 大小:2.62 MB

- 文档页数:20

QuartusII的设计流程QuartusII软件的使用方法一、设计输入1。

建立工程任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与此工程相关的所有设计文件的文件夹。

此文件夹将被EDA软件默认为工作库(Work Library)。

一般,不同的设计项目最好放在不同的文件夹中,而同一工程的所有文件都必须放在同一文件夹中。

首先建立工作库目录,以便存储工程项目设计文件。

在D盘下新建文件夹并取名Mydesign。

双击QuartusII软件启动图标,即可启动QuartusII软件,启动界面如图1—2所示。

使用New Project Wizard 可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称,还可以指定要在工程中使用的设计文件、其他源文件、用户库和EDA 工具,以及目标器件系列和具体器件等。

在此要利用“New Preject Wizard”工具选项创建此设计工程,并设定此工程的一些相关的信息,如工程名、目标器件、综合器、仿真器等。

(1)打开建立新工程管理窗.选择菜单File→New Preject Wizard 命令,即弹出“工程设置"对话框(图1-3),以此来建立新的工程。

(2)在单击图1-3后,出现了设置工程的基本信息,如图1-4所示.单击此对话框最上一栏右侧的“… "按钮,可以选择工程存放在硬盘上的位置,此例中将工程放在D盘Mydesign文件夹下.这三行的第一行的d:\Mydesign表示工程所在的工作库文件夹;第二行的half_add 表示此项工程的工程名,工程名可以取任何其他的名,也可直接用顶层文件的实体名作为工程名,在此就是按这种方式取的名;第三行是当前工程顶层文件的实体名,这里即为half_add。

(2)将设计文件加入工程中。

单击图1—4中的Next 按钮,弹出对话框如图1—5所示,在对话框中单击File name 右侧的“… ”按钮,可以将与工程相关的所有VHDL 文件(如果有的话)加入进此工程,此工程文件加入的方法有两种:第1 种方法是单击“Add … ”按钮,从工程目录中选出相关的VHDL 文件;第2 种方法是单击Add All 按钮,将设定的工程目录中的所有VHDL 文件加入到工程文件栏中。

1998年11月 电子产品世界 33枚举型(enumerated)等。

Verilog的数据类型相对比较简单,所有数据类型由语言定义,设计者不可自定义数据类型。

由于VH D L语法非常严格,数据操作必须在相同数据类型之间进行,优点是设计明了,不易产生设计错误;缺点是需要使用数据类型转换函数进行不同类型数据之间的运算操作。

Verilog可在不同字长数据间进行操作,语句比较简单,但设计者必须掌握尺度,否则可能产生不可预料的综合结果。

・运算操作 两种语言比较相似。

例外是Verilog 中无求幂运算、与非、或非、算术左/右移、循环左/右移等。

但有非常有用的约简(reduction)运算,在VH D L中则可通过循环语句完成这一算法。

・结构描述 VH D L语言中有丰富的语法定义来帮助设计者进行高层次结构管理、参数化设计和处理较大规模的电路。

如Package,con figuration,generate,generic等,并可运用于逻辑综合。

Verilog除参数化设计外,则无相应的语法定义,但在门级描述方面有较大的优势,被广泛采用进行ASIC和FPG A 库的开发。

这与Verilog语言本身最初的设计思想有关。

目前,IEEE1076.4标准解决了VH D L门级描述的问题。

・库 VH D L可通过库的方式来管理和存储编译后的设计数据,过程和函数可写在package中,以便不同设计的调用。

Verilog没有Package和库的概念,过程和函数的再利用需通过include语句。

3.易用性 由于VH D L是语法非常严格的语言,同时,对于同一功能模块,描述方法可以有各种形式,因此,VH D L对于初学者较为困难,但对高级用户来说,却是强有力的编程语言。

如果不考虑P LI以及仿真编译的指令集部分,Verilog要比VH D L容易得多,但一旦考虑这些因素,设计者相当于需要学习三种语言。

从形式上看,VH D L类似于Ada语言,而Verilog则是Ada和C的组合。

简述fpga的开发流程

简述FPGA的开发流程

FPGA开发流程是由一系列相关步骤组成的。

它可以分为前期设计环境的构建、FPGA及外围电路的设计、FPGA编程、系统烧写和调试等五个主要步骤。

一、构建设计环境

首先,需要构建FPGA的设计环境,安装设计软件,如Xilinx ISE、Quartus等,这些软件可以支持FPGA设计,建立设计环境,提供设计使用。

紧接着,对开发板进行硬件测试,检查硬件是否正常可用,以确保下一步无硬件问题,提高开发效率。

二、FPGA及外围电路设计

接下来进行FPGA及外围电路的设计,设计者可以根据具体需求,使用Verilog HDL或VHDL等语言编写FPGA及外围电路的原理图,经过仿真,验证无误后,进入下一步。

三、FPGA编程

在FPGA及外围电路设计完成后,就可以进行FPGA的编程,即将设计好的原理图编译为FPGA的可烧写文件,如.JED、.BIN等,此时可以使用烧录器进行FPGA编程,将编译加载到目标FPGA芯片中。

四、系统烧录

编程完成后,FPGA芯片可以正常工作,此时需要将系统烧录到FPGA上,使其和外围电路组成完整的系统,以满足应用需求。

五、调试

最后一步是进行系统的调试,这个步骤并不仅仅是测试芯片本身,而是测试整个系统的功能,确保系统能够按照预期工作。

通过以上步骤即可完成FPGA的开发。

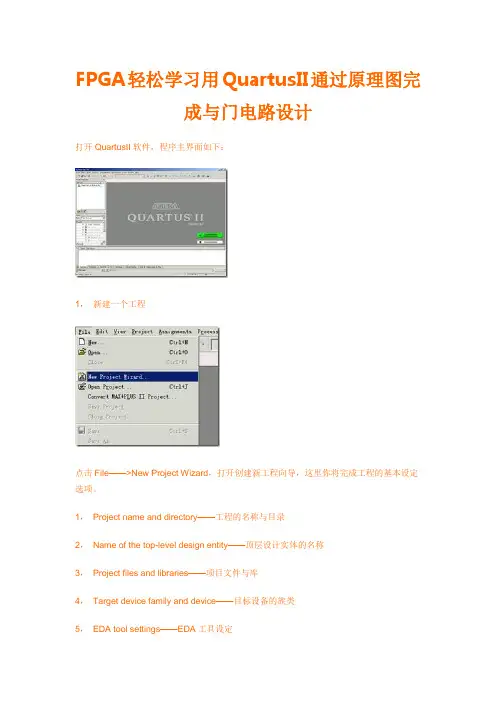

FPGA轻松学习用QuartusII通过原理图完成与门电路设计打开QuartusII软件,程序主界面如下:1,新建一个工程点击File——>New Project Wizard,打开创建新工程向导,这里你将完成工程的基本设定选项。

1,Project name and directory——工程的名称与目录2,Name of the top-level design entity——顶层设计实体的名称3,Project files and libraries——项目文件与库4,Target device family and device——目标设备的族类5,EDA tool settings——EDA工具设定这里一般设定好工程名称和目录,顶层设计实体名称以及目标设备族类就可以了,其他的暂时直接使用默认项就可以了。

2,新建一个设计文件通过点击File——>New打开新建文件选择框,由于我们这里使用原理图描述实现的,则文件类型选择Design Files——>Block Diagram/Schematic File,就新建了一个原理图文件,将其保存起来,注意命名要跟前面设置的顶层设计实体名称相同。

3,编写设计文件接下来开始在文件中绘制原理图,这里首先完成与门的添加,点击左侧工具栏中的Symbol Tool按钮,打开Symbol选择框,选择primitives——>logic——>and2,点击OK后即可在原理图中添加一个2输入的与门了。

在同样通过Symbol Tool中的加入和primitives——>pin——>output加入输入和输出引脚,然后在原理图中把他们用Orthogonal Node Tool即导线连接起来,双击输入输出引脚,为他们设定好名字,pinA,pinB,pinC,就完成了原理图中的设计。

4,编译(分析综合)点击Processing——>Start——>Start Analysis & Synthesis,进行分析综合,就好像是对程序进行编译,等待片刻,如果没有错误,编译报告会输出出来。

fpga开发流程FPGA开发流程是一种以设计、验证、发布三个步骤为主要过程的开发流程,它可以用来完成FPGA器件从设计到发布生产的快速转变。

一、设计阶段:1. 硬件设计。

在硬件设计过程中,首先需要搭建FPGA开发环境,运用芯片原理图、数据表、时序图等完成硬件电路的搭建;2. 软件设计。

在软件设计过程中,应用高级语言(如C语言)完成软件模块的设计和编程;3. 测试程序设计。

在测试程序设计步骤中,针对FPGA器件的功能和性能,利用自动控制理论和技术,设计出不同的测试程序以便于验证和检验器件的设计。

二、验证阶段:1. 模块试验。

模块试验即对设计中单个模块进行功能测试以确定其基本功能是否满足设计要求;2. 系统综合验证。

系统综合验证是在硬件设计和软件编程都完成的情况下,将硬件模块与软件模块综合起来进行功能验证,以确定FPGA器件的功能和性能是否满足设计要求;3. 单元测试。

单元测试是在器件整体完成后,从模块单元开始测试,逐步扩展最终,以确定FPGA器件的功能和性能能够达到系统综合验证中设计要求的水平,并进行可靠性测试以保证器件能够良好地运行。

三、发布阶段:1. 文档准备。

根据可行性研究所确定的芯片设计内容,准备完整的文档,包括用户手册、芯片实现原理图和技术文档,以及硬件开发计划书、软件开发计划书、可行性研究报告等;2. 工程管理。

工程管理指器件设计完成后,利用专业的硬件或软件开发工具,对FPGA设计文件进行编写、发布、测试和部署等各项管理环节;3. 交付客户。

采用与产品功能和特点最符合的标准格式交付给用户,等待其认可并按照要求将产品投入生产线。

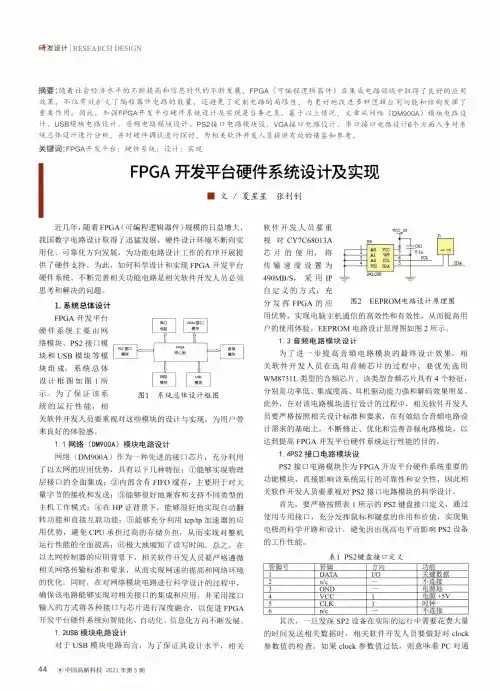

研发设计 I RESEARCH DESIGN樓块图1系统总体设计框图近几年,随着FPGA (可编程逻辑器件)规模的日益增大, 我国数字电路设计取得了迅猛发展,硬件设计环境不断向实 用化、可靠化方向发展,为功能电路设计工作的有序开展提 供了硬件支持。

为此,如何科学设计和实现FPGA 开发平台 硬件系统、不断完善相关功能电路是相关软件开发人员必须思考和解决的问题。

1.系统总体设计FPGA 开发平台硬件系统主要由网 络模块、PS 2接口模 块和U S B 模块等模 块组成,系统总体 设计框图如图1所 示。

为了保证该系 统的运行性能,相关软件开发人员要重视对这些模块的设计与实现,为用户带 来良好的体验感。

1.1网络(D M 900A )模块电路设计网络(DM 900A )作为一种先进的接口芯片,充分利用 了以太网的应用优势,具有以下几种特征:①能够实现物理 层接口的全面集成;②内部含有FIFO 缓存,主要用于对大 量字节的接收和发送:③能够很好地兼容和支持不同类型的 主机工作模式;④在HP 证背景下,能够很好地实现自动翻 转功能和直接互联功能;⑤能够充分利用tcp /tp 加速器的应 用优势,避免CPU 承担过高的存储负担,从而实现对整机 运行性能的全面提高:⑥极大地缩短了读写时间。

总之,在 以太网控制器的应用背景下,相关软件开发人员要严格遵循 相关网络传输标准和要求,从而实现网速的提高和网络环境 的优化。

同时,在对网络模块电路进行科学设计的过程中, 确保该电路能够实现对相关接口的集成和应用,并采用接口 输入的方式将各种接口与芯片进行深度融合,以促进FPGA 开发平台硬件系统向智能化、自动化、信息化方向不断发展。

1.2USB 模块电路设计对于U S B 模块电路而言,为了保证其设计水平,相关软件开发人员要重 视对 CY 7C 68013A 芯片的使用,将 传输速度设置为摘要:随着社会经济水平的不断提高和信息时代的不断发展,FPGA (可编程逻辑器件)在集成电路领域中取得了良好的应用 效果,不仅有效扩大了编程器件电路的数量,还避免了定制电路的局限性,为更好地改进多种逻辑应用功能和结构发挥了 重要作用。

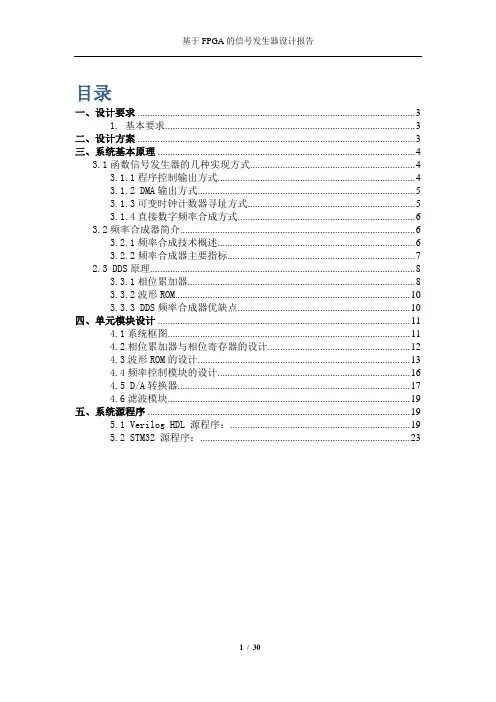

目录一、设计要求 (3)1. 基本要求 (3)二、设计方案 (3)三、系统基本原理 (4)3.1函数信号发生器的几种实现方式 (4)3.1.1程序控制输出方式 (4)3.1.2 DMA输出方式 (5)3.1.3可变时钟计数器寻址方式 (5)3.1.4直接数字频率合成方式 (6)3.2频率合成器简介 (6)3.2.1频率合成技术概述 (6)3.2.2频率合成器主要指标 (7)2.3 DDS原理 (8)3.3.1相位累加器 (8)3.3.2波形ROM (10)3.3.3 DDS频率合成器优缺点 (10)四、单元模块设计 (11)4.1系统框图 (11)4.2相位累加器与相位寄存器的设计 (12)4.3波形ROM的设计 (13)4.4频率控制模块的设计 (16)4.5 D/A转换器 (17)4.6滤波模块 (19)五、系统源程序 (19)5.1 Verilog HDL 源程序: (19)5.2 STM32 源程序: (23)摘要直接数字频率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽样定理理论和现代器件生产技术发展的一种新的频率合成技术。

与第二代基于锁相环频率合成技术相比,DDS具有频率切换时间短、频率分辨率高、相位可连续变化和输出波形灵活等优点,因此,广泛应用于教学科研、通信、雷达、自动控制和电子测量等领域。

该技术的常用方法是利用性能优良的DDS专用器件,“搭积木”式设计电路,这种“搭积木”式设计电路方法虽然直观,但DDS专用器件价格较贵,输出波形单一,使用受到一定限制,特别不适合于输出波形多样化的应用场合。

随着高速可编程逻辑器件FPGA的发展,电子工程师可根据实际需求,在单一FPGA上开发出性能优良的具有任意波形的DDS系统,极大限度地简化设计过程并提高效率。

本文在讨论DDS的基础上,介绍利用FPGA设计的基于DDS 的信号发生器。

关键字:FPGA;DDS;函数信号发生器;一、设计要求1. 基本要求(1)信号发生器能产生正弦波、方波和三角波三种周期性波形;(2)将输出信号频率范围为10Hz ~10MHz ,输出信号频率可分段调节:在10Hz ~100kHz 范围内步进间隔为10Hz ;在100kHz ~1MHz范围内步进间隔为100Hz ;在1MHz ~10MHz 范围内步进间隔为1kHz 。

FPGA课程设计题目:全天候温度纪录仪旳设计与FPGA实现姓名:学号:院系:信息科学与工程学院专业:计算机技术摘要本设计有效旳克服了老式旳数字温度计旳缺陷,采用自上而下旳设计思路,绘制出了系统构造流程图,最后又在硬件上通过对其进行调试和验证。

基于FPGA在Quartus II13.0软件下应用Verilog HDL语言编写程序,采用ALTRA公司Cyclone- IV系列旳EP4CE40F23I7 芯片进行了计算机仿真,并给出了相应旳仿真成果。

该电路可以实现较好旳测温功能。

核心字:数字温度计;FPGA;Quartus II130.;Verilog HDL;EP4CE40F2317AbstractThis design effectively overcomes the traditional digital thermometer’s wea knesses and takes a top-down approach to design flow chart of system, and fi nally pass the circuits to the hardware to debug and verify it. This design is b ased on FPGA using Verilog HDL language to write program in Quartus II sof tware, adopting EP4CE40F23I7 chip of Cyclone- IV series of ALTRA company for computer simulation and at the same time showing the corresponding sim ulation result. This circuit is able to carry out excellent temperature- measurem ent function.KeyWords:Digital thermometer;FPGA;Quartus II 13.0;Verilog HDL ;EP4CE40F2317目录一、设计规定 (1)1.1 设计题目 (1)1.2 选题背景 (1)1.3 设计规定: (1)二、系统设计 (2)2.1 系统设计图 (2)2.2 系统设计阐明 (2)三、硬件设计 (2)3.1 FPGA简介 (3)3.2 LCD1602液晶显示 (5)3.3 DS18B20温度传感器 (7)3.4 AT24C02读写模块 (9)3.5 按键模块设计 (10)四、软件设计 (11)4.1 Quartus II软件简介 (11)4.2 系统架构图 (12)4.3 系统控制器 (12)4.4 系统调试 (13)五、代码附录 (13)5.1 顶层模块 (13)5.2 LCD驱动部分代码 (15)5.3 DS18B20驱动模块 (16)全天候温度纪录仪旳设计与FPGA实现一、设计有关1.1 设计题目全天候温度纪录仪旳设计与FPGA实现1.2选题背景当今电子产品正向功能多元化,体积最小化,功耗最低化旳方向发展。

FPGA轻松学习用QuartusII通过原理图完成与门电路设计打开QuartusII软件,程序主界面如下:1,新建一个工程点击File——>New Project Wizard,打开创建新工程向导,这里你将完成工程的基本设定选项。

1,Project name and directory——工程的名称与目录2,Name of the top-level design entity——顶层设计实体的名称3,Project files and libraries——项目文件与库4,Target device family and device——目标设备的族类5,EDA tool settings——EDA工具设定这里一般设定好工程名称和目录,顶层设计实体名称以及目标设备族类就可以了,其他的暂时直接使用默认项就可以了。

2,新建一个设计文件通过点击File——>New打开新建文件选择框,由于我们这里使用原理图描述实现的,则文件类型选择Design Files——>Block Diagram/Schematic File,就新建了一个原理图文件,将其保存起来,注意命名要跟前面设置的顶层设计实体名称相同。

3,编写设计文件接下来开始在文件中绘制原理图,这里首先完成与门的添加,点击左侧工具栏中的Symbol Tool按钮,打开Symbol选择框,选择primitives——>logic——>and2,点击OK后即可在原理图中添加一个2输入的与门了。

在同样通过Symbol Tool中的加入和primitives——>pin——>output加入输入和输出引脚,然后在原理图中把他们用Orthogonal Node Tool即导线连接起来,双击输入输出引脚,为他们设定好名字,pinA,pinB,pinC,就完成了原理图中的设计。

4,编译(分析综合)点击Processing——>Start——>Start Analysis & Synthesis,进行分析综合,就好像是对程序进行编译,等待片刻,如果没有错误,编译报告会输出出来。

FPGA的设计开发流程主要包括四个步骤:设计输入(Design Entry)、仿真(Simulation)、综合(Synthesis)及布局布线(Place & Route)。

1. 设计输入(Design Entry)Summit公司的VisualHDL、Mentor公司的Renoir、Aldec公司的ActiveHDL。

均支持图文混合的层次化设计。

三者都提供PC版本,VisualHDL还有工作站版本。

图形输入包括状态图、真值表、流程图、方框图等。

其中流程图输入方法是Renoir独有的。

文本输入包括VHDL和Verilog,上述工具都而且同时支持两种语言。

Renoir支持HDL2GRAPH,即从VHDL/Verilog语言模块转换到图形。

这一特性有助于分析已有HDL的语言结构。

ActiveHDL提供HDL语法高亮显示、自动产生文本结构、自动格式化文本等非常有益的文本编辑浏览特性。

Renoir和VisualHDL甚至不提供最基本的HDL语法高亮显示。

2. 仿真(Simulation)仿真包括功能仿真和时序仿真。

其中,功能仿真在布局布线之前;时序仿真在布局布线之后。

仿真工具有Mentor公司的Modelsim和Aldec公司的ActiveHDL,二者同时支持VHDL和Verilog的仿真。

Cadence公司也提供仿真工具,似乎对Verilog的支持更强,没有评估过。

Modelsim同时提供PC和工作站版本,ActiveHDL只有PC版本。

其中Modelsim是工业界应用最广的仿真工具,已经成为事实上的标准。

界面简洁,仿真速度快,功能强大而稳定。

ActiveHDL提供图示化仿真激励输入,而且有testbench的自动生成模板,这些特性都是独有的。

而且语言的在线帮助系统非常好。

3. 综合(Synthesis)综合工具实现从HDL语言到FPGA或ASIC网表的生成。

目前有Synopsys公司的FPGA Compiler II、Mentor公司的Examplar和Synplify公司的Synplicity。

基于FPGA的函数信号发生器的设计与实现摘要波形发生器己成为现代测试领域应用最为广泛的通用仪器之一,代表了信号源的发展方向。

直接数字频率合成(DDS)是二十世纪七十年代初提出的一种全数字的频率合成技术,其查表合成波形的方法可以满足产生任意波形的要求。

由于现场可编程门阵列(FPGA)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS技术,极大的提高函数发生器的性能,降低生产成本。

本文首先介绍了函数波形发生器的研究背景和DDS的理论。

然后详尽地叙述了用FPGA完成DDS模块的设计过程,接着分析了整个设计中应处理的问题,根据设计原理就功能上进行了划分,将整个仪器功能划分为控制模块、外围硬件、FPGA器件三个部分来实现。

最后就这三个部分分别详细地进行了阐述。

本文利用Altera的设计工具QuartuSH并结合VeI’i1og一HDL语言,采用硬件编程的方法很好地解决了这一问题。

论文最后给出了系统的测量结果,并对误差进行了一定分析,结果表明,,、三角波、锯齿波、方波,通过实验结果表明,本设计达到了预定的要求,并证明了采用软硬件结合,利用FPGA技术实现波形发生器的方法是可行的。

关键词:函数发生器,直接数字频率合成,现场可编程门阵列The Design and Realize of DDS Based on FPGAAbstractArbitrary Waveform Generator(AWG) is one of the most popular instruments in modern testing domains,Which represents the developing direction of signal sources· Direct Digital frequency Synthesis(DDS) advance dearly in full digital technology for frequency synthesis,its LUT method for synthes waveform .Adapts togenerate arbitrary Waveform· Field programable GateArray(FPGA)has the feature sof Iargeseale integration,high working frequency and ean realize lal’ge Memory,50FPGAeaneffeetivelyrealizeDDS.The of Corporation Altera ehosen to do the main digitalProcessing work,which based on its large sale and highs Peed. The 53C2440MCU ehosenasa control ehip· Inthisdesign,how to design the fpga chip and theInter faee between the FPGA and the control ehiP the the method ofSoftware and hardware Programming,the design used the software Quartus11 and languageverilog一HDL solves ,the PrineiPle of DDS and Basis of EDA technology introdueed Problem is the design are analyzed and the whole fun into three Parts:masterehiP,FPGA deviee and PeriPheral three Parts are described indetail disadvantage and thing sneed toadv anceareal Of the dissertation,or asquare wave with in the frequency rangeto20MHz .Planed and the way to use software and hardware Programming method and DDS Technology to realize Functional Waveform Generatoravailable.Keywords:DDS;FPGA;Functional Waveform Generator目录第一章绪论 ................................................ IV ............................................................................................................... IV ................................................................................................................. V ......................................................................................................... V....................................................................................................... VI .............................................................................................................. VII ...................................................................................................... VIIDMA输出方式.......................................................................... VII...................................................................................................... VII..................................................................................................... V III 第二章直接数字频率合成器的原理及性能 ................................................ I .................................................................................................................. I .......................................................................................................... I......................................................................................................... I I DDS原理 ............................................................................................. I II 第三章基于FPGA的DDS模块的实现 .......................................................... I (FPGA)简介 ............................................................................................. I II软件并建立工程 ....................................................................... I I新建Block Diagram/Schematic File并添加模块电路。

第3章Quartus II使用入门及FPGA设计流程Quartus II可编程逻辑开发软件是Altera公司为其FPGA/CPLD芯片设计推出的专用开发工具,是Altera公司最新一代功能更强的EDA开发软件,可完成从设计输入,综合适配,仿真到下载的整个设计过程。

Quartus II提供了一个完整的多平台开发环境,它包含FPGA和CPLD整个设计阶段的解决方案。

Quartus II集成环境包括以下内容:系统级设计,嵌入式软件开发,可编程逻辑器件设计、综合、布局和布线,验证和仿真。

Quartus II也可以直接调用Synplify Pro、ModelSim等第三方EDA 工具来完成设计任务的综合与仿真。

Quartus II与MATLAB和DSP Builder结合可以进行基于FPGA的DSP系统开发,方便快捷。

Quartus II还内嵌SOPC Builder,可实现SOPC系统的开发。

Quartus II 9.0主界面如图3.1示。

图 3.1 Quartus II 9.0界面3.1 Quartus II 基本设计流程Quartus II 设计的主要流程包括创建工程、设计输入、分析综合、编译、仿真验证、编程下载等,其一般流程如图 3.2所示。

下面以硬件描述语言输入法设计计数器为例,说明Quartus II 的设计流程。

3.1.1 创建工程使用Quartus II 设计电路被称作工程。

Quartus II 每次只进行一个工程,并将该工程的全部信息保存在同一个文件夹中。

开始一项新的电路设计,首先要创建一个文件夹,用以保存该工程的所有文件。

之后便可通过Quartus II 的文本编辑器编辑Verilog 源文件并存盘。

3.1.2 设计输入Quartus II 中包含原理图输入和硬件描述语言输入两种方法。

(1)原理图输入原理图输入的优点是,设计者不必具有诸如编译技术、硬件描述语言等新知识就能迅速入门,完成较大规模的电路系统的设计,且具有直观,易于理解的特点,适合于初学者使用。

FPGA设计流程指南、八、,前言本部门所承担的FPGA 设计任务主要是两方面的作用:系统的原型实现和ASIC 的原型验证。

编写本流程的目的是:在于规范整个设计流程,实现开发的合理性、一致性、高效性。

形成风格良好和完整的文档。

实现在FPGA 不同厂家之间以及从FPGA 到ASIC 的顺利移植。

便于新员工快速掌握本部门FPGA 的设计流程。

由于目前所用到的FPGA 器件以Altera 的为主,所以下面的例子也以Altera 为例,工具组合为modelsim + LeonardoSpectrum/FPGACompilerII + Quartus ,但原则和方法对于其他厂家和工具也是基本适用的。

目录1. 基于HDL 的FPGA 设计流程概述 (1)1.1 设计流程图 (1)1.2 关键步骤的实现 (2)1.2.1 功能仿真 (2)1.2.2 逻辑综合 (2)1.2.3 前仿真 (3)1.2.4 布局布线 (3)1.2.5 后仿真(时序仿真) (4)2. Verilog HDL 设计 (4)2.1 编程风格( Coding Style )要求 (4)2.1.1 文件 (4)2.1.2 大小写 (5)2.1.3 标识符 (5)2.1.4 参数化设计 (5)2.1.5 空行和空格 (5)2.1.6 对齐和缩进 (5)2.1.7 注释 (5)2.1.8 参考C 语言的资料 (5)2.1.9 可视化设计方法 (6)2.2 可综合设计 (6)2.3 设计目录 (6)3. 逻辑仿真 (6)3.1 测试程序( test bench) (7)3.2 使用预编译库 (7)4. 逻辑综合 (8)4.1 逻辑综合的一些原则 (8)4.1.1 关于LeonardoSpectrum (8)4.1.1 大规模设计的综合 (8)4.1.3 必须重视工具产生的警告信息 (8)4.2 调用模块的黑盒子( Black box )方法 (8)参考修订纪录10101. 基于HDL的FPGA设计流程概述1.1设计流程图(1)设计定义说明:逻辑仿真器主要指modelsim,Verilog-XL等。

2 Quartus II软件的使用、开发板的使用

本章将通过3个完整的例子,一步一步的手把手的方式完成设计。

完成这3个设计,并得到正确的结果,将会快速、有效的掌握在Altera QuartusII软件环境下进行FPGA设计与开发的方法、流程,并熟悉开发板的使用。

2.1 原理图方式设计3-8译码器

一、设计目的

1、通过设计一个3-8译码器,掌握祝组合逻辑电路设计的方法。

2、初步了解QuartusII采用原理图方式进行设计的流程。

3、初步掌握FPGA开发的流程以及基本的设计方法、基本的仿真分析方法。

二、设计原理

三、设计内容

四、设计步骤

1、建立工程文件

1)双击桌面上的Quartus II的图标运行此软件。

开始界面

2)选择File下拉菜单中的New Project Wizard,新建一个工程。

如图所示。

新建工程向导

3)点击图中的next进入工作目录。

新建工程对话框

4)第一个输入框为工程目录输入框,用来指定工程存放路径,建议可根据自己需要更改路径,若直接使用默认路径,可能造成默认目录下存放多个工程文件影响自己的设计,本步骤结束后系统会有提示(当然你可不必理会,不会出现错误的)。

第二个输入框为工程名称输入框。

第三个输入框为顶层实体名称输入框,一般情况下保证工程名称与顶层实体名称相同。

设定完成后点击next。

指定工程路径、名称

5)设计中需要包含的其它设计文件,在此对话框中不做任何修改,直接点击next。

工程所需其它文件对话框

6)在弹出的对话框中进行器件的选择。

在Device Family框中选用Cyclone II,然后在Available device框中选择EP2C35F484C8,点击next进入下一步。

器件选择界面

7)下面的对话框提示可以勾选其它的第三方EDA设计、仿真的工具,暂时不作任何选择,在对话框中按默认选项,点击next。

第三方EDA工具选择

8)出现新建工程以前所有的设定信息后,点击finish完成新建工程的建立。

工程信息

2、建立图形设计文件

1)在创建好设计工程后,选择File下拉菜单中New菜单。

工程下新建设计文件

2)在New对话框中选择Device Design Files页下的Block Diagram/Schematic File,点击OK,出现原理图编辑窗口。

建立Block Diagram/Schematic File

原理图编辑界面

图形编辑器

3)在图形编辑器窗口的工作区双击鼠标左键,或点击图中的符号工具按钮,用鼠标点击单元库前面的“+”号,展开元件库,选择所需要的元器件,点击OK 按钮,所选的符号将显现在图形编辑器的工作区域。

元件库对话框

选择所需的元件

用库元件按原理图完成设计设计好的原理图顶层文件

4)完成图形编辑的输入后,需要保存设计文件,该原理图文件作为本设计的顶层文件,注意顶层文件的名称要与工程名一致。

保存顶层文件

3、对设计文件进行编译

点击菜单栏中的Start compiler按钮进行设计文件的全编译。

如果文件有错,在软件的下方会提示错误的原因和位置。

整个编译完成,软件会提示编译成功。

编译

4、对设计文件进行仿真

1)创建一个波形文件,在File下拉菜单中选择New,选取对话框的Other File标签下的VectorWaveform File,点击OK,打开一个空的波形编辑器窗口。

建立一个仿真波形文件

波形文件设置界面

2)加入输入、输出端口,在波形编辑器窗口的左边端口名列表区双击,在弹出的菜单中选择Node Finder按钮。

Insert Node or Bus对话框

3)出现Node Finder界面后,在Filer列表中选择Pins:all,点击List,在Node Finder窗口出现所有的信号名称,点击中间的“》”按钮则Selected Nodes 窗口下方出现被选择的端口名称,点击OK。

Node Finder对话框

Node or Bus 其他设置(暂不设置时点击OK)

波形编辑器中已加入的端口

5)制定输入端口的逻辑电平变化,最后保存该仿真波形文件,文件名与工程名相同。

波形编辑器工具栏

编辑输入端口波形

保存波形文件

6)进行仿真设置。

在软件中选择Assignments 下拉菜单下的setting命令,打开仿真器设置窗口。

设置菜单

选择Simulator Settings页面下的simulator mode下的Funtional,即做功能仿真,(也可选择simulator mode下的Timing,即做时序仿真,则下面的产生功能仿真网表文件可以跳过,直接Start simulation)然后点击OK即可。

仿真设置

功能仿真(or时序仿真)设置

然后产生功能仿真网表文件,选择Processing下拉菜单下Generate Function Simulation,产生功能仿真网表;

产生功能仿真网表(功能仿真必做,时序仿真不需要该步)点击开始仿真的START按钮开始进行仿真:

运行仿真后的仿真结果

5 引脚分配

6 完整工程的编译

7 下载到目标器件

1)下载设置

2)下载

五、实验现象。