Bandgap reference voltage and current

- 格式:doc

- 大小:56.00 KB

- 文档页数:4

电力电子-专业词汇中英文对照(一)AbsorberCircuit 吸收电路AC/ACFrequencyConverter 交交变频电路ACpowercontrol交流电力控制ACPowerController交流调功电路ACPowerElectronicSwitch交流电力电子开关AcVoltageController交流调压电路AsynchronousModulation异步调制BakerClampingCircuit贝克箝位电路Bi-directionalTriodeThyristor双向晶闸管BipolarJunctionTransistor--BJT双极结型晶体管Boost-BuckChopper升降压斩波电路Boost Chopper升压斩波电路BoostConverter升压变换器BridgeReversibleChopper桥式可逆斩波电路BuckChopper降压斩波电路BuckConverter降压变换器Commutation 换流Conduction Angle 导通角ConstantVoltageConstantFrequency--CVCF 恒压恒频ContinuousConduction--CCM (电流)连续模式ControlCircuit 控制电路CukCircuit CUK斩波电路CurrentReversible Chopper 电流可逆斩波电路CurrentSourceTypeInverter--CSTI 电流(源)型逆变电路Cycloconvertor 周波变流器DC-AC-DC Converter 直交直电路DCChopping 直流斩波DCChoppingCircuit 直流斩波电路DC-DCConverter 直流-直流变换器DeviceCommutation 器件换流DirectCurrentControl 直接电流控制DiscontinuousConductionmode (电流)断续模式displacementfactor 位移因数distortionpower 畸变功率doubleendconverter 双端电路drivingcircuit 驱动电路electricalisolation 电气隔离fastactingfuse 快速熔断器fastrecoverydiode 快恢复二极管fastrevcoveryepitaxialdiodes 快恢复外延二极管fastswitchingthyristor 快速晶闸管fieldcontrolled thyristor 场控晶闸管flybackconverter 反激电流forcedcommutation 强迫换流forwardconverter 正激电路frequencyconverter 变频器fullbridgeconverter 全桥电路fullbridgerectifier 全桥整流电路fullwaverectifier 全波整流电路fundamentalfactor 基波因数gate turn-offthyristor——GTO 可关断晶闸管generalpurposediode 普通二极管gianttransistor——GTR 电力晶体管halfbridgeconverter 半桥电路hardswitching 硬开关highvoltageIC 高压集成电路hysteresiscomparison 带环比较方式indirectcurrentcontrol 间接电流控制indirectDC-DCconverter 直接电流变换电路insulated-gatebipolartransistor---IGBT 绝缘栅双极晶体管intelligentpowermodule---IPM 智能功率模块integratedgate-commutatedthyristor---IGCT 集成门极换流晶闸管inversion 逆变latchingeffect 擎住效应leakageinductance 漏感lighttriggeredthyristor---LTT 光控晶闸管linecommutation 电网换流loadcommutation 负载换流loopcurrent 环流电力电子-专业词汇中英文对照(二)1backplane背板2Bandgapvoltagereference带隙电压参考3benchtopsupply工作台电源4BlockDiagram方块图5BodePlot波特图6Bootstrap自举7BottomFETBottomFET8bucketcapacitor桶形电容9chassis机架11constantcurrentsource恒流源12CoreSaturation铁芯饱和13crossoverfrequency交叉频率14currentripple纹波电流15CyclebyCycle逐周期16cycleskipping周期跳步17DeadTime死区时间18DIETemperature核心温度19Disable非使能,无效,禁用,关断20dominantpole主极点21Enable使能,有效,启用22ESDRatingESD额定值23EvaluationBoard评估板24Exceedingthespecificationsbelowmayresultinpermanentdamagetothedevice,ord evicemalfunction.OperationoutsideoftheparametersspecifiedintheElectricalChar acteristicssectionisnotimplied.超过下面的规格使用可能引起永久的设备损害或设备故障。

淺談參考電壓(Voltage Reference)CIC 林千智大多數的類比電路,都需要參考用的電壓、電流、或是『時間』。

參考電壓提供一個準則,如DAC或ADC的LSB大小、穩壓器(Regulator)的輸出電壓位準、電池充電器的開與關等,都是由參考電壓源或參考電流源所提供及決定。

近年來,由於製程的進步,以及環保的需求,使得系統操作電壓不斷地下降,舊式的各種參考電壓線路逐一失效。

本文將介紹於各個電壓下,一些典型的參考電壓產生方式。

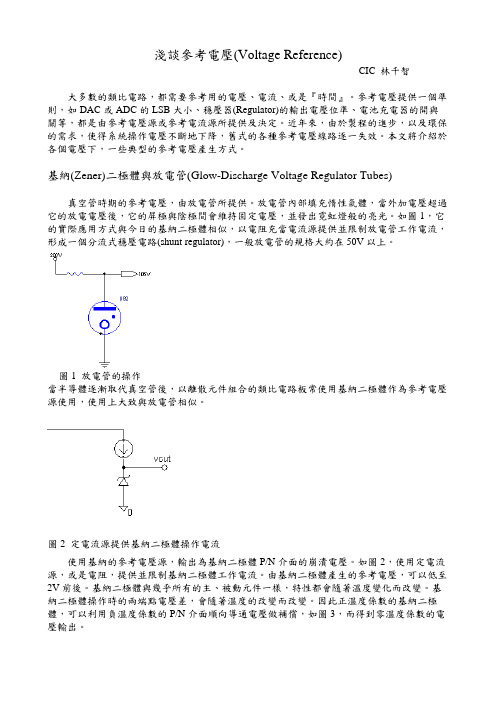

基納(Zener)二極體與放電管(Glow-Discharge Voltage Regulator Tubes)真空管時期的參考電壓,由放電管所提供。

放電管內部填充惰性氣體,當外加電壓超過它的放電電壓後,它的屏極與陰極間會維持固定電壓,並發出霓虹燈般的亮光。

如圖1,它的實際應用方式與今日的基納二極體相似,以電阻充當電流源提供並限制放電管工作電流,形成一個分流式穩壓電路(shunt regulator),一般放電管的規格大約在50V以上。

圖1 放電管的操作當半導體逐漸取代真空管後,以離散元件組合的類比電路板常使用基納二極體作為參考電壓源使用,使用上大致與放電管相似。

圖2 定電流源提供基納二極體操作電流使用基納的參考電壓源,輸出為基納二極體P/N介面的崩潰電壓。

如圖2,使用定電流源,或是電阻,提供並限制基納二極體工作電流。

由基納二極體產生的參考電壓,可以低至2V前後。

基納二極體與幾乎所有的主、被動元件一樣,特性都會隨著溫度變化而改變。

基納二極體操作時的兩端點電壓差,會隨著溫度的改變而改變。

因此正溫度係數的基納二極體,可以利用負溫度係數的P/N介面順向導通電壓做補償,如圖3,而得到零溫度係數的電壓輸出。

圖3 以負溫度係數P/N 介面 順向導通電壓進行補償 圖4 以VBE Multiplier放大P/N 接面電壓提供負溫度係數電壓的二極體,如圖4,常用"VBE multiplier",得到一個可以放大倍率調整的P/N 順向導通電壓。

带隙基准电压校准eetop -回复带隙基准电压校准(Bandgap Voltage Reference Calibration)是集成电路设计中的一个重要环节。

带隙基准电压是指在特定工作温度下产生的恒定电压,用于校准其他模拟电路元件的偏置电压,从而提高整个集成电路的工作准确性和稳定性。

本文将一步一步回答有关带隙基准电压校准的问题。

第一步:什么是带隙基准电压?带隙基准电压是指在特定工作温度下产生的恒定电压。

基于物理原理,带隙基准电压可由基于半导体材料的差分电压或其他电路元件产生。

其中,差分电压产生的带隙基准电压是最常用的。

第二步:带隙基准电压校准的目的是什么?带隙基准电压的校准旨在使得产生的恒定电压在特定工作温度下与预期值保持一致。

校准的目的是提高集成电路的工作准确性和稳定性。

这对于模拟电路的准确测量以及数字电路的正常运行非常重要。

第三步:为什么需要对带隙基准电压进行校准?在半导体材料制造过程中,微小的材料和工艺变化可能导致带隙电压的偏移。

而这种偏移会直接影响到其他模拟电路元件的偏置电压,从而引起整个集成电路的准确性和稳定性问题。

因此,对带隙基准电压进行校准是必要的。

第四步:带隙基准电压校准的方法有哪些?常见的带隙基准电压校准方法包括两点校准法和三点校准法。

两点校准法通过在待校准电路中添加大小相等、理论值已知的校准电阻,将输出电压与预期值进行比较并进行调整,从而实现电压校准。

三点校准法基于两个特定温度下的差分电压,计算带隙能。

第五步:校准过程中需要注意哪些问题?在进行带隙基准电压校准时,需要注意以下问题:1. 温度:校准过程需要进行温度控制,以确保带隙基准电压在特定工作温度下产生。

同时,还需要考虑温度对电阻、电容和电感等元件的影响。

2. 稳定性:校准过程需要考虑带隙基准电压的长期稳定性。

在实际应用中,校准电路应具有能够抵消温度波动和材料老化等因素影响的稳定性。

3. 精度:校准电路的精度直接影响到整个集成电路的准确性。

收稿日期:2021-01-15基金项目:陕西省自然科学基础研究计划项目(2020JM -583)通信作者:唐威,教授,博士,研究方向为集成电路设计㊂E-mail :tangwei @xupt .edu .cn电子元件与材料Electronic Components and Materials第40卷Vol .40第4期No .44月Apr2021年2021宽温度范围高精度基准电压源设计师洋洋,唐㊀威,刘㊀伟(西安邮电大学电子工程学院,陕西西安㊀710121)摘㊀要:针对传统Brokaw 型带隙基准电压源温度系数较高的问题,采用高阶曲率补偿方法,利用PN 结反向饱和电流随温度敏感变化的原理,通过将与基准电压温度系数呈相反趋势的补偿电流注入到基准核心部分,对基准输出电压进行温度补偿,实现了宽温度范围内基准电压源的高精度输出㊂电路基于0.18μm BCD 工艺设计㊂仿真结果表明,在3.3V 电源电压下,基准输出电压为1.978V ,在-40~+150ħ温度范围内,基准电压的温度系数为5.82ˑ10-6/ħ,低频时电源抑制比(PSRR )为79.4dB ㊂关键词:带隙基准;高精度;宽温度范围;曲率补偿中图分类号:TN 432文献标识码:ADOI :10.14106/j .cnki .1001-2028.2021.1736引用格式:师洋洋,唐威,刘伟.宽温度范围高精度基准电压源设计[J ].电子元件与材料,2021,40(4):387-392.Reference format :SHI Yangyang ,TANG Wei ,LIU Wei.Design of a wide -temperature -range and high -precision voltage reference [J ].Electronic Components and Materials ,2021,40(4):387-392.Design of a wide -temperature -range and high -precision voltage referenceSHI Yangyang ,TANG Wei ,LIU Wei(School of Electronic Engineering,Xi an University of Post and Telecommunications,Xi an㊀710121,China)Abstract :A high -order curvature compensation method was used to solve the problem of high temperature coefficient of the traditional Brokaw bandgap reference.Since the reverse saturation current of PN junction changes sensitively with temperature and its trend with temperature is opposite to the reference voltage ,it was inputed into the core part of the reference as the compensation current ,and the temperature compensation of the output voltage was realized.As a result ,a high precision output of the reference was obtained over a wide temperature range.The circuit was designed based on 0.18μm BCD process.The simulation results show that the output voltage is 1.978V under 3.3V supply voltage.The temperature coefficient of thereference voltage is 5.82ˑ10-6/ħin the temperature range of -40~+150ħ.The PSRR is 79.4dB at low frequency.Key words :bandgap reference ;high precision ;wide -temperature rage ;curvature compensated㊀㊀带隙基准电压源因具有较低温度系数和较高电源抑制比的特点,被广泛用于DC -DC ㊁模数转换器(ADC )以及低压差线性稳压器(LDO )等数模混合集成电路中[1-2]㊂传统的带隙基准电压源是通过将双极型晶体管具有负温度系数的基极-发射极电压(V BE )与正温度系数(PTAT )的电压(ΔV BE )以适当的权重相加,从而得到零温度系数的输出电压值㊂然而,传统的带隙基准电压源仅对温度特性曲线进行一阶补偿,难以满足现代高精度系统的要求㊂为了得到低温漂的基准电压源,需要进行高阶补偿[3-5]㊂对此,许多文献提出了不同的补偿方法来降低温度系数㊂文献[6]采用分段补偿技术,通过在电路中加入两个不同的曲率补偿电路,在低温段和高温段分别实现对基准电压的曲率补偿,但这种电路较复杂,且电源抑制比(PSRR )较低;文献[7]利用MOS 管工作在亚阈值区时漏电流和栅源电压的非线性特性,通过引入与基电子元件与材料准电压温度系数成相反趋势的高阶补偿电流对基准电压进行曲率补偿;虽然文献[7]在宽温度范围内降低了温度系数,但是由于使用了较多的三极管,导致占用的面积较大㊂本文设计的带隙基准电压源基于Brokaw 基本结构,利用PN 结的反向饱和电流随温度敏感变化的原理,在高温段进行了曲率补偿,使其在-40~+150ħ的宽温度范围内表现出5.82ˑ10-6/ħ的低温漂特性㊂1㊀传统Brokaw 型带隙基准电压源图1是传统的Brokaw 型带隙基准结构㊂图中,运算放大器的输出端与Q 1㊁Q 2的基极相连,为Q 1㊁Q 2提供基极电流㊂由于运算放大器的电压钳位作用使得电阻R 3和R 4上的电压降相等,若R 3=R 4,则流过R 3和R 4两条支路的电流相等,此时三极管Q 1和Q 2的基极-发射极电压差为:ΔV BE =V BE1-V BE2=V T ln I S2I S1æèçöø÷=V T ln N (1)于是流过电阻R 1的电流为:I =ΔV BE R 1=V T ln N R 1(2)则流过电阻R 2的电流为2I ㊂该电流作用在R 2上,可以产生一个具有正温度系数的电压,将该电压与Q 2的基极-发射极电压V BE 相加,便可得到输出电压V REF的表达式为:V REF =V ΒΕ2+2R 2R 1V Τln N(3)通过改变R 1㊁R 2的大小,可以获得一个与温度无关的基准电压㊂由文献[8]可知,三极管的基极-发射极电压V BE随温度变化并不是线性的,它可以表示为[9]:V BE (T )=V G0-T T 0(V G0-V BE0)-(η-α)V T ln(T T 0)(4)式中:T 为热力学温度;T 0是参考温度;V G 0是在温度为T 0时的发射结电压;η是与工艺有关但与温度无关的常数;α的值与集电极电流I C 的温度特性有关(当I C 与温度成正比时,α=0;当I C 与温度无关时,α=1)㊂图1㊀传统Brokaw 型带隙基准电压源Fig .1㊀Conventional Brokaw -type bandgap voltage reference式(4)中的V T ln (T /T 0)体现出非线性项,式(3)只能实现一阶温度补偿,获得近似零温度系数的基准电压㊂因此,要得到高精度的基准输出电压,必须对V BE 的非线性分量进行高阶补偿㊂2㊀宽温度范围高精度基准电压源设计本文设计的宽温度范围高精度基准电压源整体电路如图2所示,包含启动电路㊁偏置电路㊁带隙基准核心电路和曲率补偿电路㊂2.1㊀带隙基准核心电路图2中的Q 3㊁Q 4和R 5~R 9以及运算放大器(M 16~M 23)组成一阶带隙基准电压源㊂其中,Q 3和Q 4发射极结面积之比为1ʒ8,R 5=R 6㊂利用运放的 虚短 特性,钳位A 点和B 点电压,使得V A =V B ㊂假设Q 3和Q 4的集电极电流为I 1,则:I 1=ΔV BE R 8=V T ln8R 8(5)由KCL 有流过R 9和R trim 的电流为2I 1,所以有:V C =V E4-V R8=2I 1(R 9+R trim )=V E3(6)因此Q 3基极电压为:V B3=V C +V BE3=2I 1(R 9+R trim )+V BE3(7)于是带隙基准电压可表示为:㊃883㊃师洋洋,等:宽温度范围高精度基准电压源设计V REF =2(R 9+R trim )R 8V T ln8+V BE3(8)然后通过电阻升压网络可得到基准输出电压V OUT :V OUT =V REF R 3+R 4R 4æèçöø÷=2(R 9+R trim )R 8V T ln8+V BE3éëêêùûúúR 3+R 4R 4(9)为了产生零温度系数的带隙基准电压,对V OUT 关于温度T 求偏导,即: V OUT T= V T T2(R 9+R trim )(R 3+R 4)ln8R 8R 4+V BE3 TR 3+R 4R 4(10)由式(10)可看出,通过调节电阻R 3㊁R 4㊁R 8和R 9的比值即可得到理想的零温度系数的基准输出电压V OUT ,然后通过分压网络可得到多个零温度系数电压值,分别为电路中需要的模块提供参考㊂其中,R trim 的作用是为了解决实际生产中的偏差失配问题加入的修调电阻,减少误差㊂式(9)是在理想条件下得到的基准输出电压值㊂图2中,由于三极管Q 3㊁Q 4存在来自于R 3的基极电流,这就导致R 3和R 4上的电流不一致,使V OUT 在V REF 的基础上产生一定的温差,并且精度㊁电源抑制比等参数也会受到影响[10]㊂因此,式(9)的表述并不准确,本文通过在Q 3㊁Q 4的基极加入电阻R 7来消除基极电流带来的误差[11]㊂首先假设三极管Q 3和Q 4的基极电流为I b ,则加入电阻R 7后带隙基准电压可表示为:VᶄREF =2(ΔV BE -I b R 7)R 8(R 9+R trim )+V BE3㊀㊀㊀㊀㊀㊀㊀=2(R 9+R trim )R 8ΔV BE +V BE3-2I b R 7R 8(R 9+R trim )=V REF -2I b R 7R 8(R 9+R trim )㊀㊀㊀㊀㊀㊀(11)式(11)第二项多项式中I b 随温度变化,使得V ᶄREF在V REF 基础上多了一个随温度变化的微小变量,从而导致基准输出电压V OUT 的温度特性也发生了一定的变化㊂由于Q 3和Q 4从R 3抽取了两份基极电流,因此基准输出电压可表示为:VᶄOUT=VᶄREF R 3+R 4R 4æèçöø÷+2I b R 3㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀=V REF -2I b R 7R 8(R 9+R trim )éëêêùûúúR 3+R 4R 4æèçöø÷+2I b R 3=V OUT -2I bR 7R 8(R 9+R trim )R 3+R 4R 4æèçöø÷+2I b R 3(12)图2㊀宽温度范围高精度基准电压源整体电路Fig .2㊀The complete circuit diagram of the voltage reference withwide -temperature -range and high -precision㊀㊀由式(11)可以看出,对于带隙基准电压V ᶄREF 来讲,即使加入了R 7仍然可以通过调节R 8和R 9的比值来得到一个零温度系数的基准电压㊂对于基准输出电压V ᶄOUT 来讲,通过调节R 7(R 9+R trim )(R 3+R 4)R 8R 4的值,使之等于R 3,即可将式(12)的后两项消除,从而㊃983㊃电子元件与材料可得到R7的值为:R7=R3R4R8(R3+R4)(R9+R trim)(13)2.2㊀曲率补偿电路曲率补偿电路由M28-M30和Q5构成㊂I S由BE结短接的NPN晶体管Q5形成,补偿电流I COMP1和I COMP2通过M28-M30电流镜结构分别注入到A点和B点,对PTAT电流进行补偿㊂IS可以表示为:I S(Τ)=CΤγexp(-qV G0kΤ)(14)式中:C是与PN结的结面积及掺杂浓度有关的常数;γ在一定温度范围内也是常数;VG0为绝对零度时PN 结材料的导带底和价带顶电势差,对于给定的PN结材料,V G0为定值;q为电子的电荷量;k为玻尔兹曼常数;T为热力学温度㊂令λ=qV G0k,并用泰勒展开式e xʈ1+x+x22+x36展开,则I S可以表示为:I SʈC(Tγ-λTγ-1+λ2Tλ-22-λ3Tλ-36)(15)图2中,M28㊁M29和M30的宽长比为1ʒ8ʒ1,于是补偿电流I COMP1和I COMP2为:I COMP1=C(Tγ-λTγ-1+λ2Tλ-22-λ3Tλ-36)=I S㊀(16)I COMP2=8C(Tγ-λTγ-1+λ2Tλ-22-λ3Tλ-36)=8I S(17)经过一阶补偿和曲率补偿后的带隙基准电压可以表示成:V REF=V BE3+2R9+R trim()R8V Tln8+R9+R trim()I COMP1+I COMP2()=V BE3+2ln8R9+R trim()R8V T+R9+Rtrim()I COMP1+I COMP2()=V BE3+2ln8R9+R trim()R8KTq+R9+Rtrim()I COMP1+I COMP2()(18)将式(18)代入式(9)可得到基准输出电压V OUT的表达式为:V OUT=R3+R4R4æèçöø÷V BE3+2ln8R9+R trim()R8KTq+éëêê㊀㊀㊀㊀R9+R trim()I COMP1+I COMP2()ùûúú(19)令K0=R3+R4R4K1=2K ln8(R3+R4)(R9+R trim)qR4R8K2=(R3+R4)(R9+R trim)(C+8C)R4ìîíïïïïïïïï(20)结合式(16)~(17)和式(19)~(20)可得基准输出电压为:V OUT=K0V BE3(T)+K1T+K2(Tγ-λTγ-1+λ2Tλ-22-λ3Tλ-36)(21)式中:K0为负温度系数电压V BE3的系数;K1为一阶温度补偿系数;K2为高阶曲率补偿系数㊂其中一阶温度补偿系数K1主要与R8和R9的比值相关,而高阶曲率补偿系数K2主要与PN结面积相关㊂2.3㊀偏置电路图2中,偏置电路由电流源(M1~M9㊁Q1㊁Q2和R1)和电流偏置(M10~M15)组成㊂正常工作时,电流源产生与电源电压无关的PTAT电流后,经过电流镜成比例复制给电流偏置部分,为M16管提供偏置电压㊂令M1~M5的宽长比相等,Q1和Q2流过的集电极电流相同,假设该电流为I PTAT,Q1和Q2发射极结面积比为8ʒ1,忽略它们的基极电流,于是有:ΔV BE=V T ln I PTAT8IS2æèçöø÷-V T lnI PTATI S2æèçöø÷=V T ln8(22)I PTAT=ΔV BER1=V T ln8R1(23)通过M1~M4㊁M10㊁M12和M15电流镜结构将IPTAT按比例精确复制,产生偏置电流和M16偏置电压㊂2.4㊀启动电路带隙基准电路中,电路存在 简并 偏置点,当电源上电时,所有的晶体管均传输零电流,于是它们㊃093㊃师洋洋,等:宽温度范围高精度基准电压源设计可以无限期地保持关断,因此需要设计启动电路㊂启动电路仅应在上电时提供启动功能,当基准核心电路建立稳定后保持关闭或低功耗状态,如图2所示,M 24~M 27和C 1构成启动电路㊂当电源刚开始上电的时候,并且提供有效的使能信号EN 1,EN 1和EN 2互为反向信号,启动电路开始工作㊂EN 1为低电平时,EN 2为高电平,M 25关闭,M 26的栅端没有电荷,栅电压为0,M 23管关闭,因此Q 3基极没有电流注入;随着电源电压逐渐上升,EN 1为高,EN 2为低,M 25管导通,M 26栅端电压被抬高,从而将M 23管的栅端电压拉低,M 23管导通,开始从电源汲取电流,并注入基准核心电路,使基准核心电路开始工作;同时,M 25管的漏电流逐渐增大并对电容C 1充电,M 26栅端的电压逐渐升高,当基准核心电路正常工作时,M 23的漏端电压升高,使M 27管导通㊂从而将M 26栅端电压拉低,M 26管关断,启动电路关闭㊂3 电路仿真验证基准电压源电路采用0.18μm BCD 工艺设计,并使用Spectre 工具进行仿真验证㊂仿真条件为:V DD =3.3V ,温度范围为-40~+150ħ㊂图3和图4分别是补偿前与补偿后的基准输出电压温度特性的仿真结果㊂从图中可以看出,没有进行高阶补偿的温度系数为17.52ˑ10-6/ħ,补偿后的温度系数为5.82ˑ10-6/ħ,补偿后温度系数降低了11.7ˑ10-6/ħ,精度提高了66.8%㊂图3㊀补偿前的基准输出电压温度特性Fig .3㊀Temperature characteristics of the reference outputvoltage before compensation图5是在V DD =3.3V ,不同工艺角下基准输出电压随温度变化的仿真结果㊂从图5可以看出,在TT工艺角下基准电压源有最佳温度系数值5.82ˑ10-6/ħ,在SS 工艺角下有最差温度系数值14.6ˑ10-6/ħ㊂图6是当V DD =3.3V ,温度为27ħ时,在TT ㊁SS ㊁FF 三种工艺角下,基准电压源的电源抑制比(PSRR )仿真结果㊂从图6可以看出,低频时,TT 工艺角下的PSRR 为79.4dB ,在10kHz 时电源抑制比也有58.9dB㊂图4㊀补偿后的基准输出电压温度特性Fig .4㊀Temperature characteristics of the reference outputvoltage aftercompensation图5㊀基准电压源在不同工艺角下的温度特性Fig .5㊀Simulation results for different processcorners图6㊀基准电压源的电源抑制比曲线Fig .6㊀PSRR curves of the voltage reference表1为本文与部分参考文献带隙基准源的性能比较㊂从表1可看出,本文设计的基准电压源的温度系数优于文献[7-8],低频下的PSRR 也优于文献[6-8],且本文设计的基准电压源具有可调节的多值输出电压㊂㊃193㊃电子元件与材料表1㊀本文与其他文献带隙基准源的性能参数对比Tab.1㊀Performance parameters comparison of bandgapreference source of this paper and other literatures参数文献[6]文献[7]文献[8]本文工艺(μm)0.180.180.250.18电源电压(V) 3.3 5.0 4.5 3.3温度范围(ħ)-40~+125-40~+150-40~+150-40~+150温度系数(10-6/ħ) 3.02 6.9410 5.82 PSRR(dB)5777.47079.4基准输出电压(V)1.241 1.229 1.214 1.978是否多值输出否否否是4㊀版图设计版图的匹配性决定了基准电压源精度的误差大小㊂由式(9)和式(10)可知,电阻比值的大小直接影响着基准输出电压的精度和温漂特性㊂因此本文设计将基准电压源中的所有电阻放置在同一区域,并采用叉指法以减少工艺刻蚀造成的误差㊂此外,对于电流源电路和带隙核心电路中使用的三极管部分的版图,本文设计由8个并联的NPN三极管分别构成Q1㊁Q4,分布在Q2和Q3周围,使Q1和Q2㊁Q3和Q4均形成对称性匹配㊂图7为基准电压源的版图㊂其中,运算放大器㊁偏置电路和电阻都分别进行了合理的布局㊂图7㊀基准电压源版图Fig.7㊀Layout of the reference voltage source5㊀结论本文在传统的Brokaw型带隙基准电压源的基础上,设计了一种宽温度范围高精度的基准电压源㊂利用PN结反向饱和电流随温度敏感变化的原理在高温段产生与基准电压温度系数呈相反趋势的补偿电流,对传统的一阶补偿的带隙基准电压源进行曲率补偿,提升了基准输出电压的精度和温漂特性,并采用电阻分压网络输出多个不同的零温度系数电压值㊂仿真结果表明,在3.3V电源电压下,-40~+150ħ温度范围内,TT工艺角下,基准电压源温度系数为5.82ˑ10-6/ħ;低频时PSRR为79.4dB,通过合理的版图设计,可以应用到数模混合芯片中㊂参考文献:[1]Kostanyan H T,Hayrapetyan A K,Petrosyan A S,et al.5V widesupply voltage bandgap reference for automotive applications[C]//39th International Conference on Electronics and Nanotechnology (ELNANO).NY,USA:IEEE,2019:229-232.[2]Abbasi M U,Raikos G,Saraswat R,et al.A high PSRR ultra-lowpower1.2V curvature corrected bandgap reference for wearable EEG application[C]//13th International New Circuits and Systems Conference(NEWCAS).NY,USA:IEEE,2015:1-4. [3]Hu J L,Sun J,Bai Y B,et al.A novel1.03ppm/ħwide-temperature-range curvature-compensated bandgap voltage reference[C]//2nd International Conference on Circuits System and Simulation(ICCSS).NY,USA:IEEE,2018:22-26.[4]An J H,Wu C J,Xu D C.A wide temperature range4.6ppm/ħpiecewise curvature-compensated bandgap reference with no amplifiers[C]//International Conference on IC Design and Technology(ICICDT).NY,USA:IEEE,2019:1-4.[5]王永顺,崔玉旺,赵永瑞,等.宽温度范围高精度带隙基准电压源的设计[J].固体电子学研究与进展,2016,36(1):54-59. [6]张东亮,曾以成,陈星燕,等.曲率补偿低温漂带隙基准电压源设计[J].电子元件与材料,2015,34(11):85-88. [7]李树镇,冯全源.一种CMOS高阶曲率补偿的带隙基准源电路的设计[J].哈尔滨工业大学学报,2017,49(10):95-99. [8]张龙,冯全源,王丹.一种带曲率补偿的低功耗带隙基准源设计[J].电子元件与材料,2014,33(9):58-61.[9]Wang Y F,Sun J,Ye W X.A high-order temperature compensatedCMOS bandgap reference[C]//3rd International Conference on Cloud Computing and Internet of Things(CCIOT).NY,USA: IEEE,2018:325-328.[10]Zhu G Q,Yang Y T,Zhang Q D.A4.6-ppm/ħhigh-ordercurvature compensated bandgap reference for BMIC[J].IEEE Transactions on Circuits and Systems II:Express Briefs,2019,66: 1492-1496.[11]杨宁,史仪凯,袁小庆,等.高精度㊁低功耗带隙基准源及其电流源设计[J].传感技术学报,2014,27(1):58-63.㊃293㊃。

1.5-V高阶曲率补偿CMOS带隙基准源摘要此报告中设计了一种新的低电平,低噪声,高阶曲率补偿CMOS带隙基准源。

此带隙电路用两个电阻串来减小电源电压。

此外,由高阻抗的多晶硅电阻和扩散电阻产生的热敏电阻比来提供高阶补偿。

此所设计的带隙基准电压源能在1.5V电源电压下工作(此时0℃时V th=0.9V),它的温度系数小于15.2ppm/℃,平均电源调整率为5.5mV/V。

1.简介基准电压源是许多电子元器件的主要组成,例如电源转换器,数字转化器,射频电路。

温度对带隙基准电压源的影响毫无疑问会影响它的性能。

因此低电平,低功率,低温飘带隙基准电压源在工业生产中越来越重要。

事实上,许多现有的技术都能减小基准电压源的温度系数,如Song等人提出的二次温度补偿, Rincon-Mora等人提出的分段线性曲率校正。

Audy和Lewis等人分别提出了更简单的基于热敏电阻比来加以实现的二阶和三阶曲率补偿带隙基准源。

这个方法被Leung等人进一步发展为高阶曲率补偿用于CMOS带隙基准电压源的设计。

曲率补偿CMOS带隙基准电压源利用一个负温度系数的高阻抗多晶硅电阻和一个正温度系数的扩散电阻来产生一个热敏电阻比,以此能够有效地减少此带隙基准源的温度漂移。

以上电阻都能在CMOS工艺中实现。

有过报道的最低工作电源电压为2V,这对于将来的应用还远不够低。

为了未来应用中进一步减小所要求的电源电压,这里提出一种基于以上理论的低电压曲率补偿带隙基准源。

它利用两个完全相同的电阻串来同时提供曲率补偿和电压电平摆幅。

在文章中,我们所设计的低电压带隙基准电压源将在第2章节中介绍。

影响基准电压源精确度的重要设计因素,包括如电流镜匹配,放大器的偏移电压和输出噪声。

章节3中的实验结果证实了这一结论。

章节4为最后的总结。

2.我们所设计的曲率补偿带隙基准源此低电压,高阶曲率补偿带隙基准源的电路结构和完整原理图分别如图1.和图2.所示。

图1.高阶曲率补偿带隙基准源的电路结构图2. 高阶曲率补偿带隙基准源的原理图在常规设计中,电源电压被误差放大器的PMOS输入级电压V GS所制约,而为了降低电源电压,应使用NMOS作为误差放大器的输入级。

摘要近年来随着IC设计要求的不断开展,集成电路幅员设计是实现集成电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是否正确,而且也会极大程度地影响集成电路的性能、本钱。

而集成电路中的bandgap可以在温度和电压不稳定的环境中保持稳定的参考电压,被广泛运用于比拟器、A/D转换器等模拟电路及数模混合信号集成电路中,其性能直接影响整个系统的精度和性能。

因此,bandgap幅员设计的研究非常有意义。

本文基于Cadence 幅员设计软件平台,采用XFAB0.6µm CMOS 工艺设计。

设计的幅员元件包括PMOS、NMOS、PNP三极管、电阻、电容。

其中对差分放大器、电流镜、电阻等重要元件采用了匹配和对称的设计方法,考虑电气特性的幅员设计技术;为防止闩锁效应,本设计还运用了保护环保护整个电路,提高了bandgap 电路的可靠性。

本设计对最终设计出的幅员使用calibre验证工具进展LVS和DRC验证,并顺利通过验证。

关键字:幅员;带隙基准电压源;Cadence;匹配;验证ABSTRACTIn recent years, along with IC design request of continuously development, IC layout are essential to achieve the design of integrated circuit manufacturing sectors, it is not only related to the IC's functions are correct, but also great extent affect IC performance and cost.But bandgap reference voltage of integrated circuit can keep stability in the unsteady environment of the temperature and the electric voltage of reference electric voltage, used extensively in comparison machine, A/D conversion machine etc. analog electric circuit and some mixture signal integrated circuit. Its function is directly influence the whole accuracy and function of system. Therefore, the research which take the layout design of the bandgap reference voltage is very meaningful.This text ,according to the design software of the Cadence about layout design, adopts XFAB0.6µm CMOS of design rule.The component of layout design include PMOS, NMOS, PNP, electric resistance, electric capacity. To the OP、current and resistance which are importance components adopt layout design technique of consideration electricity characteristic; To reduce latch-up, this design still uses guard ring to protect the whole electric circuit, improving the credibility of bandgap reference voltage.In the end, this design carried LVS and DRC of verification to the landscape used calibre verification tool that finally designs and passed a verification smoothly.Key Words: Layout; Bandgap reference voltage; Cadence; matching; Symmetry目录第1章引言11.1选题背景及意义11.2国内微电子开展状况1第2章Bandgap简介32.1 什么是Bandgap32.2 Bandgap的原理32.3 Bandgap的应用6第3章 Virtuoso工具及幅员绘制7 3.1 Cadence 软件介绍73.2 Virtuoso工具的使用8建立幅员库8层选择窗的设置11幅员编辑窗的设置13的常用快捷键15第4章Bandgap的幅员设计18 4.1幅员设计中的相关主题18器件的匹配规那么18匹配管子的幅员设计22电阻幅员设计25倒比管幅员设计26双极型晶体管幅员设计27电容幅员设计284.2全局规划〔floor plan〕294.2.1模块摆放294.3整体布线30第5章Bandgap电路幅员验证32 5.1幅员验证的概述325.2幅员的DRC验证335.3 幅员的LVS验证37完毕语42参考文献43致谢44附录46外文资料原文50第1章引言1.1选题背景及意义随着IC工艺的开展,在模拟电路和数模混合电路中,片内集成的基准源电路已被普遍采用,它是集成电路中的一个重要模块。

Bandgap Reference VoltageChun-Ping Huang, Ying-Shun Chuang, Tzu-Hen Hsucphuang@Abstract-A bandgap reference voltage is an essential component of an analog-to-digital converter. It is often used to supply a reference voltage which is compared with other voltages. There are some problems arising from temperature-dependent to power supply rejection ratio when implementing a bandgap reference circuit. The main design criteria for this project is toachieve PSRR above 60dB and a variation less than 3% resulting from temperature changes between 27℃ and 85℃. The wholearchitecture is shown in Fig. 1Figure 1 Circuit of BGR1. IntroductionThe bandgap reference used in diverse applications is based on the idea of Hilbiler in 1964[1]. A bandgap reference voltage with low sensitivity to temperature and supply voltage is commonly required in analog or digital circuits. There are several methods to realize a temperature independent voltage. The base emitter junction used as a core component of the bandgap reference is the most popular approach. The general bandgap reference voltage is described by a linear combination of base-emitter voltage. We can compensate temperature dependent voltage by adding a positive-TC voltage to a negative-TC voltage. The temperature behavior of a pn junction voltage is described by2ln g c BE T TT s s E I V V V V T T I I KT ∂∂=−−∂∂ where is the thermal voltage. With T at room temperature and =750mv,T V BE V 1.5/o BEV mv K T∂≈−∂. The positive-TC voltage comes from the voltage difference between two pn junctions. The Fig. 2 shows the reason behind positive-TC voltage.12ln ln ln c c BE BE BE T T T S SI IV V V V V V I nI −=∆=−=nwhere n equals to the current density ratio ofto .2Q 1QFigure 2 Generation of temperature independent voltage Ideally, adding a positive-TC voltage to anegative-TC voltage can realize a zero temperature coefficient 1.26V at the room temperature. Additionally, the reference voltage is required to be robust to the power supply voltage. An easy way to improve power supply rejection ratio (PSRR) is to increase the open loop gain.2. Circuit of the BGRA. Start Up CircuitThe transistors have two states, on and off,when power is provided. In order to make sure the circuit works properly, we need a mechanism which can provide a small current to flow through Op Amp and enableit. This mechanism is also required to beturned off when Op Amp works properly. The start up circuit [2] is presented in Fig. 3. The start-up circuit consists of transistors, M13-M15. The mechanism works as the following. Since M13 is also in saturation, it provides a sufficient gate voltage for M15 to turn on. When M15 is on, a small current will flow through Op Amp and enable the entire circuit. Furthermore, M14 will turn on and sink all the current from M13 and disable M15. Then the start-up circuit isdisabled.Figure 3 Start up circuitB. Differential AmplifierIn the circuit depicted in Fig 4., we need to force node X and Y to have the same voltage. We use an operational amplifier for this purpose. It is composed by thecommon-source stages with diode-connected loads. In order to increase the gain, we stack two pmos transistors into it and its gain can be expressed as()108860810//v m m mb o o A g g g r r r ≈+⎡⎤⎣⎦Its output provides a bias for the entire circuits, and a feedback loop is formed. Therefore, this bias voltage ideally provides a constant gs V for the pmos transistors anda constant current can be obtained.Figure 4 Differential gain stageC. BandgapFig. 5 [3] [5] shows the basic bandgap circuit. Because of high gain of Op Amp, the voltage at node X and Y is forced to be equal.Figure 5 Bandgap circuitX V ===+Y V 1BE V 2BE V 11I R × whereln(cBE T sI V V I =. Therefore,121ln BE BE T V V V n I R −==×1The voltage difference between the two pn junctions is the positive-TC voltage. Thecurrent across 1R equals to 1ln()TV n R which is called the proportional to absolute temperature (PTAT) current. A PTAT current can be copied from the current mirror and can be adjusted by changing the width of M12 or the resistance of 1R . Adding a positive-TC voltage 22I R to a base-emittervoltage, the negative-TC voltage, canachieve a temperature independent voltage.The ideally reference voltage equals 321ln() 1.26T ref BE V n V V R V R =+=The n is usually chosen to be eight for the layout purpose. 3. SimulationThe reference voltage is required to be 1.26V at the room temperature. The relationship between reference voltage and base-emitter voltage is given by32ref BE V V I R 2=+ (1)The base-emitter voltage is 0.75V at 25℃. We can set the PTAT current going through 2R to be 54µA. Therefore, from the equation (1), the resistance of 2R can bedetermined by 1.260.759.454V VK µ−≈For Cadence simulation, the appropriate 2R is 9.37K. Fig. 6 shows the reference voltage changes with temperature ranging from 27℃ to 85℃ and 10 % supply voltage variation. The reference voltage changes around 7.24mV . The is very low sensitive to the changes of the temperature.refV Figure 6 Temperature dependence ofbandgap output voltageThe power supply rejection ratio is shown in Fig. 6. From Fig. 6, the circuit of the BGR is robust to the power supply when thetemperature changes from 27℃ to 56℃. The exact PSRR and reference voltages for certain values are depicted in the Table 1.Temperature (℃) V oltage Variation 27℃ 376.707µV 55.6℃ 499.067µV 85℃1.25189mVTable 1 Outcomes of PSRR and reference voltage at certain temperature.4. ConclusionA design using bandgap core circuit with Op amp and start-up circuit is presented and simulated. The overall performance of the BGR circuit is summarized in the Table 2. The schematic layout is shown in Figure 7.Parameter Measured Supply voltagerange2.5V±10%Temperaturerange27℃ to 85℃.V REF 1.26079V~1.25365VPSRR >52dB Powerconsumption 0.5W Layout dimension68.06µ×84.62µTable 2 Summary of performanceFigure 7 Layout of BGRComparisons with other design are shown in table 3.Design 1 [3]Our DesignSupply V oltage1V 2.5VPSRR >40dB>60dBTemp. Variation 1.2mV~5.4mV (-20℃~50℃) 7mv 0.58%≅(27℃ to85℃) Table 3(a) Comparison between differentdesigns Design 1 [4] Our Design Supply V oltage 2V 2.5VTemp. Variation <0.1% (-30℃~125℃)7mv ≅0.58%(27℃ to 85℃)Power Consumption2.2mW 0.5mWTable 3(b) Comparison between different designs5. References[1] D. F. Hilbiber, “A new semiconductor voltage standard”, ISSCC Digest Technical Papers, vol. 7, pp. 32-33, 1964[2] David Jones, “Analog Integrated CircuitDesign”[3] K. Lasanen, V. Korkala, “Design of a 1-V low power CMOS bandgap reference based on resistive subdivision”, IEEE[4] T. L. Brooks and A. L. Westwick, “A low-power differential CMOS bandgap reference,” in ISSCC Dig. Tech. Papers, Feb. 1994, pp. 248–249.[5] Behzad Razavi, “ Design of Analog CMOS Integrated Circuits”, McGRAW-Hill, 2000。

Bandgap reference voltage and current

The voltage difference between two diodes, often operated at the same current and of different junction areas, is used to generate a

p roportional t o a bsolute t emperature (PTAT) current in a first resistor. This current is used to generate a voltage in a second resistor. This voltage in turn is added to the voltage of one of the diodes (or a third one, in some implementations). The voltage across a diode operated at constant current, or here with a PTAT current, is c omplementary t o

a bsolute t emperature (CTAT—reduces with increasing temperature), with approximately −2 mV/K. If the ratio between the first and second resistor is chosen properly, the first order effects of the temperature dependency of the diode and the PTAT current will cancel out. The resulting voltage is about 1.2–1.3 V, depending on the particular technology, and is close to the theoretical 1.22 eV bandgap of silicon at 0 K. The remaining voltage change over the operating temperature of typical integrated circuits is on the order of a few millivolts. This temperature dependency has a typical parabolic behavior.

Because the output voltage is by definition fixed around 1.25 V for typical bandgap reference circuits, the minimum operating voltage is about 1.4 V, as in a CMOS circuit at least one drain-source voltage of a FET(field effect transistor) has to be added. Therefore, recent work concentrates on finding alternative solutions, in which for example currents are summed instead of voltages, resulting in a lower theoretical limit for the operating voltage (Banba, 1999).

Note that sometimes confusion arises when using the abbreviation CTAT, where the "C" is incorrectly taken to mean "c onstant" rather than

"c omplementary". To avoid this confusion, although not in widespread use, the term c onstant w ith t emperature (CWT) is sometimes used.

有三种获得与温度无关的恒定电压的方法,一种是利用齐纳二极管的反向击穿电压,也就是稳压二极管,第二种是利用耗尽MOS管和增强型MOS管的阈值电压的差值,第三种是利用负温度系数的pn结电压加上一个与温度成正比的电压来相互抵消,得到与温度无关的参考电压。

第一种方法现在不常用,因为齐纳二极管的反向击穿电压比大多数应用的电源电压还高,第二种在多数CMOS工艺中也用不上,因为多数CMOS工艺中只制造增强管,不制造耗尽管。

第三种方法是现在用得最多的,也就是常说的bandgap reference,中文称为带隙基准。

要怎样得到第三种方法中说的正温度系数电压和负温度系数电压呢?

先说正温度系数电压,pn结电流与结电压的关系为指数关系,即I=Is

exp(qV/kT),其中Is为pn结反向饱和电流,对于三极管的be结来说(CMOS工艺中如何得到三极管下面再说),be结电流为基极和集电极电流之和,忽略基极电流,则be结电流与集电极电流相等,Ic=Is exp(qVbe/kT),则be电压Vbe=(kT/q)ln(Ic/Is)。

与绝对温度成正比。

如果有两个Vbe相减,则得

Vbe1-Vbe2=(kT/q)ln(Ic1/Ic2),与绝对温度成正比,而且与Ic,Is的具体值无关,只与两只管子的Ic的比值相关。

对于负温度系数的电压,是在1967年,有人[Brugler,1967]计算出be结电压的数值具有负温度。

这里直接给出公式:

Vbe=Vg0(q-T/T0)+Vbe0T/T0+mkT/q ln(T0/T) + kT/qln(Jc/Jc0),其中Vg0为0开尔文温度时的硅原子禁带宽度电压,T0为某一参考电压,m为一个值大约为2.3的温度常数,Vbe0为温度T0下的be电压,Jc为温度T(即当前温度)进的be结电流密度,Jc0为温度T0时的结电流密度。

这样,通过搭配适当的这两个值的和,就可以得到一个在T时与温度无关的电压量,求搭配系数的方法,就是将两者的和对温度取微分,再令微分结果为0即得到两者的比例关系。

计算后得到的与温度无关的电压量刚好等于硅禁带宽度加上一个小电压量,因此就称这样得到的电压为“带隙基准”。

电路中如何让这两者相加呢?对于Vbe,可以直接利用,对于Vbe1-Vbe2则一般是通过其差值加在电阻上转换成电流,再将相同的电流流过加在三极管集电极上的电阻上间接得到Vbe1-Vbe2,这样两者相加,就得到了与温度无关的量。