基于FPGA控制的三相变频电源系统的设计

- 格式:pdf

- 大小:6.05 MB

- 文档页数:97

基于FPGA的三相电源发生器的研制许文建;卞正林;周晓【摘要】We employ FPGA and auxiliary circuits to devise a 57 V and 50 Hz three-phase power generator. We also perform functionality simulation with software Quartus II and inspect smoothness and stability of waveform with development platform DE2. This generator is devised with modularized structure and includes a signal generation module, a PWM module and some necessary auxiliary circuits. It has stronger functionalities, smaller volume, better flexibility and higher interference suppression capability, as compared with other similar products with identical functionalities. It therefore can provide convenient power supply for many experiments in industrial applications.%利用FPGA器件以及辅助电路实现了57 V,50 Hz实时三相电源的产生,并在QUARTUSⅡ环境下进行了功能仿真,通过DE2开发平台验证了波形的光滑度以及稳定度.系统的设计采用模块化设计思想,分为信号发生模块、PWM模块以及必要的外围电路.与类似产品相比,该系统功能强大,体积缩小,工作灵活性和抗干扰能力相对较高,可为工业应用中的许多实验场合提供方便的实验电源.【期刊名称】《山东科学》【年(卷),期】2011(024)003【总页数】5页(P55-58,63)【关键词】FPGA;三相电源;QUARTUS Ⅱ【作者】许文建;卞正林;周晓【作者单位】泰兴市产品质量监督检验所,江苏泰兴225400;泰兴市产品质量监督检验所,江苏泰兴225400;江苏省减速机产品质量监督检验中心,江苏泰兴225400【正文语种】中文【中图分类】TM91波形发生器是一种常用的信号源,广泛应用于科学研究、工业生产、教学实验等领域。

河南科技学院新科学院2012届本科毕业设计(设计)三相变频电源设计学生姓名:王斌所在系别:机电系所学专业:电气工程及其自动化导师姓名:田泽正完成时间:2012年5月15日摘要本设计了一个交流—直流—交流变频电源系统。

该系统利用三相电压桥式逆变,并以FPGA 为控制核心, 采用SPWM变频控制技术, 实现了三相正弦波变频输出。

其输出线电压有效值为36 V, 最大输出电流有效值达3 A。

此外,系统还具有频率测量、电流和电压有效值测量及平均功率测量等功能。

变频技术在电源中的应用,极大地减小了电源装置的体积,提高了效率,产生了巨大的经济效益,所谓变频就是利用电力电子器件(如功率晶体管GTR、绝缘栅双极型晶体管(IGBT)将5OHz的市电变换为用户所要求的交流电或其他电源。

它分为直接变频(又称交―交变频),即把市电直接变成比它频率低的交流电,大量用在大功率的交流调速中;间接变频(又称交—直—交变频),即先将市电整流成直流,再变换为要求频率的交流。

它又分为谐振变频和方波变频。

前者主要用于中频加热,方波变频又分为等幅、等宽和SPWM变频。

常用的方法有正弦波(调制波)与三角波(载波)比较的SPWM法、磁场跟踪式SPWM法和等面积SPWM法等。

逆变技术,是指整流技术的逆向变换方式。

关键词:逆变器,变频电源,脉宽调制,FPGAAbstractAn AC- DC- AC variable- frequency power supply system based on IM14400 is designed in this paper, which uses FPGA as control core. The frequency converting controlling technology of sinusoidal pulse width modulation (SPWM) is applied to get the output of three- phase variable- frequency sine wave. The RMS voltage is 36V and the maximum RMS current is up to 3A. The system also includes the following functions, Such as frequency meaurement RMS voltage and current measurement, and mean power measurement. Frequency of application of technology in the power supply, greatly reducing the power supply unit volume, improve efficiency, resulting in huge economic benefits, the so-called conversion is the use of power electronic devices (such as power transistors GTR, insulated gate bipolar transistor IGBT) 5OHz the city will be transformed into electricity requested by users or other AC power supply. It is divided into direct-conversion (also known as AC - AC converter), that is converted directly intoelectricity than its low frequency of the alternating current, a large number used in the high-power AC Drive Central; indirect conversion (also known as AC - Direct - AC Inverter ), which is first rectified into DC electricity, and then transformed into the frequency of communication required. It consists of resonant frequency and the square-wave inverter. The former is mainly used for medium frequency heating, square-wave frequency is divided into equal amplitude, width and the SPWM inverter. Commonly used methods are sine wave (modulated wave) and the triangular wave (carrier) to compare the SPWM method, the magnetic field Tracking SPWM law and the equal-area SPWM method. Inverter technology is the rectification of the reverse transformation method.Keywords:Inverter,Variable frequency power supply,PWM,IM14400,FPGA目录1 绪论 (1)1.1 课题的提出 (1)1.2 课题研究背景 (1)1.3 国内外相关研究情况 (3)1.4设计的对象 (4)2 系统总体设计方案 (4)2.1 三相正弦波变频电源设计要求 (4)2.2 三相正弦波变频电源系统设计方案比较 (4)2.3,系统总体设计方案 (6)3 系统主要功能的实现 (9)3.1 整流滤波电路的设计 (9)3.2 斩波和驱动电路 (9)3.3 逆变及驱动电路 (11)3.4 PWM 信号的产生方式 (13)3.5 SPWM 调制方式的选择 (14)3.6 测频电路 (15)3.7 AD637简介及应用电路 (15)3.8 过压保护与过流保护电路设计 (16)3.9 单片机电路设计 (18)4 理论分析与参数计算 (19)4.1 SPWM 逆变电源的谐波分析 (19)4.2 载波频率的选择 (20)5 系统软件设计 (21)5.1 程序开发语言 (21)5.2 VHDL硬件描述语言简介 (22)5.3 正弦波顶层设计程序 (22)6 结论 (24)致谢语 (24)参考文献 (25)附录:电路总图 (26)1 绪论1.1 课题的提出由于我国市电频率固定为50 Hz, 因而对于一些要求频率大于或小于50 Hz 的应用场合, 则必须设计一个能改变频率的变频电源系统。

基于FPGA的变频调速控制系统设计摘要:现代电力电子电路的控制旨在实现高速开关的计算机控制,并且朝着更高频率更低损耗和全数字化的方向发展。

现场可编程门阵列器件是最近这些年来崭露头角的一类新型集成电路,它的优势是简洁,经济,高速度,低功耗等。

同时具有全集成化,适用性强,方便开发和维护等明显优点。

同单片机,和DSP相比FPGA的频率更高,速度更快。

这些特点适应了电力电子电路的逐步高频化和复杂化发展的需要。

所以越来越多的领域中FPGA 获得了日益广泛的发展和使用。

FPGA进行设计可以简化系统的硬件结构,降低成本,并且显著改变系统的处理能力。

本文提出的FPGA设计方案可以实现数字化变频调速控制。

该系统能够产生三相正弦脉宽波形,该系统具有控制简洁,精确,易修改,可现场编程等特点,可以广泛应用于PMW变频调速系统的全数字化控制。

文中对方案的进行进行了详细的论述。

主要包括系统设计的理论分析,系统结构设计,以及在FPGA硬件上的实现,最终验证了该控制系统的可行性和有效性。

数字化是该系统的特点,系统最终生成的三相SPMW脉冲三相正弦调制波和三角载波比较得到的。

设计过程中,充分结合FPGA 器件的结构特点,产生三项正弦调制波,同三角载波通过比较器比较厚,最终得到三相SPWM脉冲序列。

概述:设计所要实现的功能:产生多路PWM波形从而实现变频调速的功能。

设计所采用的基本思想:通过调节电源频率可以调节电机的实际转速。

基于FPGA可以将所选定的变频调速控制方式和控制算法实现出来,形成输出目标控制信号的硬件电路。

系统模块设计与仿真根据系统所要实现的功能系统总体结构可以分为正弦信号生成模块,三角波产生电路D/A 转换器正弦波和三角波比较模块。

正弦波信号生成模块:生成正弦波样本,有直接数字频率合成器实现。

它主要是针对系统所需要的针线信号,做出正弦调制波模块的设计,同时在生成正弦信号的过程中完成对波形幅值的控制。

三角载波生成模块:生成三角载波,通过mif文件生成器生成三角波文件,得到三角波数据,与正弦信号生成模块中得到的数字正弦波进行比较,生成脉宽调制信号。

基于FPGA数控变频电源的设计谭本军(湖南张家界航空工业职业技术学院 湖南 张家界 427000)摘 要: 通过对PWM调制信号控制变频电源的分析研究,提出设计的基本方案,重点分析硬件设计和基于FPGA的数控部分的设计。

这种设备的输出电压具有在一定范围内幅值、频率可调的优点,能最大限度满足用户对各种交流电源的需求。

变频电源的核心技术是逆变控制系统,基于FPGA的逆变控制系统其实时性很强。

关键词: 变频电源;FPGA;逆变;SPWM中图分类号:TN86 文献标识码:A 文章编号:1671-7597(2012)1120065-021 绪论 3 硬件的设计3.1 直流母线电压源的设计现代人们的生活和发展离不开电能,但是受历史、经济等各方面的原因的影响,世界各国的电网指标还没有统一的标单端反激式变换器是指,当数字控制器的PWM调制信号控准,例如我国内地工频电压一般采用的是220V/50Hz交流电,制MOS管驱动电路导通时,次级侧的整流二极管处于截止状而台湾、美国、日本等地区使用的工频电压一样为态,能量以磁能的形式存储在变压器的初级侧的电感线圈中;110V/60Hz,英国的工频电压为240V/50Hz等,这样就给许多进当PWM调制信号控制MOS管截止时,次级侧的整流二极管处于导出口的家用电器、医疗仪器及工业设备的直接使用带来很多麻通状态,储存在初级侧线圈的能量通过互感效应传递到次级烦。

而且由于发电厂的发电功率有限,在用电高峰期和电低峰侧,经过低压整流滤波电路输出相应的DC电压,完成DC-DC降期整个电网工作在欠压或过压状态,还有工频电压抗干扰性很压变换。

3.2 直流母线调压电路的设计差很容易受到外界高频设备、雷电的影响,造成整个电源不能正常使用,那么设计一种能产出纯净的、稳定的、在一定范围调节电压幅值可以有两种方法:1)在要求输出高电压、内电压频率和幅值可调节的电源尤为重要,变频电源(交流电低精度、快速响应的情况下保持母线电压不变调节调制度;2)力频率转换器)就能满足我们的要求。

摘要:介绍了基于FPGA设计+的三相PWM发生器。

该发生器具有灵活和可编程等优点,可应用于交流电机驱动用的三相电压源逆变器。

实验结果验证了本设计的有效性。

关键词:脉宽调制 现场可编程门阵列随着现代工业的要求和微电子技术的进步,交流传动已经迅速地从模拟控制转向数据控制,其中PWM技术与方法是其核心内容。

但数字化PWM电路一直是设计中的难点,除了集成三相PWM发生器的80C196MC、TMS320F240等微处理器外,均采用中小规格集成电路设计感想 PWM,这是非常复杂的,往往使电路复杂、可靠性差。

本文介绍了一种用单片大规模FPGA实现的三相PWM发生器,它具有三相脉冲中心对称、PWM周期和死区时间可编程等特点,且性能优异、灵活性和可靠性高。

1 基本原理本设计的目的是产生三相逆变器的PWM信号波形。

图1是用FPGA实现的PWM部分设计框图,它主要由脉宽寄存器、缓冲寄存器、周期寄存器、死区寄存器、死区发生器、数值比较器、控制逻辑等几部分构成。

脉宽寄存器,决定三相PWM信号的脉宽;缓冲寄存器,实现对脉宽数据的双缓冲;周期寄存器,决定PWM的斩波周期;死区寄存器,决定上下桥臂的死区时间。

脉宽寄存器在每个开关周期中由微处理器与更新一次,其输出数据经缓冲以后与基准计数器进行数值比较,得到三相PWM信号PA、PB、PC。

再经过死区电路处理,最后产生6个中心对称的PWM驱动信号,驱动三相逆变器的6个功率器件。

PWM算法可采用SPWM(正弦PWM)或者SVPWM(空间矢量PWM)。

FPGA中的基准计数器,用来产生类似模拟电路中的三角波基准,是一个最小计数值为0、最大计数值为周期寄存器中保存的数值、计数方向交替变化的可逆计数器。

基准计数器单元在最大计数值时产生一个同步信号SYN,当它有效时将三个脉宽寄存器的数据存入各自的缓冲寄存器,实现双缓冲,使三个脉宽寄存器在SYN 无效时可依次由微处理器更新而不影响最终的三相同步关系。

基于FPGA的SVPWM 3相PWM逆变器控制IC摘要:本文提出了一种新的空间矢量脉宽调制(SVPWM)电路的实现方法。

SVPWM控制IC采用先进的现场可编程门阵列(FPGA)技术-xilink公司生产的两种基于RAM的FPGA技术xc4003和xc4010用于SVPWM IC的设计,同时数字电流控制定子电流调节环路模块也可嵌入在此SVPWM IC内。

SVPWM IC和数字信号处理器(DSP)一起提供高性能交流驱动器的整体解决方案。

通过仿真和实验结果验证了SVPWM控制IC设计的正确性。

Ⅰ.导言在交流电机驱动器和空调系统中交流电源脉宽调制(PWM)交直流转换器有着广泛的应用。

PWM调制策略对很多转换器实现最小谐波和转换损耗具有重要的作用,特别是针对三相应用。

近年来已发展成各种调制策略、控制方案和实现技术随着微电子技术的进展,微处理器或DSPs 被广泛用于各种电源转换系统的设计和应用,尤其是在脉宽调制(PWM)逆变控制器[2]-[3]。

脉宽调制策略实施基于微处理器的硬件和软件的灵活性、精确的控制,少组件、低成本和紧凑的优点。

然而,在各种应用程序和有限制字长的影响下,对于调制策略的选择,微处理器的有限的计算能力也必须仔细考虑。

超大规模集成电路技术的快速变化已经从根本上改变了设计过程。

现代电子产品的生命周期,甚至可能比其设计周期还短。

因此,需要快速的原型制造成为了现代电子产品的设计挑战。

现场可编程门阵列(FPGA)技术的出现,使数字系统的快速原型机制造成为可能[4]。

FPGA的实现为PWM策略提供了优势,如:快速原型、简单的硬件和软件设计,更高的转换频率,并释放微处理器的计算负载。

本文提出了一种基于FPGA的PWM IC的三相电源转换器的设计和实施。

空间矢量PWM(SVPWM)的技术是通过PWM IC实现。

设计的PWM IC可用于交流电机驱动器或三相交流电压调节系统。

PWM IC设计也可作为数字化交流电机驱动器的电流环路的一部分。

![基于FPGA控制的三相功率平衡装置[实用新型专利]](https://uimg.taocdn.com/8aa748284028915f814dc28d.webp)

专利名称:基于FPGA控制的三相功率平衡装置

专利类型:实用新型专利

发明人:王雷,宋元锋,荆延飞,王金,巩帅奇,牟忠,李军,李婷婷申请号:CN201620830602.4

申请日:20160801

公开号:CN205846734U

公开日:

20161228

专利内容由知识产权出版社提供

摘要:本实用新型涉及一种基于FPGA控制的三相功率平衡装置,包括依次连接的系统电源U、输出电抗器L、三相全桥逆变单元,三相全桥逆变单元的连接串联的电容C1、C2,电容C1、C2的中点连接零线电抗器L,零线电抗器L连接零线N;系统电源U与输出电抗器L之间连接电压互感器,输出电抗器L与三相全桥逆变单元之间穿接输出电流互感器,电容C1和电容C2两端连接直流采用互感器,电压互感器、输出电流互感器和直流采用互感器通过调理电路接口连接调理电路,调理电路通过AD采样芯片连接FPGA,FPGA分别连接ARM和DSP。

本实用新型能够有效消除配电网中三相负荷不平衡以及零线电流过大的电能质量问题,提高了输出补偿精度,具有较好的补偿效果和较高的系统可靠性。

申请人:山东锦华电力设备有限公司

地址:256408 山东省淄博市桓台县唐华路609号

国籍:CN

代理机构:青岛发思特专利商标代理有限公司

代理人:巩同海

更多信息请下载全文后查看。

基于FPGA的三相SPWM控制器的设计黄玉健;甘国妹;黄永庆【摘要】研究者基于FPGA设计了一种三相SPWM控制器,该设计器以Altera公司的Cyclone III系列的EP3C25Q240C8芯片作为控制核心,结合直接数字频率合成技术(DDS),利用Verilog语言和LPM宏模块设计生成三相SPWM控制器.设计仿真结果以及用逻辑分析仪SignalTap II采样显示的结果表明,该三相SPWM控制器具有调制波频率、载波频率、调制度、载波比以及死区时间均可以灵活调节的优点,生成的三相SPWM波适应性强,可方便应用于逆变电源的变频调压以及电机变频调速等领域.【期刊名称】《玉林师范学院学报》【年(卷),期】2017(038)005【总页数】8页(P41-48)【关键词】三相SPWM控制器;FPGA;DDS【作者】黄玉健;甘国妹;黄永庆【作者单位】梧州学院图像处理与智能信息系统广西高校重点实验室,广西梧州543002;玉林师范学院电子与通信工程学院,广西玉林 537000;梧州学院图像处理与智能信息系统广西高校重点实验室,广西梧州 543002【正文语种】中文【中图分类】TN7411 引言PWM((Pulse Width Modulation)脉冲宽度调制技术是非常重要的电气控制技术,在高性能要求的电机变频调速、步进电机精细控制、变频调压电源、电力电子逆变控制等方面均有非常重要的应用[1]. 当进行脉冲宽度调制的时候,使系列脉冲的占空比按照正弦规则来排列,那么输出的信号经过D/A转换和滤波可以得到正弦波形的电压,就是正弦波脉冲宽度调制(Sinusoidal PWM),亦即SPWM[3]. 相比于其他方式的脉冲宽度调制,诸如空间矢量PWM、随机采样PWM、电流滞环PWM、自然采样PWM、等面积采样PWM或规则采样PWM 等,SPWM在电气控制技术等应用中,产生的谐波成分最小,所以应用也最广泛[1]. 在交流电机变频调速和逆变电源的变频调压等领域,SPWM控制技术已经得到非常广泛的应用.目前有多种能够产生SPWM脉宽调制波的方法,常用的方法中,一种是典型的传统的方法,即利用模拟电路对正弦调制波与三角载波进行比较来产生SPWM脉冲. 该种设计电路复杂,难以与数字系统连接,对于复杂要求很难满足;另一种是使用具有生成PWM波的专用芯片,如TI公司的DSP芯片TMS320F240和TMS320F2812等,该种方法也是数字化设计,但通常不够灵活,比如只能产生6路或12路的PWM信号[3]. 而基于FPGA的方法设计产生SPWM脉宽调制波,暨可以利用FPGA并发执行的速度优势来实现实时生成SPWM波形,也可以利用FPGA半定制电路的特点来实现快速灵活的硬件编程[2],使产生的SPWM波形具有调制波频率、载波频率、调制度、载波比以及死区时间均可以根据需要灵活调节的优点.本文的组织结构如下:第2节对SPWM产生技术原理、基于FPGA的数字直接频率合成(DDS)信号发生器产生调制波的正弦波技术原理进行理论分析;第3节应用FPGA内部丰富的半定制逻辑电路,根据技术原理设计出DDS三相正弦信号发生器、三角波发生器、幅度控制器、比较器以及死区控制电路;第四节对设计出来的三相SPWM控制器进行仿真和输出波形分析. 第5节对本文进行总结.2 基于FPGA的三相SPWM控制器设计原理2.1 SPWM波形产生技术原理图1 SPWM波生成原理图图1是SPWM波生成原理图,图1上方等腰三角波是载波,正弦波是调制波. 用数字方式生成SPWM波形原理是,先把载波等腰三角波和调制波正弦波均用数字方式产生,然后这两路数字波形信号通过一个数字比较器进行比较,如果三角波大于正弦波,则比较器输出0,反之,如果正弦波大于三角波,则比较器输出1.图1下方输出的脉冲波形就是产生的SPWM波形.从上述SPWM波形产生技术原理中知道,要产生三相SPWM波形,就必须要先生成三相调制波正弦波和载波三角波. 然后分别让三相正弦波和三角波通过比较器,按SPWM波生成原理输出相应的三个SPWM波形,就可以得到三相SPWM波形. 图2就是三相SPWM控制器电路模块图[1].图2中有5个部分构成,分别是DDS正弦波发生模块、三角波发生模块、幅度控制模块、比较器模块以及死区控制模块. 下面介绍这5个模块的作用.DDS正弦波发生模块主要是用来产生三相调制波正弦波,分别是0°正弦波、120°正弦波和240°正弦波.该模块也产生三角波发生模块所需的时钟信号tri_CLK,其实就是按DDS原理产生的一个方波信号. 该模块产生的另外一个时钟信号D_CLK是频率两倍于系统时钟信号CLK0频率的一个时钟信号,用来作为死区控制模块的系统时钟.图2 三相SPWM控制器电路模块图三角波发生模块就是用来产生载波三角波,在三角波的数据位已经确定的情况下,其频率由时钟信号tri_CLK的频率来决定,这可以通过DDS正弦波发生模块内部相对应的频率控制字来调节,也可以通过对应的频率控制字来调节三角波频率和三相正弦波频率的变化关系来决定是同步调制还是异步调制. 这里涉及一个参数是载波比,是指载波三角波频率ftri和调制波正弦波的频率fsin的比值,记为Kf,即理论上载波比越大输出精度也越高,也就是输出SPWM波形通过IGBT硬件电路后还原为正弦波的精度越高,但过大的载波比也要求IGBT的开关频率极高,导致开关管高功率损耗,甚至于无法满足过高的开关频率. 所以,载波比的选择要针对实际需要并结合具体的IGBT器件性能来选择. 通过改变DDS正弦波发生模块内部相对应的频率控制字,可以灵活调节正弦波和三角波的频率,进而调节载波比. 幅度控制模块的作用是用来调节正弦波和三角波的相对幅值度. 因为要灵活改变输出SPWM波形的调制度,就得通过改变正弦波和三角波的相对幅值大小来实现. 调制度,是指调制波正弦波的幅值Vsin和载波三角波幅值Vtri的比值[5],记为KA,即一般上,调制度KA的范围在0到1之间,实际的范围通常还要小. 如果KA>1,则称为过调制. 调制度反映了载波的幅度受低频调制信号控制的程度. 在应用SPWM设计的变频电源中,通过更改调制度KA可以方便的调节输出电压. 而在本设计中,可以通过改变正弦波的幅值系数AML_sin和三角波的幅值系数AML_tri 来实现调制度KA的灵活调节.比较器模块的作用,就是通过输入调整幅值之后的三相正弦波和三角波,通过比较器,按照SPWM生成原理来生成输出三相SPWM波形,分别为SPWM_A、SPWM_B和SPWM_C.死区控制模块是为了保护IGBT,防止上下桥臂同时导通而烧毁IGBT器件. 每一相SPMW波形控制一对IGBT器件,SPWM信号和SPWM相反状态的信号各控制一个,通过延迟上升沿变化信号的变化时间来防止这一对IGBT同时导通,设置的延迟时间就称为死区时间. 为了得到更精确的死区时间,死区控制模块的时钟D_CLK为系统时钟CLK0的两倍,通过锁相环技术得到. 本设计中,系统时钟CLK0为50MHz,D_CLK为100MHz.2.2 基于FPGA的DDS正弦波生成原理[6]图3 DDS结构原理图图3为基于FPGA的DDS正弦波生成结构原理图. 它的典型结构主要由相位累加器、相位调制器、正弦ROM查找表和DA转换器以及低通滤波器构成. 由于本设计的最终目的不是生成正弦波,生成数字化正弦波后还要结合数字化三角波最终生成SPWM波形,设计中整个过程都是数字化设计,所以图3中不需要DA转换器以及低通滤波器.在图3中,相位累加器是DDS波形信号发生器的核心,功能是完成信号的相位累加功能. 相位调制器的作用是对相位累加器的输出信号进行相位调制. 正弦波ROM 查找表的功能是完成一个周期离散正弦数据查表的转换,相位调制器的输出就是ROM的地址值,根据地址值找到相应的离散正弦数据,输出一个周期的离散正弦波数据就得到一个周期的数字化正弦波.根据DDS原理,输出正弦波的频率为[7]:式(3)中,fclk是系统基准时钟clk的频率,N是相位累加器的数据位宽度,B 是频率控制字,也称频率输入字. 在硬件已经确定,也就是fclk和N都已经设计定型的情况下,输出频率值就由当时输入的频率控制字B来确定. 而且频率控制字B的数据位宽度也是N.而对于DDS系统输出正弦波的频率分辨率Δf,即俗称输出频率最小步进值,就是频率控制字B步进一个最小间隔,亦即B=1对应的频率输出值. 由公式(3)得到:由公式(3)和公式(4)可知,只要基准频率fclk足够高频足够稳定,同时N足够大,利用DDS技术,可以实现输出任意频率和任意精度的正弦信号波形[4],而同在FPAG中利用锁相环技术,fclk实现高频高稳定基准时钟功能是很容易的,因而输出的正弦波的频率范围和精度要求都容易得到满足.3 基于FPGA的三相SPWM控制器设计3.1 DDS正弦波发生模块设计本设计依托的FPGA芯片是Altera公司的Cyclone III 系列的EP3C25Q240C8芯片. 根据图3 DDS正弦波结构原理图,可以得到本设计所需的基于FPAG的DDS三相正弦波发生模块设计电路图,如图4所示,系统时钟CLK为来自晶振的50MHz时钟信号.图4 DDS三相正弦波发生模块设计电路图图4中ADDER32是32位加法器,DFF32是32位寄存器,两者共同构成32位相位累加器. 正弦波ROM查找表分别由sin_rom01、sin_rom120和sin_rom240三个模块构成,它们的地址宽度和数据宽度均是10位,分别用来产生0°、120°和240°的正弦波. fangbo_rom是方波rom查找表,用来产生方波,地址宽度和数据宽度也都是10位. 由于产生的方波是作为产生载波三角波的驱动时钟信号,为了后续设置SPWM波的载波比和输出频率,在正弦波的频率字和方波频率字之间放置一个乘法器模块tra_sin_bilv. 乘法器的一个输入是正弦波频率字,另外一个输入是系数,输出的低32位作为方波的频率字. 由于三角波发生模块的地址宽度和数据宽度也都是10位,假设该系数为M,则M和载波比Kf的关系为:图4中PLL4M模块是锁相环模块,用来输出两个时钟信号,C0输出频率100MHz,用来作为死区控制模块的系统时钟. C1输出频率为10KHz,用来作为逻辑分析仪SignalTap II的时钟信号.图5是图4设计电路输出的三相正弦波以及方波在逻辑分析仪SignalTap II显示的波形,其中三相正弦波sin0、sin120和sin240分别是0°、120°和240°的正弦波,频率为50Hz. 方波TRA_CLK频率为1.024MHz.图5 DDS三相正弦波发生模块输出三相正弦信号和方波信号SignalTap II实时数据采样波形图根据式(3),图5中的正弦波频率可以通过改变正弦波输入频率字方式实现. 根据式(5),在确定载波比的情况下,通过改变乘法器输入系数M,可以改变输出方波的频率.3.2 三角波发生模块设计由于载波三角波是等腰三角形,所以可以利用地址计数器前半段的地址值作为等腰三角形的上升边,地址计数器后半段的地址值的取反值作为等腰三角形的下降边. 本设计的三角波发生器地址宽度和数据宽度也均是10位,因此三角波的计数器也是10位. 图6是三角波发生模块的设计电路图,其中counter10B模块是10位地址计数器,sanjiao模块是三角波发生模块.图6 三角波发生模块设计电路图3.3 死区控制模块设计幅度控制模块可以直接调用LPM中的宏模块乘法器,比较器模块也是可以直接调用LPM中的宏模块比较器. 这小节重点阐述死区控制模块设计.由2.1中死区控制模块的功能与原理可知,死区控制模块就是要实现对每一相SPWM波形控制的一对IGBT不能同时导通. 由于IGBT器件从导通到关断的过程中有时间延迟,因此防止同一个SPWM波形控制的一对上下桥臂IGBT同时导通的方法,是当一个IGBT从导通转变为关断时,对另外一个IGBT器件人为设置延长从关断到导通的过渡时间. 反映到SPWM波形,就是凡是上升沿的时刻都根据需要延迟其跳变时间,延迟的具体时间根据IGBT的性能指标来决定.图7 死区控制模块设计电路图图7是死区控制模块设计电路图. 其中SPWM_IN是输入的一相SPWM波,d_clk0是接DDS三相正弦波发生器模块输出的100MHz时钟信号. SIQU_CTRO是控制单个IGBT的死区控制电路. 输出out_H和out_L是经过死区控制之后的SPMW波形,分别控制一对IGBT的上下桥臂. 死区控制延迟时间可通过改变SIQU_CTRO电路里的参数来调节.4 基于FPGA的三相SPWM控制器顶层电路设计及输出波形分析4.1 基于FPGA的三相SPWM控制器顶层电路设计根据图2 三相SPWM控制器电路模块图和第3节各个子模块的设计电路图,可以得到基于FPGA的三相SPWM控制器顶层电路设计图,如图8所示.图8 基于FPGA的三相SPWM控制器顶层电路图图8中左边的clk0是系统总的输入系统时钟,频率为50MHz. DDS_ES是DDS三相正弦波发生模块,tra3是三角波发生模块. 四个AM_CTRO是乘法器,作为是幅度控制模块,M_tra[4..0]是三角波幅度控制系数,M_sin[4..0]是正弦波幅度控制系数. 由于产生的正弦波和三角波的数据位宽同样都是10位,根据式(2)可得调制度KA的具体表达式为:从式(6)可知,通过设置M_sin[4..0]和M_tra[4..0]可以灵活调节输出SPWM波形的调制度.CMP_10和CMP都是比较器模块,其输入是三角波和正弦波,输出是SPWM波. 其中CMP_10是10位比较器,CMP是14位比较器,后者是产生经过幅度控制的SPWM波形,前者是产生没有经过幅度控制的一路SPWM波形,是为了验证没有调制的SPWM波形和调制度小于1的SPWM波形的区别而设置的.4.2 输出波形分析图9是输出的三相SPWM波形SignalTap II实时数据采样波形图.图9 SPWM波形SignalTap II实时数据采样波形图图9中SPWM_A0是没有经过调制的A相SPWM波形,SPWM_A、SPWM_B和SPWM_C是调制度为90%的A、B、C三相SPWM波形. 其中产生SPWM_A和SPWM_A0两个波形的调制波是一样的,也就是用相同的0°正弦波作为调制波,不同的地方是产生SPWM_A的波形的调制度是90%,而产生SPWM_A0的波形的载波和调制波都没有经过幅度控制,调制度是100%. 在图9中可以明显看出两种波形SPWM_A0和SPWM_A的区别.图10 死区控制电路输入输出波形仿真图图8顶层电路图中SIQU_KONGZHI是死区控制模块,每个SIQU_KONGZHI模块输出上下桥臂一对IGBT器件所需的SPWM控制信号. 图10是死区控制电路输入输出波形仿真图,其中SPWM_A是A相SPWM波形,也是A相死区控制电路的输入SPWM波形,SPWM_AH和SPWM_AL分别是A相死区控制电路输出控制上桥臂和下桥臂的SPWM波形,SPWM_BH和SPWM_BL分别是B相死区控制电路输出控制上桥臂和下桥臂的SPWM波形.限于仿真图的大小,图10中没有给出C相死区控制电路输出控制上桥臂和下桥臂的SPWM波形. 从图10中可以看出SPWM_AH上升沿明显延迟于SPWM_AL的下降沿,也就是中间错开了一段死区时间. SPWM_BH上升沿也明显延迟于SPWM_AL的下降沿.图11 输出频率50Hz载波比20调制度90% 的三相SPWM波SignalTap II实时数据采样波形图图12 输出频率40Hz载波比15调制度85% 的三相SPWM波SignalTap II实时数据采样波形图图11和图12分别是输出频率50Hz载波比20调制度90% 和输出频率40Hz载波比15调制度85%的三相SPWM波SignalTap II实时数据采样波形图,均是经过死区控制输出的三相6路SPWM波形,满足了输出频率、调制度、载波比以及死区时间均可以灵活调节的设计目的.5 总结本文基于Altera公司的Cyclone III 系列的EP3C25Q240C8 FPGA芯片作为控制核心,结合直接数字频率合成技术(DDS),利用Verilog语言和LPM宏模块设计生成三相SPWM控制器. 设计仿真以及用逻辑分析仪SignalTap II采样显示的结果表明,该三相SPWM控制器具有调制波频率、载波频率、调制度、载波比以及死区时间均可以灵活调节的优点,达到了设计的目的. 该控制器可方便应用于逆变电源的变频调压以及电机变频调速等电气控制领域. ■【参考文献】[1]潘松,黄继业,潘明.EDA技术实用教程—Verilog HDL版(第5版)[M].北京:科学出版社,2013:354-356.[2]潘健,张小磊,张伯顺,王淑青.基于FPGA 的SPWM 变频调压电源研究[J].电源技术研究与设计,2015,39(2):386-388.[3]丁卫东,郭前岗,周西峰.一种基于FPGA的SPWM波的实时生成方法[J].计算机技术与发展,2011,22(2):211-214.[4]廖磊,何魏,周晓林.单片机与FPGA实训教程[M].北京:科学出版社,2016:310-317.[5]彭宏涛,基于FPGA的变频电源的设计与实现[D].昆明:云南大学.2012:7-9[6]黄继业,潘松.EDA技术及其创新实践(Verilog HDL版)[M].北京:电子工业出版社,2012:123-126.[7]黄玉健,黄永庆.基于FPAG的DDS多功能信号发生器的设计[J].梧州学院学报,2017,27(3):10-16.。

基于FPGA数控变频电源的设计摘要:本文提出了一种基于FPGA数控变频电源的设计方案,文中对母线调压电路、逆变电路等硬件电路的实现原理进行了分析研究,并着重讲述了基于FPGA的数字控制器的设计实现方法。

经过验证,该电源的输出电压在一定范围内的幅值和频率可调,并能有效地进行逆变控制,能够满足用户的需求,实用性广泛。

关键词:变频电源;FPGA;SPWM中图分类号:TM344.6 文献标识码:A随着时代的发展以及科技的进步,人们的生活和工业的发展都离不开电力系统,然而由于目前各国对电力系统的设计标准不同,电网的统一发展受到一定的制约。

此外,由于发电厂产生的电力功率有限,而随着用电高峰期和低峰期的差异,在使用过程中往往会出现电压不够或过高的情况。

加之电力环境复杂,受雷击以及其他设备的干扰,电网也会因为抗干扰能力差出现故障,影响电力的使用。

因此,为了让满足对电源的需要,应当设计出一种能够在一定的范围内对电压的幅值和频率进行调节的、工作稳定的电源。

变频电源即是将整个电路构成交流-直流-交流-滤波的变频装置,通过整流滤波、逆变以及各种控制技术等将工频电源转变成可以调控的交流电,不仅能模拟输出不同国家的电网指标,而且也为出口电器厂商在设计开发、生产、检测等应用中提供可靠的、高稳定的电压和频率输出,通过结合目前成熟的科学技术,已经在实际中得到了广泛的应用。

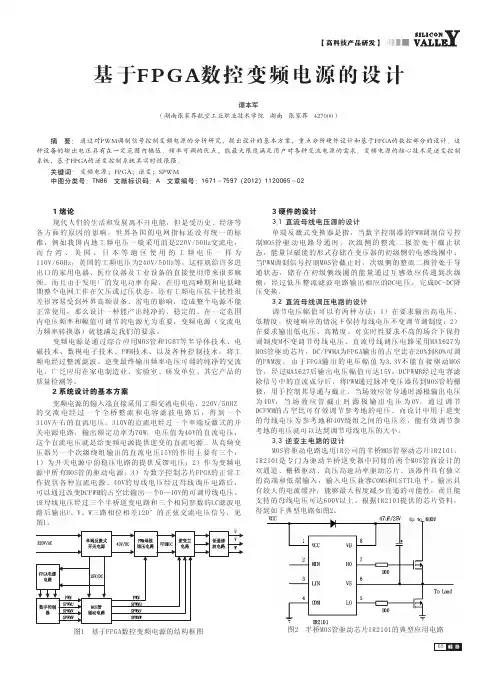

1.系统设计本课题研究的变频电源是基于FPGA芯片作为数字控制器进行设计的,其设计框图如图1。

变频电源采用工频交流电输入,经过整流和滤波,将公用的220V/50HZ的交流电转化成310V左右的直流电压,然后再经过开关电源电路输出40V的直流电压,用于变频电源的逆变,该电压经过母线调压电路、数字控制器、逆变电路等相关电路的作用,输出相位相差120°的三路正弦交流电压信号。

同时,次级绕组可以输出15V的直流电压,为变频电源中的设备提供工作电压以及电流。

图1 变频电源的设计框图2.硬件电路的设计2.1直流母线电压源的设计直流母线电压源中使用单端反激式变换器,当数字控制器中的PWM调制信号控制驱动电路的场效应管导通时,变压器次级的整流二极管截止,此时电能转变成磁能;反之,当控制器中的PWM调制信号控制驱动电路的场效应管截止时,变压器次级的整流二极管导通,此时储存的磁能通过互感传递至变压器次级,再经过低压整流滤波电路被转换成直流电压,这样就可以完成将较高的直流电压转化成较低的直流电压的过程。

第28卷第1期 武 汉 化 工 学 院 学 报 V o l .28 N o.12006年01月 J. W uhan Inst . Chem. T ech. Jan. 2006文章编号:10044736(2006)01006703基于FPGA 的三相PWM 发生器的实现方法探讨邓清秀,文小玲(武汉化工学院电气信息学院,湖北武汉430074)摘 要:介绍了在FPGA 中用V HDL 语言编程实现的三相P WM 发生器的设计方法.该发生器包括P WM 信号产生和IGBTIP M 模块故障保护两大部分,具有灵活、容易扩展、通用等优点.M A X +PLU S 中的仿真结果,验证了该设计的可行性.关键词:V HDL ;FPGA ;P WM ;三相逆变器中图分类号:T P 368 文献标识码:A收稿日期:20050117作者简介:邓清秀(1979),女,湖北武汉人,硕士研究生.研究方向:电力电子.0 引 言本设计的目的是为了应用微处理器(通常为高速的微处理器,如TM S 320V C 33)给出的信息,结合来自IGB T IPM 智能模块的故障输出信号产生三相逆变器的PWM 信号波形.工业应用中两种典型的逆变器是三相两电平和三相三电平逆变器.PWM 发生器在整个逆变器中扮演着重要角色[1],因此它的设计致关重要.本设计适用于三相两电平逆变器,经增加适当的脉宽寄存器与缓冲寄存器,就可应用于三相三电平逆变器,以及三相多电平逆变器.现在市场上主要有LA T T I C 、X I L I N X 、AL T ERA 三家公司的CPLD FPGA 芯片产品,这些产品各有所长,可挑选的范围很大.根据实际情况选用AL T ERA 公司的芯片以及该公司的M A X +PLU S 软件,用V HDL 语言编程[2],在FPGA 内实现整个PWM 发生器的功能.1 整个发生器的基本结构对PWM 信号产生的原理不作赘述,具体参看文献[3],整个设计的内部结构如图1所示.通过控制寄存器掌控FPGA内部各个模块的运行,设计中控制寄存器ctr _reg ()为16位,其中仅低6位有效,对应功能见表1.图1 FPGA 内部设计结构图F ig .1 Configurati on of the design in FPGA表1 控制寄存器有效位的功能T able1 T he functi on of effective bits in contro l registerB it0B it1B it2B it3B it4B it5计数使能位比较使能位PWM输出使能位A相PWM输出使能位B相PWM输出使能位C相PWM输出使能位1为允许,0为禁止1为允许,0为禁止1为允许,0为禁止1为允许,0为禁止1为允许,0为禁止1为允许,0为禁止 通过微处理器对控制寄存器进行赋值,可灵活控制FPGA内部各大模块的正确运行,且便于调试,使PWM输出信号更灵活可靠、可控性增强.另外在FPGA里面完成利用IGB T IPM模块的故障输出信号封锁IGB T IPM的控制信号通道的功能,弥补IPM自身保护的不足,更有效地保护器件.用V HDL编程,将整个程序分成接口模块、缓冲与比较模块、死区发生模块和保护模块四个部分.1.1 FPGA与微处理器的接口模块主要完成微处理器对FPGA的读写功能.其中写功能主要完成对死区寄存器、周期寄存器、控制寄存器、ABC三相的脉宽寄存器的赋值;读功能主要完成微处理器对FPGA内部保护寄存器值的读取.实际应用中通常选用高速微处理器来完成前端复杂的控制运算,微处理器将FPGA作为一个普通外设来进行数据交换,调试时要熟悉高速微处理器对速度不匹配的外设读写时序.这一部分作为一个独立的功能模块,需要注意的是:在程序上电第一次运行时需要先写各相的脉宽寄存器,再写死区寄存器及周期寄存器,最后写控制寄存器,这样可以同时自动将脉宽寄存器的值装入缓冲寄存器,否则缓冲寄存器的初始值为零,导致在第一个开关周期内无PWM波形输出.1.2 缓冲与比较模块这一部分是基本的PWM波形产生的核心部分.基本的过程可以参看文献[3],但是比较的过程有所不同,可以参看图2,选择在计数器的计数值为最小时三相缓冲寄存器对三相脉宽寄存器的值进行加载,当计数器的计数值非最小时,微处理器可以更新脉宽寄存器的值而不影响最终的三相同步关系.在上电第一个周期内让寄存器的值自动进入缓冲器,然后在正确的时间启动计数器.并不是一上电程序就立即启动计数器,控制寄存器中的B it0位用来控制计数器.只有当控制寄存器的值已经加载了,并且在B it0位允许的情况下才启动计数器.1.3 死区模块死区模块是最独立的一个模块.为了避免同一相上下桥臂直通现象,必须在上下桥臂的触发信号中加入延时.这段延时时间里上下桥臂都无驱动信号,也就是所谓的死区.死区时间的选择必须符合一定条件.另外若原始信号比较宽,死区时间比较短,则死区对PWM影响不大,但是若原始信号变窄死区时间过长,则会使上下管在整个PWM输出周期中没有输出,为此应保证原始脉宽不小于三倍的死区时间.这里选用的死区寄存器为8位,所以死区时间为0~256倍的FPGA 的基本时钟周期.可以通过程序在微处理器里面进行灵活调整.图2 三相基本脉冲产生原理图F ig.2 T he p roduce p rinci p le of th ree phase basedpulse1.4 保护模块来自IGB T IPM模块的6路故障输出信号经过光耦后(1为正常,0为有故障)直接进入FPGA与“1111111111”进行并位处理构成16位存入保护寄存器内.设计要求是在6路的IGB T IPM故障输出信号中,只要其中有一路为0,立即封锁所有的IGB T IPM触发信号,同时由flag 信号线向微处理器发一个信号,微处理器确认后,利用软件关断IGB T IPM的控制信号,并对保护存器内的值进行读取,然后判断是哪一路管子故障,做出相应的处理,以待故障消除后,装置重新投入运行.考虑可以输出单相或是两相电压,结合控制寄存器与保护寄存器的值,单独给出了三相PWM输出使能信号.在6路故障输出信号都正常的情况下,通过修改控制寄存器的值,可随意选择输出的单相、两相或是三相波形.这部分的实现比较简单,但它监控着所有的IGB T管的正常运行,下面给出了它作为一个子进程的完整程序. IGB T IPM保护逻辑:86武汉化工学院学报第28卷 ctr _reg ()为控制寄存器;errigb t _reg ()为保护寄存器;nR ST 为FPGA 的复位信号p rocess (ctr _reg (2),errigb t _reg ,nR ST )variab le tem p :std _logic ;tem p 为中间变量begintem p :=errigb t _reg (0)and errigb t _reg (1)and errigb t _reg (2)and errigb t _reg (3)anderrigb t _reg (4)and errigb t _reg (5);0代表错,1代表正确if (nR ST =’0’o r tem p =’0’o r ctr _reg (2)=’0’)then enpwm <=’0’;elsif (ctr _reg (2)=’1’and tem p =’1’and nTR IP =’1’)thennTR IP 为微处理器给出的紧急PWM控制信号,为1是允许PWM 输出,相反则禁止 enpwm <=’1’;else enpwm <=’0’;end if ;enpwm a <=ctr _reg (3)and enpwm ;主要是考虑可以输出单相或者两相电压enpwm b <=ctr _reg (4)and enpwm ;enpwm c <=ctr _reg (5)and enpwm ;flag <=no t (tem p );过流标志,直接与D SP 相连0正常;1过流end p rocess ;2 仿真与结果图3为最后完整程序的仿真图形.为了便于分析,对整个程序中的重要寄存器、重要变量都加了探针进行引出,使中间变量的值能被直接观察到.例如三相脉冲寄存器由探针引出来的输出变量为a ,b ,c ;三相死区前的基本PWM 波形为wm _reg 0,wm _reg 1,wm _reg 2;计数器的值也用变量n 引出;死区寄存器用变量d 引出.通过对比观察可以发现,由数据线输入的三相脉宽值可以正确地被变成PWM 波形输出,而且死区时间也正确地被加入到同一桥臂的上下管的触发波形中,同时可以发现三相脉宽寄存器的值的改变,在下一个PWM 输出波形里立即被显示出来.整个程序可以完全满足预先设定的要求.图3 仿真结果F ig .3 Em ulate result3 结 语此设计用于三相两电平逆变器的PWM 发生器,在10.23版本的M A X +PLU S 软件中经过自动适配,A CEX 1K 系列芯片EP 1K 10TC 144被选中.在实际应用中考虑两个因素:(1)后续要将三相两电平逆变器扩展成三相多电平逆变器.(2)微处理器的资源调节.当微处理器负担过重时,可将三相脉宽值的计算拿到FPGA 里面来实现.基于这两个因素,设计中可选择更大容量同系列的FPGA 芯片,如EP 1K 30TC 144和EP 1K 50TC 144.由于同一种封装中的各种A CEX 1K 器件的引脚相兼容,可在不改变硬件电路设计的情况下,更换同种封装的更大容量的芯片.用V HDL 语言来完成PWM 发生器的设计具有高灵活性、高集成度、高可靠性且成本低的优点.96第1期邓清秀等:基于FPGA 的三相两电平P WM 发生器的实现方法探讨参考文献:[1] 陈 坚.电力电子学电力电子变换和控制技术[M].北京:高等教育出版社,2002.[2] 侯伯亨,顾 新.V HDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,1998.[3] 许 强,贾正春.基于FPGA的三相P WM发生器[J].电子技术应用,2001(1):7374.D iscussion of rea l iza tion m ethod of two levels three pha seP WM genera tor ba sed on FPGAD EN G Q ing x iu,W EN X iao ling(Schoo l of E lectrical and Info r m ati on Engineering,W uhan Institute of Chem ical T echno logy,W uhan430074,Ch ina)Abstract:T h is p ap er in troduces the FPGA realizati on m ethod of a th ree phase PWM generato r u sing V HDL language.T he PWM generato r,w h ich m ain ly con sists of PWM signal generating b lock and IGB T IPM’s Fau lt p ro tecti on b lock,is characterized by flex ib le,general and easy to ex tend.T he co rrecti on and feasib ility is verified by the resu lts of si m u lati on based on M A X+PLU S environm en t.Key words:V HDL;FPGA;PWM;th ree phase inverter本文编辑:陈晓苹☆(上接第66页)The design and rea l iza tion of the W eb appl ica tion system ba sed on U MLXU Guo qing1,W EN J un hao2(1.Schoo l of Computer Science and Engineering,W uhan Institute of Chem ical T echno logy,W uhan430074,Ch ina;2.Faculty of Softw are Engineering,Chongqing U niversity,Chongqing400044,Ch ina)Abstract:U n ified M odeling L anguage(UM L)is a un iversal ob ject o rien t m odeling language.T he p rogramm er can estab lish bu siness m odel qu ick ly and design the system classes and the database accu rately by u sing R ati onal Ro se.T h is article discu sses the developm en t of the hom ew o rk release system on the in ternet based on UM L.T he system is legib le in structu re and easy in in teracti on.Key words:UM L;W eb;app licati on system本文编辑:陈晓苹07武汉化工学院学报第28卷。

基于FPGA的网络三相电能表设计摘要:文章介绍了基于FPGA的网络三相电能表的系统总体设计方法。

通过FPGA设计SOPC系统与AD73360信号采集板连接,由FPGA控制AD73360进行数据采集,然后再对采集的数据进行处理。

重点分析了采用FPGA和SOPC技术的网络三相电能表的软硬件设计方法。

该网络三相电能表具备电力参数监测、电能质量分析(谐波分析)、网络远程报文发送等功能。

关键词:FPGA;三相电能表;Sopc NiosII采用FPGA和SOPC技术设计的网络三相电能表,可以为电力测控系统的多路信号采集和处理提供足够的速度,且信号处理算法完全由FPGA硬件实现。

按照电力系统IEC 61850标准通信规约设计和传输以三相电能数据的以太网报文。

基于FPGA的网络三相电能表采用Altera公司的Cyclone II EP2C70F896和ADI公司的AD73360芯片作为该系统的主要核心部分。

在该设计中,模拟前端使用AD73360信号采集板对电压和电流进行采样,数据送给后端FPGA进行处理,然后通过DM9000A以太网模块发送。

NiosII软核CPU对电表进行总体控制。

由于FPGA采用纯硬件的工作方式,信号处理速度快,实时性强。

AD73360是一款面向工业电能计量或多通道模拟输入等通用应用的6通道模拟输入前端(AFE)处理器。

配有6个16位A/D转换通道,在声带信号带宽下,各通道均可实现77 dB的信噪比。

同时集成一个可编程输入增益放大器(PGA),增益设置分为8级:从0 ~38 dB。

AD73360特别适用于工业电能计量,因为各通道同时进行采样,可将转换间的时间(相位)延迟降至极低水平。

AD73360全部通道均支持低群延迟转换。

片内集成基准电压,支持单电源工作。

这个基准电压也可以通过编程以支持3 V或5 V操作模式。

同时,用户也可以通过编程将采样率设置为64 K、32 K、16 K和8 kHz四种采样率(主时钟频率为16.384 MHz)。

基于fpga的三相pwm整流器移相触发电路的设计与实现基于FPGA的三相PWM整流器移相触发电路的设计与实现是一个涉及电力电子和FPGA编程的复杂过程。

以下是一个简化的步骤概述:1. **系统概述**:首先,你需要对三相PWM整流器在三相静止坐标系下的数学模型进行原理介绍。

了解整流器的基本结构和其工作原理是设计触发电路的基础。

2. **确定变量**:在三相静止坐标系下,你需要确定整流器移相触发电路中的各个变量。

这些变量可能包括寄生电阻、侧电感、电感、网侧寄生电阻、滤波电容和阻尼电阻等。

此外,还需要考虑六个开关电路(S1~S6)的状态。

3. **建立计算模型**:基于上述变量和六个开关电路(S1~S6)的不同开关状态,你可以建立相应的计算公式。

这些公式将用于确定PWM信号的占空比和相位,以实现整流器的移相触发。

4. **FPGA编程**:使用FPGA编程语言(如VHDL或Verilog)实现上述计算模型。

你需要编写代码来生成PWM信号,并根据整流器的实时状态调整PWM信号的占空比和相位。

5. **电路设计与实现**:设计并实现基于FPGA的移相触发电路。

这包括选择合适的FPGA芯片、设计必要的硬件接口电路(如ADC电路用于采集实时状态信息)、以及将FPGA编程代码烧录到FPGA芯片中。

6. **测试与验证**:最后,对设计的移相触发电路进行测试和验证。

你可以通过在实际三相PWM整流器上应用该电路,观察其性能表现,如整流效果、效率、稳定性等,并根据测试结果进行必要的调整和优化。

需要注意的是,这个过程涉及到电力电子、FPGA编程和电路设计等多个领域的知识,需要具备一定的专业背景和实践经验。

同时,由于涉及的变量和计算模型可能相对复杂,因此在实际设计过程中可能需要进行一些简化和近似处理。

基于FPGA的三相变频电源系统设计周欣;李乐;刘瑞安;王为【摘要】基于现场可编程门阵列(Field Programmable Gate Array,FPGA)设计了一种单相输入三相输出的数字式控制变频电源.将单相市电输入该系统后,经过整流、升压、滤波、三相桥式逆变和低通滤波输出三相近似正弦交流电.根据三相异步电动机的调速特性,系统由控制器改变内部调制波的幅值和频率,进而调节三相正弦脉冲宽度调制(Sinusoidal Pulse Width Modulaton,SPWM)波的脉宽和频率,最终实现三相交流异步电动机的变压变频调速(Variable Voltage Variable Fregueney,VVVF)控制.系统调制结果证明该电源的设计是可行的,且系统操作方便快捷、界面友好,可为实现全数字智能控制提供参考.【期刊名称】《天津师范大学学报(自然科学版)》【年(卷),期】2012(032)001【总页数】6页(P43-47,69)【关键词】变频电源;FPGA;SPWM【作者】周欣;李乐;刘瑞安;王为【作者单位】天津师范大学物理与电子信息学院,天津300387;天津职业技术师范大学工程实训中心,天津300222;天津师范大学物理与电子信息学院,天津300387;天津师范大学物理与电子信息学院,天津300387【正文语种】中文【中图分类】TM930.2三相变频逆变电源可以实现单相交流电到三相交流电的转换[1],从而为没有三相交流电供给的设备提供电源,其变频功能还可以改变三相交流电的输出频率,很方便地用于一些中小功率三相电机的变频调速等,因此,三相变频逆变电源的应用非常广泛[2-3].但由于传统微处理器(如51系列单片机)存在指令功能不强、处理速度慢、乘除法指令周期过长和外围电路数据转换速度慢等缺点,导致现有变频电源的性能得不到充分发挥,难以实现现代工业对逆变电源高精度、实时性的要求.本研究提出一种以FPGA为主处理器,采用SPWM实现三相变频电源的方法,以满足变频电源的输出具有高频率、高精度、小畸变、高实时性以及较宽的调频范围等特点.三相变频电源由逆变部分、信号驱动部分和SPWM产生部分组成.该电源以现场可编程门阵列EP2C5T144为控制核心,利用直接数字频率合成(Direct Digital Synthesizer,DDS)技术产生SP-WM脉宽调制信号控制逆变电路,实现对输出信号的调频调幅.输出电源的频率可以由键盘和外接电位器设定,并通过液晶显示当前频率等信息.三相变频电源的系统框图如图1所示,电路的工作原理为:单相交流电经过电磁干扰(Electromagnetic Interference,EMI)共模滤波、整流和滤波之后变为平滑的直流电,再经过逆变环节和电感滤波变成正弦波,供异步电机使用.电路主要由以下几部分组成:EMI滤波器、整流电路、逆变电路、控制器、参数设定模块、显示模块、脉冲封锁电路、驱动电路、报警装置和辅助电源.1.1.1 直流回路EMI电源滤波器可以衰减共模干扰和差模干扰,起到2个低通滤波器的作用[4].EMI电源滤波器能在阻带范围内衰减射频能量,且工频无衰减或少量衰减.系统采用的05DBAG5型EMI电源滤波器(参数为115/250 V,5 A,50/60 Hz)是由电感和电容构成的无源双向多端口网络滤波设备,其电路图如图2所示.整流环节采用KBPC50 A10M型整流堆,其等效电路如图3所示.整流电路由整流二极管D6,D8,D9和D10组成,当正弦波波峰到达D6的阳极,电流通过D6、负载和D10之后,回到电源构成回路;当正弦波波峰到达D8的阳极,电流通过D8、负载和D9后回到电源构成回路,完成一个周期的整流.该整流堆为单相桥式整流,整流后的直流电压平均值只有交流电压有效值的0.9倍,关系式为:Ud=0.9UL Ud为直流电压,UL为交流电压的有效值.单相交流电输入整流后经逆变电路输出得到的三相交流线电压的有效值只有146 V,不能用来驱动三相220 V的电动机.为了驱动三相220 V电动机,在单相全波整流以后,还必须增加一个由电容C4和C6构成的升压电路.当图3中N点的电位处于正弦波的正半周时,直流回路正极的正电位将因C4的作用得到充电;而当N点的电位处于正弦波的负半周时,直流回路负极的负电位也因C6的作用得到补充,从而增大了正极和负极的直流电压值.通过适当选择C4和C6的电容量,可使直流回路的平均电压升至297 V,使逆变后的三相线电压升为220 V.电路经整流和升压后变为脉冲波,再经电容C5和C7滤波后变成平滑的直流,供逆变器使用.1.1.2 逆变电路逆变电路又称为逆变桥,由Q3、Q4、Q5、Q7 Q8和Q9组成,如图4所示.其功能是把直流电转换成频率可调的三相交流电,逆变电路实际输出线电压的波形是经过SPWM调制后的高频脉冲系列与调制的正弦波一致.在功率变换电路中,功率管的选择至关重要[5],系统采用的功率管为MOSFET.MOSFET是一种电压控制型单极晶体管,它通过栅极电压来控制漏极电流,因而具有驱动电路简单的显著特点,同时,MOSFET的驱动功率小,仅由多数载流子导电,无少子存储效应,且高频特性好,工作频率高达100 k Hz以上.工作过程中,由于变压器漏感和MOSFET具有较大开通电容的影响,MOSFET在关断时会承受一个很高的电压尖峰.为了减小这个尖峰,系统采用了RCD缓冲电路,电路图如图5所示.由于箝位关系将开关管两端的电压限制在2 V,电容会使开关管集电极或漏级电压上升速度减缓,随后电容通过电阻放电或将能量转移到电感或变压器中,最终回馈电网.电容的取值需要足够大,以使开关管电压上升速度缓慢,保证开关管不受冲击,但由于损耗原因,电容也不能太大.电阻的大小没有特别要求,电阻越小,电容的放电速度越快.1.1.3 控制器的选择FPGA具有体系结构和逻辑单元灵活、集成度高以及适用范围宽等特点,它兼容了可编程逻辑器件(Programmable Logic Device,PLD)和通用门阵列的优点,可实现较大规模的电路,编程也很灵活.与门阵列等其他专用集成电路(Application Specific Integrated Circuit,ASIC)相比,FPGA又具有设计开发周期短、制造成本低、开发工具先进、标准产品无需测试、质量稳定和可实时在线检验等优点.因此,系统采用型号为EP2C5T144的FPGA作为整个电路的控制器,通过编程实现SP-WM波形的产生,并对负载的电流和电压信号以及来自键盘和传感器的信号进行处理.1.1.4 驱动电路系统由比较器LM311组成驱动放大电路,如图6所示.驱动放大电路中,由FPGA 产生的SPWM信号首先经过RC滤波,然后进入由LM311组成的驱动电路,再经过隔离输入后级电路,这样就将FPGA输出的弱信号转化为具有一定驱动能力的SPWM信号.为了增强电路的抗干扰能力本研究在驱动放大电路中增加了一级光耦隔离电路,隔离电路由光耦TLP521和周围元件组成.信号驱动模块采用MOSFET专用的驱动电路芯片IR2110,不但可以解决驱动电源多路的麻烦,而且输出波形也较为陡峭,信号驱动原理图如图7所示.1.1.5 信号检测电路信号检测电路包括电流采样电路和电压采样电路,电路图如图8所示.电压取样信号通过滤波和电压跟随电路使采样的信号传至单片机的A/D口,做A/D的运算处理.电流采样信号通过的滤波和电压跟随电路,经2级放大后(第1级为1.5倍,第2级为18倍),输入单片机A/D口进行电流检测处理.SPWM波产生示意图如图9所示.系统的核心控制芯片是Altera公司的EP2C5T144,此芯片是该公司2000年推出的2.5 V低价格SRAM工艺PLD(FPGA)芯片,其内部具有4 992个逻辑单元,12个嵌入式RAM块,每个RAM块大小为4 Kbit,并且带有独立的嵌入式存储块(EAB),部分型号带锁相环(Phase Locked Loop,PLL),芯片使用这些存储单元,利用DDS技术形成SPWM脉宽调制信号来控制逆变电路,以形成三相正弦交流电源.波形的频率可通过键盘输入,并可以显示电压、电流和频率等输出信号.系统测试的具体步骤如下:(1)使用双踪示波器分别观测FPGA输出的SPWM波形是否正确,三相波形相位差是否为(2)把SPWM信号加到信号处理电路输入端观测输入信号波形经过处理电路后有无失真.(3)主电路经逆变和滤波后接3个阻性负载并星形连接,以测试相电压是否对称以及相位差是否正常.(4)小功率测试,直流测试中给系统加10 V电压工作5 min,检测各个MOS管有无异常,用示波器测试每一相上、下D和S极尖峰的大小;再给系统输入70 V电压进行测试,工作10 min,测试方式同上.(5)满负荷测试,给系统输入220 V电压进行系统调试,方式同步骤(4),以测试系统的过载和欠压保护功能.(1)FPGA输出波形正确,三相波形相位差为(2)SPWM信号输入到信号处理电路后,经过波形处理,电路无失真.(3)主电路经逆变、滤波后接3个阻性负载并星形连接,相电压对称,相位差正常.(4)小功率测试中,系统各个MOS管无异常.(5)满负荷测试中,系统工作正常,过载和欠压保护功能工作正常.三相变频电源系统不但实现了三相交流异步电动机的VVVF控制,还具有欠压、过流、短路、能耗制动和软启动等功能,在故障发生时通过软件和硬件2种方法封锁脉冲,实现保护.经实际运行检测,系统稳定可靠,且操作方便快捷、界面友好具有良好的可扩展能力,在电力和电子领域具有广泛的应用前景.【相关文献】[1]李彦吉,李斌.电气化铁路单-三相变频电源的研制[J].电工技术,2009,17(10):45-46.[2]梅建伟,刘美怡,徐祖建,等.数字化三相变频电源的研制[J].电源技术应用,2008,11(12):9-13.[3]吴保芳,钟炎平,林洁,等.新型组合式三相变频电源的研制[J].空军雷达学院学报,2001,15(3):46-49.[4]王海莉,吴延华.EMI电源滤波器的设计探讨[J].电子产品可靠性与环境试验,2008,26(6):16-19.[5]付明,张东来,王宏.多路太阳能功率变换模块控制策略研究[J].现代电子技术,2009,20(4):206-209.。