微机原理课件 8088管脚功能

- 格式:pdf

- 大小:111.00 KB

- 文档页数:1

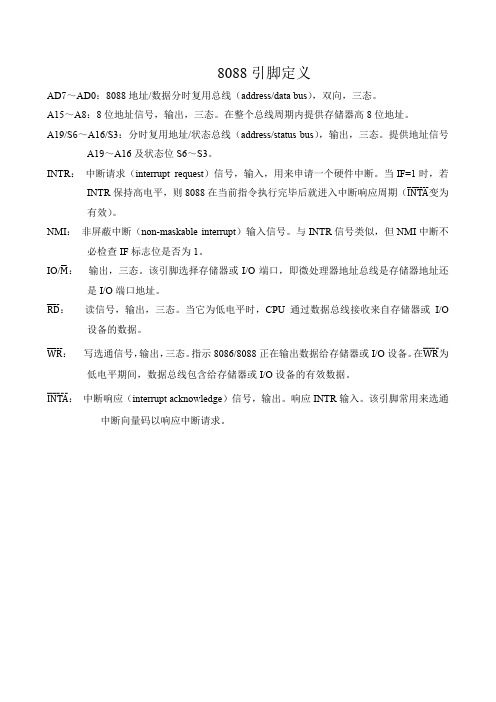

8088引脚定义

AD 7~AD0:8088地址/数据分时复用总线(address/data bus ),双向,三态。

A15~A8:8位地址信号,输出,三态。

在整个总线周期内提供存储器高8位地址。

A19/S 6~A16/S3:分时复用地址/状态总线(address/status bus ),输出,三态。

提供地址信号

A19~A16及状态位S6~S3。

INTR : 中断请求(interrupt request )信号,输入,用来申请一个硬件中断。

当IF=1时,若

INTR 保持高电平,则8088在当前指令执行完毕后就进入中断响应周期(INTA

̅̅̅̅̅̅̅变为有效)。

NMI : 非屏蔽中断(non-maskable interrupt )输入信号。

与INTR 信号类似,但NMI 中断不

必检查IF 标志位是否为1。

IO/M

̅: 输出,三态。

该引脚选择存储器或I/O 端口,即微处理器地址总线是存储器地址还是I/O 端口地址。

RD

̅̅̅̅: 读信号,输出,三态。

当它为低电平时,CPU 通过数据总线接收来自存储器或I/O 设备的数据。

WR ̅̅̅̅̅: 写选通信号,输出,三态。

指示8086/8088正在输出数据给存储器或I/O 设备。

在WR

̅̅̅̅为低电平期间,数据总线包含给存储器或I/O 设备的有效数据。

INTA

̅̅̅̅̅: 中断响应(interrupt acknowledge )信号,输出。

响应INTR 输入。

该引脚常用来选通中断向量码以响应中断请求。

80868088引脚图+内部组成框图8086(16位)/8088(准16位)引脚图及内部组成框图◆8086/8088外部结构:——表现为数量有限的输入/输出引脚(构成了处理器级总线)。

——均为40引脚。

◆8086/8088内部组成:EU执行单元和BIU总线接口单元两个独立单元组成。

EU execution unit →不直接与外部打交道。

BIU bus interface unit→负责与外部存储器和I/O端口交换数据。

EU的任务:负责执行所有指令、给BIU单元提供地址信息和数据信息、管理通用寄存器、标志寄存器。

BIU的任务:负责执行所有的外部总线周期。

取指令:从存储器指定地址取出指令送入指令队列排队等待EU控制器按顺序执行。

执行指令:根据EU命令对指定存储单元或I/O端口存取数据。

8086与8088主要区别:内部指令队列缓冲器大小不同和外部数据总线位数不同[内部]内部ALU数据总线根数相同。

→都具有16位数据总线。

可处理8位的或16位的数据。

内部Q总线根数相同。

→都具有8位的指令队列总线Q总线。

内部指令队列缓冲器大小不同。

8086→可容纳6个字节,且在每一个总线周期从存储器可以取出2个字节的指令代码填入指令队列。

8088→只能容纳4个字节,且在每一个总线周期从存储器只能取出1个字节的指令代码填入指令队列。

[外部]外部地址总线根数相同。

→都有20根地址总线。

直接寻址1M字节存储器:202=1M直接寻址64K个I/O端口(寄存器):162=64K外部数据总线位数不同。

8086外部→16根数据总线。

8088外部→8根数据总线。