双通道同步高速数据采集器的设计

- 格式:docx

- 大小:11.02 KB

- 文档页数:2

多通道高速并行预处理数据采集模板设计一、引言在当今大数据时代,数据采集和处理已经成为了各个领域的重要任务。

多通道高速并行预处理数据采集模板设计是一种能够提高数据采集效率和精度的技术,本文将详细介绍该技术的设计与实现。

二、多通道高速并行预处理数据采集模板设计原理1. 多通道采集原理多通道采集即使用多个传感器或设备同时采集不同类型的数据,并将其整合到一个系统中进行处理。

这种方式可以提高数据采集效率和减少误差。

2. 高速并行原理高速并行即使用多个处理器同时进行数据处理,以提高数据处理速度和效率。

这种方式可以充分利用计算机的多核心优势,加快计算速度。

3. 预处理原理预处理即在进行实际计算之前,对原始数据进行一定程度的清洗、过滤、归一化等操作,以提高后续计算过程的准确性和稳定性。

三、多通道高速并行预处理数据采集模板设计流程1. 硬件设计硬件方面需要选择适合需求的传感器或设备,并通过接口将其连接到计算机上。

同时需要选择合适的处理器和内存等硬件设备,以保证系统能够高效地运行。

2. 软件设计软件方面需要编写数据采集程序、并行处理程序和预处理程序。

其中,数据采集程序需要实现多通道数据采集的功能,而并行处理程序需要将各个通道的数据进行整合,并进行并行计算。

预处理程序则需要对原始数据进行清洗、过滤、归一化等操作。

3. 数据存储为了保证采集到的数据能够被后续的分析和应用所使用,需要将其存储到数据库或文件中。

这样可以方便地进行后续的查询和分析。

四、多通道高速并行预处理数据采集模板设计实现1. 硬件实现硬件实现需要根据具体需求选择适合的传感器或设备,并将其连接到计算机上。

同时需要选择合适的处理器和内存等硬件设备,以保证系统能够高效地运行。

2. 软件实现软件实现需要编写数据采集程序、并行处理程序和预处理程序。

其中,数据采集程序可以使用各种编程语言来实现,如C++、Python等;并行处理程序可以使用OpenMP、MPI等技术来实现;而预处理程序则可以根据具体需求选择不同的算法来实现。

科 技 前 沿1科技资讯 S CI EN CE & T EC HNO LO GY I NF OR MA TI ON 由于系统采集信号的时间较短,数据量较大,故设计的采集系统属于高速采集范畴。

随着科学技术的飞速发展,对各个领域的科研探索不断深入,被采信号对采样速率的要求越来越高。

近年来,伴随电子业的飞速发展,高速集成器件IC 带来的问题也得到很好的解决。

随着计算机技术广泛应用到工程实践中,整个社会的数字电子化程度越来越高,数据采集技术的应用场合越来越广泛,通用的高速数据采集系统可用于雷达、引信、生物电波、视频、电子学频谱、示波器、声波分析等瞬态信号的实时采集和研究观察等场合[1]。

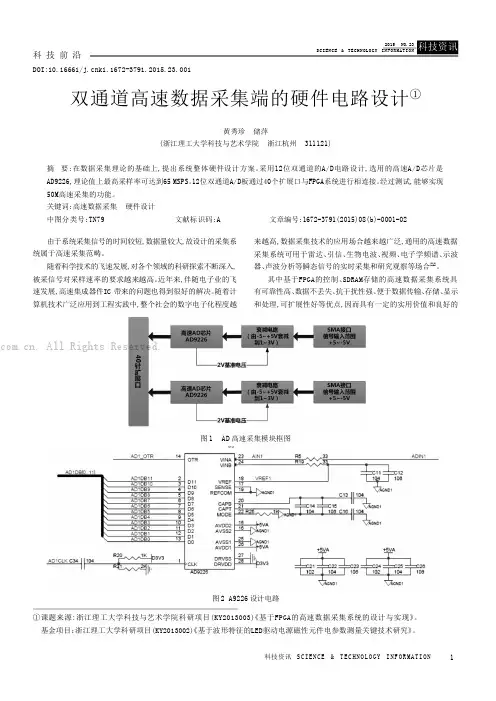

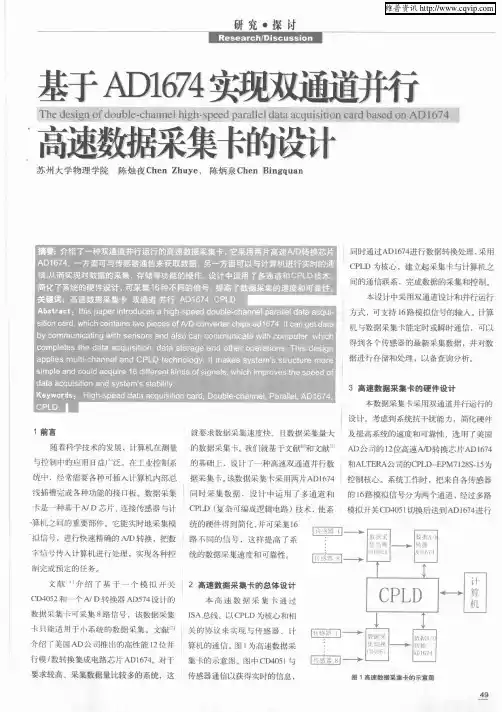

其中基于FPGA的控制、SDRAM存储的高速数据采集系统具有可靠性高、数据不丢失、抗干扰性强、便于数据传输、存储、显示和处理,可扩展性好等优点,因而具有一定的实用价值和良好的DOI:10.16661/ki.1672-3791.2015.23.001双通道高速数据采集端的硬件电路设计①黄秀珍 储萍(浙江理工大学科技与艺术学院 浙江杭州 311121)摘 要:在数据采集理论的基础上,提出系统整体硬件设计方案。

采用12位双通道的A/D电路设计,选用的高速A/D芯片是AD9226,理论值上最高采样率可达到65MSPS。

12位双通道A/D板通过40个扩展口与FPGA系统进行相连接。

经过测试,能够实现50M高速采集的功能。

关键词:高速数据采集 硬件设计中图分类号:TN79文献标识码:A文章编号:1672-3791(2015)08(b)-0001-02①课题来源:浙江理工大学科技与艺术学院科研项目(KY2013003)《基于FPGA的高速数据采集系统的设计与实现》。

基金项目:浙江理工大学科研项目(KY2013002)《基于波形特征的LED驱动电源磁性元件电参数测量关键技术研究》。

图1 AD 高速采集模块框图图2 A9226设计电路. All Rights Reserved.科 技 前 沿2科技资讯 SC I EN C E & TE C HN O LO G Y I NF O R MA T IO N应用前景。

高速数据采集系统得设计摘要:本文介绍了一种双路高速数据采集系统设计的方案,该系统通过FPGA实现了对高速A/D转换芯片的控制,并结合了应用非常广泛的单片机讨论了这一控制电路的设计思想,以及它们之间的数据处理方法。

关键词:高速A/D转换(TLC5510);单片机;FIFO;FPGA ;MAX5190 引言该数据采集系统是通过采样电路将输入的模拟信号进行模/数转换,然后将转换的结果交由FPGA或者送到单片机进行处理,并显示。

传统的方法多数由CPU 或者单片机直接控制实现。

其编程简单、控制灵活,但缺点三控制周期太长、速度较慢,不适合高速的采集。

特别是对高速转换的A/D来说,由于其转换速度很快,而单片机的速度成了整个系统的瓶颈,它限制A/D的转换速度。

就拿本介绍的高速A/D器件TLC5510来说,由于其转换速度最高可达20M,即采样周期大0.05us,远小于一条单片机的指令周期。

因此单片机对此类高速A/D器件完全无从控制。

这样在一定程度上限制了单片机在高速数据传输领域内的应用。

但是我们提出了FPGA+单片机的控制方案很好地解决了这一问题。

该系统发挥了两者的长处,单片机提供了友好的人机界面,而FPGA实现了对高速的控制,两者通过并行总线的方式连接。

整个系统模块化程度高,接口明确,易于扩展,可靠性高。

一、系统设计与方案论证该系统要求对模拟输入信号进行采集存储并且还要用示波器观察,同时还要对信号进行处理(求基波频率、有效值、二次谐波和三次谐波值),并且在发挥部分还要用LCD显示输入信号波形。

由于输入的是模拟信号,而存储的是数字信息,所以要对模拟输入进行调理、量化并将其数字信号存入数据存储器(RAM);而后在显示时再从存储器中读出数据并恢复为模拟信号,作为示波器的模拟输入,所以在该系统应具有AD、DA、RAM、等主要器件,以便对输入信号进行量化、存储和恢复。

在该系统中,控制器一方面控制AD进行数据采样同时还要将采集的数据存入RAM中;另一方面将RAM中的数据读出送给DA 并控制DA进行转换以便示波器显示;再一方面就是对采得的数据进行数字处理并控制LCD显示输入信号的信息特征。

多通道数据采集系统的设计与实现近年来,随着科技的不断发展和数据的迅速增长,对于多通道数据采集系统的需求越来越迫切。

多通道数据采集系统旨在通过多个输入通道同时采集、传输和处理多组数据,以满足大规模数据采集和处理的需求。

本文将详细介绍多通道数据采集系统的设计与实现。

1. 系统需求分析在设计多通道数据采集系统之前,首先要明确系统的需求。

根据具体的应用场景和目标,我们需要确定以下几个方面的需求:1.1 数据采集范围:确定需要采集的数据范围,包括数据类型、数据量和采集频率等。

这将直接影响系统的硬件选择和设计参数。

1.2 数据传输和存储要求:确定数据传输和存储的方式和要求。

例如,是否需要实时传输数据,是否需要数据缓存和压缩等。

1.3 系统的实时性要求:确定系统对数据采集和处理的实时性要求。

根据实际应用场景,可以确定系统对数据延迟和响应时间的要求。

1.4 系统的可扩展性:考虑系统的可扩展性,以满足未来可能的扩展需求。

这包括硬件和软件的可扩展性。

2. 系统设计在需求分析的基础上,我们进行多通道数据采集系统的设计。

系统设计主要包括硬件设计和软件设计两个方面。

2.1 硬件设计根据需求分析中确定的数据采集范围和要求,我们选择合适的硬件设备进行数据采集。

常用的硬件设备包括传感器、模拟信号采集卡和数字信号处理器等。

2.2 传感器选择根据需要采集的数据类型,选择合适的传感器进行数据采集。

不同的传感器适用于不同的数据类型,如温度传感器、压力传感器、光传感器等。

2.3 采集卡设计针对多通道数据采集系统的特点,我们需要选择合适的模拟信号采集卡进行数据采集。

采集卡应具备多个输入通道,并能够同时采集多个通道的数据。

2.4 数字信号处理器设计针对采集到的模拟信号数据,我们需要进行数字信号处理。

选择合适的数字信号处理器进行数据处理,如滤波、采样和转换等。

2.5 软件设计针对系统的需求和硬件的设计,我们需要进行软件设计,以实现数据采集、传输和处理。

2656计算机测量与控制.2010.18(11) Computer Measurement &Control数采与处理收稿日期:2010 04 23; 修回日期:2010 06 03。

作者简介:罗旗舞(1985 ),男,湖南邵阳人,硕士,主要从事基于FP GA 的信号处理及嵌入式系统应用方向的研究。

黎福海(1964 ),男,广西藤县人,教授,硕导,主要从事电路与系统、信号处理、嵌入式系统(含FPGA 、DSP)及其应用方向的研究。

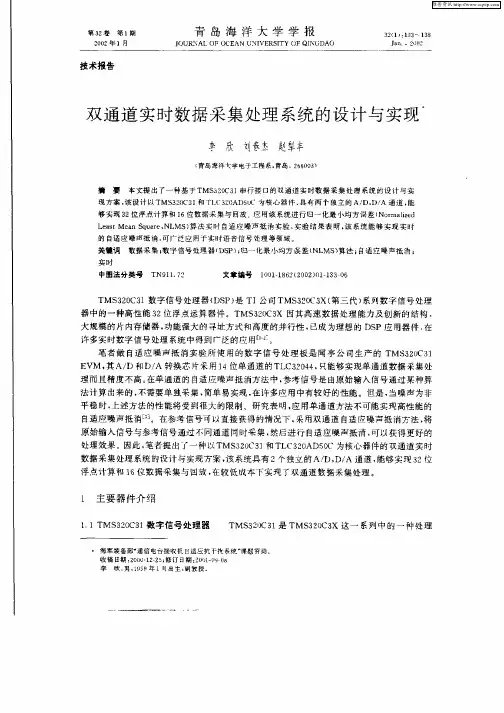

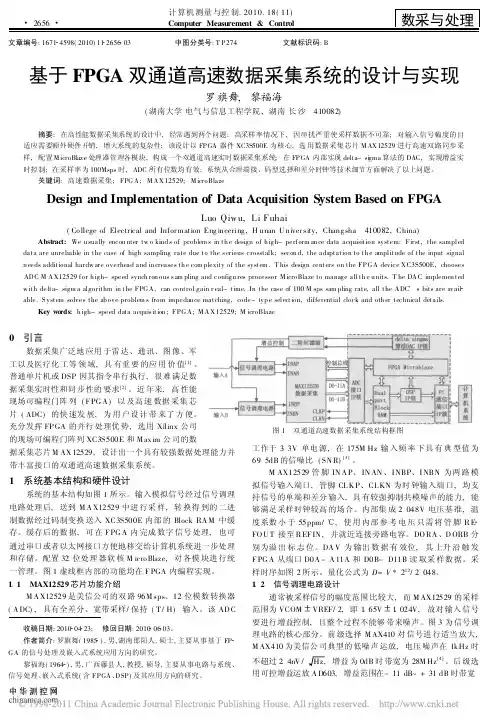

文章编号:1671 4598(2010)11 2656 03 中图分类号:T P274文献标识码:B基于FPGA 双通道高速数据采集系统的设计与实现罗旗舞,黎福海(湖南大学电气与信息工程学院,湖南长沙 410082)摘要:在高性能数据采集系统的设计中,经常遇到两个问题:高采样率情况下,因串扰严重使采样数据不可靠;对输入信号幅度的自适应需要额外硬件开销,增大系统的复杂性;该设计以FPGA 器件XC3S500E 为核心,选用数据采集芯片M AX12529进行高速双路同步采样,配置M icroBlaz e 处理器管理各模块,构成一个双通道高速实时数据采集系统;在FPGA 内部实现delta-si gma 算法的DAC,实现增益实时控制;在采样率为100Msps 时,ADC 所有位数均有效;系统从合理端接、码型选择和差分时钟等技术细节方面解决了以上问题。

关键词:高速数据采集;FPGA;M AX12529;M icroBlazeDesign and Implementation of Data Acquisition S ystem Based on FPGALuo Qiw u,Li Fuhai(Co llege of Electrical and Infor mation Eng ineering ,H unan U niver sity,Chang sha 410082,China)Abstract:We u sually encou nter tw o kind s of problem s in th e design of h igh-perform an ce data acquisition system:First,the sampled data are unreliable in the case of high sampling rate due to the s erious crosstalk;secon d,the adaptation to th e amplitude of the input signal n eeds additional hardw are overhead and in creases th e com plexity of the system.T his design centers on the FPGA device XC3S500E,chooses ADC M AX12529for h igh-speed synch ron ous s am pling and configu res processor M icroBlaze to manage all th e u nits.T he DAC implemen ted w ith delta-sigm a algorithm in the FPGA,can control gain r eal-time.In the cas e of 100M sps sam pling rate,all the ADC s bits are avail able.S ystem solves the ab ove problem s from impedan ce matching,code-typ e selection,differential clock and oth er technical details.Key words :h igh-speed data acquis ition ;FPGA;M AX12529;M icroBlaze图1 双通道高速数据采集系统结构框图0 引言数据采集广泛地应用于雷达、通讯、图像、军工以及医疗化工等领域,具有重要的应用价值[1]。

基于DSP的双路高速数据采集系统的设计[摘要]:文章提出了一种基于DSP高速数据采集系统,该系统实现了对双路数兆赫兹的模拟信号进行采样和存储。

通过DSP控制数据采集和处理,通过串行口将SRAM中的数据上传到微机,以便进行进一步处理。

[关键字]:双路; 高速采样; DSP1. 引言数据采集是获取信息的基本手段,数字信号处理器(DSP)的出现,很好地满足了高速数据采集系统对于核心处理器的要求,并使得在其上实现数字信号处理算法变得简单。

本文本着实用、可靠、安全、简洁及经济等设计原则,提出了一种设计开发基于DSP技术的高速数据采集系统及数字信号处理方法。

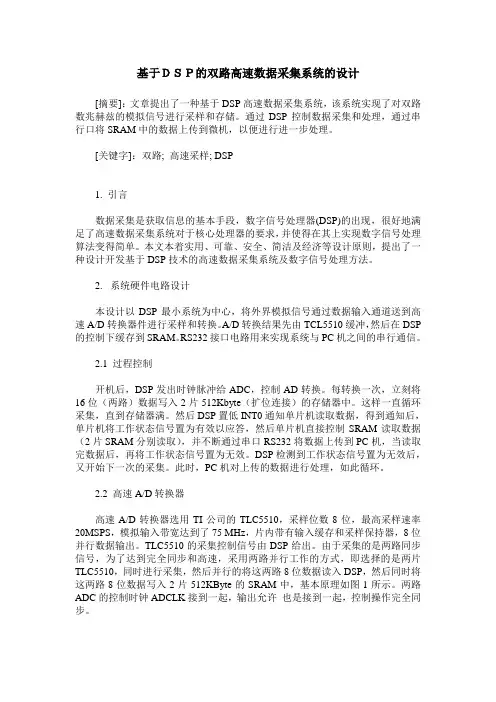

2. 系统硬件电路设计本设计以DSP最小系统为中心,将外界模拟信号通过数据输入通道送到高速A/D转换器件进行采样和转换。

A/D转换结果先由TCL5510缓冲,然后在DSP 的控制下缓存到SRAM。

RS232接口电路用来实现系统与PC机之间的串行通信。

2.1 过程控制开机后,DSP发出时钟脉冲给ADC,控制AD转换。

每转换一次,立刻将16位(两路)数据写入2片512Kbyte(扩位连接)的存储器中。

这样一直循环采集,直到存储器满。

然后DSP置低INT0通知单片机读取数据,得到通知后,单片机将工作状态信号置为有效以应答,然后单片机直接控制SRAM读取数据(2片SRAM分别读取),并不断通过串口RS232将数据上传到PC机,当读取完数据后,再将工作状态信号置为无效。

DSP检测到工作状态信号置为无效后,又开始下一次的采集。

此时,PC机对上传的数据进行处理,如此循环。

2.2 高速A/D转换器高速A/D转换器选用TI公司的TLC5510,采样位数8位,最高采样速率20MSPS,模拟输入带宽达到了75 MHz,片内带有输入缓存和采样保持器,8位并行数据输出。

TLC5510的采集控制信号由DSP给出。

由于采集的是两路同步信号,为了达到完全同步和高速,采用两路并行工作的方式,即选择的是两片TLC5510,同时进行采集,然后并行的将这两路8位数据读入DSP,然后同时将这两路8位数据写入2片512KByte的SRAM中,基本原理如图1所示。

双通道同步高速数据采集器的设计

荆成财;王顺杰;王润田

【期刊名称】《电子产品世界》

【年(卷),期】2012(19)12

【摘要】@@%本文设计了一种Windows操作系统环境下通过USB接口实现的双通道同步高速数据采集器.该采集器利用FT2232H接口芯片完成上位机USB口与ADC转换器件之间的数据通讯.采集器中设置有一个微处理器(MCU),上位机通过USB口发布命令给数据采集器,可以控制采样频率、数据长度及数据传输速率等参数.该采集器设置有两路同步工作的ADC,可实现双通道信号高速采集,最高采样频率可以达到10MSPS.

【总页数】3页(P43-44,54)

【作者】荆成财;王顺杰;王润田

【作者单位】中国科学院声学研究所东海站,上海200030;中国科学院声学研究所东海站,上海200030;中国科学院声学研究所东海站,上海200030

【正文语种】中文

【相关文献】

1.基于USB

2.0的同步高速数据采集器的设计 [J], 梁鸿翔;王润田

2.基于USB2.0的同步高速数据采集器的设计 [J], 林植平;倪瑛

3.基于USB2.0的同步高速数据采集器的设计 [J], 林植平;倪瑛

4.基于USB2.0的同步高速数据采集器的设计 [J], 李林涛;陈明;梁宜勇;王晓萍

B2.0的同步高速数据采集器的设计 [J], 董杨;侯乐

因版权原因,仅展示原文概要,查看原文内容请购买。

多通道数据采集仪的设计与制造数据采集是现代化制造过程中不可或缺的一环,对于监测、控制和分析生产过程中的各项参数具有重要意义。

针对多通道数据采集的需求,设计和制造一款高效可靠的多通道数据采集仪显得尤为重要。

本文将深入探讨多通道数据采集仪的设计与制造,从硬件设计、信号调理到数据处理和通信传输等方面进行全面的讨论。

一、硬件设计在多通道数据采集仪的硬件设计中,关键要素包括模拟输入电路、模数转换器、时钟和触发电路等。

首先是模拟输入电路的设计,它需要能够接受多个通道的模拟信号,并将其转化为数字信号进行后续处理。

为了保证采集的准确性和稳定性,我们需要合理选择高性能的运放和滤波电路,并对输入信号进行适当的放大和滤波,以适应不同通道的输入信号幅值范围和频率特性。

其次是模数转换器的选择和配置,模数转换器的性能将直接影响数据采集仪的精度和速度。

常见的模数转换器有逐次逼近型和Delta-Sigma型等,根据实际需求选择合适的型号,并进行适当的校准和校验,以提高测量的准确性。

时钟和触发电路对于数据采集的同步和触发非常重要。

合理选择和设计时钟电路,使其具有高精度和稳定性,可以确保数据采集的时序准确无误。

而触发电路则能够根据外部或内部信号的变化实现采集的触发和同步,以满足不同应用场景的需求。

二、信号调理在多通道数据采集仪中,信号调理是十分关键的一步。

信号调理的主要任务是对采集到的模拟信号进行预处理,以提高信噪比并滤除噪声和干扰。

信号调理常见的方法包括滤波、放大、去偏移、去噪声和数字滤波等。

滤波是信号调理的一项重要工作,通过滤波可以去除不必要的高频噪声和低频干扰,提取出我们所需的信号成分。

常见的滤波方法有低通滤波、高通滤波和带通滤波等,根据信号的频率范围和噪声特性选择合适的滤波器。

放大是为了增加信号的幅度,并将其调整到合适的范围内以适应后续的模数转换器的输入范围。

放大电路的设计需要考虑到增益的稳定性、幅频特性和噪声等因素,以保证信号的准确性和可靠性。

双通道同步高速数据采集器的设计摘要:本文设计了一种Windows操作系统环境下通过USB接口实现的双通道同步高速数据采集器。

该采集器利用FT2232H接口芯片完成上位机USB口与ADC转换器件之间的数据通讯。

采集器中设置有一个微处理器(MCU),上位机通过USB口发布命令给数据采集器,可以控制采样频率、数据长度及数据传输速率等参数。

该采集器设置有两路同步工作的ADC,可实现双通道信号高速采集,最高采样频率可以达到10MSPS。

引言作为信号处理的第一步,数据的采集传输成为影响系统性能的重要环节。

RS232等传统串口不仅难以满足高速要求,且被主流笔记本所摒弃,而USB接口具有连接方便,高速,即插即用,支持热插拔等优点,使其成为PC机的标准配置,应用范围越来越广。

很显然,利用USB标准实现对仪器仪表输出的模拟信号采集和数据传输已经成为趋势。

梁鸿翔等人利用Cypress公司的USB 控制芯片CY7C68013和同步数据采集芯片AD7862实现双通道信号的同步采集传输,但其驱动开发复杂,灵活性差等缺点,限制了其应用范围。

本文采用FT2232H作为USB协议转换芯片,连接两路独立的ADC,配套底层驱动,避免了驱动开发的难题,而且灵活性好,可扩展性高。

系统组成本文数据采集器由MCU,FT2232H接口芯片,两路ADC(本文为ADC1173)和电源转换电路等组成,其结构框系统硬件设计系统硬件设计主要包括电源部分设计,各器件之间的接口设计和一些辅助电路设计。

本文采用TPS54140电源芯片,外部24V电压供电,转换为系统所需的3.3V。

系统硬件电路设计的重点是FT2232H与ADC的接口设计和FT2232H 与MCU 的接口设计。

FT2232H 与ADC 的接口设计FT2232H 是FTDI 公司生产的USB 与并行接口协议转换芯片。

其具有两个多用途的UART/FIFO 控制器,每个控制器拥有8K 字节缓存(发送和接收各4K 字节缓存),通过其官网提供的配置软件可以分别对其进行功能配置,应用方便简单。

双通道同步数据采集系统的设计与实现

徐灵飞;李健

【期刊名称】《自动化仪表》

【年(卷),期】2011(032)001

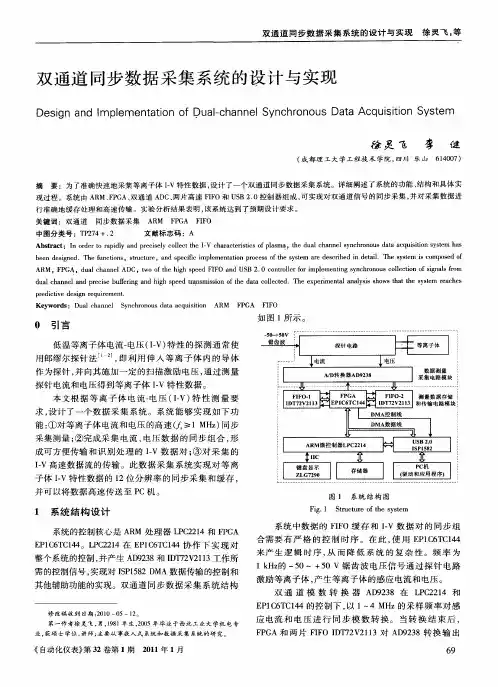

【摘要】为了准确快速地采集等离子体I-V特性数据,设计了一个双通道同步数据采集系统.详细阐述了系统的功能、结构和具体实现过程.系统由ARM、FPGA、双通道ADC、两片高速FIFO和USB 2.0控制器组成,可实现对双通道信号的同步采集,并对采集数据进行准确地缓存处理和高速传输.实验分析结果表明,该系统达到了预期设计要求.

【总页数】4页(P69-72)

【作者】徐灵飞;李健

【作者单位】成都理工大学工程技术学院,四川,乐山,614007;成都理工大学工程技术学院,四川,乐山,614007

【正文语种】中文

【中图分类】TP274+.2

【相关文献】

1.基于ARM的双通道数据采集系统的设计与实现 [J], 丁君武;殳国华;张斌斌

2.同步控制数据采集系统的设计与实现 [J], 黎小巨

3.双通道高速同步数据采集系统的设计 [J], 施杨;迟宗涛;赵泓扬

4.基于FPGA双通道高速数据采集系统的设计与实现 [J], 罗旗舞;黎福海

5.双通道雷达数据采集系统的设计与实现 [J], 李鹏;赵文武;张旭峰;王国庆

因版权原因,仅展示原文概要,查看原文内容请购买。

双通道同步高速数据采集器的设计

摘要:本文设计了一种Windows操作系统环境下通过USB接口实现

的双通道同步高速数据采集器。

该采集器利用FT2232H接口芯片完成上位机USB口与ADC转换器件之间的数据通讯。

采集器中设置有一个微处理器(MCU),上位机通过USB口发布命令给数据采集器,可以控制采样频率、数据长度及

数据传输速率等参数。

该采集器设置有两路同步工作的ADC,可实现双通道信

号高速采集,最高采样频率可以达到10MSPS。

引言

作为信号处理的第一步,数据的采集传输成为影响系统性能的重要环节。

RS232等传统串口不仅难以满足高速要求,且被主流笔记本所摒弃,而USB接口具有连接方便,高速,即插即用,支持热插拔等优点,使其成为PC机的标

准配置,应用范围越来越广。

很显然,利用USB标准实现对仪器仪表输出的

模拟信号采集和数据传输已经成为趋势。

梁鸿翔等人利用Cypress公司的USB 控制芯片CY7C68013和同步数据采集芯片AD7862实现双通道信号的同步采

集传输,但其驱动开发复杂,灵活性差等缺点,限制了其应用范围。

本文采用

FT2232H作为USB协议转换芯片,连接两路独立的ADC,配套底层驱动,避

免了驱动开发的难题,而且灵活性好,可扩展性高。

系统组成

本文数据采集器由MCU,FT2232H接口芯片,两路ADC(本文为

ADC1173)和电源转换电路等组成,其结构框系统硬件设计

系统硬件设计主要包括电源部分设计,各器件之间的接口设计和一些辅

助电路设计。

本文采用TPS54140电源芯片,外部24V电压供电,转换为系统

所需的3.3V。

系统硬件电路设计的重点是FT2232H与ADC的接口设计和。