Quaruts II 7.1简单入门

- 格式:doc

- 大小:3.48 MB

- 文档页数:47

Quartus II简明教程前言本教程是给Quartus II软件的初学者使用的入门级读物,主要翻译Altera公司DE2开发板CD-ROM 中的Quartus II Introduction Using Verilog Design教程而成。

主要内容是结合Altera公司的DE2开发板,通过一个简单的例子介绍使用Quartus II软件进行FPGA设计的整个流程,同时简单介绍FPGA设计的的一些基本知识。

主要作为哈尔滨理工大学电子科学与技术系的<<可编程逻辑器件>>和<<硬件描述语言>>两门课的试验指导材料使用。

限于水平,难免有错误和不妥之处,恳请读者批评指正。

联系作者,作者将不胜感激。

Altera公司的Quartus II设计软件是用来进行SOPC(System-on-a-programmable-chip)设计的综合设计环境。

本教程适用于Quartus II软件的新用户,介绍使用Quartus II软件的进行FPGA设计的基本方法。

需要注意,本教程并不是Quartus II软件的详尽的参考手册。

本教程包含的主要内容:1、典型的FPGA设计流程;2、开始3、新建project4、设计输入5、编译6、引脚分配7、仿真8、编程、配置FPGA器件9、板级调试1、典型的FPGA设计流程计算机辅助设计(Computer Aided Design,CAD)软件的使用使得使用可编程逻辑器件(Programmable Logic Device,PLD)器件(比如Field Programmable Gate Array,FPGA)进行数字逻辑电路设计变得非常容易。

使用CAD软件进行FPGA设计的典型流程如图1所示。

Quartus II软件支持以上设计流程的所有阶段。

本教程介绍Quartus II软件的基本特征。

2、开始在Quartus II软件中设计的每个电路或者子电路都叫做项目(Project)。

QuartusII7.1(SP1)中第三方软件的使用从QuartusII7.1开始支持Node-Locked License的第三方综合器直接从Quartus中调用,因此,使用第三方软件更加方便了。

下面举例说明如何直接从Quartus中直接调用第三方的综合器和仿真器进行综合与仿真。

综合器以Synplify为例,仿真器以Modelsim为例。

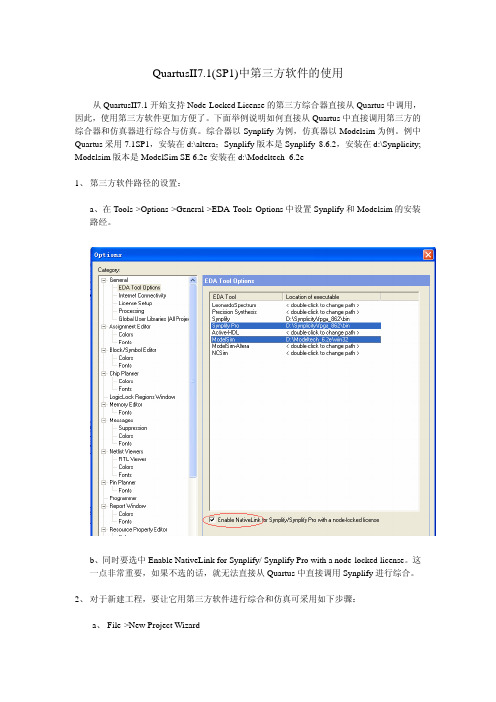

例中Quartus采用7.1SP1,安装在d:\altera;Synplify版本是Synplify 8.6.2,安装在d:\Synplicity; Modelsim版本是ModelSim SE 6.2e安装在d:\Modeltech_6.2e1、第三方软件路径的设置:a、在Tools->Options->General->EDA Tools Options中设置Synplify和Modelsim的安装路经。

b、同时要选中Enable NativeLink for Synplify/ Synplify Pro with a node-locked license。

这一点非常重要,如果不选的话,就无法直接从Quartus中直接调用Synplify进行综合。

2、对于新建工程,要让它用第三方软件进行综合和仿真可采用如下步骤:a、File->New Project Wizard点Next进行下一步。

b、设置工程路径,完成后点Next进行下一步。

c、如果己有源程序,可以在此加入到工程中,如果没有选Next进行下一步。

d、选择器件e、设置第三方工具,EDA design entry/synthesis tool选Synplify,选中Run this toolautomatically to synthesize the current design;EDA simulation tool选Modelsim;如果让Quartus在综合、适配后自动调用Modelsim进行门级时序仿真可以选中Run Gate Level Simulation automatically after compilation,点Next进行下一步。

图解Quartus2使用教程编译程序:file---new---VHDL file-----okBy:酱油跑龙套编译程序---点保存---选择文件夹----修改文件名为of之前内容(注意大小写,保持相同)----点保存By:酱油跑龙套之后弹出建立工程的对话框,选…------选中文件,点打开,再添加By:酱油跑龙套Next之后按如下选择By:酱油跑龙套点finish---然后编译By:酱油跑龙套之后等待弹出编译成功的对话框,点确定。

编译文件完成By:酱油跑龙套原理图文件---左上窗口点file----选中文件右键----创建@¥#……¥By:酱油跑龙套创建原理图文件By:酱油跑龙套加入工程元件By:酱油跑龙套加入输入输出文件By:酱油跑龙套修改输入输出名字(强调方括号,中间两点)By:酱油跑龙套点保存(这个名字无要求)---设置顶层文件----点编译---弹出编译成功的对话框---点确定----原理图文件完成By:酱油跑龙套时序图文件,新建文件By:酱油跑龙套Edit---end timeBy:酱油跑龙套一般为55usBy:酱油跑龙套在时序图中加入引脚By:酱油跑龙套By:酱油跑龙套By:酱油跑龙套之后可以设置输入的高低电平,以及时钟信号By:酱油跑龙套保存,编译,名字无影响,编译成功By:酱油跑龙套●程序下载——pins●By:酱油跑龙套设置硬件引脚By:酱油跑龙套插上usb线后,会安装驱动,按默认安装就好连接成功后选择下载By:酱油跑龙套驱动安装成功后,点击start,下载完成后测试以上所有原文来自天津工业大学:酱油跑龙套By:酱油跑龙套。

Quartus II 入门(以一个简单选择器为例)实验准备随着EDA技术的发展,使用硬件描述语言来设计PLD/FPGA已经成为一种趋势。

利用硬件描述语言,设计者可以将非常复杂的数字系统分为不同层次的模块进行设计,利用EDA工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表。

最后利用FPGA自动布局布线工具,把网表转换为要实现的具体电路布线结构。

Quartus II 软件是数字系统设计的仿真工具,他拥有FPGA和CPLD设计的所有阶段的解决方案,我们可以使用Quartus II 软件完成数字逻辑设计仿真的所有阶段。

Quartus II的设计流程如图错误!文档中没有指定样式的文字。

-1所示。

图错误!文档中没有指定样式的文字。

-1 Quartus II的设计流程图本实验以一个简单的选择器为例介绍利用Quartus II进行数字逻辑设计的基本流程。

选择器是数字逻辑系统的常用电路,是组合逻辑电路中的主要集成元件之一,它是由几路数据输入、一位或多位的选择控制和一路数据输出所组成的。

多路选择器从多路输入中选取其中一路将其传送到输出。

由选择控制信号决定输出的是第几路输入信号。

如图错误!文档中没有指定样式的文字。

-2所示,图中X0-X3为输入端;Y为输出端,选择X0-X3的某个值输出;A1和A0为选择控制端,A1和A0的值决定了Y选择X0-X3的哪一个值输出。

图错误!文档中没有指定样式的文字。

-2 4选1选择器实验目的Quartus II 软件支持多种设计输入模型,本次实验使用Verilog HDL语言输入设计,在DE2-70 开发平台上设计一个基本组合逻辑电路——2选1选择器。

本实验在学习使用Verilog HDL语言进行选择器的设计的同时初步熟悉Quartus II 软件的使用方法。

实验内容1 建立工程。

在用Quartus II 进行设计之初,需要为设计的项目建立一个工程,工程包括设计过程中所有的文件:软件源文件和编译过程中产生的其他文件。

Quartus II入门详细教程实例讲解写在前面:1.本教程适合以前没有接触过QuartusII开发软件的新手,本教程是基础的入门,后续的学习还得大家自己努力。

2.本教程非常详细手把手带大家入门,网上现存的很多教程,有的过于跳跃,难以跟上;有的遇到错误,但教程没有指出,导致我们不知道怎么做。

3.本教程首先通过简单的仿真实验带大家入门。

VHDL源代码会附在文档最后。

4.本教程使用Quartus II 9.1版本进行演示,其他版本的操作差别不是太大,也可以进行学习。

目录一、Quartus II开发软件基本介绍1.1 Quartus Ⅱ简介Quartus Ⅱ是Altera公司推出的专业EDA工具,支持原理图输入、硬件描述语言的输入等多种输入方式。

硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。

1.2 Quartus Ⅱ开发流程使用Quartus II 软件进行开发的流程如图1.2.1所示。

需注意的是,Quartus II还可以使用命令行模式的TCL批处理脚本进行自动流程控制。

图1.2.1 Quartus Ⅱ开发流程二、用3-8译码器的设计介绍QuartusⅡ的基本使用方法(VHDL仿真)1.1打开软件双击桌面安装好的QuartusⅡ 9.1图标,打开软件,主页面如图1所示。

图1在图1中,1区为菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。

2区为快捷工具栏:提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

3区为资源管理窗口。

4区为编译及综合的进度栏:编译和综合的时候该窗口可以显示进度,当显示100%是表示编译或者综合通过。

5区为工作区。

6区为信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

2.2新建工程运行菜单命令“File->New Project Wizard”,打开新工程向导,首先出现如图2所示的工程向导介绍对话框。

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。

可以这样讲,ASIC(Application Specific Integrated Circuit )内部的所有资源,是用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。

并且可以通过软件仿真,我们可以事先验证设计的正确性。

第一章FPGA的基本开发流程下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。

下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管理。

2、建立顶层图。

可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里边,编译的时候就将这些模块整合在一起。

也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。

3、采用ALTERA公司提供的LPM功能模块。

Quartus软件环境包含了大量的常用功能模块,比如计数器、累加器、比较器等等。

4、自己建立模块。

由于有些设计中现有的模块功能不能满足具体设计的要求,那就只能自己设计。

使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。

这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。

5、将顶层图的各个功能模块连线起来。

实验一多路选择器的设计

1、如图1所示在F盘,建立以自己学号命令的文件夹如200913000000,并在其中建立

命为EX1的文件夹,用来保存实验1的文件。

图1

2、如图2所示,点击Flie->New Project Wizard建立新的工程文件。

图2

3、将出现如图3所示的界面,点击如图所示的省略号,选择工程文件所要保存的位置。

图3

4、如图4所示,选中F:\20091300000\EX1并点击打开,进入如图5所示的界面

图4

5、如图5所示,在工程文件保存的路径中显示刚才所选择的路径F:\20091300000\EX1

图5

6、如图6所示,在What is the name of this project的栏目中输入工程的名字本实验临时取mux21a。

同时下面的顶层实体名也同步显示,然后点击Next进入到界面7。

图6

7、如图7所示,本界面是需要选择已有的文件,因为我们是新的工程,暂时没建立任何文件,所以直接点击Next进入到界面8。

图7

8、如图8所示,进行器件选择,我们要根据实验箱的芯片来进行器件选择。

选择ACEX1K 系列。

(注:8B202实验室QII软件为9.1版本,该版本软件不再支持老器件ACEX1K 系列,在实验时请选择Cyclone系列)

图8

9、如图9所示,在ACEX1K系列下选择EP1K30TC144-3的芯片。

然后点击Next进行界面10。

(注:8B202实验室QII软件为9.1版本,该版本软件不再支持老器件ACEX1K 系列,在实验时请选择EP1C6Q240C8)

图9

10、如图10所示,此界面是选择额外的综合、仿真工具软件,因为Quartus II本身自带有这些功能,所以我们不选择额外的工具软件。

直接点击Next进入到界面11。

图10

11、如图11所示,此界面显示前面所有步骤的结果,包括文件保存路径、工程名、顶层实体名、芯片的系列与具体型号、额外的工具软件等等。

检查没错后点击Finish,如果有错点击Back返回进行修改。

图11

12、如图12所示为已经建好工程的界面,显示工程名与工程文件路径。

图12

13、如图13所示,点击新建文件按钮或File->New建立新文件,进入到如图14界面。

图13

14、如图14所示,在Device Design Files栏选择VHDL File,然后点击OK进入下一界面。

如果以后选择建立原理图输入或是其它语言文件,就可选择相应的文件。

图14

15、如图15所示,为已经建立好的VHDL空白文件,点击保存,进入保存文件的界面。

图15

16、如图16所示,为文件保存界面,路径与工程文件统一,默认名为顶层实体名(工程名)。

所以直接点击保存即可。

图16

17、如图17所示,在文件编辑区输入本次实验的VHDL代码。

注意一些括号、分号,别少输或多输。

图17

18、如图18所示,输完代码后,即可对代码进行编译,点击编译按钮。

图18

19、如图19所示为编译过程,会显示编译进度与编译信息。

绿色的为正常的信息提示,蓝色的为警告信息提示,红色的错误信息提示。

出现错误时,编译会自动停止,然后根据错误提示进行排错。

比较常见的错误是实体名与文件名不相同,少输入了一些分号或括号。

如果编译过程没错,则能见到编译成功的界面。

图19

20、如图20所示,为成功编译后的界面,会显示相关信息,如芯片信息、使用资源信息等等。

接下来就可建议仿真文件进行仿真。

图20

21、如图21所示,点击New建立新文件,在Other file 栏选择Vector Waveform File,即建立仿真波形文件。

图21

22、如图22所示为新建vwf文件信息,双击红色矩形框所选的空白区域,弹出红色椭圆所选的插入信号节点的对话框。

再点击Nober Finder…

图22

23、如图23所示为点击Nobe Finder…所出现的对话框,选中要仿真的文件名mux21a,然后点击List。

图23

24、如图24所示为点击List所出现的对话框。

图24

25、如图25所示,点击小红色椭圆所选区域,即把信号节点选入仿真列表,再点击OK 按钮。

图25

26、如图26所示,点击OK按钮。

即可把信号节点添加进vwf文件里。

图26

27、如图27所示为信号节点添加进仿真文件。

图27

28、如图28所示为设置仿真时间区域的对话框,在Edit菜单中选择End Time项,即可弹出图面所示的画面,把单位选“us”,这里仿真时间设为10us,(仿真时间视情况而定)再点击OK按钮。

图28

29、如图29所示为在Edit菜单中选择Grid Size所出现的画面,此选项可以设置栅格的间隔大小,以方便手动画波形大小。

设置完点击OK按钮。

图29

30、如图30所示,用鼠标点击设置对应的波形大小,出现深颜色画面。

图30

31、如图31所示,设置信号波型a的周期,改变红色椭圆所选的区域的值就能改变周期大小。

但必须注意的一点是设置的周期不能太小,即不能小于器件的固有延时,否则,仿真结果会出错。

图31

32、如图32所示为设置信号a周期大小的结果。

图32

33、如图33所示为设置信号b周期大小的对话框,这里设置为100ns。

图33

34、如图34所示为设置信号b周期大小的结果。

图34

35、如图35所示,通过点击放大放小按钮,可以自由地对信号波形进行查看。

图35

36、如图36所示,点击红色矩形所选的按钮进行手动设置信号波形的周期大小,视情况自己设置周期大小。

图36

37、如图37所示,设置完信号波形周期后,点击Fil e→Save,并且命名mux21a(默认)。

图37

38、保存完后,正式进入信号仿真阶段,点击如图38所示的红色矩形所选的波形仿真按钮进行仿真。

图38

39、仿真过程如图39所示,仿真的信息在下方可以出现,仿真成功之后,仿真结果会自动出现。

图39

40、如图40所示为时序仿真结果,可以通过放大放小按钮进行查看。

图40

41、如图41所示,通过了之前的时序仿真验证逻辑,接下来可以进行引脚锁定,选择Assignments 菜单中的Pins 项。

图41

42、如图42所示为选择Pins项出现的画面。

图42

43、如图43所示,在Location中选择对应实验箱中FPGA的引脚。

(对应的引脚可在实验箱说明书Word文档中找到)

图43.

44、如图44所示是各输入输出引脚配置好的画面,其它选项暂时不用管(默认)。

图44

45、引脚配置好后,再编译一遍程序。

图45

46、编译完之后,进入配置文件下载。

点击红色椭圆所选的编程按钮,或者在菜单Tool 中选择Programmer。

此时系统自动会出现配置文件mux21a.sof,,在Mode中选择JTAG (默认)。

并且对配置文件打钩,最后,点击Start进行配置文件下载。

(注:8B202实验室没有EDA实验箱,该步骤无法执行成功。

)

图46。