《数字电路与逻辑设计》改错

- 格式:doc

- 大小:173.84 KB

- 文档页数:3

1. 下列逻辑门中,属于复合逻辑门并可取代其他逻辑门的是 ( )

A.与非门 B.非门 C.或门 D.与门

答案:A

解析:与非门是由与门和非门组合而成

2.下列说法不正确的是()

A.集电极开路的门称为OC门

B.三态门输出端有可能出现三种状态(高阻态、高电平、低电平)

C.OC门输出端直接连接可以实现正逻辑的线或运算

D.利用三态门电路可实现双向传输

答案:C

解析:OC门输出端直接连接可以实现线与运算

3.描述组合逻辑电路的逻辑功能的方式是( )

A.流程表 B.波形图 C.状态表 D.真值表

答案:D

解析:组合逻辑电路的逻辑功能的方式是真值表,前三个都是时序逻辑电路的逻辑功能的表示方式。

4. 下列逻辑电路中,不是组合逻辑电路的是()

A.译码器 B.编码器 C.数据比较器 D.寄存器

答案:D

解析:译码器、编码器、数据比较器都是组合逻辑电路。

5. 如果—半加器的输入为X及Y,产生的和为S,进位为C,则 ( )

A.S=X+Y,C=XY B.S=,C=

C.S=,C=XY D.S=,C=

答案: C

【解析】列出半加器真值表可知。

ACDDC

二、多选题

组合逻辑电路中消除险象的常用方法有哪三种( )

A.触发 B.增加惯性延时环节

C.增加冗余项 D.选通

答案:BCD

解析:BCD都是组合逻辑电路中消除险象的常用方法。

三、简答题

写出下图所示逻辑图输出Y的逻辑表达式,画出其对应的真值表。

答案:{

Y的逻辑表达式

函数F的真值表见表:

}。

《数字电路与逻辑设计》试题3参考答案一. 填空题(10)1. 一个触发器有Q 和Q 两个互补的输出引脚,通常所说的触发器的输出端是指 Q ,所谓置位就是将输出端置成 1 电平,复位就是将输出端置成 0 电平。

2. 我们可以用逻辑函数来表示逻辑关系,任何一个逻辑关系都可以表示为逻辑函数的 与或 表达式,也可表示为逻辑函数的 或与 表达式。

3.计数器和定时器的内部结构是一样的,当对不规则的事件脉冲计数时,称为 计数 器,当对周期性的规则脉冲计数时,称为 定时 器。

4.当我们在计算机键盘上按一个标为“3”的按键时,键盘向主机送出一个ASCII 码,这个ASCII 码的值为 33H 。

5.在5V 供电的数字系统里,所谓的高电平并不是一定是5V ,而是有一个电压范围,我们把这个电压范围称为 高电平噪声 容限;同样所谓的低电平并不是一定是0V ,而也是有一个电压范围,我们把这个电压范围称为 低电平噪声 容限。

二. 选择题(10)1.在数字系统里,当某一线路作为总线使用,那么接到该总线的所有输出设备(或器件)必须具有 b结构,否则会产生数据冲突。

a. 集电极开路;b. 三态门;c. 灌电流;d. 拉电流2.TTL 集成电路采用的是 b 控制,其功率损耗比较大;而MOS 集成电路采用的是 a 控制,其功率损耗比较小。

a. 电压;b.电流;c. 灌电流;d. 拉电流3. 欲将二进制代码翻译成输出信号选用 b ,欲将输入信号编成二进制代码选用 a ,欲将数字系统中多条传输线上的不同数字信号按需要选择一个送到公共数据线上选用 c ,欲实现两个相同位二进制数和低位进位数的相加运算选用 e 。

a. 编码器;b. 译码器;c. 多路选择器;d. 数值比较器;e. 加法器;f. 触发器; g. 计数器; h. 寄存器4. 卡诺图上变量的取值顺序是采用 b 的形式,以便能够用几何上的相邻关系表示逻辑上的相邻。

a. 二进制码; b. 循环码; c. ASCII 码; d. 十进制码5. 根据最小项与最大项的性质,任意两个不同的最小项之积为 0 ,任意两个不同的最大项之和为1 。

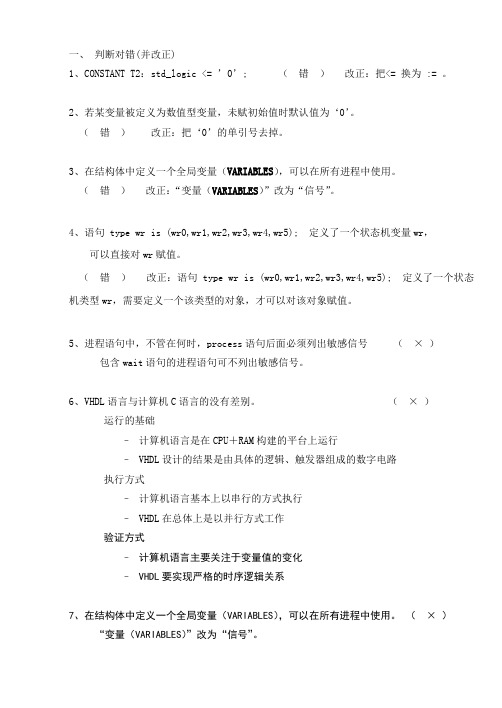

一、判断对错(并改正)1、CONSTANT T2:std_logic <= ’0’;(错)改正:把<= 换为 := 。

2、若某变量被定义为数值型变量,未赋初始值时默认值为‘0’。

(错)改正:把‘0’的单引号去掉。

3、在结构体中定义一个全局变量(VARIABLES),可以在所有进程中使用。

(错)改正:“变量(VARIABLES)”改为“信号”。

4、语句 type wr is (wr0,wr1,wr2,wr3,wr4,wr5); 定义了一个状态机变量wr,可以直接对wr赋值。

(错)改正:语句 type wr is (wr0,wr1,wr2,wr3,wr4,wr5); 定义了一个状态机类型wr,需要定义一个该类型的对象,才可以对该对象赋值。

5、进程语句中,不管在何时,process语句后面必须列出敏感信号(×)包含wait语句的进程语句可不列出敏感信号。

6、VHDL语言与计算机C语言的没有差别。

(×)运行的基础–计算机语言是在CPU+RAM构建的平台上运行–VHDL设计的结果是由具体的逻辑、触发器组成的数字电路执行方式–计算机语言基本上以串行的方式执行–VHDL在总体上是以并行方式工作验证方式–计算机语言主要关注于变量值的变化–VHDL要实现严格的时序逻辑关系7、在结构体中定义一个全局变量(VARIABLES),可以在所有进程中使用。

(×)“变量(VARIABLES)”改为“信号”。

8、Moore状态机输出只是状态机当前状态的函数,Mealy状态机输出为有限状态机当前值和输入值的函数(√)9、传统的系统硬件设计方法是采用自上而下(top down)的设计方法,利用硬件描述语言(HDL)的硬件电路设计方法采用自下而上(bottom up)的设计方法。

(×)传统的系统硬件设计方法是采用自下而上(bottom up)的设计方法,利用硬件描述语言(HDL)的硬件电路设计方法采用自上而下(top down)的设计方法10、VHDL可以采用层次化的设计,一个高层的结构体中可以调用低层的实体(√)11、一个VHAL程序中仅能使用一个进程(process)语句。

数字电路与逻辑设计习题答案数字电路与逻辑设计习题答案数字电路与逻辑设计是计算机科学与工程领域中的重要基础课程,它涉及到数字信号的处理和转换,以及逻辑门电路的设计和分析。

学习这门课程时,习题是巩固知识和提高能力的重要途径。

下面将给出一些常见的数字电路与逻辑设计习题的答案,希望对大家的学习有所帮助。

1. 设计一个4位二进制加法器电路,实现两个4位二进制数的相加。

答案:一个4位二进制加法器电路可以由四个全加器电路组成。

每个全加器电路有三个输入:两个被加数和一个进位输入,以及两个输出:和位和进位输出。

将四个全加器电路按位级联,将进位输出连接到下一位的进位输入,最后一个全加器的进位输出作为最高位的进位输出。

和位的输出即为两个4位二进制数的和。

2. 给定一个3输入的逻辑电路,输出为1的条件是至少有两个输入为1。

请设计一个电路,实现这个逻辑功能。

答案:可以使用与门和或门组合的方式来实现这个逻辑功能。

首先,将三个输入分别与一个与门的三个输入相连,将输出连接到一个或门的输入。

然后,将三个输入分别与一个或门的三个输入相连,将输出连接到与门的输入。

这样,当至少有两个输入为1时,与门的输出为1,或门的输出也为1。

3. 给定一个4输入的逻辑电路,输出为1的条件是输入中有奇数个1。

请设计一个电路,实现这个逻辑功能。

答案:可以使用异或门实现这个逻辑功能。

首先,将四个输入两两分组,然后将每组的输出与另一组的输出进行异或操作。

最后,将四个异或门的输出连接到一个或门的输入。

这样,当输入中有奇数个1时,异或门的输出为1,或门的输出也为1。

4. 设计一个4位比较器电路,实现两个4位二进制数的大小比较。

答案:一个4位比较器电路可以由四个比较器组成。

每个比较器有两个输入:两个被比较的位,以及一个输出:比较结果。

将四个比较器电路按位级联,将每个比较器的输出连接到下一位比较器的输入。

最后一个比较器的输出即为两个4位二进制数的大小比较结果。

5. 给定一个3输入的逻辑电路,输出为1的条件是输入中的1的个数大于等于2。

数字电路与逻辑设计习题及参考答案一、选择题1. 以下表达式中符合逻辑运算法则的是 D 。

A.C ·C=C 2B.1+1=10C.0<1D.A+1=12. 一位十六进制数可以用 C 位二进制数来表示。

A . 1B . 2C . 4D . 163. 当逻辑函数有n 个变量时,共有 D 个变量取值组合?A. nB. 2nC. n 2D. 2n4. 逻辑函数的表示方法中具有唯一性的是 A 。

A .真值表 B.表达式 C.逻辑图 D.状态图5. 在一个8位的存储单元中,能够存储的最大无符号整数是 D 。

A .(256)10B .(127)10C .(128)10D .(255)106.逻辑函数F=B A A ⊕⊕)( = A 。

A.BB.AC.B A ⊕D. B A ⊕7.求一个逻辑函数F 的对偶式,不可将F 中的 B 。

A .“·”换成“+”,“+”换成“·”B.原变量换成反变量,反变量换成原变量C.变量不变D.常数中“0”换成“1”,“1”换成“0”8.A+BC= C 。

A .A+B B.A+C C.(A+B )(A+C ) D.B+C9.在何种输入情况下,“与非”运算的结果是逻辑0。

DA .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是110.在何种输入情况下,“或非”运算的结果是逻辑1。

AA .全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为111.十进制数25用8421BCD 码表示为 B 。

A .10 101B .0010 0101C .100101D .1010112.不与十进制数(53.5)10等值的数或代码为 C 。

A .(0101 0011.0101)8421BCDB .(35.8)16C .(110101.11)2D .(65.4)813.以下参数不是矩形脉冲信号的参数 D 。

A.周期B.占空比C.脉宽D.扫描期14.与八进制数(47.3)8等值的数为: BA. (100111.0101)2B.(27.6)16C.(27.3 )16D. (100111.101)215. 常用的BCD码有 D 。

《数字电路》 勘误表第一章2.第16页图1.16(a )改为A B FC D3.第16页图1.17(a )和图1.18(a )门电路符号分别改为=1A BFA BF=4.第17页表1.11第1行、第5列AB 改为B A 。

5.第18页例1.11解答中)()(C B A B C A B A Y ++⋅+⋅+=改为)()(C B A B C A B A Y ++⋅+⋅+= 6.第22页图1.21输出变量F 改为Z 。

7.第23页第4行、到数11、12行中“∑-=121n i im”改为“∑-=120n i im”8.第24页中间“)()(35B A B M M +++++=+”改为 “)()(35C AC B A M M +++++=+=1”9.第28页图1.26左边卡诺图右上角方格中B A 改为B A10.第29页表11.第29页图1.30卡诺图左上角符号F 改为L 。

12.第30页图1.31卡诺图改为100011110ABCD00011110010*********1L13.第37页第3题“A C D B B A A C C B B A ++=++”改为“A C C B B A A C C B B A ++=++” 14.第38页17题“A D D C C B B A D C B A ABCD +++=+”改为 “A D D C C B B A D C B A ABCD +++=+”第二章15.第49页倒数第7行,“V OH =V DD +I OH ×r DSP =5V -4.5mA ×100Ω=0.45V ”改为“V OH =V DD +I OH ×r DSP =5V -4.5mA ×100Ω=4.55V ”16.第53页图2.21(a )中“V DD 1=5V ”改为“V DD =5V ”。

17.第57页式2.8“)(1TDD -=V v S ei i ”改为“)(1TDD -=V v S eI i ” 18.第59页,图2.31和图2.32中逻辑门中的小圆圈去掉。

《数字电路与逻辑设计》综合练习题及解答第一部分习题一、填空1.将十进制数转换成等值的二进制数、十六进制数。

10 = 2= 162.10= 余3BCD= 8421BCD 3.16= 24.一位二进制数只有2个数,四位二进制数有个数;为计64个数,需要位二进制数。

5.二进制数2的等值八进制数是8。

6.二进制数2的等值十进制数是10。

7.欲对100个对象进行二进制编码,则至少需要位二进制数。

8.二进制数为000000~111111能代表个十进制整数。

9.为将信息码10110010配成奇校验码,其配奇位的逻辑值为;为将信息码01101101配成偶校验码,其配偶位的逻辑值为。

10.格雷码的特点是。

11.n变量函数的每一个最小项有个相领项。

12.当ij时,同一逻辑函数的两个最小项mimj=。

2n113.n变量的逻辑函数,mi为最小项,则有mi=。

i014.逻辑函数FABCD的反函数F=。

15.逻辑函数FA(BC)的对偶函数F是。

16.多变量同或运算时,=0,则xi=0的个数必须为。

17.逻辑函数F(A,B,C)1C18. 逻辑函数F(A,B,C,D)( )。

19.逻辑函数F(A,B,C)(ABC)(ABC)的最简与或式为。

20.巳知函数的对偶式F(A,B,C,D)ABCDBC,则它的原函数F =。

* * * * * 21.正逻辑约定是、。

22.双极型三极管截止状态过渡到饱和状态所需的过渡时间称为时间,它时间和时间两部分组成,可用等式描述。

23.双极型三极管饱和状态过渡到截止状态所需的过渡时间称为时间,它时间和时间两部分组成,可用等式描述。

1。

AB的最小项表达式为F(A,B,C)=m(1,2,3,4,8,10)(0,12,14)的最简与或式为F=24.三极管反相器带灌电流负载时,负载电流的方向是从,此时反相器输出电平。

25.三极管反相器带拉电流负载时,负载电流的方向是从,此时反相器输出电平。

26.输入端的噪声容限说明。

数字电路答案2210 = 2*81+ 6*8 0 = 268268 = 2 6 = 1011Q010110101102 = 00010110= 1^62 1 010810 = 1*8 + 5*8 + 4*8 = 15481548 = 1 5 4 = 11011002001101100110110Q = 0110(100= 6C 166 C1 0 - 113.12510 = 1*8 1 + 5*8 0 + 1*8 1 = 15.1815.18= 1 5. 1 = 1101.0012001 101 0011101.001 = 1101.0010= D.216D2131.62510 = 2*8 2 + 0*8 1 + 3*8 0 + 5*8 "1 =203.58203.58 = 2 0 3. 5= 10000011.101010 000 011 10110000011.10!= 10000011.1010= 83.A 1683A1-1数字电路答案 第一章习题(1) 1-2 (1)1011012= 101101= 5581011012= 0010(10仁2D558= 5*8 1 + 5*8 0 = 451011100101= 011{0010仁3451110010!= {1100101= E^6E 53458 = 3*8 2 + 4*8 1 + 5*8 0 = 22910(1)168 = 1*8 1+ 6*8 0= 1410168= 16= 1110200111011102= 1110= E 161728 二 1*8 2+ 7*8 1+ 2*8 01728 = 1 7 2 = 11110102001111 01011110102 01111010 7A 167 A61.538 = 6*8 1 + 1*8 0 + 5*8 1 + 3*8 2 = 49.6721。

61.538 = 6 1.5 3 = 110001.101011110 001 101 011110001.101011 = 00110001.10101100= 31.AC 1631A C2 10 1126.748 = 1*8 + 2*8 + 6*8 + 7*8 " 126.748 = 1 2 6. 7 4 = 1010110.1111001 010110 1111001010110.1111= 01010110.1111= 56.F 165 6 F1-41-3 101.0011= 101.001100= 5.148101.001!= 0101.0011= 5.3165.148 = 5*8 0 + 1*8"1+ 4*8 ■2 = 5.187510100111.101 = 100{11.{01=47.4100111.101 = 00100111.{010= 27.A 16 47.58 4*81 7*80 5*8 139.625i 0(1)-2+ 4*8 = 86.9375102A= 2 A = 101010,16001010101010102 = 101010= 528I 5 I 21 0528= 5*8 + 2*8 = 4210(1)(2)B2F16 = B 2 F = 1011001011111011 00101111101100101111 = 101100{l01f1仁545785 4 5 754578 = 5*8 3 + 4*8 2 + 5*8 1 + 7*8 0 = 2863。

数字电路与逻辑设计

位置

原内容

修改后

P5

第25行 (502.67)8=(101000.110111)B

(502.67)8=(101000010.110111)B P7 第1行

① 当S 为整数时:

②当S 为小数时:

P8 第7行 解:[N1+N2]补= [N1]补+[N2]补=1.0100 + 1.1110= 1. 0 1 1 0 解:[N1+ N2]补= [N1]补+[ N2]补=1.0100 + 1.1110= 1. 0 0010 P9 表1.3

格雷码 0011 0100 0101 0110 0111 1000 1001 1010 1011

1100

格雷码 0000 0001 0011 0010 0110 0111 0101 0100 1100

1101

P15

第1行

证明:设变量A X =,则: 0,1=∙=∙=+=+A A A A A A A X

证明:设变量A X =,则:

,1=∙=∙=+=+A A A X A A A X

P15 第7行至第8行

B A X +=证明:设B A B B A A B A B A B A X ⋅⋅+⋅⋅=⋅⋅+=⋅+)(则0=⋅=⋅A A A X

B A X B A ⋅==+∴

B

A X +=证明:设B

A B A B A B B A A B A B A B A X B A B A B

A B A B A X ⋅=+∴=+=⋅⋅+⋅⋅=⋅⋅+=⋅⋅=+=⋅++=⋅++=⋅+000)(11则

P18倒数 第6行 则这个与项称为该函数的一个标准或

项 则这个或项称为该函数的一个标准或项 P19

则逻辑函数的最小项表达式中有该变

则逻辑函数的最大项表达式中有该变量取

[S]反=

S 0≤S <2n

2n+1-1+S -2n

<S ≤0

表2-8下 第1行 量取值组合对应的最大项。

值组合对应的最大项。

P24 第6行 而只有五个以上变量的卡诺图中才会有相对相邻关系。

而只有五个以上变量的卡诺图中才会有相重 相邻关系。

P26 图 2.14下第2行 D C A D C AB D C B A =+ D C A D C AB D C B A =+

P27 第29行 D C A CD BC F ++= D C A CD BD F ++= P28 第6~7行 C

B CD AB F ++=))()((

C B

D C B A F F +++==

D

B CD AB F ++=))()((D B D

C B A F F +++==

P29 表2-12

表格第8列中第5行的P 4改为√,表格第8列中第6行的√改为P 4 P32倒数第8行 约束条件为AB+AC=0

约束条件为AB+CD=0

P32倒数第4行 化简得:C A BD D A F ++= 化简得:C A B D A F ++=

P32 图2-21

P51 图3-23

P2是或门的输出,即P2之前的逻辑门无小圆圈

P52倒数第4行 A A A F =⋅= A A A F =⋅= P52倒数第3行 A A F =⋅=1

A A F =⋅=1

P53倒数第9行 A A F =+=0

A A F =+=0

P53倒数第28行 A A A A A F =⋅+⋅=

A A A A A F =⋅+⋅=

P56 图3-30a

P56倒数第2行

03=X Y 00X Y =

A

C

00

11

1

0011 1

1

1

1 1 d 0

d d d

d

d

d

1

1 1

AB

C 00 01

0 1 11

10

0 1 0

0 1

0 1

P57

AB

C B A B A B A S =⊕=+=

AB

H B A B A B A S =⊕=+=

P60 第7行 当M =1时,B ⊕1=B ,

电路执行A -B=A+B 运算。

当M =1时,B ⊕1=B , 电路执行A -B 运算。

P64 表3-25 X G G 、种取值组合为的第、1221

X G G 、种取值组合为的第、0221

P68 图3-57 左下逻辑门为异或门 左下逻辑门为或门

P69 图3-57

P70

表3-29

比 较 输 入

级 联 输 入

输 出 A 3 B 3 A 2 B 2 A 1 B 1 A 0 B 0 (a >b)(a <b)(a=b) (A >B)(A <B)(A=B) A 3<B 3 A >B 3 A 3 =B 3 A 3=B 3 A 3=B 3 A 3=B 3 A 3 =B 3 A 3=B 3 A 3=B 3 A 3=B 3

A 3 =

B 3 × × × × A 2<B 2 A 2>B 2 A 2 =B 2 A 2 =B 2 A 2 =B 2 A 2 =B 2 A 2 =B 2 A 2 =B 2

A 2 =

B 2

× × × × × × × × A 1<B 1 A 1>B 1 A 1 = B 1 A 1 = B 1 A 1 = B 1 A 1 = B 1 A 1 = B 1 × × × × × × × × × × × × A 0<B 0 A 0>B 0 A 0 =B 0 A 0 =B 0 A 0 =B 0

× × × × × × × × × × × × × × × × × × × × × × × × 0 1 0 1 0 0 0 0 1

0 1 0 1 0 0 0 1 0 1 0 0 0 1 0 1 0 0 0 1 0 1 0 0 0 1 0 1 0 0 0 0 1

F A > B

F A < B F A = B 1

A B

&

&

= 1

1。