数字实验指导书20130506

- 格式:doc

- 大小:529.50 KB

- 文档页数:13

数字电子技术实验指导书信息学院2013年2月数字电路实验注意事项1.每次实验前,必须预习,并自行设计实验原始记录表格,提交预习报告。

2.每次实验完毕,须做好实验原始记录;关闭所有仪器的电源,关闭电源插座板上的开关;整理实验台,并在学生实验记录本上签名,并记录仪器使用情况。

该项工作作为部分成绩记入实验总成绩。

最后,经老师同意方可离开实验室。

3.做好实验总结报告,准时在下次实验时提交。

4.拨插芯片请使用专用工具,在把芯片插入插座之前,请用镊子将芯片管脚修理整齐,拨芯片须使用起拨器。

5.将芯片插入插座时,一定注意芯片的方向。

6.每次接线完毕,须检查正确后,方可接上电源。

实验二组合逻辑电路(逻辑运算及全加器)一、实验目的1.掌握组合逻辑电路的功能调试。

2.验证半加器和全加器的逻辑功能。

3.学会M进制数的运算规律。

二、实验仪器及材料逻辑箱74LS00 74LS86 74LS54三、预习要求1.预习组合逻辑电路的分析方法.2.预习用与非门和异或门构成的半加器、全加器的工作原理。

3.预习二进制数的运算。

四、实验内容1.组合逻辑电路功能测试(1)用2片74LS00组成图2.1所示逻辑电路。

为便于接线和检查,在图中要注明芯片编号及各引脚对应的编号。

图2.1(2)先按图2.1写出Y2的逻辑表达式并化简。

表2.1输入输出A B C Y1 Y20 0 0 1 1 1 1 0 011111111(3)图中A、B、C接逻辑开关,Y1,Y2接发光管电平显示。

(4)按表2.1要求,改变A、B、C输入的状态,填表写出Y1,Y2的输出状态。

(5)将运算结果与实验结果进行比较。

2.用门电路组成半加器电路根据半加器的逻辑表达式可知,半加器Y是A、B的异或,而进位Z 是A、B相与,即半加器可用一个异或门和二个与非门组成一个电路。

如图2.2。

图2.2(1)在数字电路实验箱上插入异或门和与非门芯片。

输入端A、B接逻辑开关k,Y,Z接发光管电平显示。

《数字测图原理与方法》实习指导任务书兰州理工大学技术工程学院《数字测图原理与方法》教学实习指导书一、实习目的与要求《数字测图原理与方法》是测绘工程专业的主要基础课之一,又是一门实践性很强的课程,为进一步巩固和深化课堂教学内容,培养学生运用所学测量学基本理论和基本技能解决实际问题的能力,加强基本功训练和测量工程师素质的培养,培养学生吃苦耐劳、团结协作的集体精神,根据教学计划安排,于2014年6月30日~7月18日安排为期三周的集中教学实习,其目的与要求为:1.熟练掌握常用测量仪器(水准仪、经纬仪、全站仪)的使用方法。

2.掌握图根导线测量、交会测量,四等水准测量的观测方法和计算方法。

3.掌握数字测图的基本要求和成图过程,掌握大比例尺数字测图方法和数字成图软件的使用。

二、实习任务与计划1. 图根控制测量(包括选点、埋石、观测和计算);2. 1:500数字地形测图。

三、实习组织实习组织:由指导教师,各班班长、学习委员组成实习组织领导。

每班分为若干实习小组(由班长学委根据仪器分组),设组长1人,实行组长负责制,负责全组的实习分工和仪器安全管理。

四、实习生职责1. 实习生应严格遵守学校和实习队的规章制度,严格遵守测量仪器、工具的正确使用和维护要求”、“测量资料的记录要求”以及有关实验室规则。

2. 严格遵守实习纪律。

按时出工、收工,要特别注意自身安全,不做有损自身安全的事情。

未经实习队和学校批准,不得缺勤、私自外出,不得组织、参与影响社会安定团结和人民生命财产安全的活动,否则后果自负。

3. 实习期间,注意劳逸结合,生活讲究卫生,生病及时治疗,保证身体健康。

4.实习生应熟悉实习的目的、任务及要求,在规定的时间内保质保量完成实习任务。

熟练掌握作业程序,提高测量作业技能,注意理论联系实际,培养分析问题、解决问题的能力,注重创新能力和综合素质的提高。

5. 实习期间,要特别注意测量仪器的安全,各组要指定专人妥善保管仪器、工具。

数字系统设计实验指导书Experiments Handbook of Digital System Design实验一:8位简单算逻运算单元电路设计8 bit Simple ALU实验学时:4学时实验类型:设计型一、目的与任务要求学生在理论课学习的基础上,掌握采用Verilog HDL、基于自顶向下的模块化设计方法;掌握在Quartus II EDA平台进行设计输入、编译、仿真的全过程。

二、内容与要求1. 内容在Quartus II EDA平台上,运用基于模块化的设计方法,采用Verilog HDL,设计一个8位简单ALU及其数据通道,功能如表,分别根据操作码实现加、减、逻辑与、或等八种运算,数据通道在读写命令控制下,完成从寄存器读出操作数及写入运算结果。

要求:其输入操作数为实验学生学号末尾开始尽量非零的四位数对应的8421码组合(例如,学号11070023两个操作数分别为32和71,对应的8421码00110010,2.要求预习实验内容,编写Verilog HDL程序。

课上,进行编程输入、编译、时序仿真。

课后写出实验报告(实验名称、实验内容、顶层框图、V erilog HDL程序、仿真波形、资源分配、实验小结)三、考核与成绩评定本实验为学生必做实验,本实验分值为20 分考核内容:预习25%,实验过程50%,实验报告25%。

成绩评定方法:根据考核内容进行综合评定。

四、实验说明本实验的重点在于自顶向下的模块化设计的概念及设计方法。

五、参考资料ALU及数据通道参考教材《VerilogHDL高级数字系统设计》P478和P208实验三、基于循环算法的数字签名分析电路的验证Verification of Repetitive Algorithm based Digital SignatureAnalysis Circuit实验学时:2 实验类型:验证型一、目的与任务:要求学生在理论课学习的基础上,分析基于CRC码进行数字签名验证功能需求,学习用Verilog HDL中循环算法进行行为建模的功能设计,在EDA平台-QuartusII下,完成设计的输入及编译综合以及仿真验证。

目录实验一通用模拟与数字双踪示波器的使用及测量 (1)实验二信号发生器性能测试和应用 (11)实验三相位、时间和频率的测量 (18)实验四交流电压表的测量及分析 (20)实验五 LabVIEW的示波器原理及应用仿真实验 (27)实验一通用模拟与数字双踪示波器的使用及测量一、实验目的和要求1.根据已学的示波器理论知识学习正确使用通用双踪示波器,并利用示波器进行各种电信号的测量,熟练掌握模拟示波器的使用。

2.学习数字式通用示波器的使用,了解其在测量上的强大功能,并与模拟示波器进行比较,体会各自在测量上的特点。

3.认真按实验内容的要求进行实验,记录有关的数据和波形,回答实验内容中提出的有关问题,并按时提交实验报告。

二、实验原理在时域信号测量中,电子示波器无疑是最具代表性的典型测量仪器。

它可以精确复现作为时间函数的电压波形(横轴为时间轴,纵轴为幅度轴),不仅可以观察相对于时间的连续信号,也可以观察某一时刻的瞬间信号,这是电压表所做不到的。

我们不仅可以从示波器上观察电压的波形,也可以读出电压信号的幅度、频率及相位等参数。

电子示波器是利用随电信号的变化而偏转的电子束不断轰击荧光屏而显示波形的,如果在示波管的X偏转板(水平偏转板)上加一随时间作线性变化的时基信号,在Y偏转板(垂直偏转板)加上要观测的电信号,示波器的荧光屏上便能显示出所要观测的电信号的时间波形。

若水平偏转板上无扫描信号,则从荧光屏上什么也看不见或只能看到一条垂直的直线。

因此,只有当X偏转板加上锯齿电压后才有可能将波形展开,看到信号的时间波形。

一般说来,Y偏转板上所加的待观测信号的周期与X偏转板上所加的扫描锯齿电压的周期是不相同的,也不一定是整数倍,因而每次扫描的起点对待观测信号来说将不固定,则显示波形便会不断向左或向右移动,波形将一片模糊。

这就有一个同步问题,即怎样使每次扫描都在待观测信号不同周期的相同相位点开始。

近代电子示波器通常是采用等待触发扫描的工作方式来实现同步的。

福建农林大学计算机与信息学院《数字逻辑》实验指导书2012年3月编电子技术实验室实验守则一、实验课前:每个学生必须认真预习实验指导书和与本实验有关的教材内容,写出实验预习报告。

明确实验目的和实验原理,了解实验内容与步骤,掌握仪器、仪表的使用方法,作好实验准备工作。

二、上实验课:学生必须认真听讲,接好线路后,需经指导教师复查批准,才准接通电源。

三、实验时,每个学生都应严肃认真,勤于动手、独立思考、细心操作,注意观察、如实作好记录。

教师根据每个学生的实验技能,动手能力评定平时成绩。

四、实验过程中,如发现仪器设备有冒烟、焦味、异响、漏电等异常现象,应立即切断电源,保持现场,请指导教师检查处理。

五、实验完成后,需请指导教师检查预习报告和实验数据以及所使用的仪器设备,经教师检查签字后方可离开实验室。

六、学生因请假而需要补做实验者,应本人申请,经指导教师同意,并安排好时间补做。

七、每个学生必须爱护实验室的仪器设备,使用前,若发现故障及时请指导教师检查。

与本实验无关的仪器设备不准动用,凡不听教师讲解,进行错误操作以致损坏设备者,按赔偿条例酌情处理。

八、实验室是教学场所,应保持整洁,安静,不得喧哗打闹,不准吸烟,不准随地吐痰,不准乱抛纸屑,不准在实验室内吃东西,不准在仪器设备上或桌面上涂写,穿拖鞋者一律不准进入实验室。

九、对违反上述规则又不听劝阻者,教师有权令其退出实验室实验一 TTL与非门参数及功能测试一、实验目的1. 了解TTL 与非门电路的主要参数。

2. 掌握TTL 与非门电路的主要参数和传输特性的测试方法。

3. 熟悉TTL 门电路的逻辑功能的测试方法。

二、实验仪器与器件1. 数字电路实验箱1个2. 万用表1只3. 示波器1台4. 元器件TTL与非门74LS00 2片电阻、电容若干三、实验原理TTL 门电路是最简单、最基本的数字集成电路元件,利用其通过适当的组合连接便可以构成任何复杂的组合电路。

因此,掌握TTL 门电路的工作原理,熟练、灵活地使用它们是数字技术工作者必备的基本功之一。

数字电子技术实验指导书(2010-8-6)注意事项:1、进入实验室(一教805)必须穿鞋套,否则不允许进入实验室。

2、进入实验室后遵守实验室的规章制度3、该课程共有6个实验,实验内容有验证性、综合性和设计性实验。

在做实验之前必须做好预习工作。

完成每个实验的预习要求,明确实验目的,切实地掌握理论知识和实验原理,尽量做到带着问题来实验。

对于设计性实验,需要预先设计好电路,画出电路原理图和器件引脚连接图。

4、进入实验室学生要细心连接电路,通电前须仔细检查电路的电源电压和接地情况,检查无误后通电。

出现问题时要冷静的分析并查找原因。

对实验过程中出现的现象、电路调整的过程以及测量结果要认真、客观的记录。

做实验的过程中最多是2人一组,2人互相配合完成实验,发现不积极主动做实验的,本次实验成绩为0。

5、实验时注意观察,若发现有破环性现象(如元器件发烫、异味、冒烟),应立即关断电源,保持现场,并报告指导老师,找出原因,排除故障,经指导老师同意后再继续实验。

6、实验完成后要让指导教师检查实验结果,正确后方可拆除电路。

7、实验结束后,撰写实验报告(电子版),分析和整理实验数据,加深对理论知识和实验原理的理解,增强利用理论知识,解决设计问题的能力。

实验报告的格式在网络教学平台,自己下载。

8、有2个或2个以上的实验没有完成,该课程的实验成绩为不及格。

实验项目:实验一:门电路逻辑功能及参数测试一、实验目的1 •熟悉数字逻辑实验箱的结构、基本功能和使用方法。

2•掌握常用非门、与非门、异或门的逻辑功能及其试方法二、实验器材1.数字逻辑实验箱DICE-SEM1台2.万用表1只3.元器件:74LS002块74LS04 (或CD4069 74LS20 74LS86 各1 块导线若干三、实验说明1 •数字逻辑实验箱提供+ 5V ± 12V的直流电源供用户使用。

2•连接导线时,为了便于区别,最好用不同颜色导线区分电源和地线,一般用红色导线接电源,用黑色导线接地。

《数字系统设计》实验报告班级_______电信2班_________________ 姓名____潘俊俊_____________________ 学号___1309121091__________________实验1 组合电路的设计实验目的:熟悉ISE的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

实验内容:首先利用ISE完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出仿真波形。

实验程序:ENTITY mux21a ISPORT (a, b, s: IN BIT;Y: OUT BIT);END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGINPROCESS (a, b, s)BEGINIF s='0' THEN y<=a; ELSE y<=b;END IF;END PROCESS;END ARCHITECTURE one;实验结果:1、综合电路图2、 仿真时序图实验分析:在0—275ns 内,s=0, 则输出a 波形;在275—685ns 内,s=1,则输出b 波形;在685ns 以后,s=0, 则输出a 波形;仿真结果与实验要求一致,故仿真结果正确。

实验2 时序电路的设计实验目的:熟悉ISE的VHDL文本设计过程,学习简单时序电路的设计、仿真和测试。

实验任务:设计一个带使能输入及同步清0的增1/减1的3位计数器,并仿真。

实验程序:Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity up_down isPort(clk,rst,en,up: in std_logic;Sum: out std_logic_vector(2 downto 0);Cout: out std_logic);End;Architecture a of up_down isSignal count: std_logic_vector(2 downto 0);BeginProcess(clk,rst)BeginIf rst=’0’ thenCount<=(others=>’0’);Elsif rising_edge(clk) thenIf en=’1’ thenCase up isWhen ‘1’ => count<=count+1;When others =>count<=count-1;End case;End if;End if;End process;Sum<=count;Cout <=’1’ when en=’1’ and ((up=’1’ and count=7) or (up=’0’ and count=0)) else ‘0’;End;实验结果:1、综合电路图2、仿真时序图实验分析:当rst=’0’ ,输出被清零;否则(rst=1,en=1)当up=1时,输出count<=count+1,若up=0,输出count<=count-1。

数字电子技术实验指导书电子工程系目录第一部分实验基础知识一实验的基本过程---------------------------------------------3二实验操作规范和故障检查方法---------------------------------4 三数字电路实验箱简介-----------------------------------------6 第二部分基本实验实验一逻辑门电路的逻辑功能及测试------------------------------7 实验二组合逻辑电路的设计-------------------------------------10 实验三数据选择器及应用---------------------------------------12 实验四译码器及应用-------------------------------------------14 实验五字段译码器逻辑功能测试及应用---------------------------16 实验六触发器-------------------------------------------------19 实验七计数器及其应用-----------------------------------------22 实验八移位寄存器功能测试及应用-------------------------------25 实验九 555定时器---------------------------------------------28 实验十计数、译码、显示电路-----------------------------------31附录:常用集成电路引脚功能图-------------------------35第一部分实验基础知识随着科学技术的发展,数字电子技术在各个科学领域中都得到了广泛的应用,它是一门实践性很强的技术基础课,在学习中不仅要掌握基本原理和基本方法,更重要的是学会灵活应用。

《数字集成电路》实验指导书何爱香信息与电子工程学院2013年1月目录实验1译码器 (3)实验2组合逻辑电路..................................................................6实验3半加器...........................................................................8实验4全加器...........................................................................9实验5三进制计数器 (11)实验6 555多谐振荡器 (13)实验7电压比较器 (15)实验8Pspice最坏情况分析 (16)实验1 译码器一、 实验目的1. 理解译码器逻辑功能。

2. 掌握译码器电路设计方法。

二、 实验内容译码器74155的芯片如下图所示,逻辑函数式:B A Y +=三、 实验步骤(1) 在pspice 中,启动Place/Part 命令,出现下图所示的选择框,输入74155,点击OK 。

(2)控制端1C 设置为高电平,使能端G 1设置为低电平。

在pspice 中,高低电平要用专门的符号来设置,启动Place/Ground 命令,出现下图所示的选择框,在SOURE 库中取“$D_HI ”符号,即为接入高电平,取“$D_LO ”符号,接到电路的输入端,即为接入低电平。

(2) 设置输入信号AB启动Place/Part 命令,出现下图所示的选择框,输入DigClock 。

通过设置时钟信号源参数调整方波的周期可占空比。

设置输入信号A 的ONTIME 和OFFTIME 为。

设置输入信号B 的ONTIME 和OFFTIME 为1ms时钟信号源有5个周期参数要设置:在一个周期内,低电平状态的持续时间:在一个周期内,低电平状态的持续时间。

数值计算基础实验指导书2013年目录实验一直接法解线性方程组的 (1)实验二插值方法 (20)实验三数值积分 (7)实验四常微分方程的数值解 (11)实验五迭代法解线性方程组与非线性方程 (16)实验一 直接法解线性方程组一、实验目的掌握列选主元消去法与追赶法解线性方程组。

二、实验内容分别写出Guass 列选主元消去法与追赶法的算法,编写程序上机调试出结果,要求所编程序适用于任何一解线性方程组问题,即能解决这一类问题,而不是某一个问题。

实验中以下列数据验证程序的正确性。

1、用Guass 列选主元消去法求解方程组⎥⎥⎥⎦⎤⎢⎢⎢⎣⎡=⎥⎥⎥⎦⎤⎢⎢⎢⎣⎡⎥⎥⎥⎦⎤⎢⎢⎢⎣⎡--5.58.37.33.47.11.85.16.93.51.53.25.2321x x x2、用追赶法求解方程组⎥⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎢⎣⎡-=⎥⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎢⎣⎡⎥⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎢⎣⎡-----000010210000210000210000210000254321x x x x x 三、实验仪器设备与材料主流微型计算机四、实验原理1、Guass 列选主元消去法 对于AX =B1)、消元过程:将(A|B )进行变换为)~|~(B A ,其中A ~是上三角矩阵。

即:⎪⎪⎪⎪⎪⎭⎫⎝⎛→⎪⎪⎪⎪⎪⎭⎫ ⎝⎛n nnnn n nnn n nn b a b a b a a b a a a b a a a b a a a010122111221222221111211 k 从1到n-1a 、 列选主元选取第k 列中绝对值最大元素ik ni k a ≤≤max 作为主元。

b 、 换行ik ij kj b b n k j a a ⇔+=⇔,,1,c 、 归一化 kkk k kj kk kj b a b n k j a a a ⇒+=⇒/,,1,/d 、 消元nk i b b a b n k j n k i a a a a i k ik i ij kj ik ij ,,1,,,1;,,1, +=⇒-+=+=⇒-2)、回代过程:由)~|~(B A 解出11,,,x x x n n -。

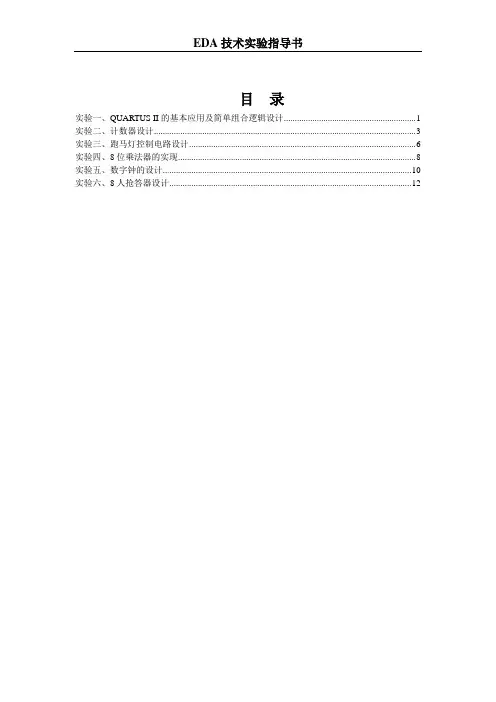

目录实验一、QUARTUS II的基本应用及简单组合逻辑设计 (1)实验二、计数器设计 (3)实验三、跑马灯控制电路设计 (6)实验四、8位乘法器的实现 (8)实验五、数字钟的设计 (10)实验六、8人抢答器设计 (12)实验一、QUARTUS II的基本应用及简单组合逻辑设计一、实验前准备本实验例子使用独立扩展下载板EP1K10_30_50_100QC208(芯片为EP1K100QC208或者芯片为EP1K30TC144)。

EDAPRO/240H实验仪主板的VCCINT跳线器右跳设定为3.3V;EDAPRO/240H实验仪主板的VCCIO跳线器组中“VCCIO3.3V”应短接,其余VCCIO均断开;独立扩展下载板“EP1K10_30_50_100QC208”的VCCINT跳线器组设定为2.5V;独立扩展下载板“EP1K10_30_50_100QC208”的VCCIO跳线器组设定为3.3V。

二、实验目的1、熟悉Quartus II的菜单、元件库、功能模块及基本应用操作;2、熟悉Quartus II的Verilog HDL文本方式及原理图方式设计实现流程。

3、学习使用JTAG接口下载逻辑电路到可编程逻辑器件并能调试到正常工作。

4、熟悉数字电路集成设计的过程。

三、实验内容1、用Verilog HDL文本方式设计带使能控制的3-8译码器;三、实验原理1、3-8译码器:译码器是把输入的数码解出其对应的数码,译码器有N个二进制选择线,那么最多可译码转换成2N个数据。

当一个译码器有N条输入线及M条输出线时,则称为N×M的译码器。

3×8译码器是依此而来。

3×8译码器真值表如下表所示:四、实验步骤新建设计文件夹(不可用中文)-》新建设计文件-》输入设计项目(原理图/Verilog HDL 文本代码)-》存盘(注意原理图/文本取名)-》将设计项目设置成Project-》选择目标器件-》启动编译-》建立仿真波形文件-》仿真测试和波形分析-》引脚锁定并编译-》编程下载/配置-》硬件测试五、硬件测试说明1、把译码器的输入接到拨码开关,使能控制端接按键,输出端接8个LED灯,通过拨码开关改变输入的逻辑电平变化来观察LED输出情况,验证3×8译码器的工作状态。

《数字电子技术》实验指导书一、实验目的数字逻辑是一门实践性、工程性很强的技术基础课。

因此,不仅要重视理论教学,更要注重实践技能的培养和训练。

实验是本课程的重要组成部分,通过实验,使学生学会查阅产品手册、拟定实验方案、选择与配置实验设备、查明与排除故障和分析实验现象等。

从而巩固、加深和拓宽学生对课程内容的理解,培养分析、设计和调试数字系统的能力。

二、实验程序通过逻辑设计实验,可验证设计思想,测试和调整电路的输入、输出关系,进一步完善电路的逻辑功能。

实验的一般程序是:1.实验准备实践证明,实验前的准备工作做得越充分,则实验成功的可能性就越大。

因此,不可忽视实验前的准备,实验前应做好如下工作。

①实验者应根据实验目的、要求及内容,认真复习有关的理论知识,并写出满足实验内容要求的逻辑函数表达式。

②根据实验所提供的集成电路组件,将输出函数表达式转换成适当的形式。

③写实验预习报告。

实验预习报告是实验操作的依据,要求报告尽可能写得简洁,思路清楚,一目了然。

实验预习报告以实验逻辑图为主,附以简要的文字说明,并拟定好实验步骤以及记录实验结果的有关表格。

2.布线实验准备工作完毕后,就要动手将逻辑电路图变为实际电路。

在布线前,必须校准集成电路组件两排引脚的距离,使之与实验台的通用逻辑测试板上的插孔行距相等。

将集成电路组件插入测试板时,用力要轻、均匀,开始不要插得太紧,待确定集成电路组件的引脚和插孔位置一致后,再用力将其插牢。

这样可避免集成电路组件引脚弯曲或折断。

布线所用导线最好选用不同颜色,以便区别不同用途。

例如,接地导线用黑色,电源线用红色,输入信号线统一用黄色,输出信号线统一用白色等。

布线最好有顺序地进行,不要随意接线,以免漏接。

布线时应首先将电源、地线及实验过程中始终不改变电平的输入端接好,然后按信号流向顺序依次布线。

布线用的导线不宜太长,并且应尽量避免导线相互重叠、跨越集成电路组件的上空及无规则的交错连接在空中搭成网状等现象。

目录物理实验一(使用DAS软件操作) (4)练习用位移传感器测量 (4)研究匀速直线运动 (5)瞬时速度的测定 (5)从v—t 图求加速度 (6)研究自由落体运动 (7)斜面上力的分解 (7)验证力的平行四边形定则 (7)牛顿第二定律 (8)力的相互作用 (9)动能大小的比较 (10)动量定理 (10)机械能守恒定律 (11)气体压强与体积的关系 (12)气体压强与温度的关系 (13)研究摩擦生热 (13)小灯泡的U—I 曲线描述 (14)电源电动势与内阻测量 (14)通电螺线管的磁感应强度 (14)测量微弱磁通量变化时的感应电流 (15)观察音叉的振动 (15)物理实验二(使用单机运行平台操作) (16)匀变速直线运动 (16)牛顿第二定律 (17)瞬时速度、加速度的测量 (17)弹簧振子的振动过程 (18)向心力摆研究向心力 (19)转动平台研究向心力 (20)弹簧的弹力与弹簧的伸长的关系 (22)滑动摩擦力与正压力 (23)气体压强与体积的关系 (23)气体绝热过程 (24)研究电容充放电 (24)LC电磁振荡 (25)通电螺线管的磁场 (25)单导线切割磁力线 (26)测小灯泡的U—I特性曲线 (26)定值电阻上电压——电流关系 (27)交流电的研究 (27)放射性辐射测量实验 (28)化学实验(使用单机运行平台操作) (29)探究人体吸入的空气和呼出的气体有什么不同 (29)探究酒精灯外焰、内焰加热效果的不同 (30)探究空气中氧气和二氧化碳的含量 (31)不同催化剂对双氧水的催化分解 (31)酸碱中和滴定曲线的绘制 (32)酸碱中和反应中反应热的测量 (33)探究硫代硫酸钠结晶过程中的能量变化 (34)探究实验-———盐酸与碳酸钠的过量反应 (35)探究稀硫酸与氢氧化钡溶液过程中的电导率变化 (36)无水硫酸铜水化热的测量 (37)物质溶解过程中的能量变化 (38)盐酸滴定碳酸钠pH反应曲线的绘制 (39)冰醋酸稀释过程中的电导率变化(连续测量) (40)冰醋酸稀释过程中的电导率变化(单点采样) (41)研究弱电解质的电离平衡 (42)研究电解质的电离 (43)研究强弱电解质的电导率 (44)探究盐溶液的酸碱性 (44)生物实验(使用单机运行平台操作) (45)考马斯亮兰法测定蛋白质的含量 (45)酵母菌发酵的实验 (47)探究绿豆发芽过程中的呼吸作用 (48)细胞膜的渗透作用 (49)食物中铁元素含量的测定 (49)探究不同pH对过氧化氢酶催化活性的影响 (51)探究不同温度对过氧化氢酶催化活性的影响 (52)验证酶催化的高效性 (54)研究水果电池 (55)植物的光合作用 (55)植物的呼吸作用 (57)探究蜡烛在烧杯中燃烧过程中氧气和二氧化碳浓度的变化 (57)测量水中的溶解氧 (58)附录: (59)第一部分软件安装使用说明 (59)一、软件安装使用说明 (59)(一)GQY数字实验平台安装说明: (59)(二)系统要求: (59)(三)驱动安装说明: (60)二、产品使用常见问题与解决方法: (60)第二部分:DAS 软件操作说明 (62)第三部分:单机运行平台操作说明 (63)打开软件 (63)装载实验模板 (63)装载实验模板 实验实验例操作 (63)清空实验数据 (63)回软件主界面 (63)保存实验数据 (63)单机平台与模板制作平台的切换 (63)调试与运行控键 (63)求导采样间隔 (63)标定 (63)选择连接方式 (63)数据采集器与软件的连接 (63)数据采集器与软件的连接 实验实验例操作 (63)开始和结束实验 (63)保留一次实验的部分实验数据及曲线——实验曲线区域选择 (64)实验数据整理 ......................................................................................................................... 64 针对一次..实验的全部实验数据......及曲线拟合方式——拟合方式1 (64)(1)拟合 (64)(2)预设拟合 (64)针对一次..实验的部分..实验数据及曲线拟合方式--拟合方式2 .......................................... 64 (1)拟合 .. (64)(2)预设拟合 (64)针对多次..实验的实验数据拟合方式(实验结果分析)-—拟合方式3 .............................. 65 传感器校零 .. (65)传感器校零实例操作 (65)单点采样 (65)单点采样实验实例操作 (65)实验回放 (65)实验回放实例操作 (66)退出软件 (66)第四部分:生化传感器标定 (66)一 、溶解氧传感器的使用及标定 (66)二、 色度计测量方法 (67)三、 氧化还原电位的测量标准溶液 (67)四、 pH 值传感器的使用及标定 (68)第五部分:配套教具使用方法(部分) (69)1、GQYelab 机械能守恒实验仪(J-23) (69)2、GQYelab 导轨小车及其附件(J —4) (71)3、GQYelab力的合成与分解实验仪(J-27) (71)4、GQYelab电流磁场线圈(J—7) (71)5、GQYelab受迫振动与共振实验仪(J—6) (71)6、GQYelab向心力仪(转动平台) (72)7、GQYelab斜面上力的分解实验仪一 (73)8、GQYelab斜面上力的分解实验仪二 (74)第六部分数据采集器的使用说明 (75)一、DAS-5104D数据采集器使用说明 (75)二、DAS—5104数据采集器使用说明 (75)按键说明 (75)数据采集器软件操作说明 (76)物理实验一(使用DAS软件操作)练习用位移传感器测量►实验器材:数据采集器、计算机、位移传感器。

数字电子技术综合性、设计性实验指导书于瑞红编防灾科技学院2013年4月实验一 基本逻辑门电路功能测试一、实验目的1.初步学习使用数字电子实验箱。

2.在数学电路学习机上测试基本逻辑门电路的功能。

二、实验仪器及材料1.数字电子实验箱 2.与非门(74LS20)、异或门(74LS86)、与或非门(74LS64)三、预习要求1.预习基本逻辑门电路的功能。

2.画出与非门、异或门、与或非门的逻辑真值表。

四、实验概述1.与非门的逻辑功能与非门的逻辑功能是:当输入端有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”。

)其逻辑表达式为 ....AB Y =本实验采用四输入双与非门74LS20,其引脚排列如图1.1所示。

1C 1A 1B 1F 2A 2B 2F图 1.1 图 1.22.异或门的逻辑表达式为 .....⊕⊕=B A Y本实验采用二输入四异或门74LS86,其引脚排列如图1.2所示。

3.与或非门的逻辑表达式为 .....++=CD AB Y 本实验采用与或非门74LS64,其引脚排列如图1.3所示。

图 1.3 图 1.4五、实验任务1.测试与非门的逻辑功能。

在数字实验箱上插装一个与非门(74LS20),用逻辑电平开关的输出作为与非门的输入,发光二极管作为与非门的输出指示,改变输入电平,记录下与非门的输出状态,画出真值表,测试结果应与真值表相符。

2.测试异或门的逻辑功能。

在数字实验箱上插装一个异或门(74LS86),其引脚排列如图1.2所示。

选择两个逻辑电平开关的输出作为异或门的输入,用发光二极管作为输出指示,改变输入电平,记录异或门的输出状态,画出真值表。

3.图1.4所示是一个与或非门,写出它们的逻辑表达式。

在数字实验箱上插装一个与或非门(74LS64),测试它的逻辑功能。

记录测试结果并列真值表。

六、实验报告1.要求画出真值表并与测试结果比较。

《数字电子技术》实验指导书安阳工学院电子信息与电气工程学院实验要求一、实验前必须充分预习,完成指定的预习任务。

二、用仪器和实验箱前必须了解其性能、操作方法及注意事项,在操作时应严格遵守。

三、实验时接线要认真,相互仔细检查,确定无误才能接通电源。

四、实验时应注意观察,若发现有破坏性异常现象,例如元件冒烟、发烫或有异味等,应立即关断电源,保持现场,报告指导老师。

找出原因、排除故障,经指导老师同意后再继续做实验。

五、实验过程中需要改接线时,应关断电源后才能拆、接线,使用自锁紧插头时,严禁用力拉线,拆线时,应手捏线端并旋转轻微向上用力拔起,以防线被拉断。

六、实验过程中要仔细观察实验现象,记录实验结果(数据、波形、现象)。

所记录的实验结果经指导老师审阅签字后再拆除实验线路。

七、实验结束后,必须关断电源、拔出电源插头,并将仪器、设备、工具、导线等按规定整理。

八、实验后每个学生必须按要求独立完成实验报告。

数字电路实验箱使用说明本实验箱可以完成数字电路课程实验,由实验板和保护箱组成。

该实验箱的实验板采用独特的两用板工艺,正面贴膜,印有原理图及符号,反面为印制导线并焊有相应元器件,需要测量及观察的部分装有自锁紧式接插件,使用直观、可靠。

一、技术性能及配置1、电源输入 : AC220V 士 10 %。

输出 : DC 5V/1A 、 DC 1、25V ~ 15V/0、2A (两路) 有过载保护及自动恢复功能。

2、信号源单脉冲:为消抖动脉冲,可同时输出正负两个脉冲,前后沿≤20ns ,脉冲宽度≤0、2μs ,脉冲幅值为 TTL 电平。

连续脉冲:两组,一组为 4 路固定频率的方波。

其频率分别为 200KHZ 、100KHz、50KHz、25KHz 。

另一组为: 1Hz~5KHz 连续可调方波,分二档由开关切换,两路输出均为 TTL 电平。

3、八组逻辑电平开关:可输出“O”、“1”电平。

置于H时输出为+5V,置于L时输出为0。

数字电路实验指导书莆田学院自编-、集成门电路二、 T TL 集电极开路门与三态输出门的应用 (9)三、 加法器 (15)四、 数据选择器 (19)五、 触发器 (23)六、 集成电路计数器、译码和显示 (30)七、 移位寄存器 (35)八、 集成定时器 (41)九、 电子秒表 (47)十、模/数和数/模转换器 (52)(1)(3)实验一集成门电路一、实验目的1.学习测试“与非”门电路的电压传输特性和逻辑功能。

2.了解“与非”门组成的具它逻辑门。

二、实验原理“与非”门是门电路中应用较多的一种,它的逻辑功能是:全“1”出“0”,有“0”出“1”。

即只有当全部输入端都接高电平“1”时,输出端才是低电平“0”,否则,输出端为高电平“1”。

图1一1是一个具有3个输入端的“与非”门逻辑图。

根据手册规定,“与非” 门的高低电平和具他电参数有一定的规范值,(见表1一1)。

若不符合,则表明该“与非” 门不能使川。

图1一2检验“与非”门应按表1 — 1规定的测试条件进行。

在实际使用时,有时可用万用表对 “与非”门进行简易检验。

以TTL “与非”门为例,当接通5V 直流电源后,先让各个输入 端接高电平,用万用表测量其输出端的电压。

然后把各个输入端依次接地,测量输出端的电 压,根据测量数据是否符合规范值则可判别这个“与非”门好否。

集成“与非”门的电压传输特性,指的是“与非”门输出电压妆)随输入电压他变化的 关系曲线,如图1一2所示。

图中A 点相应的输入电压称为关门电平“曲,B 点相应的输入 电压称为开I 】电平〃()N 。

传输特性的测量方法很多,最简单的方法是把直流电压通过电位器分压加在与非门的输 入端,如图1一4所示,川万川表逐点测出对应的输入,输出电压,然后绘制成曲线。

为了 读数容易,在调节⑷过程屮即可先监视输出电压的变化,再读出U 来,否则在开门电平和 关门电平Z 间变化的电压不易读出来。

为了在示波器上观察到电压传输特性,可按图 1—3接线,可把输岀电压«()接入示波器的y 输入端,输入电压U 可由函数 信号发生器输出的100Hz 正弦波通过二极管半波整 流示得到,同时把这个输 入信号送入示波器的x图1一3正弦波信号轴,作为扫描电压,调节绚人小可在示波器显示屏上观察到一条完整的电压传输特性Illi 线。

实验一基本门电路

一、实验目的

(1)熟悉常用门电路的逻辑功能;

(2)学会利用门电路构成简单的逻辑电路。

二、实验器材

数字电路实验箱 1台;74LS00、74LS02、74LS86各一块

三、实验内容及步骤

1、TTL与非门逻辑功能测试

将四2输入与非门74LS00插入数字电路实验箱面板的IC插座上,任选其中一与非门。

输入端分别输入不同的逻辑电平(由逻辑开关控制),输出端接至LED“电平显示”。

观察LED亮灭,并记录对应的逻辑状态。

按图1-1接线,检查无误方可通电。

图1-1 表1-1 74LS00逻辑功能表

2、TTL或非门逻辑功能测试

选取四2输入或非门74LS02任一门电路,测试其逻辑功能。

74LS02逻辑功能表

3、TTL异或门逻辑功能测试

选取四2输入异或门74LS86中的任一门电路,测试其逻辑功能。

74LS86逻辑功能表

4、用四2输入与非门74LS00实现与或门Y=AB+CD的功能。

画出实验连线图,并验证其逻辑功能。

四、思考题

1.TTL与非门输入端悬空相当于输入什么电平?

2.如何处理各种门电路的多余输入端?

附:集成电路引出端功能图

实验二组合逻辑电路

一、实验目的

熟悉简单组合电路的设计和分析过程。

二、实验器材

数字电路实验箱 1台,74LS00 三块,74LS02、74LS04、74LS08各一块

三、实验内容及步骤

1、设计一个能比较一位二进制A与 B大小的比较电路,用X1、X

2、X3分别表示三种状态:A>B时,X1=1;A<B时X2=1;A=B时X3=1。

(用74LS04、74LS08和74LS02实现)

要求:(1)列出真值表;

(2)写出函数逻辑表达式;

(3) 画出逻辑电路图,并画出实验连线图;

(4)验证电路设计的正确性。

2、测量组合电路的逻辑关系:

(1)图2-2电路用3块74LS00组成。

按逻辑图接好实验电路,输入端A、B、C分别接“逻辑电平”,输出端D、J接LED“电平显示”;

图2-2 表2-2

(2)按表2-2要求,将测得的输出状态和LED显示分别填入表内;

(3)根据测得的逻辑电路真值表,写出电路的逻辑函数式,判断该电路的功能。

四、思考题

总结组合逻辑电路分析和设计步骤。

附:集成电路引出端功能图

74LS08

实验三 译码器及其应用研究

一、实验目的

(1)测试3线-8线译码器74LS138的逻辑功能; (2)研究用译码器设计组合电路。

二、实验器材

数字电路实验箱 1台,74LS138、74LS30各一块 三、实验内容及步骤 1、74LS138逻辑功能测试

对照74LS138引脚图连接实验连线图,使能端S 1 、S 2′、S 3′和地址输入端A 2 、A 1 、A 0分别接“逻辑电平”,输出端接LED“电平显示”;将测试结果填入功能表3-1。

表3-1

2、用74LS138构成逻辑函数发生器 要求用74LS138实现逻辑函数:

(1)推导出与译码器输出端相对应的函数式; (2)画出逻辑电路图,并画出实验连线图; (3)将测试结果填入真值表3-2。

四、思考题

1.分析74LS138的S 1、S 2′、S 3′端的作用。

2.总结用译码器设计组合电路的方法。

附:集成电路引脚排列图 表3-2

74LS30(8输入与非门)

ABC

C AB C B A C B A C B A Y +'+'+''+'''

=

实验四数据选择器及其应用研究

一、实验目的

(1)测试双4选1数据选择器74LS153、8选1数据选择器74LS151的逻辑功能;

(2)研究用数据选择器设计组合电路的方法。

二、实验器材

数字电路实验箱 1台,74LS153、74LS151、74LS32、74LS04各一块

三、实验内容及步骤

1、74LS153逻辑功能测试

(1)按实验电路图4-1连线,地址输入端A1、A0分别接逻

辑开关K1、K2,S1′接开关K3。

(2) K3=0,当A1A0=00时,数据输入端D10接逻辑开关,观

察输出端Y1与D10的关系;依次将其余输入端输入数据观察

输出状态。

将实验结果填入功能表4-1。

(3) K3=1,观察输出状态是否改变。

(4) 当S2′接逻辑开关K3时,重复上述步骤。

图4-1

表4-1

2、74LS153扩展成8选1数据选择器。

按图4-2连接,观察A2分别为0和1时,输出与哪一组数据输入相关。

图4-2 表4-2

3、用74LS151(扩展后的74LS153)设计一个多数表决电路。

该电路有三个输入端A、B、C,分别代表三个人的表决情况。

“同意”为1态,“不同意”为0态,当多数同意时,输出为1态,否则输出为0态。

(1)根据题意列真值表,写出最小项逻辑表达式;

(2)画出逻辑电路图,完成实验连线图,并将测试结果填入表4-2。

附:集成电路引出端功能图

74LS32

实验五 触发器及其应用

一、实验目的

(1)掌握基本的SR 、JK 、D 和T 触发器的逻辑功能; (2)掌握集成触发器的逻辑功能及使用方法; (3)熟悉触发器之间相互转换的方法。

二、实验器材

数字电路实验箱 1台,74LS00 、74LS76、 74LS74各一块 三、实验内容及步骤 1、测试SR 锁存器的逻辑功能

按图5-1,用两个与非门组成SR 锁存器,输入端R ′、S ′接逻辑开关,输出端Q 、Q ′接逻辑电平显示,按表5-1要求测试,并记录之。

图5-1 表5-1

2、测试双JK 触发器74LS76逻辑功能 (1)测试 的复位、置位功能,任取一个JK 触发器,使 、 J 、K 接逻辑开关插口,CLK 接单次脉冲源,Q 、Q ′端接至逻辑电平,按表5-2测试 、 功能。

表5-2

(2) 测试JK 触发器的逻辑功能和触发方式

D

R '

D

S 'D

S

'D

R 'D

R 'D S

'

使==1,按表5-3要求改变J、K、CLK状态,观察Q状态的变化,观察触发器状态更新是否发生在CLK脉冲下降沿。

表5-3 表5-4

(3)将JK触发器J、K端连在一起,接高电平,构成T′触发器。

在CLK端输入1Hz连续脉冲,观察Q端的变化。

3、测试维持阻塞D触发器74LS74的逻辑功能

(1)测试R D′、S D′的复位、置位功能,内容同本实验2之(1),自拟表格。

(2) 测试D触发器的逻辑功能:按表5-4要求进行测试,观察触发器状态更新是否发生在CP 脉冲上升沿

(3)将D触发器的Q′端与D端相连接,构成T′触发器,测试方法同本实验2之(3)

四、思考题

用JK触发器74LS76和用D触发器74LS74构成的T′触发器会有什么不同?

附:集成电路引出端功能图

D

R'

D

S

'

实验6 时序逻辑电路

一、实验目的

(1)了解触发器在计数电路中的应用,熟悉计数器的工作原理。

(2)掌握用触发器构成计数器的方法。

二、实验器材

数字电路实验箱 1台,74LS76两块

三、实验内容及步骤

1、异步二进制加法计数器

图6-1

(1)将两个74LS76按图6-1接成4位二进制加法计数器,4个触发器的输出端Q分别接至LED显示,RD′接逻辑开关,SD′接高电平,CLK0接手动单脉冲或1Hz连续方波脉冲。

(2)RD′接低电平,使各触发器清零后,再将RD′接高电平,让单次脉冲逐个送入CLK0, 观察并记录Q3~Q0的状态,填入表6-1。

表6-1

(3)将单次脉冲改为1Hz连续脉冲,观察Q3~Q0

的状态。

2、异步二进制减法计数器

将低位触发器的Q′端与高一位的CLK端相连构成减法计数器如图6-2。

重复实验1(2)、(3)。

自拟表格填入数据。

图6-2

四、思考题

下降沿触发的JK触发器构成的异步4位二进制加法、减法计数器是如何串接的?附:集成电路引出端功能图

实验七计数器及其应用

一、实验目的

(1)熟悉计数器的工作原理。

(2)掌握中规模集成计数器的使用及功能测试方法。

(3)掌握运用集成计数器实现任意进制的计数器的方法。

二、实验器材

数字电路实验箱 1台,74LS161(或74LS160)、74LS20各一块

三、实验内容及步骤

1、测试74LS161(或74LS160)的逻辑功能。

自拟实验连线图,验证表7-1的工作状态。

表7-174LS161/160功能表

2、用74LS161(或74LS160)和与非门74LS20实现七进制计数器。

电路图如图7-1,按图接线并验证,其有效状态转换图如图7-2。

若用置零法实现电路应如何连接。

画出原理图,连线并验证之。

四、思考题

若要构成十三进制计数器用一片74LS161能否实现?一片74LS160能否实现?

附:集成电路引出端功能图。