计算机组成原理实验静态随机存储器

- 格式:doc

- 大小:860.50 KB

- 文档页数:6

北京科技大学计算机与通信工程学院实验报告实验名称:静态随机存储器学生姓名:专业:计算机科学与技术班级:学号:指导教师:实验成绩:实验地点:机电楼301实验时间:2015 年 6 月 1 日一、实验目的与实验要求1、实验目的(1)掌握微程序控制器的组成原理;(2)掌握微程序的编制、写入方法;(3)观察并掌握微程序的运行过程;(4)掌握静态随机存储器的基本结构;(5)掌握静态随机存储器RAM工作特性及数据的读写方法。

2、实验要求(1)验证性实验:微程序控制器实验(2)用QuartusⅡ软件编写一个静态随机存储器二、实验设备(环境)及要求实验箱,Window 8,QuartusⅡ软件三、实验内容与步骤1、实验1(1)实验原理微程序控制器的基本任务是完成当前指令的翻译和执行,即将当前指令的功能转换成可以控制的硬件逻辑部件工作的微命令序列,完成数据传送和各种处理操作。

它的执行方法就是将控制各部件动作的微命令的集合进行编码,即将微命令的集合仿照机器指令一样,用数字代码的形式表示,这种表示成为微命令。

这样就可以用一个由多条微指令组成的序列表示一条机器指令,这种微指令序列称为微程序。

微程序存储在一种专用的存储器中,成为控制存储器,微程序控制器原理框图如图3.25所示。

本实验所用的微程序控制器单元主要有编程部分和核心微控器组成,如图3.26所示。

本实验中的微指令字长共24位,控制位顺序如表3.8所示。

本实验安排了四条机器指令,分别为ADD(0000 0000)、IN(0010 0000)、OUT(0011 0000)和HLT(0101 0000),括号中为各指令的二进制代码,指令格式如表3.9所示,其中高4位为操作码。

实验中的4条机器指令由CON单元的二进制开关手动给出,其余单元的控制信号均由微程序控制器自动产生,为此可以设计出相应的数据通路图,见图3.27所示。

将全部微程序按微指令格式变成二进制微代码,可得到表3.10的二进制代码表。

静态随机存储器实验报告1. 背景静态随机存储器(SRAM)是一种用于存储数据的半导体器件。

与动态随机存储器(DRAM)相比,SRAM速度更快、功耗更低,但成本更高。

SRAM通常用于高速缓存、寄存器文件和数据延迟线等需要快速访问的应用。

本实验旨在通过设计和实现一个简单的SRAM电路来深入了解SRAM的工作原理和性能特点。

2. 设计和分析2.1 SRAM基本结构SRAM由存储单元组成,每个存储单元通常由一个存储电容和一个存储转换器(存储反转MOSFET)组成。

存储电容用于存储数据位,存储转换器用于读取和写入数据。

存储单元按照空间布局进行编址,每个存储单元都有一个唯一的地址。

地址线和控制线用于选择要读取或写入的存储单元。

SRAM还包括写入电路、读取电路和时钟控制电路等。

2.2 SRAM工作原理在SRAM中,数据是以二进制形式存储。

写入操作通过将所需的位值写入存储电容来完成。

读取操作通过将控制信号应用到存储单元和读取电路上来完成。

读取操作的过程如下: 1. 选择要读取的存储单元,将其地址输入到地址线上; 2. 控制信号使存储单元的存储转换器进入放大模式,将存储电容中的电荷放大到可观测的输出电压; 3. 读取电路将放大后的信号恢复到合适的电平,供外部电路使用。

写入操作的过程如下: 1. 选择要写入的存储单元,将其地址输入到地址线上; 2. 控制信号使存储单元的存储转换器进入写入模式; 3. 将数据位的值输入到写入电路; 4. 控制信号触发写入电路将输入的值写入存储电容。

2.3 SRAM性能指标SRAM的性能指标主要包括存储体积、访问速度、功耗和稳定性。

存储体积是指存储单元和控制电路的总体积,通常以平方毫米(㎡)为单位衡量。

访问速度是指读写操作的平均时间。

它受到电路延迟、线材电容和电阻等因素的影响。

功耗是指SRAM在正常操作期间消耗的总功率,通常以毫瓦(mW)为单位衡量。

功耗由静态功耗和动态功耗组成,其中静态功耗是在存储器处于静止状态时消耗的功率,动态功耗是在读取和写入操作期间消耗的功率。

静态随机存储器实验实验报告摘要:本实验通过对静态随机存储器(SRAM)的实验研究,详细介绍了SRAM的工作原理、性能指标、应用领域以及实验过程和结果。

实验使用了仿真软件,搭建了SRAM电路,通过对不同读写操作的观察和分析,验证了SRAM的可靠性和高速性。

一、引言静态随机存储器(SRAM)是一种常用的存储器类型,被广泛应用于计算机系统和其他电子设备中。

它具有存储速度快、数据可随机访问、易于控制等优点,适用于高速缓存、寄存器堆以及其他要求高速读写和保持稳定状态的场景。

本实验旨在通过设计和搭建SRAM电路,深入理解SRAM的工作原理和性能指标,并通过实验验证SRAM的可靠性和高速性。

二、实验设备和原理1. 实验设备本实验使用了以下实验设备和工具:- 电脑- 仿真软件- SRAM电路模块2. SRAM原理SRAM是由静态触发器构成的存储器,它的存储单元是由一对交叉耦合的反相放大器构成。

每个存储单元由6个晶体管组成,分别是两个传输门、两个控制门和两个负反馈门。

传输门被用于读写操作,控制门用于对传输门的控制,负反馈门用于保持数据的稳定状态。

SRAM的读操作是通过将存储单元的控制门输入高电平,将读取数据恢复到输出端。

写操作是通过将数据线连接到存储单元的传输门,将写入数据传输到存储单元。

三、实验过程和结果1. 设计电路根据SRAM的原理和电路结构,我们设计了一个8位的SRAM 电路。

电路中包括8个存储单元和相应的读写控制线。

2. 搭建电路通过仿真软件,我们将SRAM电路搭建起来,连接好各个线路和电源。

确保电路连接正确无误。

3. 进行实验使用仿真软件中提供的读写操作指令,分别进行读操作和写操作。

观察每个存储单元的输出情况,并记录数据稳定的时间。

4. 分析实验结果根据实验结果,我们可以得出以下结论:- SRAM的读操作速度较快,可以满足高速读取的需求。

- SRAM的写操作也较快,但需要保证写入数据的稳定性和正确性。

**大学实验(实训)报告实验名称运算器、存储器所属课程计算机组成与结构所在系计算机科学与技术班级学号姓名指导老师实验日期试验静态存放器试验2.1. 试验目掌握静态存放器RAM工作特征及数据读写方法。

2.2. 试验内容给存放器00H、 01H、 02H、 03H、 04H 地址单元中分别写入数据 11H、 12H、 13H、14H、 15H, 再依次读出数据。

2.3. 试验设备TDN-CM++计算机组成原理教学试验系统一台, 排线若干。

2.4. 试验原理试验所用静态存放器由一片6116(2K×8bit)组成(位于MEM单元), 如图2-1所表示。

6116有三个控制线: CS(片选线)、 OE(读线)、 WE(写线), 其功效以下图, 当片选有效(CS=0)时, OE=0时进行读操作,WE=0时进行写操作, 本试验将CS常接地。

图2-1 SRAM 6116 引脚图因为存放器最终挂接到CPU上, 所以还需要一个读写控制逻辑, 使得CPU能控制MEM 读写, 试验中读写控制逻辑如图2-2所表示, 因为T3参与, 能够确保MEM写脉宽与T3一致, T3由时序单元TS3给出。

IOM用来选择是对 I/O还是对MEM进行读写操作, RD=1时为读, WR=1时为写。

试验原理如图2-3所表示, 存放器数据线接至数据总线, 数据总线上接有8个LED 灯显示D7…D0 内容。

地址线接至地址总线, 地址总线上接有8个LED 灯显示A7…A0内容, 地址由地址锁存器给出。

数据开关经一个三态门连至数据总线, 分时给出地址和数据。

地址寄存器为8位, 接入6116地址A7…A0, 6116高三位地址A10…A8接地, 所以其实际容量为256字节。

MRMW D7 —————D0D7 —————D0A7 —————A0OE CST3 IOMRD WE读写译码RD WR74LS27374LS245IN 单元AD7|||AD0LDARIOR IN_BA10 —A8————————————————————----—————6116图2-3 存放器试验原理图试验箱中全部单元时序都连接至时序与操作台单元, CLR 都连接至CON 单元CLR 按钮。

《计算机组成原理》实验报告学院:计算机学院专业:交通工程班级学号:AP0804114学生姓名:黄佳佳实验日期:2010.11.30指导老师:李鹤喜成绩评定:五邑大学信息学院计算机组成原理实验室存储器读写实验一、实验目的:掌握半导体静态随机存储器RAM的特性和使用方法。

掌握地址和数据在计算机总线的传送关系。

了解运算器和存储器如何协同工作。

二、预习要求:预习半导体静态随机存储器6116的功能。

三、实验设备:EL-JY-II8型计算机组成原理实验系统一套,排线若干。

四、电路组成:电路图见图3-1,6116的管脚分配和功能见图3-2。

图3-1 存储器电路图3-2(a)6116管脚分配图3-2(b)6116功能五、实验步骤Ⅰ、单片机键盘操作方式实验注:在进行单片机键盘控制实验时,必须把K4开关置于“OFF ”状态,否则系统处于自锁状态,无法进行实验。

1. 实验连线:实验连线图如图3-4所示。

连线时应按如下方法:对于横排座,应使排线插头上的箭头面向自己插在横排座上;对于竖排座,应使排线插头上的箭头面向左边插在竖排座上。

图3-4 实验三键盘实验接线图2.写数据:拨动清零开关CLR ,使其指示灯显示状态为亮—灭—亮。

在监控指示灯滚动显示【CLASS SELECt 】时按【实验选择】键,显示【ES--_ _ 】输入03或3,按【确认】键,监控指示灯显示为【ES03】,表示准备进入实验三程序,也可按【取消】键来取消上一步操作,重新输入。

再按【确认】键,进入实验三程序, 监控指示灯显示为【CtL= - -】,输入1,表示准备对RAM 进行写数据,在输入过程中,可按【取消】键进行输入修改。

按 【确认】键,监控指示灯显示【Addr- -】,提示输入2位16进制数地址,输入“00”按【确认】键,监控指示灯显示【dAtA 】,提示输入写入存储器该地址的数据(4位16进制数),输入“3344”按【确认】键,监控指示灯显示【PULSE 】,提示输入单步,按【单步】键,完成对RAM 一条数据的输入,数据总线显示灯(绿色)显示“0011001101000100”,即数据“3344”,地址显示灯显示“0000 0000”,即地址“00”,监控指示灯重新显示【Addr- -】,提示输入第二条数据的2位十六进制的地址。

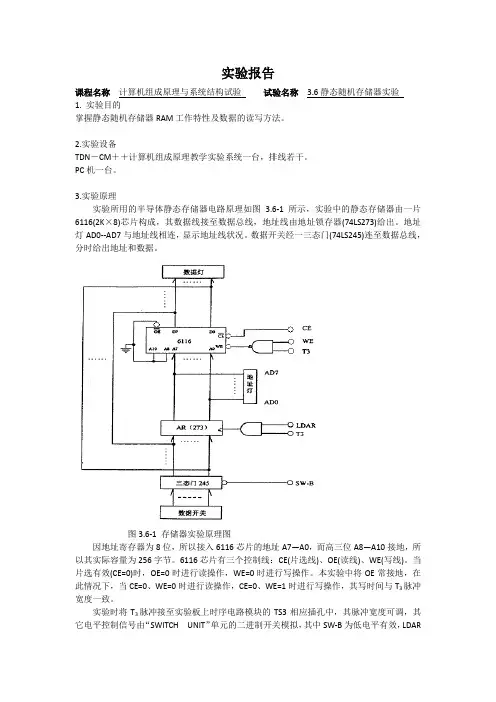

实验报告课程名称计算机组成原理与系统结构试验试验名称 3.6静态随机存储器实验1. 实验目的掌握静态随机存储器RAM工作特性及数据的读写方法。

2.实验设备TDN-CM++计算机组成原理教学实验系统一台,排线若干。

PC机一台。

3.实验原理实验所用的半导体静态存储器电路原理如图3.6-1所示,实验中的静态存储器由一片6116(2K×8)芯片构成,其数据线接至数据总线,地址线由地址锁存器(74LS273)给出。

地址灯AD0--AD7与地址线相连,显示地址线状况。

数据开关经一三态门(74LS245)连至数据总线,分时给出地址和数据。

图3.6-1 存储器实验原理图因地址寄存器为8位,所以接入6116芯片的地址A7—A0,而高三位A8—A10接地,所以其实际容量为256字节。

6116芯片有三个控制线:CE(片选线)、OE(读线)、WE(写线)。

当片选有效(CE=0)时,OE=0时进行读操作,WE=0时进行写操作。

本实验中将OE常接地,在此情况下,当CE=0、WE=0时进行读操作,CE=0、WE=1时进行写操作,其写时间与T3脉冲宽度一致。

实验时将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,其脉冲宽度可调,其它电平控制信号由“SWITCH UNIT”单元的二进制开关模拟,其中SW-B为低电平有效,LDAR为高电平有效。

4.实验步骤(1) 形成时钟脉冲信号T3。

具体接线方法和操作步骤如下:①接通电源,用示波器接入方波信号源的输出插孔H23,调节电位器W1及W2,使H23端输出实验所期望的频率和占空比的方波。

②将时序电路模块(STATE UNIT)单元中的φ和信号源单元(SIGNAL UNIT)中的H23排针相连。

③在时序电路模块中有两个二进制开关“STOP”和“STEP”。

将“STOP”开关置为“RUN”状态、“STEP”开关置为“EXEC”状态时,按动微动开关START,则TS3端输出为连续的方波信号,此时调节电位器W1,用示波器观察,使T3输出实验要求的脉冲信号。

计算机组成原理实验报告实验⼀静态随机存取存贮器实验⼀.实验⽬的了解静态随机存取存贮器的⼯作原理;掌握读写存贮器的⽅法。

⼆.实验内容实验仪的存贮器MEM单元选⽤⼀⽚静态存贮器6116(2K×8bit)存放程序和数据。

CE:⽚选信号线,低电平有效,实验仪已将该管脚接地。

OE:读信号线,低电平有效。

WE:写信号线,低电平有效。

A0..A10: 地址信号线。

I/O0..I/O7:数据信号线。

SRAM6116存贮器挂在CPU的总线上,CPU通过读写控制逻辑,控制MEM的读写。

实验中的读写控制逻辑如下图:读写控制逻辑M_nI/O⽤来选择对MEM还是I/O读写,M_nI/O = 1,选择存贮器MEM;M_nI/O = 0,选择I/O设备。

nRD = 0为读操作;nWR = 0为写操作。

对MEM、I/O的写脉冲宽度与T2⼀致;读脉冲宽度与T2+T3⼀致,T2、T3由CON单元提供。

存贮器实验原理图存贮器数据信号线与数据总线DBus相连;地址信号线与地址总线ABus相连,6116的⾼三位地址A10..A8接地,所以其实际容量为256字节。

数据总线DBus、地址总线ABus、控制总线CBus与扩展区单元相连,扩展区单元的数码管、发光⼆极管上显⽰对应的数据。

IN单元通过⼀⽚74HC245(三态门),连接到内部数据总线iDBus上,分时提供地址、数据。

MAR由锁存器(74HC574,锁存写⼊的地址数据)、三态门(74HC245、控制锁存器中的地址数据是否输出到地址总线上)、8个发光⼆极管(显⽰锁存器中的地址数据)组成。

T2、T3由CON单元提供,按⼀次CON单元的uSTEP键,时序单元发出T1信号;按⼀次uSTEP键,时序单元发出T2信号;按⼀次uSTEP键,时序单元发出T3信号;再按⼀次uSTEP键,时序单元⼜发出T1信号,……按⼀次STEP键,相当于按了三次uSTEP键,依次发出T1、T2、T3信号。

其余信号由开关区单元的拨动开关模拟给出,其中M_nI/O应为⾼(即对MEM 读写操作)电平有效,nRD、nWR、wMAR、nMAROE、IN单元的nCS、nRD 都是低电平有效。

一、实验目的1. 理解静态随机存储器(RAM)的基本原理和组成结构。

2. 掌握静态随机存储器的读写操作方法。

3. 熟悉静态随机存储器在实际应用中的功能。

二、实验原理静态随机存储器(RAM)是一种易失性存储器,它可以在正常电源供电的情况下保持数据。

RAM具有读、写速度快,功耗低,体积小等优点,广泛应用于计算机、通信、嵌入式系统等领域。

静态随机存储器主要由存储单元、地址译码器、读/写控制逻辑、数据输入/输出电路等部分组成。

存储单元是RAM的基本存储单元,通常由一个触发器组成,用于存储一个二进制位的数据。

地址译码器将地址信号转换为对应的存储单元地址,读/写控制逻辑根据控制信号完成数据的读写操作。

三、实验器材1. 静态随机存储器(RAM)芯片:6116(2Kx8bit)2. 逻辑分析仪3. 信号发生器4. 信号源5. 接线板6. 电路测试仪器四、实验内容1. 静态随机存储器芯片的引脚功能说明6116芯片的引脚功能如下:(1)A0-A10:地址线,用于选择存储单元;(2)D0-D7:数据线,用于数据的输入/输出;(3)CS:片选线,低电平有效;(4)OE:输出使能,低电平有效;(5)WE:写使能,低电平有效。

2. 静态随机存储器的读写操作(1)写操作:首先将地址信号输入到地址线A0-A10,然后将要写入的数据通过数据线D0-D7输入,将CS、OE、WE线置为低电平,即可完成写操作。

(2)读操作:首先将地址信号输入到地址线A0-A10,然后将CS、OE、WE线置为低电平,即可完成读操作。

3. 实验步骤(1)搭建实验电路:根据实验原理图,将6116芯片、逻辑分析仪、信号发生器等设备连接到实验板上。

(2)设置地址信号:通过信号发生器生成地址信号,并将其输入到6116芯片的地址线A0-A10。

(3)设置读写控制信号:将CS、OE、WE线置为低电平,表示进行读写操作。

(4)观察逻辑分析仪的波形:在逻辑分析仪上观察数据线的波形,分析读写操作的正确性。

计算机科学与技术系实验报告专业名称计算机科学与技术课程名称计算机组成与结构项目名称静态随机存储器实验班级学号姓名同组人员无实验日期 2015-10-24一、实验目的与要求掌握静态随机存储器RAM工作特性及数据的读写方法二、实验逻辑原理图与分析2.1 实验逻辑原理图及分析实验所用的静态存储器由一片6116(2K×8bit)构成(位于MEM单元),如下图所示。

6116有三个控制线:CS(片选线)、OE(读线)、WE(写线),当片选有效(CS=0)时,OE=0时进行读操作,WE=0时进行写操作,本实验将CS常接地线。

由于存储器(MEM)最终是要挂接到CPU上,所以其还需要一个读写控制逻辑,使得CPU能控制MEM的读写,实验中的读写控制逻辑如下图所示,由于T3的参与,可以保证MEM的写脉宽与T3一致,T3由时序单元的TS3给出。

IOM用来选择是对I/O还是对MEM进行读写操作,RD=1时为读,WR=1时为写。

XMRDXIORXIOWXMWRRDIOMWET3读写控制逻辑实验原理图如下如所示,存储器数据线接至数据总线,数据总线上接有8个LED灯显示D7…D0的内容。

地址线接至地址总线,地址总线上接有8个LED 灯显示A7…A0的内容,地址由地址锁存器(74LS273,位于PC&AR单元)给出。

数据开关(位于IN单元)经一个三态门(74LS245)连至数据总线,分时给出地址和数据。

地址寄存器为8位,接入6116的地址A7…A0,6116的高三位地址A10…A8接地,所以其实际容量为256字节。

实验箱中所有单元的时序都连接至操作台单元,CLR都连接至CON单元的CLR 按钮。

试验时T3由时序单元给出,其余信号由CON单元的二进制开关模拟给出,其中IOM应为低(即MEM操作),RD、WR高有效,MR和MW低有效,LDAR高有效。

三、数据通路图及分析(画出数据通路图并作出分析)分析:如果是实验箱和PC联机操作,则可通过软件中的数据通路图来观测实验结果,方法是:打开软件,选择联机软件的“实验——存储器实验”,打开存储器实验的数据通路图(如下图所示)。

图1 存储器实验原理图1静态随机存储器实验一.实验目的掌握静态随机存储器RAM 工作特性及数据的读写方法。

二.实验设备1.TDN-CM+或TDN-CM++教学实验系统一台。

2.PC 微机(或示波器)一台。

三.实验原理实验所用的半导体静态存储器电路原理如图所示,实验中的静态存储器由一片6116 (2K ×8)构成,其数据线接至数据总线,地址线由地址锁存器(74LS273)给出。

地址灯AD0~AD7与地址线相连,显示地址线内容。

数据开关经一个三态门(74LS245)连至数据总线,分时给出地址和数据。

实验四图2 静态随机存储器实验接线图2 因地址寄存器为8位,所以接入6116的地址为A7~A0,而高三位A8~A10接地,所以其实际容量为256字节。

6116有三个控制线:CE (片选线)、OE (读线)、WE (写线)。

当片选有效(CE=0)时,OE=0时进行读操作,WE=0时进行写操作。

本实验中将OE 常接地,在此情况下,当CE=0、WE=0时进行读操作,CE=0、WE=1时进行写操作,其写时间与T3脉冲宽度一致。

实验时将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,其脉冲宽度可调,其它电平控制信号由“SWITCH UNIT ”单元的二进制开关模拟,其中SW-B 为低电平有效,LDAR 为高电平有效。

四.实验步骤(1) 形成时钟脉冲信号T3。

具体接线方法和操作步骤如下:① 接通电源,用示波器接入方波信号源的输出插孔H23,调节电位器W1及W2 ,使H23端输出实验所期望的频率及占空比的方波。

② 将时序电路模块(STATE UNIT )单元中的ф和信号源单元(SIGNAL UNIT )中的H23排针相连。

③在时序电路模块中有两个二进制开关“STOP ”和“STEP ”。

将“STOP ”开关置为“RUN ”状态、“STEP ”开关置为“EXEC ”状态时,按动微动开关START ,则TS3端即输出为连续的方波信号,此时调节电位器W1,用示波器观察,使T3输出实验要 求的脉冲信号。

计算机组成原理存储器实验报告

实验名称:计算机组成原理存储器实验

实验目的:通过实验验证存储器的基本原理,掌握存储器的基本操作方法。

实验原理:

计算机系统中的存储器是计算机系统中最基本的组成部分之一,也是最重要的组成部分之一。

存储器主要是用来储存计算机程序和数据的,计算机在执行程序时需要从存储器中读取指令和数据,将结果写回存储器中。

根据存储器的类型,存储器可以分为RAM和ROM两种类型。

RAM(Random Access Memory)是一种随机读写存储器,它能够随机存取任意地址的数据。

RAM又分为静态RAM(SRAM)和动态RAM (DRAM)两种类型。

其中,静态RAM(SRAM)是使用闪存电路实现的,其速度快、性能优异,但成本相对较高;而动态RAM(DRAM)是使用电容储存信息的,价格相对较低,但性能相对较差。

ROM(Read Only Memory)是只读存储器,它不能被随意修改,只能被读取。

ROM主要用来存储程序中需要固化的数据和指令,如BIOS和系统引导程序等。

实验步骤:

1. 打开计算机,将存储器连接到计算机主板上的插槽上。

2. 打开计算机并进入BIOS设置。

3. 在BIOS设置中进行存储器检测。

4. 在操作系统中查看存储器容量。

实验结果:

本次实验中,存储器检测结果显示正常,存储器容量为8GB,符合预期。

实验总结:

本次实验通过了解存储器的基本原理和操作方法,掌握了存储器

的检测和使用方法。

同时也深入了解了计算机系统中存储器的重要性和种类。

对于今后的计算机学习和使用将具有重要的帮助作用。

静态随机存储器实验报告静态随机存储器实验报告引言:静态随机存储器(Static Random Access Memory, SRAM)是一种常见的存储器类型,广泛应用于计算机系统中。

本实验旨在通过对SRAM的实验研究,深入了解其工作原理、特性以及性能表现。

一、实验目的本实验的目的是通过实践操作,学习SRAM的基本原理和操作方法,掌握其读写操作的过程和时序,并了解SRAM的性能指标。

二、实验器材和方法实验器材:1. SRAM芯片2. 逻辑分析仪3. 示波器4. 示教板实验方法:1. 连接SRAM芯片和逻辑分析仪,建立实验电路。

2. 在示波器上观察SRAM的读写时序,并记录相关数据。

3. 使用示教板进行SRAM的读写操作,观察并记录操作结果。

三、实验结果与分析1. SRAM的读操作通过示波器观察SRAM的读操作时序,可以发现读取数据的过程包括地址输入、读使能信号的激活以及数据输出等步骤。

读操作的时序图显示了这些步骤的顺序和时机。

根据实验数据,我们可以计算出SRAM的读取速度和稳定性。

2. SRAM的写操作写操作是将数据写入SRAM芯片中的过程。

通过示波器观察SRAM的写操作时序,可以发现写操作包括地址输入、写使能信号的激活以及数据输入等步骤。

写操作的时序图显示了这些步骤的顺序和时机。

根据实验数据,我们可以计算出SRAM的写入速度和稳定性。

3. SRAM的性能指标通过对实验数据的分析,我们可以得出SRAM的性能指标,如读写速度、稳定性和可靠性等。

这些指标对于评估SRAM芯片的质量和适用范围非常重要。

四、实验总结通过本次实验,我们深入了解了静态随机存储器的工作原理和操作方法。

通过观察和分析实验数据,我们对SRAM的性能指标有了更清晰的认识。

实验过程中,我们学习了使用逻辑分析仪和示波器等工具,提高了实验操作和数据分析的能力。

通过这次实验,我们不仅对SRAM有了更深入的了解,还培养了实验思维和动手能力。

在今后的学习和研究中,这些能力将对我们的科研工作有着重要的帮助。

第1篇一、实验背景随着计算机技术的飞速发展,存储器作为计算机系统的重要组成部分,其性能直接影响着计算机系统的整体性能。

为了深入了解存储器的原理及其在实际应用中的表现,我们进行了储存原理实验。

二、实验目的1. 理解存储器的基本概念、分类、组成及工作原理;2. 掌握存储器的读写操作过程;3. 了解不同类型存储器的优缺点;4. 分析存储器性能的影响因素。

三、实验内容1. 静态随机存储器(SRAM)实验(1)实验目的:掌握SRAM的读写操作过程,了解其优缺点。

(2)实验内容:通过实验,观察SRAM的读写过程,记录读写时序,分析读写速度。

(3)实验结果:SRAM读写速度快,但价格较高,功耗较大。

2. 动态随机存储器(DRAM)实验(1)实验目的:掌握DRAM的读写操作过程,了解其优缺点。

(2)实验内容:通过实验,观察DRAM的读写过程,记录读写时序,分析读写速度。

(3)实验结果:DRAM读写速度较SRAM慢,但价格低,功耗小。

3. 只读存储器(ROM)实验(1)实验目的:掌握ROM的读写操作过程,了解其优缺点。

(2)实验内容:通过实验,观察ROM的读写过程,记录读写时序,分析读写速度。

(3)实验结果:ROM只能读,不能写,读写速度较慢。

4. 固态硬盘(SSD)实验(1)实验目的:掌握SSD的读写操作过程,了解其优缺点。

(2)实验内容:通过实验,观察SSD的读写过程,记录读写时序,分析读写速度。

(3)实验结果:SSD读写速度快,功耗低,寿命长。

四、实验分析1. 不同类型存储器的读写速度:SRAM > SSD > DRAM > ROM。

其中,SRAM读写速度最快,但价格高、功耗大;ROM读写速度最慢,但成本较低。

2. 存储器性能的影响因素:存储器容量、读写速度、功耗、成本、可靠性等。

在实际应用中,需要根据具体需求选择合适的存储器。

3. 存储器发展趋势:随着计算机技术的不断发展,存储器性能不断提高,功耗不断降低,成本不断降低。

一、实验目的1. 掌握静态随机存储器(RAM)的工作原理和特性。

2. 熟悉静态RAM的读写操作方法。

3. 了解静态RAM在计算机系统中的应用。

二、实验原理静态随机存储器(RAM)是一种易失性存储器,它可以在断电后保持数据。

与动态RAM(DRAM)相比,静态RAM具有读写速度快、功耗低等优点。

本实验使用的静态RAM芯片为6116,其容量为2K×8位。

三、实验设备1. 实验箱2. PC机3. 6116静态RAM芯片4. 时序单元5. 读写控制逻辑电路6. 数据总线7. 地址总线8. LED灯四、实验内容1. 连接电路根据实验原理图,将6116静态RAM芯片、时序单元、读写控制逻辑电路、数据总线和地址总线连接起来。

确保所有连接正确无误。

2. 初始化在实验开始前,将6116静态RAM芯片的所有地址线、数据线和控制线初始化为高阻态。

3. 写操作(1)设置片选信号(CS)为低电平,表示选中6116静态RAM芯片。

(2)设置写使能信号(WE)为低电平,表示进行写操作。

(3)设置地址线,指定要写入数据的存储单元地址。

(4)设置数据线,将要写入的数据写入指定存储单元。

(5)等待时序单元产生的写脉冲信号(T3)完成数据写入。

4. 读操作(1)设置片选信号(CS)为低电平,表示选中6116静态RAM芯片。

(2)设置读使能信号(OE)为低电平,表示进行读操作。

(3)设置地址线,指定要读取数据的存储单元地址。

(4)等待时序单元产生的读脉冲信号(T2)完成数据读取。

(5)读取数据线上的数据,即可得到指定存储单元的数据。

5. 验证通过LED灯显示数据总线上的数据,验证读写操作是否成功。

五、实验步骤1. 按照实验原理图连接电路。

2. 初始化电路。

3. 执行写操作,将数据写入指定存储单元。

4. 执行读操作,读取指定存储单元的数据。

5. 观察LED灯显示的数据,验证读写操作是否成功。

六、实验结果与分析1. 实验过程中,通过LED灯显示的数据验证了写操作和读操作的成功执行。

实验二SRAM 静态随机存储器实验

存储器是计算机各种信息存储与交换的中心。

在程序执行过程中,所要执行的指令是从存储器中获取,运算器所需要的操作数是通过程序中的访问存储器指令从存储器中得到,运算结果在程序执行完之前又必须全部写到存储器中,各种输入输出设备也直接与存储器交换数据。

把程序和数据存储在存储器中,是冯·诺依曼型计算机的基本特征,也是计算机能够自动、连续快速工作的基础。

一、实验目的

掌握静态随机存储器RAM工作特性及数据的读写方法。

二、实验设备

PC机一台,TD-CMA实验系统一套。

三、实验原理

实验所用的静态存储器由一片6116(2K×8bit)构成(位于MEM单元),如图2-1所示。

6116有三个控制线:CS(片选线)、OE(读线)、WE(写线),其功能如表2-1所示,当片选有效(CS=0)时,OE=0时进行读操作,WE=0时进行写操作,本实验将CS常接地。

图2-1 SRAM 6116引脚图

由于存储器(MEM)最终是要挂接到CPU上,所以其还需要一个读写控制逻辑,使得CPU能控制MEM 的读写,实验中的读写控制逻辑如图2-2所示,由于T3的参与,可以保证MEM的写脉宽与T3一致,T3由时序单元的TS3给出。

IOM用来选择是对I/O还是对MEM进行读写操作,RD=1时为读,WR=1时为写。

表2-1 SRAM 6116功能表

CS WE OE功能

1 0 0 0×

1

×

1

不选择

读

写

写

XMRD

XMWR

XIOW XIOR

RD

T3WR

图2-2 读写控制逻辑

实验原理图如图2-3所示,存储器数据线接至数据总线,数据总线上接有8个LED 灯显示D7…D0的内容。

地址线接至地址总线,地址总线上接有8个LED 灯显示A7…A0的内容,地址由地址锁存器(74LS273,位于PC&AR 单元)给出。

数据开关(位于IN 单元)经一个三态门(74LS245)连至数据总线,分时给出地址和数据。

地址寄存器为8位,接入6116的地址A7…A0,6116的高三位地址A10…A8接地,所以其实际容量为256字节。

RD WR

图2-3 存储器实验原理图

实验箱中所有单元的时序都连接至时序与操作台单元,CLR 都连接至CON 单元的CLR 按钮。

实验时T3由时序单元给出,其余信号由CON 单元的二进制开关模拟给出,其中IOM 应为低(即MEM 操作),RD 、WR 高有效,MR 和MW 低有效,LDAR 高有效。

四、实验步骤

(1) 关闭实验系统电源,按图2-4连接实验电路,并检查无误,图中将用户需要连接的信号用圆圈标明。

(2) 将时序与操作台单元的开关KK1、KK3置为运行档、开关KK2置为‘单步’档。

(3) 将CON单元的IOR开关置为1(使IN单元无输出),打开电源开关,如果听到有‘嘀’报警声,说明有总线竞争现象,应立即关闭电源,重新检查接线,直到错误排除。

图2-4 实验接线图

(4) 给存储器的00H、01H、02H、03H、04H地址单元中分别写入数据11H、12H、13H、14H、15H。

由前面的存储器实验原理图(图2-3)可以看出,由于数据和地址由同一个数据开关给出,因此数据和地址要分时写入,先写地址,具体操作步骤为:先关掉存储器的读写(WR=0,RD=0),数据开关输出地址(IOR=0),然后打开地址寄存器门控信号(LDAR=1),按动ST产生T3脉冲,即将地址打入到AR中。

再写数据,具体操作步骤为:先关掉存储器的读写(WR=0,RD=0)和地址寄存器门控信号(LDAR=0),数据开关输出要写入的数据,打开输入三态门(IOR=0),然后使存储器处于写状态(WR=1,RD=0,IOM=0),按动ST产生T3

脉冲,即将数据打入到存储器中。

写存储器的流程如图2-5所示(以向00地址单元写入11H为例):

WR = 0

RD = 0

IOM = 0

IOR = 0

LDAR = 0

WR = 0

RD = 0

IOM = 0

IOR = 0

LDAR = 1

T3=

WR = 0

RD = 0

IOM = 0

IOR = 0

LDAR = 0

WR = 1

RD = 0

IOM = 0

IOR

= 0

LDAR = 0

T3=

图2-5 写存储器流程图

(5) 依次读出第00、01、02、03、

04

号单元中的内容,观察上述各单元中的内容是否与前面写入的一致。

同写操作类似,也要先给出地址,然后进行读,地址的给出和前面一样,而在进行读操作时,应先关闭IN单元的输出(IOR=1),然后使存储器处于读状态(WR=0,RD=1,IOM=0),此时数据总线上的数即为从存储器当前地址中读出的数据内容。

读存储器的流程如图2-6所示

(以从00

地址单元读出11H为例):

WR =

RD = 0

IOM = 0

IOR = 0

LDAR = 0

WR = 0

RD = 0

IOM = 0

IOR = 0

LDAR = 1

T3=

WR = 0

RD = 0

IOM = 0

IOR = 1

LDAR = 0

WR = 0

RD = 1

IOM = 0

IOR = 1

LDAR = 0

图2-6 读存储器流程图

如果实验箱和PC联机操作,则可通过软件中的数据通路图来观测实验结果(软件使用说明请看附录1),方法是:打开软件,选择联机软件的“【实验】—【存储器实验】”,打开存储器实验的数据通路图,如图2-7所示。

进行上面的手动操作,每按动一次ST按钮,数据通路图会有数据的流动,反映当前存储器所做的操作(即使是对存储器进行读,也应按动一次ST按钮,数据通路图才会有数据流动),或在软件中选择“【调试】—【单周期】”,其作用相当于将时序单元的状态开关置为‘单步’档后按动了一次ST按钮,数据通路图也会反映当前存储器所做的操作,借助于数据通路图,仔细分析SRAM的读写过程。

实验数据表。