数电实验题参考答案

- 格式:doc

- 大小:244.50 KB

- 文档页数:4

数字电子技术试卷(1)参考答案一.填空1. 1111011,7B2. 8613. 与,或,非 4. 0,1,高阻5. 真值表,逻辑图,逻辑表达式,卡诺图,波形图(时序图) 6. 波形的整形 7. 20伏8. 并行A/D ,串并行A/D ,逐次比较A/D ,双积分A/D (写出三种) 二.判断题1.× 2.√ 3.× 4.√ 5.√三.化简逻辑函数1.D B A Y +=-2.--+=D B A Y四.C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.AQ Q Qn +=-+1,A Q n =+1六.采用D 触发器,-=122Q Q D ,--=231Q Q D ,1230Q Q Q D -+=电路图略。

将非工作状态101,110,111带入方程得次态,101→001,110→101→001, 111→001,电路可以自启动。

七.f =65Hz数字电子技术(2)参考答案 一.填空题(16)1. 100011.110,23.C 2. 0,13. 当前输入,原状态4. 0,1,高阻;任何时候,只能有1个三态门被选通。

5. 有两个稳态,在触发信号作用下状态可相互转变,有记忆功能 6. 延时 7. 5.5v 8. 13二.判断题(10)1.√ 2.× 3.×4.√ 5.√三.化简题(14)1. B Y =2. -++=D A C B Y 四.(15)CD A B A Y --+= 五.(15)--+=B A Qn 11, Q B Q A Qn ---++=21六.(15)驱动方程:1,121=⊕=-K Q X J ,1,212=⊕=K Q X J逻辑功能:X=0时,同步三进制计数器;X =1时,同步三进制减法计数器。

该电路为同步三进制可逆计数器,并且能自启动。

七.(15)数字电子答案3 一.填空题(16)1. 1010110,100001102. 7 3. 16,64. 状态转换表,状态转换图,特性方程5. 06. 256×4bit 7. 5.275伏8. 转换精度,转换速度二.回答问题(10)1. 不正确。

实验一、常用电子仪器的使用一、实验目的1、学习电子技术实验中常用电子仪器的主要技术指标、性能和正确使用方法。

2、初步掌握用示波器观察正弦信号波形和读取波形参数的方法。

电路实验箱的结构、基本功能和使用方法。

二、实验原理在模拟电子电路实验中,要对各种电子仪器进行综合使用,可按照信号流向,以接线简捷,调节顺手,观察与读数方便等原则进行合理布局。

接线时应注意,为防止外界干扰,各仪器的公共接地端应连接在一起,称共地。

1.信号发生器信号发生器可以根据需要输出正弦波、方波、三角波三种信号波形。

输出信号电压频率可以通过频率分挡开关、频率粗调和细调旋钮进行调节。

输出信号电压幅度可由输出幅度调节旋钮进行连续调节。

操作要领:1)按下电源开关。

2)根据需要选定一个波形输出开关按下。

3)根据所需频率,选择频率范围(选定一个频率分挡开关按下)、分别调节频率粗调和细调旋钮,在频率显示屏上显示所需频率即可。

4)调节幅度调节旋钮,用交流毫伏表测出所需信号电压值。

注意:信号发生器的输出端不允许短路。

2.交流毫伏表交流毫伏表只能在其工作频率范围内,用来测量300伏以下正弦交流电压的有效值。

操作要领:1)为了防止过载损坏仪表,在开机前和测量前(即在输入端开路情况下)应先将量程开关置于较大量程处,待输入端接入电路开始测量时,再逐档减小量程到适当位置。

2)读数:当量程开关旋到左边首位数为“1”的任一挡位时,应读取0~10标度尺上的示数。

当量程开关旋到左边首位数为“3”的任一挡位时,应读取0~3标度尺上的示数。

3)仪表使用完后,先将量程开关置于较大量程位置后,才能拆线或关机。

3.双踪示波器示波器是用来观察和测量信号的波形及参数的设备。

双踪示波器可以同时对两个输入信号进行观测和比较。

操作要领:1)时基线位置的调节开机数秒钟后,适当调节垂直(↑↓)和水平(←→)位移旋钮,将时基线移至适当的位置。

2)清晰度的调节适当调节亮度和聚焦旋钮,使时基线越细越好(亮度不能太亮,一般能看清楚即可)。

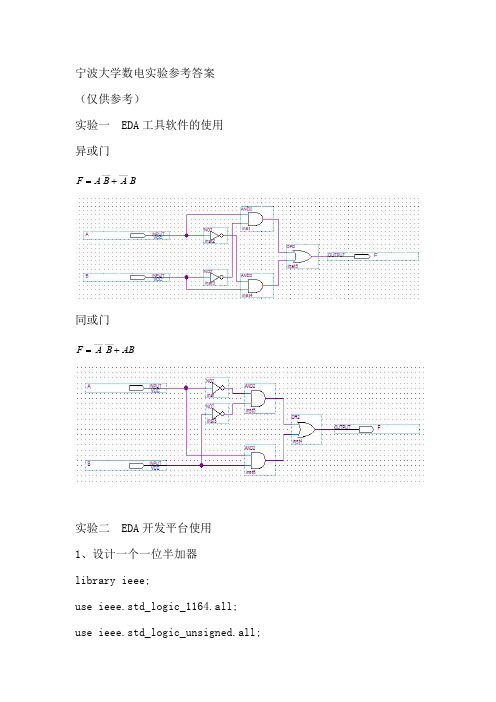

宁波大学数电实验参考答案(仅供参考)实验一EDA 工具软件的使用异或门B A B A F ______+=同或门AB B A F +=______实验二EDA 开发平台使用1、设计一个一位半加器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity banjia isport(a,b:in std_logic;s,c:out std_logic);end banjia;architecture behav of banjia is begins<=a xor b;c<=a and b;end behav;2、二进制全加器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fadder isport(a:in std_logic;b:in std_logic;c:in std_logic;s:out std_logic;d:out std_logic);end fadder;architecture behav of fadder isbegins<=a xor b xor c;d<=(a and b)or(a and c)or(b and c);end behav;实验五MSI组合电路的HDL设计1、3—8译码器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity decoder38isport(x:in std_logic_vector(2downto0);y:out std_logic_vector(7downto0) );end decoder38;architecture behav of decoder38isbeginprocess(x)begincase x iswhen"000"=>y<="00000001"; when"001"=>y<="00000010"; when"010"=>y<="00000100"; when"011"=>y<="00001000"; when"100"=>y<="00010000"; when"101"=>y<="00100000"; when"110"=>y<="01000000"; when"111"=>y<="10000000";when others=>null;end case;end process;end behav;2、显示译码器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity xianshi isport(a:in std_logic_vector(3downto0);b:out std_logic_vector(6downto0) );end xianshi;architecture behav of xianshi isbeginprocess(a)begincase a iswhen"0000"=>b<="0111111";when"0001"=>b<="0000110";when"0010"=>b<="1011011";when"0011"=>b<="1001111";when"0100"=>b<="1100110"; when"0101"=>b<="1101101"; when"0110"=>b<="1111101"; when"0111"=>b<="0000111"; when"1000"=>b<="1111111"; when"1001"=>b<="1101111"; when"1010"=>b<="1110111"; when"1011"=>b<="1111100"; when"1100"=>b<="0111001"; when"1101"=>b<="1011110"; when"1110"=>b<="1111001"; when"1111"=>b<="1110001";when others=>null;end case;end process;end behav;3、数据选择器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity select41isport(x:in std_logic_vector(1downto0);a:in std_logic;b:in std_logic;c:in std_logic;d:in std_logic;y:out std_logic);end select41;architecture behav of select41isbeginprocess(x)begincase x iswhen"00"=>y<=a;when"01"=>y<=b;when"10"=>y<=c;when"11"=>y<=d;when others=>null;end case;end process;end behav;实验六用MSI设计组合逻辑电路1、输血血型验证2、单“1”检测器实验七集成触发器及使用1、用触发器设计四位异步计数器2、用触发器设计四位移位寄存器实验八时序电路的HDL设计1、模可变计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder isport(clk:in std_logic;E:in std_logic;--E='1'则使能G:in std_logic;--G='1'为加,'0'为减M:in std_logic_vector(1downto0);--模选择y:out std_logic_vector(3downto0)--结果);end adder;architecture behav of adder issignal q:std_logic_vector(3downto0);beginprocess(E,G,clk)beginif E='0'thenq<=(others=>'0');elsif clk'event and clk='1'thenif G='1'thenif M="00"thenif q<"0001"thenq<=q+1;else q<=(others=>'0');end if;elsif M="01"thenif q<"0111"thenq<=q+1;else q<=(others=>'0');end if;elsif M="10"thenif q<"1001"thenq<=q+1;else q<=(others=>'0');end if;elsif M="11"thenq<=q+1;end if;elsif G='0'thenif M="00"thenif q>"1110"thenq<=q-1;elsif q="0000"thenq<="1111";else q<="1111";end if;elsif M="01"thenif q>"1000"thenq<=q-1;elsif q="0000"thenq<="1111";else q<="1111";end if;elsif M="10"thenif q>"0110"thenq<=q-1;elsif q="0000"thenq<="1111";else q<="1111";end if;else q<=q-1;end if;end if;end if;end process;y<=q;end behav;2、移位寄存器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity shiftreg isport(clk:in std_logic;clr:in std_logic;load:in std_logic;fx:in std_logic;--fx='1'则左移,'0'右移M:in std_logic_vector(3downto0);y:out std_logic_vector(3downto0) );end shiftreg;architecture behav of shiftreg issignal q:std_logic_vector(3downto0);beginprocess(clk,clr,load)beginif clr='1'thenq<=(others=>'0');elsif clk'event and clk='1'thenif load='1'thenq<=M;elsif fx='1'thenq(3downto1)<=q(2downto0);q(0)<='0';elsif fx='0'thenq(2downto0)<=q(3downto1);q(3)<='0';end if;end if;end process;y<=q;end behav;实验十综合时序电路设计1、序列发生器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fangfa1isport(clk:in std_logic;y:out std_logic_vector(7downto0)--结果);end fangfa1;architecture behav of fangfa1issignal q:std_logic_vector(2downto0);beginprocess(clk)beginif clk'event and clk='1'thenq<=q+1;end if;end process;begincase q iswhen"000"=>y<="00000001";when"001"=>y<="00000010";when"010"=>y<="00000100";when"011"=>y<="00001000";when"100"=>y<="00010000";when"101"=>y<="00100000";when"110"=>y<="01000000";when"111"=>y<="10000000";end case;end process;end beha或2、序列检测器use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity jiance2isport(clk:in std_logic;din:in std_logic;--串行输入数据clr:in std_logic;--复位信号result:out std_logic--检测结果);end jiance2;architecture behav of jiance2issignal d:std_logic_vector(3downto0);signal y:std_logic_vector(3downto0);signal c:std_logic;begind<="1101";process(clr,clk,din)--序列移位存储beginif clr='1'or c='1'theny<="0000";else if clk'event and clk='1'theny<=y(2downto0)&din;else null;end if;end if;end process;process(clk,y)--比较序列beginif clk'event and clk='0'then--同步时钟,去除毛刺if y=d thenresult<='1';c<='1';else result<='0';c<='0';end if;else null;end if;end process;end behav;实验十一多功能数字中的设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fen isport(clk:in std_logic;load:in std_logic;sw_set:in std_logic_vector(2downto0);gw_set:in std_logic_vector(3downto0);Qa:out std_logic_vector(2downto0);co:out std_logic;Qb:out std_logic_vector(3downto0));end;architecture a of fen issignal tema:std_logic_vector(2downto0);signal temb:std_logic_vector(3downto0);signal sw_setreg:std_logic_vector(2downto0);signal gw_setreg:std_logic_vector(3downto0);beginprocess(clk,load)beginif load='1'then tema<=sw_set;temb<=gw_set;co<='0';elsif(clk'event and clk='1')thenif tema="101"then--若时间达59时,则清零if temb>="1001"thentema<="000";temb<="0000";co<='1';else temb<=temb+"0001";co<='0';end if;elsif temb>="1001"thentema<=tema+"001";temb<="0000";co<='0';else temb<=temb+"0001";co<='0';end if;end if;Qa<=tema;Qb<=temb;end process;end a;ibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity hours isport(clk:in std_logic;load:in std_logic;sw_set:in std_logic_vector(1downto0);gw_set:in std_logic_vector(3downto0);Qa:out std_logic_vector(1downto0);Qb:out std_logic_vector(3downto0));end;architecture a of hours issignal tema:std_logic_vector(1downto0); signal temb:std_logic_vector(3downto0); signal sw_setreg:std_logic_vector(1downto0); signal gw_setreg:std_logic_vector(3downto0);beginprocess(clk,load)beginif load='1'then tema<=sw_set;temb<=gw_set;elsif(clk'event and clk='1')thenif tema="10"then--若时间达23时,则清零if temb>="0011"thentema<="00";temb<="0000";else temb<=temb+"01";end if;elsif temb>="1001"thentema<=tema+"01";temb<="0000";else temb<=temb+"0001";end if;end if;Qa<=tema;Qb<=temb;end process;end a;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity miao isport(clk,load:in std_logic;sw_set:in std_logic_vector(2downto0);gw_set:in std_logic_vector(3downto0);Qa:out std_logic_vector(2downto0);co:out std_logic;Qb:out std_logic_vector(3downto0));end;architecture a of miao issignal tema:std_logic_vector(2downto0); signal temb:std_logic_vector(3downto0); signal sw_setreg:std_logic_vector(2downto0); signal gw_setreg:std_logic_vector(3downto0); beginprocess(clk,load)beginif load='1'then tema<=(others=>'0');temb<=(others=>'0');elsif(clk'event and clk='1')thenif tema="101"then--若时间达59,则清零if temb>="1001"thentema<="000";temb<="0000";co<='1';else temb<=temb+"0001";co<='0';end if;elsif temb>="1001"thentema<=tema+"01";temb<="0000";co<='0';else temb<=temb+"0001";co<='0';end if;end if;Qa<=tema;Qb<=temb;end process;end a;实验十二交通信号灯的设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity traffic isport(clk1k:in std_logic;-------时钟信号(1khz)rst:in std_logic;-------紧急控制信号etime:out std_logic_vector(3downto0);sr,sg,sy:out std_logic;------南北方向红黄绿灯信号er,eg,ey:out std_logic------东西方向红黄绿灯信号);end traffic;architecture behav of traffic istype states is(sta0,sta1,sta2,sta3,sta4,sta5,sta6,sta7,sta8,sta9,sta10,sta11,sta12,sta13,sta1 4,sta15,sta16,sta17,sta18,sta19,sta20,sta21);signal current_state,next_state:states:=sta0;signal temp1,temp2,temp3:std_logic_vector(7downto0);signal temp4,temp5:std_logic_vector(9downto0);signal flag1,flag2,flag3,flag4:std_logic;--分别用于指示绿灯亮、绿灯闪烁、黄灯闪烁、分频signal etimereg:std_logic_vector(3downto0);signal end1,end2,end3:std_logic;signal clk:std_logic;--分频后得到的1hz时钟beginprocess(clk1k,rst)beginif rst='1'thencurrent_state<=sta0;elsif clk1k'event and clk1k='1'thencurrent_state<=next_state;end if;end process;process(current_state)begincase current_state is---------------sta0为初始状态-----------------------when sta0=>er<='1';eg<='0';ey<='0';sr<='1';sg<='0';sy<='0';flag1<='0';flag2<='0';flag3<='0';flag4<='0';etime<="1111";--stiem<="00000000";next_state<=sta1;---------------sta1为状态1:东西路口的绿灯亮,南北路口的红灯亮,持续10秒-----------------------when sta1=>er<='0';eg<='1';ey<='0';sr<='1';sg<='0';sy<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;flag1<='1';if end1='1'thennext_state<=sta2;else next_state<=sta1;end if;---------------sta2-sta6为状态2:东西路口的绿灯闪烁,南北路口的红灯亮-----------------------when sta2=>er<='0';eg<='0';--绿灯灭ey<='0';sr<='1';sg<='0';sy<='0';flag2<='1';flag1<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;if end2='1'thennext_state<=sta3;else next_state<=sta2;end if;when sta3=>er<='0';eg<='0';ey<='0';sr<='1';sg<='0';sy<='0';flag2<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;next_state<=sta4; when sta4=>er<='0';eg<='1';--绿灯亮ey<='0';sr<='1';sg<='0';sy<='0';flag2<='1';flag4<='1';etime<=etimereg;--stime<=stimereg;if end2='1'thennext_state<=sta5;else next_state<=sta4;end if;when sta5=>er<='0';eg<='1';ey<='0';sr<='1';sg<='0';sy<='0';flag2<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;next_state<=sta6;when sta6=>er<='0';eg<='0';--绿灯灭ey<='0';sr<='1';sg<='0';sy<='0';flag2<='1';flag4<='1';etime<=etimereg;--stime<=stimereg;if end2='1'thennext_state<=sta7;else next_state<=sta6;end if;---------------sta7-sta9为状态3:东西路口的黄灯闪烁,南北路口的红灯亮-----------------------when sta7=>er<='0';eg<='0';ey<='1';--黄灯亮sr<='1';sg<='0';sy<='0';flag2<='0';flag3<='1';flag4<='1';etime<=etimereg;--stime<=stimereg;if end3='1'thennext_state<=sta8;else next_state<=sta7;end if;when sta8=>er<='0';eg<='0';ey<='1';sr<='1';sg<='0';sy<='0';flag3<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;next_state<=sta9;when sta9=>er<='0';eg<='0';ey<='0';--黄灯灭sr<='1';sg<='0';sy<='0';flag3<='1';flag4<='1';etime<=etimereg;--stime<=stimereg;if end3='1'thennext_state<=sta10;else next_state<=sta9;end if;when sta10=>er<='0';eg<='0';ey<='0';--过渡状态sr<='1';sg<='0';sy<='0';flag3<='0';flag4<='0';etime<=etimereg;--stime<=stimereg;next_state<=sta11;when sta11=>er<='1';eg<='0';ey<='0';sr<='0';sg<='1';sy<='0';flag1<='0';flag2<='0';flag3<='0';flag4<='0';etime<="1111";--stiem<="00000000";next_state<=sta12;---------------东西路口红灯亮,同时南北路口的绿灯亮,南北方向开始通车----------------------when sta12=>er<='1';eg<='0';ey<='0';sr<='0';sg<='1';sy<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;flag1<='1';if end1='1'thennext_state<=sta13;else next_state<=sta12;end if;---------------sta2-sta6为状态2:南北路口的绿灯闪烁,东西路口的红灯亮-----------------------when sta13=>er<='1';eg<='0';--绿灯灭ey<='0';sr<='0';sg<='0';sy<='0';flag2<='1';flag1<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;if end2='1'thennext_state<=sta14;else next_state<=sta13;end if;when sta14=>er<='1';eg<='0';ey<='0';sr<='0';sg<='0';sy<='0';flag2<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;next_state<=sta15;when sta15=>er<='1';eg<='0';--绿灯亮ey<='0';sr<='0';sg<='1';sy<='0';flag2<='1';flag4<='1';etime<=etimereg;--stime<=stimereg;if end2='1'thennext_state<=sta16;else next_state<=sta15;end if;when sta16=>er<='1';eg<='0';ey<='0';sr<='0';sg<='1';sy<='0';flag2<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;next_state<=sta17;when sta17=>er<='1';eg<='0';--绿灯灭ey<='0';sr<='0';sg<='0';sy<='0';flag2<='1';flag4<='1';etime<=etimereg;--stime<=stimereg;if end2='1'thennext_state<=sta18;else next_state<=sta17;end if;---------------sta7-sta9为状态3:东西路口的黄灯闪烁,南北路口的红灯亮-----------------------when sta18=>er<='1';eg<='0';ey<='0';--黄灯亮sr<='0';sg<='0';sy<='1';flag2<='0';flag3<='1';flag4<='1';etime<=etimereg;--stime<=stimereg;if end3='1'thennext_state<=sta19;else next_state<=sta18;end if;when sta19=>er<='1';eg<='0';ey<='0';sr<='0';sg<='0';sy<='1';flag3<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;next_state<=sta20;when sta20=>er<='1';eg<='0';ey<='0';--黄灯灭sr<='0';sg<='0';sy<='0';flag3<='1';flag4<='1';etime<=etimereg;--stime<=stimereg;if end3='1'thennext_state<=sta21;else next_state<=sta20;end if;when sta21=>er<='1';eg<='0';ey<='0';--sr<='0';sg<='0';sy<='0';flag3<='0';flag4<='1';etime<=etimereg;--stime<=stimereg;next_state<=sta0; when others=>next_state<=sta0;end case;end process;process(flag1,clk)beginif flag1='0'thentemp1<="00000000";end1<='0';elsif clk'event and clk='0'thenif temp1>="00001001"thenend1<='1';else temp1<=temp1+"00000001";end1<='0';end if;end if;end process;process(flag2,clk)beginif flag2='0'thenend2<='0';elsif clk'event and clk='0'thenend2<='1';end if;end process;process(flag3,clk)beginif flag3='0'thenend3<='0';elsif clk'event and clk='0'then end3<='1';end if;end process;process(flag4,clk)beginif flag4='0'thenetimereg<="1111";elsif clk'event and clk='1'then etimereg<=etimereg-1; end if;end process;process(clk1k)beginif clk1k'event and clk1k='1'thenif temp4>="1111101000"thenclk<='1';temp4<=(others=>'0');else temp4<=temp4+"0000000001";clk<='0';end if;end if;end process;end behav;。

题1.1 完成下面的数值转换:(1)将二进制数转换成等效的十进制数、八进制数、十六进制数。

①(0011101)2②(11011.110)2③(110110111)2解:①(0011101)2 =1×24+ 1×23+ 1×22+ 1×20=(29)10(0011101)2 =(0 011 101)2= (35)8(0011101)2 =(0001 1101)2= (1D)16②(27.75)10,(33.6)8,(1B.C)16;③(439)10,(667)8,(1B7)16;(2)将十进制数转换成等效的二进制数(小数点后取4位)、八进制数及十六进制数。

①(89)②(1800)10③(23.45)1010解得到:①(1011001)2,(131)8,(59)16;②(11100001000) 2,(3410) 8,(708) 16③(10111.0111) 2,(27.31) 8,(17.7) 16;(3)求出下列各式的值。

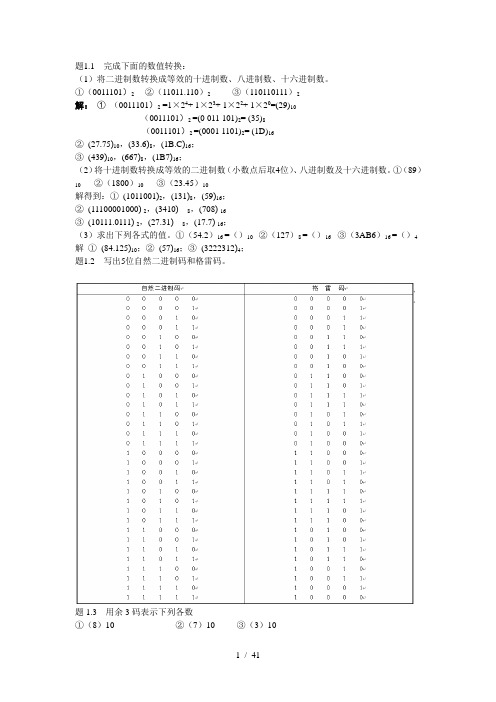

①(54.2)16=()10 ②(127)8=()16 ③(3AB6)16=()4解①(84.125)10;②(57)16;③(3222312)4;题1.2 写出5位自然二进制码和格雷码。

题1.3 用余3码表示下列各数①(8)10 ②(7)10 ③(3)10解(1)1011;(2)1010;(3)0110题1.4 直接写出下面函数的对偶函数和反函数。

()()Y AB C D E C'=++()()Y AB A C C D E ''=+++ (())Y A B C D E '''=++++()Y A B C A B C '''=++解(1)(())(())(2)()(())()(())(3)(())(())(4)D D D D Y A B C D E C Y A B C D E C Y A B A C C D E Y A B AC C D E Y A BC DE Y A B C D E Y ABC A B C Y A B C A B C'''''''=+++=+++''''''''=+++=+++''''''''''=='''''''=+++=+++,,,,题1.5 证明下面的恒等式相等 ()()()()()()()()AB C B ABC A BC ABC AB B A B A BBC AD A B B D A C C D A C B D B D AB BC ''+=++''++=++=++++'''+++=+1、(AB+C)B=AB+BC=AB ( C+C')+ ( A+A')BC=ABC +ABC'+ABC + A'BC= ABC+ABC'+ A'BC 2、AB'+B+A'B=A+B+A'B=A+B+B=A+B3、左=BC+AD , 对偶式为(B+C)(A+D)=AB+AC+BD+CD 右=(A+B)(B+D) (A+C)(C+D),对偶式为: AB+AC+BD+CD 对偶式相等,推得左=右。

数字电子技术实验报告实验一门电路逻辑功能及测试 (1)实验二数据选择器与应用 (4)实验三触发器及其应用 (8)实验四计数器及其应用 (11)实验五数码管显示控制电路设计 (17)实验六交通信号控制电路 (19)实验七汽车尾灯电路设计 (25)班级:08030801学号:2008301787 2008301949姓名:纪敏于潇实验一门电路逻辑功能及测试一、实验目的:1.加深了解TTL逻辑门电路的参数意义。

2.掌握各种TTL门电路的逻辑功能。

3.掌握验证逻辑门电路功能的方法。

4.掌握空闲输入端的处理方法。

二、实验设备:THD—4数字电路实验箱,数字双踪示波器,函数信号发射器,74LS00二输入端四与非门,导线若干。

三、实验步骤及内容:1.测试门电路逻辑功能。

选用双四输入与非门74LS00一只,按图接线,将输入电平按表置位,测输出电平用与非门实现与逻辑、或逻辑和异或逻辑。

用74LS00实现与逻辑。

用74LS00实现或逻辑。

用74LS00实现异或逻辑。

2.按实验要求画出逻辑图,记录实验结果。

3.实验数据与结果将74LS00二输入端输入信号分别设为信号A 、B用74LS00实现与逻辑1A B A B =∙逻辑电路如下: 12374LS00AN45674LS00ANA BA 端输入TTL 门信号,B 端输入高电平,输出波形如下:A 端输入TTL 门信号,B 端输入低电平,输出波形如下:1、 用74LS00实现或逻辑11A B A B A B +=∙=∙∙∙逻辑电路如下12374LS00AN45674LS00AN910874LS00ANcU1A BA 端输入TTL 门信号,B 端输入高电平,输出波形如下:A 端输入TTL 门信号,B 端输入低电平,输出波形如下:2、用74LS00实现异或逻辑⊕=+=∙=∙A B AB BA AB BA ABB ABA逻辑电路如下:A端输入TTL门信号,B端输入高电平,输出波形如下:A端输入TTL门信号,B端输入低电平,输出波形如下:实验二数据选择器及其应用一、实验目的1.通过实验的方法学习数据选择器的电路结构和特点。

《数字电子技术实践》练习题参考答案说明:本参考答案并不是唯一答案或不一定是最好答案,仅供参考。

单元 1 数字电路基础知识 边学边练1.11、 (1)12位,每位数需要一个4位BCD 码。

(2)0001 0100 01112、(1)最大为FFFH ;最小为000H 。

(2)为4096。

3、(1) 5(2) 000C7H (3) 000F9H 边学边练1.2指示灯用L 表示,亮为1,不亮为0;驾驶员到位与否用D 表示,到位为1,不到位为0;安全带扣环用B 表示,扣上为1,未扣为0;点火开关用S 表示,闭合为1,断开为0。

逻辑表达式:S B D L真值表综合练习1、 C B A D B A C B A F ⋅⋅+⋅⋅+⋅⋅=2、DC BD A H D C B A D C B A D C B A D C B A G DC B AD C A B A F DC B A E ⋅⋅+⋅=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=⋅⋅⋅+⋅⋅+⋅=⋅⋅⋅=3、设逻辑变量A 、B 、C 、D 分别表示占有40%、30%、20%、10%股份的四个股东,各变量取值为1表示该股东投赞成票;F 表示表决结果,F =1表示表决通过。

F =AB +AC +BCD4、设A 、B 开关接至上方为1,接至下方为0;F 灯亮为1,灯灭为0。

F =A ⊙B5、设10kW 、15kW 、25kW 三台用电设备分别为A 、B 、C ,设15kW 和25kW 两台发电机组分别为Y 和Z ,且均用“0”表示不工作,用“1”表示工作。

CAB Z B A B A Y ⋅=⋅=6、 真值表逻辑函数式为:F =A +BD +BC7、输入为余3码,用A 、B 、C 、D 表示,输出为8421BCD 码,用Y 0、Y 1、Y 2、Y 3表示。

DC A B A Y C BD C B D B Y DC Y DY ⋅⋅+⋅=⋅+⋅⋅+⋅=⊕==32108、设红、绿、黄灯分别用A 、B 、C 表示,灯亮时为1,灯灭时为0;输出用F 表示,灯正常工作时为0,灯出现故障时为1。

实验一:1. 在示波器处于“内触发”、“常态”扫描方式时,若改变电压灵敏度(V/div),特别是降低它,则可能会使信号波形消失。

问若是“外触发”,是否也会影响信号波形的显示呢?解:这道题主要从以下几种情况来分析:A.示波器是“内触发”,而误打到“外触发”的情况下,如果是“自动”扫描方式,示波器有波形显示,但是不会稳定;如果是“常态”扫描方式,示波器没有波形显示;B.示波器确实是“外触发”,则要求外触发信号与被测信号的频率和相位都相关,这时波形才有可能稳定。

C.示波器在“外触发”工作时,若改变电压灵敏度,会影响波形的显示。

当扫描方式为“常态”时,如果降低它,可能会使波形消失,原因是降低了电压灵敏度的同时也降低了触发信号的电平,当触发电平降低到一定的程度,就不足以使触发器工作,触发器不工作,扫描发生器也就不能工作产生扫描电压,波形就消失了。

2.实验内容3中,如何用示波器观察CH1+CH2的波形?解:要观察CH1+CH2的波形,只要使示波器的显示方式处于“叠加”,同时保证CH1和CH2的电压灵敏度保持一致就可以了。

3.简述用示波器测量TTL高、低电平的步骤。

解:将函数发生器输出TTL波形(f=1kHz)接到示波器一个通道上;示波器扫描方式打“AU TO”;电压灵敏度选择旋钮和时基因数选择旋钮处于适当的位置(比如1V/div和0.2ms/div);微调旋钮都处于“校准”位置;把输入耦合方式打到“GND”,确定零电平线的位置,再打到“DC”,读出高低电平值。

4.对于方波和三角波,交流毫伏表的指示值是否它们的有效值?如何根据交流毫伏表的指示值求得方波或三角波的有效值?解:对于方波和三角波,交流毫伏表的指示值不是他们的有效值。

先由指示值除以1.11得到它们的平均值,然后根据平均值和有效值的关系求到有效值。

U方=U平,U三=1.15U平。

实验二1.由实验结果总结以上各门电路的逻辑关系,画出真值表、逻辑图,写出表达式。

一、判断题:请在你认为陈述正确的题目前圆括号内打“√”认为错误的打“×”(每题 1 分,共 10 分)

1.(×) CMOS 电路比 TTL 电路功耗大。

2.(√)数字示波器TDS-2002垂直灵敏度设置过高时,峰峰值测量结果带“?”。

3.(×)寄存器、计数器都属于组合电路;编码器、译码器属于时序电路。

4.(×)单稳态触发器无需外加触发脉冲就能产生周期性脉冲信号。

5.(√) EPROM 存储器属于只读存储器,当掉电后其存储的信息不会消失。

6.(×)模拟示波器具有平均值采样功能

7.(√)二进制计数器既可实现计数也可用于分频。

8. (√)同步计数器的计数速度比异步计数器快。

9. (√)数码管有共阳和共阴两种,选用要根据译码器的类型而定。

10. (√)将几个 D 触发器进行串接,前一级触发器的输出与后一级触发器的输入连接起

来,就构成了移位寄存器。

二、解答下列问题(共 20 分)

1.简述扫描测试法测量TTL与非门V TH的步骤,下图中V OH、V OL 、V T是多少伏?(8分)

答:步骤如下:

(1)在被测量门的输入端输入锯齿波,CH1接输入端信号,CH2接输出端信号;(2分)(2)调节示波器,使其工作在XY的工作模式下,并调好坐标原点;(2分)

(3)根据显示波形读出水平方向的V TH的值。

(2分)

图中V OH、V OL 、V T的值分别是4.8V、0.4V、1.3V。

(2分)

2.用数字示波器同时测量74LS161的QA QB QC QD 4路输出波形时,触发信号源应如何设置?简述操作步骤。

(7分)

答:1.应该将频率最低的QD信号接入示波器并设为触发信源,调节触发电平使波形稳定显示,在调好后,调节触发电平和扫描旋钮就不能再做调节。

(4)

2.在测量过程中QD必须保持与示波器连接,用另外的一个通道观察和测量其余信号。

(3分)

3.简述Electronic Workbench与MAX+plus II 在功能上的主要不同?下图是异或门74LS86在MAX+plus II平台上采用器件EPM7128LCS84-6的仿真波形,从逻辑功能上看,它是否正确?简要说明理由。

(6分)

答:两者主要的不同是Electronic Workbench 不能实现硬件电路功能,而MAX+plus II 可以。

(3分)

从逻辑功能上看,该波形是正确。

(3分)

理由是:由于采用器件EPM7128LCS84-6,它的延迟是6ns ,而在仿真时间栅格的大小设置为6ns ,使每个输出的状态刚好推迟一个栅格,故是正确的。

三、实验设计(70分)

用JK 触发器设计一个计数器输出4位2进制数Q4 Q3 Q2 Q1按以下规律变化:

设计一控制电路,将计数器的输出作为输入,当Q4Q3Q1Q1为1001、1010时 输出Y 为0;其余六个状态输出Y 为1,要求器件数量最少。

1.计数器、控制电路完整的理论推导,画出实验电路原理图。

(25分)

可用器材包括:四位二进制计数器74LS161一片,双 J-K 触发器74LS73两片、四2输入与非门74LS00两片;四2输入与非门CD4011一片、四2输入或非门74LS02一片、四2输入或门74LS32一片、四异或门74LS86一片。

1KHz 方波信号源一个,+5V 直流稳压电源,万用表,TDS-2002数字示波器,虚拟仪器DSO2516A 等。

2. 按照实验原理图进行接线,用TDS-2002数字示波器观察并描绘CLK 、Q4、Q3、Q2、

Q1和Y 的波形(40分)

完成此步骤后须举手要求监考老师检查并评分,经监考老师同意方可拆卸实验电路。

若未经监考老师检查就拆线的,视该项未能完成,得0分

3.波形记录及实验结果分析(5分) 解:

1、根据题意可得真值表如下:(10分)

0000 0111 1000 1011

1010

1001 1100

1101

2、列逻辑表达式并化简(10分)

4

Q n+1

=n n n n n n Q Q Q Q Q Q 142434++=n n n n n Q Q Q Q Q 424)13(++ n

n

n

n

n

n

n

n

n

n

n

n

n

n

n

n

n

n

n

n Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 3

13124133)124(13123343

1

+∙∙∙=++=++=+

n

n n n n n n n n n n n n n Q Q Q Q Q Q Q Q Q Q Q Q Q Q 21213412123242

1

+∙∙∙=++=+

n

n Q Q 11

!

=+

J4=n Q 2 K4=n n Q Q 13+ J3= n n n Q Q Q 124 K3=Q1n

J2= n n n Q Q Q 134 K2=Q1

J1=K1=1

Y=)12(3123123Q Q Q Q Q Q Q Q Q ⊕=+ 3、画原理图如下:(5分)

5、波形记录及实验结果分析(5分)

该波形图能够反映电路的功能,符合题目的设计要求。