Altera project实验报告

- 格式:doc

- 大小:1.33 MB

- 文档页数:16

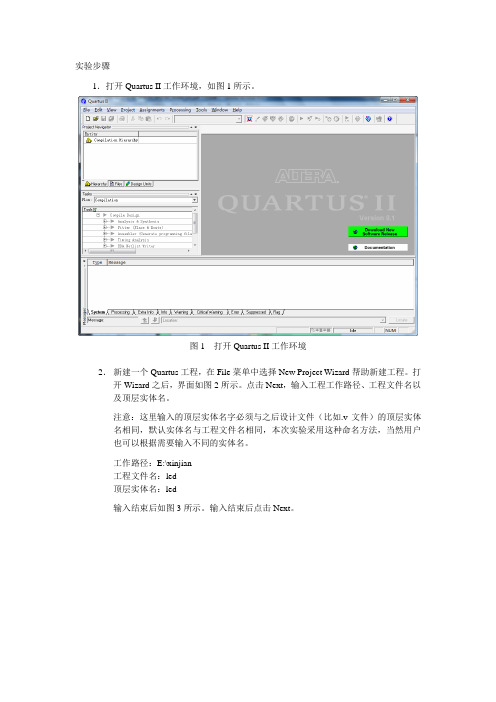

实验步骤1.打开Quartus II工作环境,如图1所示。

图1 打开Quartus II工作环境2.新建一个Quartus工程,在File菜单中选择New Project Wizard帮助新建工程。

打开Wizard之后,界面如图2所示。

点击Next,输入工程工作路径、工程文件名以及顶层实体名。

注意:这里输入的顶层实体名字必须与之后设计文件(比如.v文件)的顶层实体名相同,默认实体名与工程文件名相同,本次实验采用这种命名方法,当然用户也可以根据需要输入不同的实体名。

工作路径:E:\xinjian工程文件名:led顶层实体名:led输入结束后如图3所示。

输入结束后点击Next。

图2 New Project Wizard界面图3 输入设计工程信息3.添加设计文件,界面如图4所示。

如果用户之前已经有设计文件(比如.v文件),那么再次添加相应文件,如果没有完成的设计文件,点击Next,之后添加并且编辑设计文件。

图4 添加设计文件4.选择设计所用器件。

由于本次实验使用Altera公司提供的DE2开发板,用户必须选择与DE2开发板相对应的FPGA器件型号。

在Family菜单中选择CycloneII在Target device选项框中选择Specific device selected in ‘A vailable devices’ list 在A vailable device列表中选择EP2C35F672C6这个型号的器件。

完成后如图5所示,点击Next。

图5 选择相应器件5.设置EDA工具。

设计中可能会用到的EDA工具有综合工具、仿真工具以及时序分析工具。

在本次实验中不使用这些工具,因此点击Next直接跳过设置。

图6 设置EDA工具6.查看新建工程总结。

在基本设计完成后,Quartus II会自动生成一个总结让用户核对之前的设计(如图7所示),确认后点击Finish完成新建。

图7 新建工程总结在完成新建后,Quartus II界面中Project Navigator的Hierarchy标签栏中会出现用户正在设计的工程名以及所选用的器件型号,如图8所示。

project项目管理实验报告项目管理实验报告一、引言在现代社会中,项目管理已经成为各个行业中不可或缺的一部分。

项目管理的目标是通过有效地规划、组织、执行和控制项目活动,以实现项目的目标和交付成果。

本次实验旨在通过一个实际的项目案例,探讨项目管理的重要性和应用。

二、项目背景本次实验的项目是一个软件开发项目,旨在开发一款在线购物平台。

项目团队由开发人员、设计师和测试人员组成,总共有十人。

项目的目标是在三个月内完成开发,并成功上线。

三、项目规划在项目规划阶段,团队首先进行了需求分析和范围确定。

通过与客户的沟通和讨论,明确了平台的功能和特性,并制定了详细的项目计划。

项目计划包括了各个阶段的时间安排、资源分配和风险管理策略。

四、项目执行项目执行阶段是整个项目的核心,团队成员根据项目计划开始进行开发工作。

开发人员采用敏捷开发方法,将项目分为多个迭代周期,每个周期都有具体的任务和交付物。

团队成员之间进行了紧密的合作和沟通,确保任务按时完成。

五、项目控制项目控制是项目管理的重要环节,通过监控项目进展和控制项目变更,确保项目按计划进行。

团队使用了项目管理工具来追踪任务的进度和资源的使用情况。

同时,团队定期召开会议,讨论项目的问题和挑战,并制定相应的解决方案。

六、项目评估在项目完成后,团队进行了项目评估,对项目的整体表现进行了分析和总结。

评估包括了项目的成本、时间和质量等方面的考量。

通过评估,团队发现了项目中存在的问题和不足,并提出了改进的建议。

七、项目管理的意义通过本次实验,我们深刻认识到了项目管理的重要性和意义。

项目管理可以帮助团队有效地组织和协调各项工作,提高工作效率和质量。

同时,项目管理还可以帮助团队应对项目中的风险和挑战,确保项目的顺利进行。

八、结论通过本次实验,我们不仅学习了项目管理的理论知识,还亲身体验了项目管理的实践过程。

项目管理不仅仅是一种工具和方法,更是一种思维方式和管理能力。

只有通过不断的实践和反思,我们才能不断提升自己的项目管理能力,更好地应对各种挑战和问题。

昆明理工大学信息工程与自动化学院学生实验报告(2011 —2012 学年第 2 学期)课程名称: FPGA 开课实验室:信自楼xxx 2012年 03 月 04日年级、专业、班计科xxx 学号Xxxxxxxxx 姓名Xxx 成绩实验项目名称熟悉Altera Quarstus II 开发环境指导教师Xxxx 教师评语教师签名:年月日注:报告内容按实验须知中七点要求进行。

一、实验目的●熟悉QuartusII软件的操作环境。

●熟悉QuartusII软件开发FPGA的基本操作流程。

●可独立使用使用QuartusII软件开发新工程。

二、实验原理Quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL 以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Quartus II可以在XP、Linux以及Unix上使用,除了可以使用Tcl脚本完成设计流程外,提供了完善的用户图形界面设计方式。

具有运行速度快,界面统一,功能集中,易学易用等特点。

Quartus II支持Altera的IP核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。

对第三方EDA 工具的良好支持也使用户可以在设计流程的各个阶段使用熟悉的第三方EDA工具。

此外,Quartus II 通过和DSP Builder工具与Matlab/Simulink相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统(SOPC)开发,集系统级设计、嵌入式软件开发、可编程逻辑设计于一体,是一种综合性的开发平台。

三、实验内容本次实验通过给定的工程实例“38译码器”来熟悉Altera QuartusII软件的基本操作、设计、编译以及仿真流程。

实验二Quartus II使用入门姓名:学号:班级:日期:一、实验目的和要求1、了解Altera 公司EDA软件Qutartus II的基本设计流程2、通过对DE1的操作,初步掌握设计项目的建立,编译,适配过程3、初步认识Verilog硬件描述语言二、实验环境1、PC机,Pentium 4 2.0G以上,内存1G以上,硬盘500G以上,1024×768彩显,USB接口,网络接口,串口。

2、友晶DE1开发板和相关配件。

3、软件:Windows XP或者Windows 7操作系统,DE1配套光盘。

三、实验内容1、通过最简单工程项目了解Quartus II基本设计过程。

2、DE1开光和发光管的对应显示控制,即拨动开关,对应的LED亮或灭。

3、了解Modelsim仿真工具和Quartus II的逻辑仿真及时序仿真。

四、实验步骤1、建立Quartus 工程:1)打开Quartus II 工作环境。

2)点击菜单项File->New Project Wizard 帮助新建工程。

3)输入工程工作路径、工程文件名以及顶层实体名。

自己起名字,例如学号等。

注意:输入的顶层实体名必须与之后设计文件的顶层实体名相同,默认的顶层实体名与工程文件名相同,本类实验均采用这种命名方法以便于管理。

4)添加设计文件。

如果用户之前已经有设计文件(比如.v 文件)。

那么直接添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑新的设计文件。

5)选择设计所用器件。

由于本次实验使用 Altera 公司提供的DE1 开发板,用户必须选择与之相对应的FPGA 器件型号,如下图:6)设置 EDA 工具。

设计中可能会用到的EDA 工具有综合工具、仿真工具以及时序分析工具。

本次实验中不使用这些工具,因此点击Next 直接跳过设置。

7)查看新建工程总结。

在基本设计完成后,Quartus II 会自动生成一个总结让用户核对之前的设计,确认后点击Finish 完成新建。

用ModelSimSE进行 功能仿真和时序仿真的方法 (ALTERA篇)黄俊April 2007用ModelSim SE进行功能仿真和时序仿真的方法 (ALTERA篇)软件准备(1) QuartusII,本文截图是QuartusII 6.1界面的。

我个人认为,如果是开发StratixII或CycloneII或MAXII,用QuartusII6.0+SP1+SP2比较稳定。

(2) ModelSim SE. ALTERA仿真库要已经装好,安装仿真库的笔记已记录于《在ModelSimSE中添加ALTERA仿真库的详细步骤》中。

我电脑上装的是ModelSim SE6.1b。

例子程序的制作先在Quartus II里生成一个例子程序,以方便介绍三种仿真的方法。

步骤如下:1、新建一个工程(Project),工程名取lpm_shift, 器件选CycloneII EP2C5Q208C, 第三方的工具暂时都不选。

2、菜单栏上ToolsÆMegaWizard Plug-In Manager, 点Next,在storage中选LPM_SHIFTREG,输出文件格式根据习惯选一种语言,在这里以Verilog的为例,在右边的output file名字中加上lpm_shift。

点Next。

3、这个例子是做一个移位寄存器,调用lpm库,和cycloneII元件库,也正好可以作为对前面建好的ALTERA库的一个验证。

点可以查到该模块的使用说明和详细介绍。

移位寄存器比较简单,就不用细看了。

如下图设置.点Next.4、加上一个异步清零端,点Next,再点Next,最后点Finish.Add/Remove Files in Project…,6、点图标,选中生成的lpm_shift,点打开再点Add都加到项目中去。

7、在这里直接把lpm_shift.v当成顶层文件,就不需要再例化它了。

8、下面写一个简单的TestBench.a)Quartus II工具栏上点图标,选Verilog HDL;b)点,设文件名为top_tb;c)如下所述写一个简单的TestBench.(例子见附件)开始仿真z ModelSim仿真有很多种流程,下面我采用个人感觉比较好一个流程进行仿真验证:基于工程(Project)的流程Step1 新建一个工程Step2 添加文件到工程中去Step3 编译设计文件Step4 启动仿真器,指定顶层设计单元Step5 查看和调试结果z对的设计有三个阶段的仿真。

project项目管理实验报告项目管理可交付物项目管理软件project项目管理案例microsoftproject 篇一:project计算机项目管理实验报告计算机辅助项目管理课程报告班级:学号:姓名:指导教师:完成日期:目录一、项目基本信息1、项目简介2、项目任务关系、固定成本及资源需求量3、可用资源4.、项目管理要求二、项目初始计划1、定义项目2、定义常规工作时间3、列出项目中任务4、初始计划的内容5、初始计划的分析三、基准计划1、分配资源2、删除(替换)资源3、资源的调整4、基准计划调整5、监控6、第一轮监控7、第二轮监控8、第三轮监控9、第四轮监控10、第五轮监控四、竣工验收1、竣工验收的程序五、心得体会摘要:目前工程建设项目规模逐渐增大,渐趋复杂,业主要求采用计算机进行项目管理。

各单位市场竞争的需要、项目管理人才自身发展的需要、导致应用计算机进行项目管理的客观条件已基本成熟。

如何有效管理这些冗杂的项目信息?如何对收集的大量信息进行加工?如何将加工后的信息及时分享给组织中的每个成员?这些问题都可以用project软件解决!项目Microsoft Project 不仅可以快速、准确地创建项目计划,而且可以帮助项目经理实现项目进度、成本的控制、分析和预测,使项目工期大大缩短,资源得到有效利用,提高经济效益!本文仅以一个案例来说明该软件的部分功能!关键词:资源分配;调整;监控;一、项目基本信息1、项目简介项目的主要工作是维修某主要道路下一段长约1公里的供水管道,市政局要求电力部门配合施工,同时铺设一条地下电缆,以增加该道路两侧的用电用户。

由于该项目是在现有道路上开挖,故市政局决定在回填后顺便铺设新的混凝土路面。

为此,专门成立了一个项目管理办公室,以管理、协调该项目。

项目内容包括:供水工程、电力工程和道路工程。

整个项目从2011年7月1日提交预算报批为开始,市政局希望将项目施工对公众造成的影响降至最低,故希望该项目能在2011年10月底竣工并恢复交通。

《FPGA系统设计》实验报告》QuartusII软件入门并设计1位半加器

一、设计任务

1、熟悉ALTERA公司EDA设计工具软件QuartusII。

2、熟悉EDA实验箱。

3、学习QuartusII软件。

4、在QuartusII软件中使用原理图输入法设计并实现一个1位半加器。

二、设计过程

1、半加器的设计:电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。

是实现两个一位二进制数的加法运算电路。

2、半加器表达式:进位:co=a and b

和:so=a xnor (not b)

3、半加器原理图、如下:

图1.1 半加器原理图

1.行为描述程序

2.数据流描述程序

3.结构体描述程序

图1.2 半加器实验操作图4、真值表

表1.1 半加器真值表

5、引脚分配图

图1.3 引脚分配图

6、调试过程

将99脚和98脚接到拨码开关,87脚和86脚接发光二极管,当开关全拨至1或全拨至0不亮,反之会亮。

三、总结

通过这次实验,我学会了用VHDL语言实现半加器功能,掌握Quartus‖软件输入设计流程,本次实验我分别用实验箱上的开关K1、K2作为半加器两输入A、B;分别用LED灯LED1、LED2作为半加器的两个输出端S、C。

实验时将实验箱的拨动开关拨向下时为低电平“0”。

拨向上时为高电平“1”,LED高电平时灯亮,低电平时灯灭。

其结果均符合半加器的真值表。

2017-2018学年第二学期《Project软件应用》课程实验报告班级: 12011501学号: 2015302850姓名:张盼盼2018年6月目录一、项目目标 (2)二、项目初始创建计划 (2)三、基准计划 (4)(1) 资源调配分析 (6)(2) 资源调配结果 (7)四、跟踪调整计划 (7)1.8月底的进度监控 (7)(1)跟踪项目日程 (8)(2)跟踪项目成本 (8)(3)跟踪项目工时 (8)(4)调整方法和结果 (9)2.9月份进度监控 (9)(1)项目跟踪结果 (9)3.10月底的监控 (10)(1)项目跟踪结果 (10)4.11月底的监控 (10)五、项目实施心得体会 (11)1. 学习中的重点与困难 (11)2. 反思和感悟 (11)一、项目目标项目范围:维修某主要道路下一段长约1公里的供水管道进度目标:2018年8月1日开始,2018年11月底通过学习和运用MS Project 软件,进行项目规划、项目监控和项目调整,使得该维修供水管道项目在项目计划时间内完成,即2018年11月底完成,并控制项目成本在项目成本预算以下。

二、项目初始创建计划1.打开 MS Project 软件,由文件-新建,并保存。

2.打开文件-选项-日程,调整工作周和工作日,设置项目开始日程,为2018年8月1日;设置项目日程(包括工期和工时的显示单位,资源单位等)。

3.创建一个新的日历。

由〔项目〕菜单选取〔更改工作时间〕。

选择新建日历,改新建日历的名称;“标准”的副本(项目日历)。

由于在项目执行期间有节假日(中秋节与国庆节),在日历下方选择添加例外日期,设置开始和完成时间如图所示,并保存。

然后运用新的日历。

由〔项目〕菜单选取〔项目信息〕。

4.建立资源列表,根据项目数据可知,技工与壮工(非技工的)按工时一天8小时来计算,则技工标准费率=50(元/日)/8(小时)=6.25元/小时,壮工则为3.75元/日。

管理费标准费率也同样计算为6.25元/小时。

实验一QUARTUS II软件安装、基本界面及设计入门一、实验目的:QUARTUSII是Altera公司提供的EDA工具,是当今业界最优秀的EDA设计工具之一。

提供了一种与结构无关的设计环境,使得电子设计人员能够方便地进行设计输入、快速处理和器件编程。

通过本次实验使学生熟悉QUARTUSII软件的安装,基本界面及基本操作,并练习使用QUARTUS的图形编辑器绘制电路图。

二、实验内容:1、安装QUARTUSII软件;2、熟悉QUARTUSII基本界面及操作;3通过一个4位加法器的设计实例来熟悉采用图形输入方式进行简单逻辑设计的步骤。

三、实验仪器:1、PC机一台;2、QUARTUSII软件;3、EDA实验箱。

四、实验原理:4位加法器是一种可实现两个4位二进制数的加法操作的器件。

输入两个4位二进制的被加数A和B,以及输入进位Ci,输出为一个4位二进制和数D和输出进位数Co。

半加操作就是求两个加数A、B的和,输出本位和数S及进位数C。

全加器有3位输入,分别是加数A、B和一个进位Ci。

将这3个数相加,得出本位和数(全加和数)D和进位数Co。

全加器由两个半加器和一个或门组成。

五、实验步骤:安装QUARTUSII软件;因为实验时我的机器了已经有QUARTUSII软件,所以我并没有进行安装软件的操作。

设计半加器:在进行半加器模块逻辑设计时,采用由上至下的设计方法,在进行设计输入时,需要由下至上分级输入,使用QuartusIIGraphic Editor进行设计输入的步骤如下。

(1)、打开QUARTUSII软件,选择File-new project wizard…新建一个设计实体名为has的项目文件;(2)、新建文件,在block.bdf窗口下添加元件符号,并连接。

如下图:半加器原理图(3)、将此文件另存为has.gdf的文件。

(4)、在主菜单中选择Processing→Start Compilation命令,系统对设计进行编译,同时打开Compilation Report Flow Summary窗体,Status视图显示编译进程。

quartusii初步的实验流程总结下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!Quartus II 初步的实验流程总结1. 介绍Quartus II 是一款由 Altera 公司推出的集成电路设计软件,被广泛应用于数字逻辑电路设计和 FPGA(现场可编程门阵列)开发中。

实验报告一、分析思路实验开始前,根据案例分析要求,运用Visio 软件对project 文档编制项目计划的思路及过程进行了编绘,思路图如下:二、案例分析过程(1)新建project 文件,在文件选项卡,项目信息中设置项目标题为"笔记本开发”;保存文件,命名为"89+1306100114+李幸果”,打开项目选项卡下的项目信息,设置项目开 始时间为“ 2016年1月1 日";解读项目案例背杲>开始项目设盏录入/■修改I 页目僧息完成其他信息设置>分析进度根据根表预计 顷目完成对资源逬行调整(2)在文件选项卡的“选项”中打开project选项窗口,按照项目信息设置日程信息,设置项目每周开始于“星期一”即周一,财政年度开始于“八月”,默认开始时间为“9:00”, 默认结束时间为“ 18:00 ”如下:点击项目选项卡下的“更改项目时间”打开相应窗口,启用并编辑日历“标准” ,根据项目组规定,在“默认”的中点击“详细信息”,设置工作日工作时间为 “9:00-12:00/13:00-18:00 ” ;日历“日时 对荃淮曰历・I Sil ■■■dim!需称 1 [默认]I 帮助⑩工佗周彫卜日期 开啊■同毎宋眄间[ 确定 ] 职哨详细信息⑥…]V选项(£)...茸助迪m :i 粒非日_ 1 二 E六1A 2016年1月旧 朗工作时间:___- 00:00 至 1£ 00—17:00i r-3i ';工作时问有吏]1出姑日期|在业日历上I rai l 例外日期设剖L 工乍周的工作吋间匕将Project 默M 时间零十下列日期⑪- 0将所列日期设晝为非工作时冋@〕.O 对所列日期设豈以下特定工乍时间w:w 的軼认工作周.对于日历◎:新建日历QJ).X日历1“[默认严的洋细信息单击工作日以査看其二作吋司®2D16年1月在“例外日期”中添加(元旦、春节、劳动节、国庆节)休假时间,安排为法定节假日 放假;更改工作时间 IX对于日历C); 日历1倾目日历) 日历M 日时为基唯日历. !工作日菲工作日 i 在比日历上:r3i"i 耳蹴认工作周 :—:—二 三 四 五 AB1 2 3 4 5 67 a9 10 11 1£ 13 14 15 W 17 18 19 20 21 2223 2425 26 2T28 西 30单击工件日以查看苴工件时间®:如1&年4月新建日历逼)2016年4月21日的工祚时间;-09:00 至 1"。

《电子设计自动化》实验报告实验一实验名称:3-8译码器的设计专业及班级:姓名:学号:一、实验目的:1.掌握组合逻辑电路的设计方法。

2.掌握 VHDL 语言的基本构造及设计的输入方法。

3.掌握 VHDL 语言的基本描绘语句的使用方法。

二、实验步骤(附源代码及仿真结果图):1.成立工程, Quartus II -- project wizard (注意工程目录中不可以出现中文字符,不可以成立在桌面上);弹出窗口如图 2-3 所示。

图 2-3 New Project Wizard 窗口2.点击next,在出现的对话框中输入以下项目信息:a.项目路径,如: D:\EDA experiment\decoder38; b.项目名称,如: decoder38。

如图 2-4 所示:图 2-4 项目路径和项目名称对话框3.点击 2 次 next 后,出现如图 2-5 所示的对话框:a.Device family 中选择 Cyclone IV E;b.Available devices 中选择 EP4CE115F29C7.图 2-5器件选择窗口4.点击next后,出现EDA工具设置对话框。

在Simulation一行中, Tool Name 选择ModelSim-Altera , Fomat(s)选择 VHDL ,如图 2-6 所示。

图 2-6 EDA 工具设置对话框5.点击 next,出现如图 2-7 所示的对话框:图 2-7 新建项目汇总对话框6. 点击 Finish 后,出现如图2-8 所示的界面:图 2-8 decoder38 项目界面7.点击 File->New->VHDL File ,如图 2-9 所示。

点击 ok 封闭对话框。

图 2-9 新建 VHDL 文件窗口8.在文本编写框内键入以下程序:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY decoder38 ISPORT(A, B,C,G1,G2A,G2B: IN STD_LOGIC;Y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END decoder38;ARCHITECTURE Behavior OF decoder38 ISSIGNAL indata: STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINindata <= C&B&A;PROCESS (indata, G1, G2A,G2B)BEGINIF (G1='1' AND G2A='0' AND G2B='0') THENCASE indata ISWHEN "000"=>Y<="11111110";WHEN "001"=>Y<="11111101";WHEN "010"=>Y<="11111011";WHEN "011"=>Y<="11110111";WHEN "100"=>Y<="11101111";WHEN "101"=>Y<="11011111";WHEN "110"=>Y<="10111111";WHEN "111"=>Y<="01111111";WHEN OTHERS =>Y<="XXXXXXXX";END CASE;ELSEY<="11111111";END IF;END PROCESS;END Behavior;9. 将文件保留为decoder38.vhd 后,开始编译,点击Processing->Start Compilation ,编译成功后,出现如图2-10 所示界面:图 2-10 编译成功界面10.再次新建一个 vhdl 文件,键入以下的 modelsim 测试程序:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY decoder38_tb ISEND decoder38_tb;ARCHITECTURE Behavior OF decoder38_tb ISCOMPONENT decoder38PORT (A,B,C,G1,G2A,G2B: IN STD_LOGIC;Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT;SIGNAL A: STD_LOGIC:='0';SIGNAL B : STD_LOGIC:='0';SIGNAL C: STD_LOGIC:='0';SIGNAL G1: STD_LOGIC:='1';SIGNAL G2A: STD_LOGIC:='0';SIGNAL G2B: STD_LOGIC:='0';SIGNAL Y: STD_LOGIC_VECTOR(7 DOWNTO 0);CONSTANT CLK_PERIOD: TIME:=10ns;BEGINA<=not A after CLK_PERIOD;B<=not B after 20ns;C<=not C after 40ns;U1: decoder38 port map(A=>A,B=>B,C=>C,G1=>G1,G2A=>G2A,G2B=>G2B,Y=>Y);END behavior;11.将文件保留为 decoder38_tb.vhd ,编译经过。

CPLD/FPGA 应用开发技术实验报告学生姓名: 张齐昌 学 号: 201410204065 学 院: 信息工程学院 班 级: 通信14-2 指导教师: 荀延龙2017年 4 月 16日实验一组合逻辑电路的设计一、实验目的:1、掌握用VHDL语言和EPLD进行组合逻辑电路的设计方法。

2、加深对EPLD设计全过程的理解。

3、掌握组合逻辑电路的静态测试方法。

二、实验设备:1、PC机2、EDA实验箱(主芯片是ALTERA公司EP1K100QC208-3 或EP1K30TC30144-3)。

三、实验内容(任意选做3个):1、用VHDL语言输入法设计一个四舍五入判别电路,其输入为8421BCD码,要求当输入大于或等于5时,判别电路输出为1;反之为0。

2、用VHDL语言输入法设计3个开关控制一盏灯的逻辑电路,要求当开关都断开时,灯灭;任一开关闭合或断开,灯的状态变换一次。

3、用VHDL语言输入法设计一个4选1数据选择器,信号A、B、D3、D2、D1、D0、Y、S。

要求S=“0”时,根据A、B的状态m i选择输出端Y=D i。

4、用VHDL语言输入法设计一个3线-8线译码器,信号A、B、C、Y7、Y6、Y5、Y4、Y3、Y2、Y1、Y0、S。

要求S=“0”时,根据A、B、C的状态m i选择输出端Y i=“0”。

四、实验步骤:1、采用文本编辑器输入VHDL语言源程序,建立工程。

2、编译。

3、仿真。

4、对芯片进行编程。

5、根据管脚分配情况连线。

(1)四舍五入判别电路的四个输入管脚分别与四个拨码开关相连,输出数据与LED灯相连。

(2)开关控制电路的3个输入管脚分别与3个按键开关相连,输出管脚与LED 灯相连。

(3)4选1数据选择器的7个信号A、B、D3、D2、D1、D0、S分别连7个拨码开关,输出信号Y与LED灯相连。

(4)3线-8线译码器4个信号A、B、C、S分别连4个拨码开关,输出信号Y i 与8个LED灯相连。

实验报告一、分析思路实验开始前,根据案例分析要求,运用Visio软件对project文档编制项目计划的思路及过程进行了编绘,思路图如下:二、案例分析过程(1)新建project文件,在文件选项卡,项目信息中设置项目标题为“笔记本开发”;保存文件,命名为“李幸果”,打开项目选项卡下的项目信息,设置项目开始时间为“2016年1月1日”;(2)在文件选项卡的“选项”中打开project选项窗口,按照项目信息设置日程信息,设置项目每周开始于“星期一”即周一,财政年度开始于“八月”,默认开始时间为“9:00”,默认结束时间为“18:00”如下:点击项目选项卡下的“更改项目时间”打开相应窗口,启用并编辑日历“标准”,根据项目组规定,在“默认”的中点击“详细信息”,设置工作日工作时间为“9:00-12:00/13:00-18:00”;在“例外日期”中添加(元旦、春节、劳动节、国庆节)休假时间,安排为法定节假日放假;录入项目信息,分别设置项目之间的关系以及前置任务;录入资源信息,按照资源信息表分配各个任务资源;(3)查看项目的初步计划:打开甘特图视图,初步查看项目的计划情况;(4)检查项目的进度、成本和资源情况:①“工期”——形成项目初步计划后,我发现项目的工期与任务信息表不符,项目完成时间为2019年2月19日,超过了项目计划的计划时间2018年12月31日;调整方法:A.方法一:部分任务的工作日过长,对工期进行缩减:将任务“评估生产过程的稳定性和成本效益”原来的工期30日缩减至“20日”(如下图),操作过后项目结束时间提前到了“2019年2月5日”,有效缩短工期;B.方法二:改变部分工作的链接关系,经过分析,我认为下图中三项任务中的“开始商业产量生产”和“监控用户接受程度试验”可以同时进行,可取消二者之间的前置任务关系,选中两项任务点击“日程”分栏中的“取消链接任务”,然后将任务90“监控用户接受程度试验”的前置任务设为与任务89“开始商业产量生产”相同的88;操作后项目的结束时间提前至2019年1月29日;C.反复经过以上两种方式的调节后(具体如下图),最终可将项目的结束时间控制到了2018年12月28日,在计划范围内;②“成本”——在“表格”下拉栏中选择打开“成本”视图查看项目成本情况:如下如所示,“笔记本开发”项目总成本1086160元(108.616万元),超过了项目总预算成本108万元;调整方法:A.在调节过度分配资源的过程中考虑了以成本较低的资源替换了过度分配且成本较高的资源,最终总成本也得到了有效控制,如下图,在资源分配完成后,项目总成本降到了1,070,160元,在项目预算成本的范围内;B.经过工期的调节后,成本进一步缩减,见下图:③“资源”——在“资源使用情况”视图中可以看到资源“设计师”、“市场经理”、“项目经理”分配过度,通过“资源表格”中可以在“过度分配的资源”中查看资源分配过度情况。

project项目管理实验报告《项目管理实验报告》项目管理是现代企业管理中非常重要的一环,通过科学的项目管理方法可以提高项目的执行效率,降低成本,提高项目成功的概率。

本实验报告旨在探讨项目管理的重要性,并通过实际案例分析展示项目管理的实际应用效果。

一、项目管理的重要性项目管理是一种系统的管理方法,通过规划、组织、指挥、协调和控制来实现项目的目标。

在当今竞争激烈的商业环境中,项目管理的重要性不言而喻。

良好的项目管理可以帮助企业提高效率,降低成本,提高客户满意度,提高企业的竞争力。

二、实验案例分析在实验中,我们选择了一个实际的项目案例进行分析。

该项目是一个软件开发项目,由于之前缺乏有效的项目管理,导致项目进度拖延,成本超支,客户满意度低。

在引入项目管理后,我们采取了以下措施:1. 制定详细的项目计划,包括项目范围、时间表、成本预算等,确保项目目标清晰可行;2. 设立项目团队,明确每个成员的职责和任务,建立有效的沟通机制;3. 确保项目进度的及时监控和调整,及时发现和解决问题;4. 定期与客户沟通,及时了解客户需求,确保项目与客户期望一致。

通过以上措施的实施,项目管理取得了显著的效果。

项目进度得到了有效控制,成本得到了有效降低,客户满意度明显提高。

最终项目顺利完成,取得了良好的经济效益和社会效益。

三、结论通过本次实验,我们深刻认识到了项目管理在实际中的重要性和实际应用效果。

良好的项目管理可以帮助企业提高效率,降低成本,提高客户满意度,提高企业的竞争力。

因此,我们应该高度重视项目管理,不断提升项目管理能力,为企业的可持续发展做出更大的贡献。

电气技术实践可编程逻辑器件FPGA应用开发实验报告2016年12月目录一、实验目的二、实验要求三、实验内容四、实验代码及实验结果(1)4位二进制加法计数器(2)半加器(3)LED静态显示(4)38译码器(5)点阵扫描显示(6)步进电机状态机五、实验感想六、学习并使用FPGA的心得与体会七、电气技术实践总结一、实验目的1、熟悉使用可编程逻辑器件(Altera公司FPGA Cyclone系列EP1C6Q)。

2、熟悉使用硬件描述语言VHDL。

3、掌握FPGA集成环境(Altera公司FPGA QuartusII 开发流程。

4、熟悉使用核心目标系统板与接口电路等工作原理及其功能模块绑定信息。

5、熟悉并掌握下载线方式和下载文件的选择。

二、实验要求1、学习并掌握文本、图形等输入和时序、功能仿真方法。

2、学习并熟悉门电路、组合电路、时序电路等单一模块功能。

3、学习并设计各种不同状态机逻辑功能。

4、学习并设计由单一模块→较多功能模块集成→系统集成方法。

5、学习并选择多种模式显示(发光二极管显示、米字型数码管显示、七段数码管→动态扫描或静态扫描显示、LED点阵显示各种字符和图形或静止或移动等方式、LCD液晶显示各种字符和图形或静止或移动等方式)。

6、根据自已的兴趣和愿望,可从以下给定的实验目录中选取或自已设定功能题目。

7、实验数目没有要求,关键是看质量,是否是自已编写、调试、实现。

三、实验内容1、按指导书集成开发环境章节操作实现文本编程实例1和图形编程实例2全过程。

2、任选门电路、组合电路、时序电路实验各完成一个其逻辑功能,其实现方案自已规定。

在进行FPGA目标器件输入和输出引脚绑定时,输入引脚绑定高/低电平、单脉冲、各种分频连续脉冲等多种信号,输出引脚可绑定发光二极管、七段数码管、LED点阵等显示模式。

3、在完成1位十进制计数器的基础上,可增加完成2或3等多位十进制计数器逻辑功能并用多位七段数码管来显示。

4、根据状态机工作特点,设计一个有一定功能效果的例程。

实验1:状态机实验目的:学习FPGA设计软件教学基本要求:掌握软件流程,掌握状态机编程实验内容提要:设计一个状态机1. 你觉得上面这段代码中,q 到底在怎样变化?(实验1ppt14页)答:在上述代码中,q变化如下:首先判断复位信号 rst 是否为 0,如果是 0 则q复位为0;否则当时钟信号上升沿到来时,将d的值赋给q,再判断a的值,如果a为1,则将b赋值给次态q,如果a为其他值,则将现态q赋给次态q。

2. 本页中,q 到底在怎样变化?(实验1 ppt15页)答:如果异步复位信号rst为0,则q置0;rst不为0时,当时钟上升沿到来时,判断a的值,如果a=1,则将b的值赋给q的次态,如果a是其他值,则将q的现态赋给q 的次态,结束这个判断语句后,将d赋值给q。

3. 画出你理解的这个电路的原理图(ppt16页)4.Out1 out2 out3 out4有什么区别?out1的上升沿与下降沿和50MHz时钟的上升沿始终保持一致,周期变为50MHz时钟的6倍,实现周期扩展;out2的上升沿与clkin的上升沿保持一致,下降沿与out1的上升沿保持一致,可将clkin的数据记录下来以起数据使能作用;out3的上升沿恰好是out2的下降沿,比out2慢一拍,是更适合使用的前端使能;out4的上升沿与out3的下降沿保持一致,可以减少延迟。

2. 红绿灯实验中,该状态机最少几个触发器可以实现?该逻辑情况下红绿灯状态机最少只需8个触发器即可实现。

将3个计时计数触发器合并,并将溢出、使能触发器达成的功能改由计数数值在各状态下的交替变化,使用组合逻辑代替触发器,达成减少触发器使用的设计方案。

实验2 数字钟设计实验目的:掌握FPGA语言设计方法教学基本要求:学习基本的VHDL语言结构和设计实验内容提要:使用VHDL设计一个完整的数字钟实验问题回答:1.现在的时钟是秒时钟,实际系统的时钟是50MHz.那用50MHz的时钟的情况下,仿真1小时要多少时间?如何解决该问题?仿真一小时需要计数器计数3600次,计数脉冲由50MHz的时钟驱动。

ALTERA Project实验报告选题:打砖块第二组:张渝缘,李任,李烨一、实验目的:1、通过实验能独立的运行文件达到效果。

2、深入了解软硬结合的功能,学会独立的解决问题。

二、实验器材:1、ALTERA DE2板子一个2、台式显示器一个3、PC机一台三、实验步骤:1、硬件部分的编译:(1)打开所给的lab3文件,文件中自给的代码如图:代码分析:对时钟信号的定义:控制砖块左右移动的按键:起止条件的判断:(2)单击NEW中选择Block Diagram/Schematic File得到:(3)打开TOOLS-Sopc Builder,对软核进行编译。

选择Processors-Nios II Processor,打开界面:选择确定:双击Project项中的de2_sram_controller,对静态随机存储器进行编译。

选择确定,将其重命名为sram。

选择Interface Protocols-Serial-JTAG UART,对JTAG UART进行编译:选择Memories and Memory Controllers-External Memory Interfaces-SDRAM interfaces-SDRAM Controller并将参数按图中设置:并将其重命名为sdram。

编译显示器与DE板间的传输器VGA,在Project中选择DE2 _vga _raster,并进行编译。

最后选择Project中的rotary_controller,重命名为rotary:再对CPU进行设置:最后整理得到软核如图:单击确定按钮,进行编译。

编译完成后,双击我们建立的BDF文件,选择建立好的PTF文件。

得到所编译好的图,再右键选择GENERATE PINS FOR SYMBOL PORTS。

可以得到器件连接的原理图。

再导入所给的TCL文件,完成对引脚的分配,则此时软核的编译已经完成。

若想要检查自己引脚分配是否有问题,则点击pin-planner。

![ALTERA可靠性报告-中文[1]](https://img.taocdn.com/s1/m/670eac29b4daa58da0114a31.png)

可靠性报告51 Q1 2011XXX翻译、批注公司权利声明(略)目录概述Altera的质量体系图1:典型制造流程可靠性试验方法表1:可靠性认证要求表2:可靠性监控流程寿命测试:方法和失效率预测寿命试验方法失效率预测表3:常见失效机理和加速系数寿命测试结果(以某族为例)Stratix IV,ArriaII GX和HardCopy III/IV 40nm族高温存储试验回流焊模拟及湿气预处理耐湿加速试验高压蒸煮试验(AC)无偏强加速应力试验(Unbiased HAST)有偏温湿度试验(THB)强加速有偏温湿度试验(HAST)温度循环焊接可靠性概述Altera致力于设计并制造可编程逻辑器件(PLDs),Altera提供丰富的PLDs,帮助用户实现特定的数字逻辑功能。

器件的详细说明请参考相应的数据手册。

产品信息,比如器件架构,详细的封装信息,使用和表面贴装的指引,和产品变更通知,请查阅以下的网页:。

Altera 的文献可使用Adobe Acrobat或PostScript软件打开。

Altera的技术支持信息可以从网站产寻:https:///myaltera/mal-index.jsp 。

Altera的在线技术支持系统和Altera知识库,可以帮助你找到技术问题的答案。

另外,常见的问题,还可以通过Altera维护的免费热线电话获得解决:800-800-EPLD (U.S.以外地区呼入:1-408-544-8767)。

Altera建立了质量和可靠性的监控体系,符合ISO9001:2008,MIL-I-45208,和JEDEC等标准的要求。

Altera和其所有的主要供应商都通过了ISO9000认证。

Altera的可靠性认证和监控体系同时满足内部规范。

1994年10月,Altera首次通过了ISO9001认证,核准方是NSAI(爱尔兰国家标准局)。

Altera的企业使命是要成为领先的可编程逻辑芯片解决方案,IP 核,以及相关软件开发工具,和技术支持的首选供应商。

ALTERA Project实验报告

选题:打砖块

第二组:张渝缘,李任,李烨

一、实验目的:

1、通过实验能独立的运行文件达到效果。

2、深入了解软硬结合的功能,学会独立的解决问题。

二、实验器材:

1、ALTERA DE2板子一个

2、台式显示器一个

3、PC机一台

三、实验步骤:

1、硬件部分的编译:

(1)打开所给的lab3文件,文件中自给的代码如图:

代码分析:

对时钟信号的定义:

控制砖块左右移动的按键:

起止条件的判断:

(2)单击NEW中选择Block Diagram/Schematic File得到:

(3)打开TOOLS-Sopc Builder,对软核进行编译。

选择Processors-Nios II Processor,打开界面:

选择确定:

双击Project项中的de2_sram_controller,对静态随机存储器进行编译。

选择确定,将其重命名为sram。

选择Interface Protocols-Serial-JTAG UART,对JTAG UART进行编译:

选择Memories and Memory Controllers-External Memory Interfaces-SDRAM interfaces-SDRAM Controller并将参数按图中设置:

并将其重命名为sdram。

编译显示器与DE板间的传输器VGA,在Project中选择DE2 _vga _raster,并进行编译。

最后选择Project中的rotary_controller,重命名为rotary:

再对CPU进行设置:

最后整理得到软核如图:

单击确定按钮,进行编译。

编译完成后,双击我们建立的BDF文件,选择建立好的PTF文件。

得到所编译好的图,再右键选择GENERATE PINS FOR SYMBOL PORTS。

可以得到器件连接的原理图。

再导入所给的TCL文件,完

成对引脚的分配,则此时软核的编译已经完成。

若想要检查自己引脚分配是否有问题,则点击pin-planner。

可以看到引脚分配上没有错误,下面运行已编译好的程序。

耐性等待一段时间后发现编译并没有错误。

那么硬件部分的编译已经完成,说明没有问题。

2、软件部分的编译:

打开NIOS SOFTWARE文件,选择NEW-NIOS II APPLICATION and BSP from Template。

按如图结果对其进行设置,设置好后进行运

行完成。

可以看到出现了两个文件夹,这就是我们软件的编译环境。

下面添加一个源文件,右键选择NEW-SOURCE FILE,建立一个main.c 的主文件,点击FINISH,完成建立。

在源文件里面将已给源代码考入进去完成建立。

原文件建立好后,点击保存建立好的main函数,如果不保存将导致文件BUILD错误。

下面对文件进行编译右键选择BUILD PROJECT,

等待一段时间后发现文件建立完成。

则现在软件部分也编译完成。

3、连接DE2板子并进行调试。

将画面切回到刚才的QUARTUS中,连接好DE2板,将硬件考入到板子中去。

点击START将硬件考入到了CE2板中。

可以看到板子和显示器上的结果如图:

显示器上

再运行NIOS II,右键选择RUN AS-NIOS II HARDW ARE,这运行了软

件,观察实验结果。

四、实验小结

本次实验是ALTERA的最后一次实验,其目的是将以前所学的综合起来让我们去运行,通过此次学习,我们理解了ALTERA的具体的运行方式,明白了如何去完整的实验软硬件的结合,并且基本掌握了ALTERA的使用方法。

五、任务分配

张渝缘:负责硬件的编写和报告的书写。

李任:负责软件的编写。

李烨:负责整体的运行和调试。