中规模集成电路的应用实验报告

- 格式:doc

- 大小:535.07 KB

- 文档页数:12

中规模集成电路的应⽤实验报告1. 74ls139功能验证基本功能验证:如右图2. 74ls148功能验证基本功能验证:如下图3.⽤74ls138以及74ls00实现全加器、全减器(1)实验分析:74ls138三个输⼊对应8个输出,意思就是⼀个3位的⼆进制输⼊对应⼀个10进制的⼀位例如ABC输⼊111那他那边的Y就会输出对应的⼀个位置如果ABC译码为8那Y⾥⾯就有⼀个位被弄为低电平。

74ls138就是38译码器,是TTL系列的,也就是74系列,有三个输⼊端A0,A1,A2,其中A2是⾼位,输出是⼋个低电平输出Y0 ~ Y7,⼯作电压⼀般的5V。

(2)⽤74ls138、74ls00实现全加器电路图如下:(4)全减器真值表:⽤74LS138、74LS00实现全减器电路图如下:74ls247验证如右图74ls248验证如下图74ls85验证如下图74ls283将8421码转为余3码(如右图)J1端为输⼊8421码端。

灯X1、X2、X3、X4分别代表余三循环码的四位⾼低电平,灯亮代表⾼电平1,灯灭代表低电平0.(如下图)输⼊为8421码制的0111时输出为相对应的余三码制的应为1111,结果如下图:1.74LS74加法器(左图)74LS74减法器(左图)74LS112加法器(下图) 74LS112减法器(下图)74ls160:1.⽤于快速计数的内部超前进位2.⽤于n 位级联的进位输出3.同步可编程序4.有置数控制线5.⼆极管箝位输⼊6.直接清零同步计数74ls160是⼗进制计数器,也就是说它只能记⼗个数从0000-1001(0-9)到9之后再来时钟就回到0,⾸先是clk,这是时钟。

之后是rco,这是输出,MR是复位低电频有效(图上接线前⾯花圈的都是低电平有效)load是置数信号,当他为低电平时,在始终作⽤下读⼊D0到D3。

为了使161正常⼯作ENP和ENT接1另外D0到D3是置数端Q0到Q3是输出端。

这种同步可预置⼗进计数器是由四个D型触发器和若⼲个门电路构成,内部有超前进位,具有计数、置数、禁⽌、直接(异步)清零等功能。

班级:XX姓名:XXX学号:XXXXXX指导老师:XXX实验日期:XXXX年XX月XX日一、实验目的1. 理解集成电路的基本组成和工作原理。

2. 掌握基本的集成电路设计方法,包括原理图设计、版图设计、仿真分析等。

3. 学习使用集成电路设计软件,如Cadence、LTspice等。

4. 通过实验加深对集成电路理论知识的理解,提高动手能力和问题解决能力。

二、实验内容本次实验主要包括以下内容:1. 原理图设计:使用Cadence软件绘制一个简单的CMOS反相器原理图。

2. 版图设计:根据原理图,使用Cadence软件进行版图设计,并生成GDSII文件。

3. 仿真分析:使用LTspice软件对设计的反相器进行仿真分析,测试其性能指标。

4. 版图与原理图匹配:使用Cadence软件进行版图与原理图的匹配,确保设计正确无误。

三、实验步骤1. 原理图设计:- 打开Cadence软件,选择原理图设计模块。

- 根据反相器原理,绘制相应的电路符号,包括NMOS和PMOS晶体管、电阻和电容等。

- 设置各个元件的参数,如晶体管的尺寸、电阻和电容的值等。

- 完成原理图设计后,保存文件。

2. 版图设计:- 打开Cadence软件,选择版图设计模块。

- 根据原理图,绘制晶体管、电阻和电容的版图。

- 设置版图规则,如最小线宽、最小间距等。

- 完成版图设计后,生成GDSII文件。

3. 仿真分析:- 打开LTspice软件,选择仿真模块。

- 将GDSII文件导入LTspice,生成对应的原理图。

- 设置仿真参数,如输入电压、仿真时间等。

- 运行仿真,观察反相器的输出波形、传输特性和功耗等性能指标。

4. 版图与原理图匹配:- 打开Cadence软件,选择版图与原理图匹配模块。

- 将原理图和版图导入匹配模块。

- 进行版图与原理图的匹配,检查是否存在错误或不一致之处。

- 修正错误,确保版图与原理图完全一致。

四、实验结果与分析1. 原理图设计:- 成功绘制了一个简单的CMOS反相器原理图,包括NMOS和PMOS晶体管、电阻和电容等元件。

数字集成电路设计实验报告

摘要:

本实验旨在设计一个数字集成电路,实现特定功能。

本报告将介绍实验目的、背景和理论知识、设计方法、实验步骤、结果分析和讨论以及实验总结。

1.实验目的:

设计一个数字集成电路,实现特定功能,并通过实验验证设计的正确性和可行性。

2.背景和理论知识:

简要介绍数字集成电路的基本概念和原理,并介绍与本实验相关的理论知识,包括逻辑门、布尔代数、时序电路等。

3.设计方法:

本部分将详细介绍实验中采用的设计方法,包括采用的逻辑门类型、布尔代数的转换方法、时序电路的设计方法等。

4.实验步骤:

本部分将详细描述实验的具体步骤,包括电路图的绘制、器件的选择和布局、逻辑设计的步骤、时序电路的设计方法、电路的仿真等。

5.结果分析和讨论:

本部分将对实验结果进行分析和讨论,比较设计与实际结果的差异,分析可能的原因,并讨论实验的局限性和改进方向。

6.实验总结:

总结实验过程中的收获和经验,评估实验的结果和设计的可行性,并提出对未来工作的展望和建议。

通过对数字集成电路设计实验的详细介绍和分析,本报告旨在提供一份完整的实验报告,帮助读者理解实验过程和结果,并为今后的设计工作提供参考。

实验二 译码器及其应用一、 实验目的1、掌握译码器的测试方法。

2、了解中规模集成译码器的管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

4、学习译码器的扩展。

二、 实验设备及器件1、数字逻辑电路实验板1块 2、74HC(LS)20(二四输入与非门) 1片 3、74HC(LS)138(3-8译码器)2片三、 实验原理74HC(LS)138是集成3线-8线译码器,在数字系统中应用比较广泛。

下图是其引脚排列,其中A 2、A 1、A 0为地址输入端,Y ̅0~Y ̅7为译码输出端,S 1、S ̅2、S ̅3为使能端。

下表为74HC(LS)138功能表。

74HC(LS)138工作原理为:当S 1=1,S ̅2+S ̅3=0时,电路完成译码功能,输出低电平有效。

其中:Y ̅0=A ̅2A ̅1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅4=A 2A ̅1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅1=A ̅2A ̅1A 0̅̅̅̅̅̅̅̅̅̅ Y ̅5=A 2A ̅1A 0̅̅̅̅̅̅̅̅̅̅ Y ̅2=A ̅2A 1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅6=A 2A 1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅3=A ̅2A 1A 0̅̅̅̅̅̅̅̅̅̅Y ̅7=A 2A 1A 0̅̅̅̅̅̅̅̅̅̅因为74HC(LS)138的输出包括了三变量数字信号的全部八种组合,每一个输出端表示一个最小项(的非),因此可以利用八条输出线组合构成三变量的任意组合电路。

实验用器件管脚介绍:1、74HC(LS)20(二四输入与非门)管脚如下图所示。

2、74HC(LS)138(3-8译码器)管脚如下图所示。

四、实验内容与步骤(四学时)1、逻辑功能测试(基本命题)m。

验证74HC(LS)138的逻辑功能,说明其输出确为最小项i注:将Y̅0~Y̅7输出端接到LED指示灯上,因低电平有效,所以当输入为000时,Y̅0所接的LED指示灯亮,其他同理。

一、设计目的及要求:(一)实验目的:1. 通过实验培养学生的市场素质,工艺素质,自主学习的能力,分析问题解决问题的能力以及团队精神。

2. 通过本实验要求学生熟悉各种常用中规模集成电路组合逻辑电路的功能与使用方法,学会组装和调试各种中规模集成电路组合逻辑电路,掌握多片中小规模集成电路组合逻辑电路的级联、功能扩展及综合设计技术,使学生具有数字系统外围电路、接口电路方面的综合设计能力。

(二)实验要求1. 数字显示电路操作面板:左侧有16个按键,编号为0到15数字,面板右侧有2个共阳7段显示器。

2. 设计要求:当按下小于10的按键后,右侧低位7段显示器显示数字,左侧7段显示器显示0;当按下大于9的按键后,右侧低位7段显示器显示个位数字,左侧7段显示器显示1。

若同时按下几个按键,优先级别的顺序是15到0。

二、电路框图及原理图原理图概要:数字显示电路由键盘、编码、码制转换、译码显示组成。

各部分作用:1. 键盘:用于0~15数字的输入。

可以由16个自锁定式的按键来排列成4×4键盘。

2.编码:采用两片74ls148级联来完成对0~15的编码,并且是具有优先级的编码。

3.码制转换:本电路采用了2个74ls00、1个74ls04、1个74ls283来完成对0~15出事编码的码制转换,转换成个位与十位的8421bcd码,为下一步的解码做准备。

4.译码显示:本电路采用了两个74ls47分别对码制转换后的bcd码进行译码,并且由这两个芯片分别驱动两片七段共阳极数码管。

原理图:三、设计思想及基本原理分析:篇二:数电实验实验报告数字电路实验报告院系:电气工程学院专业:电气工程极其自动化班级:09级7班姓名:王哲伟学号:2009302540221 实验一组合逻辑电路分析一.试验用集成电路引脚图74ls00集成电路 74ls20集成电路四2输入与非门双4输入与非门二.实验内容 1.实验一x1abdabcd按逻辑开关,“1”表示高电平,“0”表示低电平2.5 vc示灯:灯亮表示“1”,灯灭表示“0”自拟表格并记录: 2.实验二密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。

集成电路的基础实验与应用摘要:本文旨在介绍集成电路的基础实验与应用。

首先,介绍了集成电路的定义和分类。

随后,探讨了集成电路的基本特性以及其在电子产品中的广泛应用。

然后,详细介绍了集成电路实验的基本原理和操作步骤。

最后,讨论了集成电路在通信、计算机和医疗等领域的应用,并指出了未来发展的趋势。

1. 引言集成电路(Integrated Circuit,简称IC)是在单个芯片上集成了数百到数百万个电子元件的电路。

它的产生极大地推动了电子技术的发展,使得电子产品更加小型化、高效化和可靠化。

本文旨在通过实验和应用的角度探讨集成电路的基础知识和相关技术。

2. 集成电路的定义和分类集成电路是将多个电子元件(如晶体管、二极管等)通过金属联系线等方式连接在一起,形成一个电子系统。

根据电子元件的数量和复杂程度,集成电路可以分为小规模集成电路(SSI)、中规模集成电路(MSI)和大规模集成电路(LSI)等多个类别。

3. 集成电路的基本特性集成电路相比于传统的离散元件电路,具有以下几个基本特性:1) 紧凑性:集成电路中的电子元件被集成在一个小芯片上,具有很高的集成度和紧凑性。

2) 可靠性:集成电路采用批量生产的工艺,因此在质量和可靠性上具有很高的保障。

3) 低功耗:由于电子元件之间的距离很近,集成电路具有较低的功耗特性。

4) 高性能:集成电路在单个芯片上集成了大量电子元件,因此具有较高的性能和功能。

4. 集成电路的应用集成电路在电子产品的制造中具有广泛的应用,包括但不限于:1) 通信领域:集成电路在手机、无线网络和卫星通信等领域中扮演重要的角色,实现了信息的传递和交流。

2) 计算机领域:集成电路是计算机硬件的重要组成部分,通过集成电路的高速运算,实现了计算机的高效处理能力。

3) 医疗领域:集成电路在医疗器械中的应用越来越广泛,如心脏起搏器、血压计和体温计等。

4) 汽车电子领域:集成电路在汽车电子系统的控制和管理中发挥着关键作用,提高了汽车的安全性和舒适性。

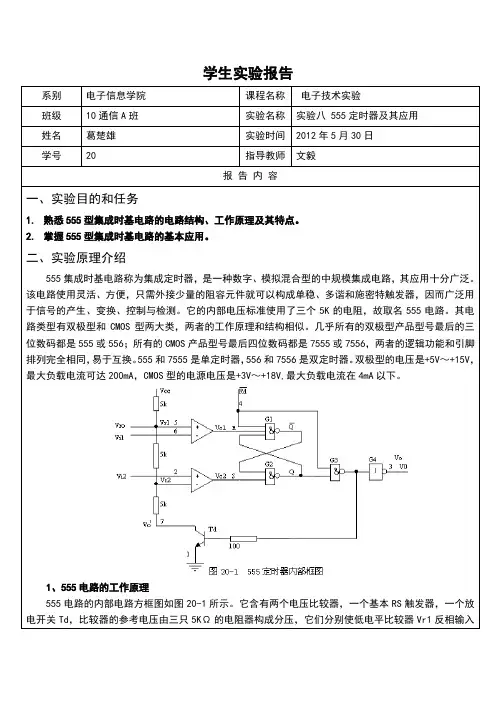

学生实验报告系别电子信息学院课程名称电子技术实验班级10通信A班实验名称实验八 555定时器及其应用姓名葛楚雄实验时间2012年5月30日学号20指导教师文毅报告内容一、实验目的和任务1.熟悉555型集成时基电路的电路结构、工作原理及其特点。

2.掌握555型集成时基电路的基本应用。

二、实验原理介绍555集成时基电路称为集成定时器,是一种数字、模拟混合型的中规模集成电路,其应用十分广泛。

该电路使用灵活、方便,只需外接少量的阻容元件就可以构成单稳、多谐和施密特触发器,因而广泛用于信号的产生、变换、控制与检测。

它的内部电压标准使用了三个5K的电阻,故取名555电路。

其电路类型有双极型和CMOS型两大类,两者的工作原理和结构相似。

几乎所有的双极型产品型号最后的三位数码都是555或556;所有的CMOS产品型号最后四位数码都是7555或7556,两者的逻辑功能和引脚排列完全相同,易于互换。

555和7555是单定时器,556和7556是双定时器。

双极型的电压是+5V~+15V,最大负载电流可达200mA,CMOS型的电源电压是+3V~+18V,最大负载电流在4mA以下。

1、555电路的工作原理555电路的内部电路方框图如图20-1所示。

它含有两个电压比较器,一个基本RS触发器,一个放电开关Td,比较器的参考电压由三只5KΩ的电阻器构成分压,它们分别使低电平比较器Vr1反相输入端和高电平比较器Vr2的同相输入端的参考电平为2/3VCC和1/3VCC。

Vr1和Vr2的输出端控制RS触发器状态和放电管开关状态。

当输入信号输入并超过2/3VCC时,触发器复位,555的输出端3脚输出低电平,同时放电,开关管导通;当输入信号自2脚输入并低于1/3VCC时,触发器置位,555的3脚输出高电平,同时充电,开关管截止。

R是异步置零端,当其为0时,555输出低电平。

平时该端开路或接VCC。

Vro是控制电压端(5脚),D平时输出2/3VCC作为比较器Vr1的参考电平,当5脚外接一个输入电压,即改变了比较器的参考电平,从而实现对输出的另一种控制,在不接外加电压时,通常接一个的电容器到地,起滤波作用,以消除外来的干扰,以确保参考电平的稳定。

数字逻辑电路实验报告指导老师:班级:学号:姓名:时间:第一次试验一、实验名称:组合逻辑电路设计1二、试验目的:掌握组合逻辑电路的功能测试。

1、验证半加器和全加器的逻辑功能。

2、、学会二进制数的运算规律。

3、试验所用的器件和组件:三、74LS00 3片,型号二输入四“与非”门组件74LS20 1片,型号四输入二“与非”门组件74LS86 1片,型号二输入四“异或”门组件实验设计方案及逻辑图:四、/全减法器,如图所示:1、设计一位全加时做减法运时做加法运算,当M=1M决定的,当M=0 电路做加法还是做减法是由SCin分别为加数、被加数和低位来的进位,、B和算。

当作为全加法器时输入信号A分别为被减数,减数Cin、B和为和数,Co为向上的进位;当作为全减法时输入信号A 为向上位的借位。

S为差,Co和低位来的借位,1)输入/(输出观察表如下:(2)求逻辑函数的最简表达式函数S的卡诺图如下:函数Co的卡诺如下:化简后函数S的最简表达式为:Co的最简表达式为:2(3)逻辑电路图如下所示:、舍入与检测电路的设计:2F1码,用所给定的集成电路组件设计一个多输出逻辑电路,该电路的输入为8421为奇偶检测输出信号。

当电路检测到输入的代码大于或F2为“四舍五入”输出信号,的个数为奇数时,电路。

当输入代码中含1F1=1;等于5是,电路的输出其他情况F1=0 F2=0。

该电路的框图如图所示:的输出F2=1,其他情况输出观察表如下:(输入/0 1 0 0 1 01 0 1 0 0 11 1 1 0 0 01 0 1 1 1 11 0 0 1 0 11 0 1 0 0 11 0 0 1 1 01 1 1 0 1 11 0 1 1 0 011111求逻辑函数的最简表达式(2)的卡诺如下:函数F1 F2函数的卡诺图如下:的最简表达式为:化简后函数F2 的最简表达式为:F1)逻辑电路图如下所示;(3课后思考题五、化简包含无关条件的逻辑函数时应注意什么?1、答:当采用最小项之和表达式描述一个包含无关条件的逻辑问题时,函数表达式中,并不影响函数的实际逻辑功能。

接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138 还可作数据分配器3.3 线-8 线译码器74LS138的逻辑图与功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7 个输出引脚全为高电平1。

如果出现两个输出引脚同时为0 的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出(2)74LS139基本功能当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一个对应的输出端以低电平译出。

若将选通端(G1)作为数据输入端时,139 还可作数据分配器。

管脚图内部逻辑引脚功能引出端符号:A、B:译码地址输入端G1、G2 :选通端(低电平有效)Y0~Y3:译码输出端(低电平有效)真值表(3)74LS148基本功能74LS148是8 线-3 线优先编码器,共有54/74148 和54/74LS148两种线路结构型式,将8 条数据线(0-7)进行3 线(4-2-1)二进制(八进制)优先编码,即对最高位数据线进行译码。

利用选通端(EI)和输出选通端(EO)可进行八进制扩展。

管脚图管脚介绍0-7 编码输入端(低电平有效)EI 选通输入端(低电平有效)A0、A1、A2 三位二进制编码输出信号即编码输出端(低电平有效)GS 片优先编码输出端即宽展端(低电平有效)EO 选通输出端,即使能输出端逻辑图真值表由74ls148真值表可列输出逻辑方程为:A2 = (I4+I5+I6+I7)IEA1 = (I2I4I5+I3I4I5+I6+7)·IEA0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE工作原理该编码器有8个信号输入端,3个二进制码输出端。

此外,电路还设置了输入使能端EI,输出使能端EO和优先编码工作状态标志GS。

数电实验报告实验二利用MSI设计组合逻辑电路一、实验目的1. 学习MSI(Medium Scale Integration,即中规模集成电路)的基本概念和应用。

2.掌握使用MSI设计和实现组合逻辑电路的方法。

3.了解MSI的类型、特点及其在实际电路设计中的作用。

二、实验设备与器件1.实验设备:示波器、信号发生器、万用表。

2.实验器件:组合逻辑集成电路74LS151三、实验原理1.MSI的概念MSI是Medium Scale Integration的简称,指的是中规模集成电路。

MSI由几十个至几千个门电路组成,功能比SSI(Small Scale Integration,即小规模集成电路)更为复杂,但比LSI(Large Scale Integration,即大规模集成电路)简单。

2.74LS151介绍74LS151是一种常用的组合逻辑集成电路之一,具有8个输入端和1个输出端。

其功能是从八个输入信号中选择一个作为输出。

利用该器件可以轻松实现数据选择器、多路选择器等功能。

四、实验内容本实验的任务是利用74LS151设计一个简单的多路选择器电路。

具体实验步骤如下:1.将74LS151插入实验板中,注意引脚的正确连接。

2.将信号发生器的输出接入到74LS151的A、B、C三个输入端中,分别作为输入0、输入1、输入2、将示波器的探头分别接到74LS151的输出端Y,记录下不同输入情况下Y的输出情况。

3.分别将信号发生器的输出接入74LS151的D0、D1、D2、D3、D4、D5、D6、D7八个输入端,接通电源,记录下不同输入情况下Y的输出情况。

4.通过以上实验数据,绘制74LS151的真值表。

五、实验结果与数据处理根据实验步骤所述,我们完成了实验,并得到了以下数据:输入0:0000001111001111输入1:1111110010100101输入2:1010101001010101根据这些数据,我们可以绘制74LS151的真值表如下:输入0,输入1,输入2,输出Y--------,--------,--------,--------0,0,0,00,0,1,10,1,0,00,1,1,11,0,0,11,0,1,01,1,0,11,1,1,1六、实验总结通过本次实验,我们学习了MSI的基本概念和应用,初步掌握了使用MSI设计和实现组合逻辑电路的方法。

集成电路导论实验报告实验一:集成电路的基本参数测量方法实验目的:1. 了解集成电路的基本参数。

2. 学习集成电路的测量方法。

3. 掌握集成电路测量所需的仪器和设备的使用方法。

实验器材:1. 集成电路:选取常见的几种逻辑门电路芯片。

2. 集成电路测试台:包括电源、波形发生器、示波器等。

3. 测试电缆和测量仪器。

实验步骤:1. 准备集成电路和测试台,并将电源、波形发生器和示波器连接好。

2. 将集成电路插入测试台相应插槽,并按照测试仪器的要求连接电路。

3. 打开电源并设置合适的电压和频率。

4. 使用示波器观察集成电路的输入输出电压波形,并记录相应数据。

5. 根据所测数据计算集成电路的基本参数,如电压增益、功耗等。

6. 对不同类型的集成电路重复上述步骤,进行不同参数的测量。

实验结果:以74LS00为例,通过测量得到的数据如下:输入电压:2V输出电压:4V功耗:20mW增益:2实验讨论:根据测得的数据,可以看出74LS00逻辑门电路芯片在2V的输入电压下,产生4V的输出电压,且功耗为20mW。

通过计算得到的增益为2,即输出电压是输入电压的2倍。

这些参数的测量结果可以用来评估集成电路的性能和设计电路时的参考。

实验总结:通过本次实验,我们学习了集成电路的基本参数测量方法,掌握了集成电路测量所需的仪器和设备的使用方法。

实验中我们选取了几种常见的逻辑门电路芯片进行了测量,通过观察波形、记录数据和计算参数,获得了它们的基本参数。

这些参数的测量对于电路设计和性能评估都具有重要的参考价值。

实验一数字电路实验基础一、实验目的⑴掌握实验设备的使用和操作⑵掌握数字电路实验的一般程序⑶了解数字集成电路的基本知识二、预习要求复习数字集成电路相关知识及与非门、或非门相关知识三、实验器材⑴直流稳压电源、数字逻辑电路实验箱、万用表⑵74LS00、74LS02、74LS48四、实验内容和步骤1、实验数字集成电路的分类及特点目前,常用的中、小规模数字集成电路主要有两类。

一类是双极型的,另一类是单极型的。

各类当中又有许多不同的产品系列。

⑴双极型双极型数字集成电路以TTL电路为主,品种丰富,一般以74(民用)和54(军用)为前缀,是数字集成电路的参考标准。

其中包含的系列主要有:▪标准系列——主要产品,速度和功耗处于中等水平▪LS系列——主要产品,功耗比标准系列低▪S系列——高速型TTL、功耗大、品种少▪ALS系列——快速、低功耗、品种少▪AS系列——S系列的改进型⑵单极型单极型数字集成电路以CMOS电路为主,主要有4000/4500系列、40H系列、HC系列和HCT系列。

其显著的特点之一是静态功耗非常低,其它方面的表现也相当突出,但速度不如TTL集成电路快。

TTL产品和CMOS产品的应用都很广泛,具体产品的性能指标可以查阅TTL、CMOS集成电路各自的产品数据手册。

在本实验课程中,我们主要选用TTL数字集成电路来进行实验。

2、TTL集成电路使用注意事项⑴外形及引脚TTL集成电路的外形封装与引脚分配多种多样,如附录中所示的芯片封装形式为双列直插式(DIP)。

芯片外形封装上有一处豁口标志,在辨认引脚分配时,芯片正面(有芯片型号的一面)面对自己,将此豁口标志朝向左手侧,则芯片下方左起的第一个引脚为芯片的1号引脚,其余引脚按序号沿芯片逆时针分布。

⑵电源每片集成电路芯片均需要供电方能正常使用其逻辑功能,供电电源为+5V单电源。

电源正端(+5V)接芯片的VCC引脚,电源负端(0V)接芯片的GND引脚,两者不允许接反,否则会损坏集成电路芯片。

组合逻辑电路综合实验报告课程名称:班级:姓名:学号:实验一常用逻辑门电路功能测试一、实验目的1.掌握TTL与非门输入、输出之间的逻辑关系。

2.熟悉TTL中、小规模集成电路的外形、管脚及使用方法。

3. 了解常用的逻辑门电路。

二、实验类型验证性与设计性实验。

三、实验仪器设备二输入四与非门74LS00一片四、实验原理1. 典型的TTL与非门电路2. 7400是一种有4个2输入与非门的集成电路五、实验内容测试74LS00一个与非门的输入和输出的逻辑关系。

六、实验步骤1引脚和2引脚接输入端k1和k2,3引脚接输出端灯L1,14引脚接电源,7引脚接地。

让电路工作,调试电路。

七、实验结果八、实验总结1.充分了解了与非门的输入、输出之间的逻辑关系。

2.做实验时,要先将芯片插好再连线,最后将电源打开,这样不仅安全还能保护电路不收损伤。

3. 与非门的逻辑表达式为Z=ABC。

4. 亲自动手实验让我对数字逻辑电路这门课程产生了更高的兴趣。

九、实验改进建议1.要提前预习实验弄清楚实验目的,弄懂实验原理。

2.可以用电脑模拟软件来模拟电路实验,这样可以减少由于操作不当而造成的电路元件烧毁等现象造成的不必要的损失。

实验二中规模逻辑器件功能测试一、实验目的1.掌握三线——八线译码器的逻辑电路构成、特点及应用2.熟悉三线——八线译码器的功能及其引脚3. 巩固组合逻辑电路的设计方法。

4.熟悉TTL中规模集成电路的外形、管脚及使用方法。

5.掌握中规模逻辑器件译码器的输入、输出之间逻辑关系。

二、实验类型验证性与设计性实验。

三、实验仪器设备三线——八线译码器74LS138一片四、实验原理1. 变量译码器是指将n位二进制输入变量译成n2个不同输出信号的译码器。

2. 将每一组输入代码译为一个特定的输出信号,以表示代码原意的组合逻辑电路,由三位2进制数译出8个输出信号。

五、实验内容测试74LS138三线——八线译码器的输入和输出逻辑关系。

六、实验步骤16引脚接电源,8引脚接地。

实习报告二——数字钟制作一、实习目的:1. 熟悉电子焊接技术。

2. 了解ZX2042型数码显示电子钟的原理。

3. 通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法。

4. 学会制作数字钟。

二、实习时间:2010-9-8——2010-9-9三、实习内容:焊接一个ZX2042型数码显示电子钟。

自行装配调试,并能发现问题和解决问题。

写出制作的全过程,编写实习报告。

四、实习步骤:1.数字钟工作原理电路原理图如下图。

LM8560(IC1)是50/60HZ的时基24小时专用数字钟集成电路,有28只管脚,1-14脚是显示笔划输出,15脚为电源端,20脚为负电源端,27脚是内部振荡器RC输入端,16脚为报警输出。

T1为降压变压器,经桥式整流(VD6-VD9)及滤波(C3、C4)后得到直流电,供主电路和显示屏工作。

当交流电源停电时,备用电池通过VD5向电路供电。

IC2(CD4060)、JT、R2、C2构成50HZ的时基电路,CD4060内部包含14位二分频器和一个振荡器,电路简洁,30720HZ的信号经分频后,得到50HZ的信号送到LM8560的25脚,并做秒信号经VT2、VT3驱动显示屏内的冒号闪动。

当调好定时时间后,并按下开关K1,显示屏右下方有绿点指示,到定时时间有驱动信号经R3使VT1工作,即可定时报警输出。

2.焊接步骤A、先焊接在电路板较低的元件,如:电阻、二极管、集成电路、跳线。

B、其次焊接在在电路板上排列稍微高一点的元件,如:LED、插针、电源座。

C、最后将电容、三极管等较高的元件焊上。

3.安装工艺要求在动手焊接前先用表将各元件测量一下,做到心中有数,安装时先装低矮和耐热的元件(如电阻),然后再装大一点的元件,最后装怕热的元件(如三极管、集成电路等)。

电阻的安装:将电阻的阻值选择好后,根据两孔德距离可采用立式紧贴电路板安装。

电解电容器、二极管、三极管安装时注意极性,电解电容器C4紧贴电路板卧式安装,C3紧贴电路板立式安装;二极管紧贴电路板立式安装;三极管安装时注意型号。

计数、译码、显示电路实验一、实验器材(设备、元器件):1,数字、模拟实验装置(1台);2,数字电路实验板(1块);3,74LS90、74LS00芯片(各一片);4,函数信号发生器(1台)。

二、实验内容及目的:1,熟悉和测试74LS90的逻辑功能;2,运用中规模集成电路组成计数、译码、显示电路。

三、实验步骤:1、利用数字电路实验装置测试74LS90芯片的逻辑功能异步计数器74LS90为中规模TTL集成计数器,可实现二分频、五分频、十分频等功能,它由一个二进制计数器和一个五进制计数器构成,其外引脚图和功能表如下图所示:异步:同步:满足1)2()1(00=∙R R ,1)2()1(=∙Sq Sq 时:①1CP =CP ,2CP =0时:二进制计数; ②1CP =0,2CP =CP 时:五进制计数;③1CP =CP ,2CP =A Q 时:8421码二进制计数; ④1CP =D Q ,2CP =CP 时:5421码十进制计数。

插好74LS90芯片,连好电源和接地端,计数脉冲由函数信号发生器提供,)1(0R 、)2(0R 、)1(9S 、)2(9S 分别接逻辑开关,四个输出端接电平显示或数码管,按功能表拨动开关验证其结果。

2,设计一个显示星期的计数器,使之重复0——6的显示(用74LS90与74LS00实现)利用反馈归零法可以使74LS90实现十以内的N 进制计数器,即从0记到要设计的进制时使清零端)1(0R 、)2(0R 有效(同时为高电平),进而反馈清零。

此实验实现0——6显示,即设计七进制数,当计数器计到111时,用反馈清零法使之为000,故先将)1(9S 、)2(9S 接地,1CP 接计数脉冲CP ,2CP 接A Q ,构成十进制数,再由于此只为七进制,故只用到A Q 、B Q 、C Q ,又用74LS00,故可使C Q 接B Q 、A Q 与非后再和“1”与非后接)2(0R ,使得当计数器计到111时,)1(0R 、)2(0R 实现清零。

功能验证:

2. 74ls248

74ls248是4线——七段译码器/驱动器(BCD输入,有上拉电阻)

简要说明:

248为有内部上拉电阻的BCD—七段译码器/驱动器,共有54/74248和54/74LS248两种线路结构型式。

输出端(a~g)为低电平有效,可直接驱动指示灯或共阴极LED。

当要求输入0~15时,消隐输入(/BI)应为高电平或开路,对于输出0时还要求脉冲消隐输入(/RBI)为高电平或开路。

当BI为低电电平,不管其它输入端状态如何,a~g均为低电平。

当/RBI和地址端(A~D)均为低电平,并且灯测试(/LT)为高电平时,a~g均为低电平,脉冲消隐输出(/RBO)为

低电平。

当BI为高电平开路时,/LT的低电平可使a~g为高电平。

引出段符号:

A,B,C,D译码地址输入端

/BI,/RBO消隐输入(低电平有效)

脉冲消隐输出(低电平有效)

/LT灯测试输入端(低电平有效)

/RBI脉冲消隐输入端(低电平有效)

a~g段输出(低电平有效)

74ls248引脚图

3. 74ls85

74ls85两个位数相同的二进制数进行比较74ls85引脚图及功能

从功能表可以看出,该比较器的比较原理和两位比较器的比较原理相同。

两个4位数的比较是从A的最高位A3和B的最高位B3进行比较,如果它们不相等,则该位的比较结果可以作为两数的比较结果。

若最高位A3=B3,则再比较次高位A2和B2,余类推。

显然,如果两数相等,那么,比较步骤必须进行到最低位才能得到结果。

真值表中的输入变量包括A3与B3、A2与B2、A1与

B1、A0与B0和A与B的比较结果。

其中A和B是另外两个低位数,IA》B、IA《B和IA=B是它们的比较结果。

设置低位数比较结果输入端是为了能与其他数值比较器连接,以便组成位数更多的数值比较器。

4. 74ls283

74ls283是4位二进制超前进位全加器

简要说明:283为具有超前进位的4位全加器

283可进行两个4位二进制数的加法运算,每位有和输出∑1~∑4,进位由第四位得到C4.

引出端符号:

A1–A4运算输入端

B1–B4运算输入端

C0进位输入端

Σ1–Σ4和输出端

C4进位输出端

74ls283引脚图

74ls283逻辑功能图

(2)用74LS283实现8421码转为余3码。

逻辑门图

逻辑式

X1=AB’C’+A'D+A’C

X2=AB’C’D’A’B+A’C+A’D X3=B’C’+A’BCD+A’B’D’X4=A’C。