混频器设计

- 格式:docx

- 大小:1.13 MB

- 文档页数:13

2012~2013学年第一学期《高频电子线路》课程设计报告题目:混频器电路的设计专业:电子信息工程电气工程系2012年12月20日任务书摘要混频,又称变频,也是一种频谱的线性搬移过程,它是使信号自某一个频率变换成另一个频率。

完成这种功能的电路称为混频器。

混频技术的应用十分广泛。

混频器是超外差式收音机中的关键部件。

直放式接收机高频小信号检波,工作频率变化范围大时,工作频率对高频通道的影响比较大,灵敏度较低。

采用超外差技术后,将接收信号混频到一固定中频,放大量基本不受接收频率的影响,这样,频段内信号的放大一致性好,灵敏度可以做得很高,选择性也较好。

因为放大功能主要在中放,可以用良好的滤波电路。

采用超外差接收后,调整方便,放大量、选择性主要由中频部分决定,且中频较高频信号的频率低,性能指标容易得到满足。

混频器在一些发射设备中也是必不可少的。

在频分多址信号的合成、微波接力通信、卫星通信等系统中也有其重要的地位。

此外,混频器也是许多电子设备、测量仪器的重要组成部分。

关键字:信号;频率;混频器目录摘要 (2)第一章系统分析 (4)1.1 设计任务 (4)1.2 工作原理及系统框图 (4)第二章软件介绍 (5)2.1 Multisim 10简介 (5)2.2 Multisim 10特点 (5)第三章硬件电路图及原理分析 (6)3.1 总电路图 (6)3.2 本地振荡回路 (7)3.2.1 振荡起振条件 (7)3.2.2 电路参数选择及原理分析 (8)3.3 变频电路 (9)3.3.1 混频原理 (9)3.3.2 电路参数选择及性能分析 (11)3.4中频滤波电路 (12)第四章仿真及结果 (14)第五章结论 (17)参考文献 (18)1.1 设计任务设计一混频电路要求输入信号为10MHz ,本振信号为16.455MHz 左右,中频频率为6.455MHz 。

1.2 工作原理及系统框图一个实际应用中调幅收音机的混频器电路的主要功能是使信号自某一个频率变换成另外一个频率,实际上是一种频谱线性搬移电路。

混频与鉴频器的设计混频器和鉴频器是无线通信系统中非常重要的组件,它们分别用于信号的混频和鉴频。

混频器的主要作用是将高频信号和低频信号相乘,从而将高频信号转换成中频或基带信号,以便进行信号处理。

而鉴频器则用于将调制信号解调为原始信号。

混频器的设计通常需要考虑以下几个方面:1.混频器的工作频率范围:混频器的工作频率范围决定了它在不同应用中的适用性。

设计中需要选择合适的转换技术和电路拓扑,以确保混频器在所需的频率范围内具有良好的性能。

2.混频器的转换损耗:混频器在信号转换过程中会引入一定的转换损耗,也就是信号的功率损失。

设计中需要通过合适的电路参数和材料选择来降低转换损耗,并提高混频器的效率。

3.混频器的非线性特性:混频器在工作时会引入非线性失真,例如互调失真和交调失真。

这些失真会导致频谱扩展和杂散分量增加,对无线通信系统的性能造成影响。

因此,设计时需要选择合适的电路结构和优化电路参数,以减少非线性失真。

4.混频器的隔离度和带外抑制:混频器在混频过程中会引入一些杂散分量,它们可能会干扰其他无线设备或频段的信号。

设计中需要通过增强隔离度和带外抑制能力,以降低对其他信号的干扰。

鉴频器的设计也需要考虑类似的因素,同时还需要关注以下几点:1.鉴频器的解调效率:鉴频器的解调效率决定了解调后的信号质量。

设计中需要选择合适的解调方法和电路参数,以提高鉴频器的解调效率。

2.鉴频器的带宽和选择性:鉴频器通常需要适应不同带宽的信号,例如窄带和宽带信号。

设计时需要选择合适的电路结构和调整电路参数,以实现所需的带宽和选择性。

3.防止锁定和抗混叠:鉴频器设计需要考虑避免频率偏移和频率混叠的问题。

通过合适的信号处理技术和滤波器设计,可以提高鉴频器的抗干扰能力。

4.鉴频器的抗噪声性能:鉴频器中通常存在一定的噪声,例如热噪声和杂散噪声。

设计时需要选择合适的放大器和滤波器来提高鉴频器的抗噪声性能。

总体而言,混频器和鉴频器的设计需要综合考虑频率范围、转换损耗、非线性特性、隔离度、带宽、选择性、解调效率、抗锁定和抗噪声性能等因素。

混频器设计与应用技术混频器(Heterodyne Mixer)是一种常用于射频(RF)和微波(microwave)电路中的器件,用于将不同频率的信号进行混频处理。

本文将介绍混频器的设计原理、主要类型以及广泛应用的技术。

一、混频器设计原理混频器的设计原理基于频率混合的特性,利用非线性元件,如二极管或场效应晶体管(FET),将两个不同频率的信号进行混合。

通过混频器的非线性特性,原始信号的频率被转换成新的频率,即中频(intermediate frequency, IF)。

二、混频器的主要类型1. 非平衡混频器非平衡混频器是最简单和常见的混频器类型之一。

它通常由一个二极管和匹配网络组成。

非平衡混频器具有较低的转换增益和较高的转换损耗,适用于一些要求简单性能的应用场景。

2. 平衡混频器平衡混频器是由两个对称的非线性电路组成,可以抵消输入信号中的互调失真。

平衡混频器具有较好的抗互调能力和较高的转换增益,适用于一些性能要求较高的应用场景。

3. 双平衡混频器双平衡混频器是在平衡混频器的基础上增加了额外的平衡结构,可以进一步提高抗互调能力和转换增益。

双平衡混频器通常用于一些对性能要求非常高的应用,如通信系统中的高动态范围接收机。

4. 有源混频器有源混频器是将放大器与混频器集成在一起的混频器。

它具有较高的增益和较低的噪声性能,适用于需求较高的射频接收机和通信系统。

三、混频器的应用技术1. 超外差接收技术超外差接收技术是混频器的一种重要应用技术,用于将接收到的射频信号转换成中频信号进行后续处理。

通过使用合适的混频器和滤波器,可以实现高灵敏度、高选择性的无线通信接收系统。

2. 雷达系统混频器在雷达系统中广泛应用。

雷达系统通过发射和接收射频信号来探测目标。

混频器用于将接收到的回波信号和本振信号进行混频处理,提取出目标的距离、速度和角度等信息。

3. 通信系统在通信系统中,混频器用于频率转换、频谱分析和信号调制等关键步骤。

通信电子中的混频器设计与实现混频器是通信电子系统中常用的重要组件,它能够将两个不同的信号混合在一起,并产生新的频率信号。

混频器的应用范围很广,从基于微波的通信电子系统到基于射频的调制解调器都需要使用混频器。

本文将从混频器的基础知识、工作原理和设计实现三个方面来介绍混频器。

基础知识混频器的核心组件是二极管,它能够将两个信号进行非线性混合,产生一个包含原信号频率之和和差的新信号。

在混频器中,一个信号称为本振信号,另一个信号称为射频信号。

本振信号的频率在混频器中是固定的,而射频信号的频率是需要混频的信号。

混频器的输出信号称为中频信号,它的频率通常在几十千赫兹到几百兆赫兹之间,这是通讯电子系统能够处理的频率范围。

混频器的工作原理混频器的工作原理可以分为以下几个步骤:1. 在混频器的输入端口,本振信号和射频信号经过耦合器相结合。

2. 二极管的非线性特性会导致信号的幅度被混合在一起。

3. 混频器的输出信号将包含频率为本振频率、射频频率、本振频率加上射频频率和本振频率减去射频频率的信号。

4. 混频器为了提高输出信号质量和频率准确度,会在输出信号上添加一个滤波器。

设计实现混频器的设计需要考虑多种因素,包括本振频率选择、二极管特性评估、匹配和精度要求等。

以下是一些常见的混频器设计技巧:1. 选择合适的二极管:二极管的选择与设计的频段密切相关,必须对二极管的特性进行评估并选择适当的二极管。

2. 频率匹配:为了提高混频器的效率,必须使输入端口和输出端口的阻抗相互匹配。

本振和输入信号之间的匹配非常重要,以保证最好的混频效率。

3. 滤波器选择:滤波器用于过滤混频器输出信号中的杂散信号。

同时,选择更好的滤波器将提高混频器输出信号的质量和频率准确度。

4. 精度控制:混频器在设计和调试过程中需要进行精度控制。

意味着必须对本振和射频的频率进行准确的测量,并针对结果进行必要的校准,以获得最好的混频结果。

总结混频器是通信电子系统中常用的重要组件,它扮演了将射频信号转换为中频信号的重要角色。

混频器电路设计

混频器电路是一种广泛应用于通信、雷达、测量等领域的电路,主要功能是将两路不同频率的信号合并成一路,以获得混频信号。

混频器电路的设计主要涉及以下几个方面:

1. 混频器类型选择:混频器电路通常可以选择三种类型的混频器,即互补式、抑制式和反向式混频器。

不同类型的混频器具有不同的性能特点和优缺点,需要根据具体应用场景选择。

2. 设计频率选择:混频器的输入频率范围和输出频率范围需要根据具体应用需求确定,同时考虑到混频器的增益和带宽等参数。

3. 传输线设计:混频器电路中的传输线设计对混频器的性能有很大影响。

传输线具有传输延时、传输损耗等参数,需要合理选择设计参数来优化混频器电路的性能。

4. 滤波器设计:混频器电路常常需要加入滤波器,去除不需要的频率分量,保留所需频率分量,以提高混频器电路的选择性和干扰抑制能力。

5. 电路布局与封装:混频器电路的布局和封装方式对混频器电路的性能和可靠性有很大影响,需要合理设计和选择。

综上所述,混频器电路的设计需要综合考虑电路类型、频率、传输线、滤波器及电路布局等因素,以达到优化性能、选择性和干扰抑制能力的目的。

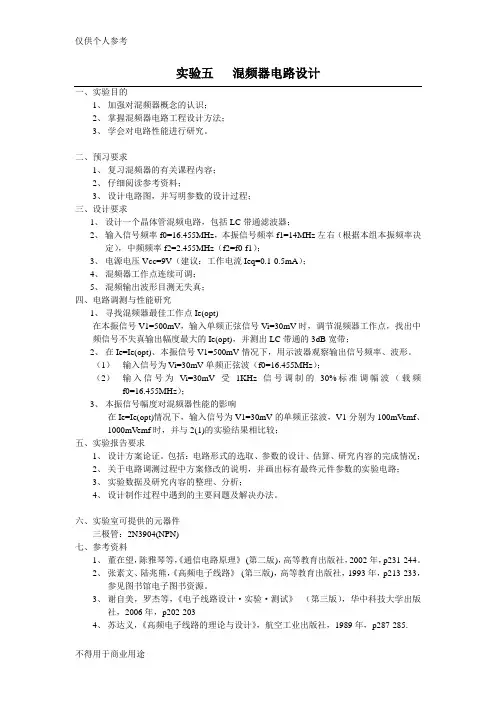

实验五混频器电路设计一、实验目的1、加强对混频器概念的认识;2、掌握混频器电路工程设计方法;3、学会对电路性能进行研究。

二、预习要求1、复习混频器的有关课程内容;2、仔细阅读参考资料;3、设计电路图,并写明参数的设计过程;三、设计要求1、设计一个晶体管混频电路,包括LC带通滤波器;2、输入信号频率f0=16.455MHz,本振信号频率f1=14MHz左右(根据本组本振频率决定),中频频率f2=2.455MHz(f2=f0-f1);3、电源电压Vcc=9V(建议:工作电流Ieq=0.1-0.5mA);4、混频器工作点连续可调;5、混频输出波形目测无失真;四、电路调测与性能研究1、寻找混频器最佳工作点Ie(opt)在本振信号V1=500mV,输入单频正弦信号Vi=30mV时,调节混频器工作点,找出中频信号不失真输出幅度最大的Ie(opt),并测出LC带通的3dB宽带;2、在Ie=Ie(opt)、本振信号V1=500mV情况下,用示波器观察输出信号频率、波形。

(1)输入信号为Vi=30mV单频正弦波(f0=16.455MHz);(2)输入信号为Vi=30mV受1KHz信号调制的30%标准调幅波(载频f0=16.455MHz);3、本振信号幅度对混频器性能的影响在Ie=Ie(opt)情况下,输入信号为V1=30mV的单频正弦波,V1分别为100mV emf、1000mVemf时,并与2(1)的实验结果相比较;五、实验报告要求1、设计方案论证。

包括:电路形式的选取、参数的设计、估算、研究内容的完成情况;2、关于电路调测过程中方案修改的说明,并画出标有最终元件参数的实验电路;3、实验数据及研究内容的整理、分析;4、设计制作过程中遇到的主要问题及解决办法。

六、实验室可提供的元器件三极管:2N3904(NPN)七、参考资料1、董在望,陈雅琴等,《通信电路原理》(第二版),高等教育出版社,2002年,p231-244。

混频器设计开题报告混频器设计开题报告一、引言混频器(Mixer)是无线通信系统中重要的组成部分,用于将不同频率的信号进行混合,产生新的频率。

在现代通信系统中,混频器广泛应用于频谱分析仪、雷达、卫星通信等领域。

本开题报告旨在介绍混频器的设计原理和方法,探讨如何提高混频器的性能。

二、混频器的基本原理混频器是一种非线性电路,其基本原理是利用非线性元件的特性将两个或多个不同频率的信号进行混合,产生新的频率。

混频器通常由非线性元件、输入端口和输出端口组成。

三、混频器设计的挑战混频器设计面临着多个挑战,其中包括:1. 频率转换损耗:混频器在将不同频率的信号进行混合时,会引入一定的损耗。

设计师需要在平衡损耗和性能之间进行权衡。

2. 非线性失真:由于混频器是一种非线性电路,会引入非线性失真。

设计师需要采取措施来减小非线性失真对系统性能的影响。

3. 噪声:混频器在信号混合过程中会引入噪声。

设计师需要优化电路结构和参数,以降低噪声水平。

4. 带宽限制:混频器的带宽限制会影响其工作频率范围。

设计师需要综合考虑带宽和性能需求,进行合理的设计。

四、混频器设计的方法在混频器设计中,有多种方法可供选择,其中包括:1. 有源混频器:有源混频器采用放大器作为非线性元件,可以提供较高的增益和较低的噪声。

然而,有源混频器的功耗较高,对电源要求较高。

2. 无源混频器:无源混频器采用二极管或场效应晶体管等被动元件作为非线性元件,功耗较低。

但是,无源混频器的增益和噪声性能较有源混频器差。

3. 双平衡混频器:双平衡混频器通过使用两个非线性元件,可以抵消一部分非线性失真和噪声。

这种设计方法可以提高混频器的性能。

五、混频器设计的优化为了优化混频器的性能,设计师可以采取以下方法:1. 选择合适的非线性元件:不同的非线性元件具有不同的特性,设计师需要根据具体应用选择合适的非线性元件。

2. 优化电路结构:通过优化电路结构和参数,可以降低非线性失真和噪声水平,提高混频器的性能。

微波混频器的设计与应用微波混频器是一种关键的射频电路元件,广泛应用于通信系统、雷达、卫星通信等领域。

本文将探讨微波混频器的设计原理、常见类型及其在通信系统中的应用。

设计原理微波混频器的设计原理基于非线性元件的特性,常用的非线性元件包括二极管和场效应管。

在微波混频器中,输入信号与局部振荡信号通过非线性元件进行混频,产生包含原始信号频率之差的新频率成分。

通过适当的滤波和放大,可以提取所需的中频信号。

常见类型1. 单平衡混频器(SB Mixer):单平衡混频器采用一个二极管或场效应管,具有简单的结构和较低的成本。

然而,其性能受到器件的非线性和失调的影响较大。

2. 双平衡混频器(DB Mixer):双平衡混频器采用两个对称的非线性元件,具有良好的抑制杂散信号的能力和较高的转换增益,适用于高要求的通信系统。

3. 集总混频器(MMIC Mixer):集总混频器集成了多个微波电路元件于一体,具有小尺寸、低功耗和高可靠性的特点,适用于微波集成电路的应用。

应用微波混频器在通信系统中具有重要的应用价值,主要体现在以下几个方面:1. 频率转换:微波混频器可以实现信号的频率转换,将高频信号转换为中频信号,以便进行后续的信号处理和解调。

2. 调频解调:微波混频器可以将调频信号解调为基带信号,用于语音、数据等信息的传输和处理。

3. 射频前端:微波混频器作为射频前端的重要组成部分,起到信号放大、滤波和混频的作用,提高通信系统的性能和灵敏度。

总结微波混频器作为通信系统中的关键元件,具有重要的设计原理和广泛的应用场景。

不同类型的微波混频器在性能和应用方面存在差异,工程师需要根据具体的需求选择合适的混频器类型,并结合其他射频电路元件进行系统设计与优化。

混频器的设计及应用一选题的意义混频器在通信工程和无线电技术中,应用非常广泛,在调制系统中,输入的基带信号都要经过频率的转换变成高频己调信号。

在解调过程中,接收的己调高频信号也要经过频率的转换,变成对应的中频信号。

特别是在超外差式接收机中,混频器应用较为广泛,如AM r 播接收机将己调幅信号535KHZ-—1605KHZ要变成为465KHZ中频信号,电视接收机将已调48. 5M 一870M的图象信号要变成38MHZ的中频图象信号。

移动通信中一次中频和二次中频等。

在发射机中,为了提高发射频率的稳定度,采用多级式发射机。

用一个频率较低石英晶体振荡器做为主振荡器,产生一个频率非常稳定的主振荡信号,然后经过频率的加、减、乘、除运算变换成射频,所以必须使用混频电路,又如电视差转机收发频道的转换,卫星通讯中上行、下行频率的变换等,都必须采用混频器。

由此可见,混频电路是应用电子技术和无线电专业必须掌握的关键电路。

二总体方案对于混频电路的分析,重点应掌握,一是混频电路的基本组成模型及主要技术特点,二是混频电路的基木原理及混频跨导的计算方 法,三是应用电路分析。

混频电路的基本组成模型及主要技术特点:混频,工程上也称变频,是将信号的频率由一个数值变成另一个 数值的过程,实质上也是频谱线性搬移过程,完成这种功能的电路就 称为混频电路或变频电路。

混频电路的组成模型及频谱分析图a 是混频电路的组成模型,可以看出是由三部分基木单元电路 组成。

分别是相乘电路、木级振荡电路和带通滤波器(也称选频网络)。

当为接收机混频电路时,其中us(t)是己调高频信号。

Ul(t)是等 幅的余弦型信号,而输出则是U i(t)为中频信号。

混频电路的基木原理:"图2中,Us (t)为输入信号,Uc(t)为本振信号。

ui (t)输出信号。

选频网络 Uj(t)U.(t)U.(t) 图aUp(t)分析:当Us (t) =Usmcos V stuc(t)=Ucmcos V ct则 Up (t) =Us (t) *Uc (t)=U sm cos 巾• stUcm cos 巾 ct=Am cos 2 st*cos 巾 ct其中:Am=Usm*lJcm对上式进行三角函数的变换则有Up(tl=Am cos 巾 st*cos ct: 1 / 2Am [cos ( V c+ 巾 s) t+COS (⑪ c 一巾 s) t] 从上式可推出,Up(t)含有两个频率分量和频为(Vc+its),差频为(巾c 一巾3。

模拟电路混频器设计在模拟电路设计中,混频器是一个重要的组件,用于将不同频率的信号进行混合。

本文将介绍模拟电路混频器的设计原理和步骤,以及一些常见的混频器电路结构。

一、设计原理在模拟电路中,混频器是将两个或多个不同频率的信号进行非线性运算,产生新的频率组合的电路。

混频器广泛应用于无线通信系统、雷达系统、视频处理等领域。

混频器的主要原理是利用非线性元件(如二极管、晶体管)的非线性特性,将输入信号的频率进行线性非线性转换,产生输出信号。

在混频器中,输入信号通常有两路,分别为射频信号(RF)和本地振荡信号(LO)。

混频器的输出信号一般为中频信号(IF)。

根据输入和输出信号的频率关系,混频器可分为上变频和下变频两种。

二、设计步骤下面以单二极管环形混频器为例,介绍混频器的设计步骤。

1. 选择工作频率首先确定混频器的工作频率范围,根据具体需求选择射频和本地振荡信号的频率。

2. 确定器件参数根据所选的工作频率,选择合适的二极管。

常用的二极管有硅二极管和砷化镓二极管,其特性参数包括最大工作频率、截止频率、反向击穿电压等。

3. 绘制电路图根据混频器的电路结构,绘制混频器的电路图。

对于单二极管环形混频器,电路图包括二极管、匹配网络和偏置电源。

4. 设计匹配网络在混频器中,匹配网络的设计非常重要。

它主要用于确保输入输出的阻抗匹配,提高混频器的性能。

匹配网络的设计需要考虑负载阻抗、源阻抗、谐振频率等因素。

5. 确定偏置电源混频器中的二极管需要合适的偏置电源,以确保其处于合适的工作状态。

偏置电源的设计需考虑二极管的导通和截止状态。

6. 进行仿真和验证完成混频器的设计后,进行电路仿真和验证。

利用电路仿真软件,验证混频器的性能指标,如增益、带宽等。

三、常见的混频器电路结构除了单二极管环形混频器,常见的混频器电路结构还包括平衡混频器、同步混频器、开关混频器等。

每种电路结构都有其特点和适用范围。

平衡混频器采用互补输入电路,可以大大降低非线性失真,适用于高要求的应用场景。

混频器设计开题报告一、引言混频器是现代通信系统中至关重要的一个组成部分,主要用于将不同频率的信号进行混合处理,以便实现带宽利用、信号处理等功能。

本文旨在介绍混频器设计的相关背景、研究目的、方法及预期结果。

二、研究背景在通信系统中,混频器扮演着频率转换的关键角色。

传统的混频器设计往往受到元件参数限制、功耗以及性能指标的影响,因此,研究新的混频器设计方法具有重要意义。

目前,混频器设计中常用的技术包括被动混频器、主动混频器和混频器阵列等。

其中,主动混频器由于其高度可控性和适应性而受到广泛关注。

本研究将聚焦于主动混频器的设计与优化,以提升其性能和指标。

三、研究目的本研究的主要目的是设计一种新型的主动混频器,通过优化参数以提高其性能和指标。

具体目标如下:1.提高混频器的转换增益,以实现更好的信号处理能力;2.降低混频器的功耗,以节省能源并延长电池寿命;3.减小混频器的尺寸和重量,以便于集成和应用于微型通信设备;4.提高混频器的抗干扰能力,以确保通信质量。

四、研究方法本研究将采用以下方法来实现混频器的设计与优化:1.了解现有的混频器设计理论和方法,包括混频器的架构、元件选择和参数控制等;2.建立混频器的数学模型,分析混频器的工作原理和性能表现;3.进行混频器的仿真实验,通过调整参数和结构来优化性能;4.进行实际混频器的制作和测试,验证仿真结果的准确性。

五、预期结果本研究的预期结果如下:1.实现混频器的转换增益提升,使其具备更好的信号处理能力;2.降低混频器的功耗,实现能源节约和电池寿命延长;3.减小混频器的尺寸和重量,提高其集成度和便携性;4.提高混频器的抗干扰能力,保证通信质量和可靠性。

六、论文结构本论文的结构安排如下:1.引言:介绍混频器设计的背景和研究目的;2.研究背景:概述混频器在通信系统中的重要性;3.研究方法:详细说明混频器设计和优化的具体方法;4.预期结果:阐述本研究的预期成果和影响;5.结论:总结本研究的核心内容和未来工作展望。

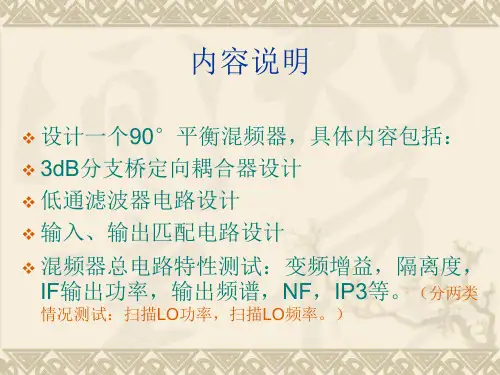

低噪放、平衡混频器设计姓名:万宵鹏一、LNA仿真设计(一)设计要求:用AVAGO公司的ATF-33143场效应管仿真设计低噪放。

指标:1.f:1805MHz-1880MHz2.NF≤0.9dB3.G≥30dB4.VSWR(in)≤25.VSWR(out)≤1.5给出设计分析过程、仿真结果、结果分析。

(二)LNA设计过程1.直流偏置设计采用Rs=0的共源极结构。

从晶体管参数文件中可以看出在Vds=4V,Ids=80mA时增益较大,噪声系数在设计范围之内。

此时,根据参数文件,Vgs=-0.5V,故采用双电源供电,得到如图所示直流偏置电路。

C C1V_DC SRC12.射频设计1)对设置了直流偏置的管子进行S 参数扫描freq, GHzd B (S (2,1))Forward Transmission, dBfreq, GHzn f (2)2)匹配网络设计测量输出阻抗如图,在中心频率1.840GHz 处, 输出阻抗 Zout 为18.576+j4.722。

应用史密斯圆图对输入端按照最小噪声匹配。

对输出进行共轭匹配。

如图:freq 1.700 GHz 1.710 GHz 1.720 GHz 1.730 GHz 1.740 GHz 1.750 GHz 1.760 GHz 1.770 GHz 1.780 GHz 1.790 GHz 1.800 GHz 1.810 GHz 1.820 GHz 1.830 GHz 1.840 GHz 1.850 GHz 1.860 GHz 1.870GHzZin118.785 + j3.325 18.768 + j3.427 18.751 + j3.528 18.735 + j3.629 18.719 + j3.730 18.703 + j3.830 18.688 + j3.931 18.673 + j4.031 18.658 + j4.130 18.643 + j4.230 18.629 + j4.329 18.616 + j4.427 18.602 + j4.526 18.589 + j4.624 18.576 + j4.722 18.563 + j4.820 18.551 + j4.918 18.539+j5.015输入匹配网络输出匹配网络得到如下图所示电路仿真并运用调谐工具对输入匹配网络调谐,得到结果如图显然增益未达到设计要求,通过计算或者查看管子的技术手册可以看到最大转换功率增益为19dB左右,因此必须采用两级放大结构。

项目 7 混频器分析与设计本项目重难点:(1)混频器的工作原理、技术指标;(2)混频器三阶截点、1 dB 压缩点、隔离度等主要参数;(3)混频器的电路结构形式;(4)混频器电路的一般设计方法。

(5)混频器三阶截点、1 dB 压缩点的测试方法;(6)利用ADS 仿真软件进行混频器电路仿真设计。

任务 1 混频器原理、主要技术指标分析与测试重难点分析:(1)混频器的工作过程以及输出信号类型;(2)混频器的主要技术指标及其测试方法。

一、混频器工作原理混频器的工作过程可以用图7.1表示。

从混频器的工作过程可知:(1)输出中频调幅波与输入高频调幅波规律完全相同,即载波振幅的包络 形状完全相同,唯一的差别是载波频率不同。

(2)从频谱上看,输出中频信号与输入高频信号的频谱结构相同,只不过 在频谱上搬移了一个位置。

(3)在射频/微波工程中,输出信号可能为以下三个频率之一: ① 差频(低中频)或超外差, I L s f f f =- ,称为下变频。

② 和频(高中频), I s L f f f =+ ,称为上变频。

图 7.1 混频器工作过程示意图③ 谐波混频, s L f nf f =- 。

(4)一般用于振幅调制与解调的电路均可用于混频,需要改变的只是输入、 输出回路和输出滤波器的参数。

二、混频器电路主要技术指标1.变频增益(变频损耗)定义:混频器的输出中频信号电压 I U (或功率 I P )与输入信号电压S U (或功 率 S P )的比值。

电压增益: IU SU A U = (7.1) 功率增益: IP S P G P =(7.2) 电压增益与功率增益的关系:2 2 S I I L P U 2 S L S S () / () / R P U R G A P R U R === 射频口阻抗 中频口阻抗按照增益划分,混频器可分为有源混频器(增益大于1)和无源混频器(增 益小于1)。

若用分贝表示增益大小,则IC S 10lg P G P = 或 IC S 20lg U A U = (7.3)式中,射频输入功率 S P 和中频输出功率 I P 均以dBm为单位。

混频器设计4.1引言无线传感网(WSN,Wireless Sebnsor Networks)就是由部署在监测区域内的大量的廉价微型传感器节点组成,通过无线通信的方式形成的一个多跳自组织网络,它是一种全新的信息获取平台,能够实现监测和采集网络分布区域内的各种检测对象的信息。

由于无线传感网的广泛发展,应用于无线传传感的技术也得到广泛的发展,下混频器是无线传感网中的关键模块,它的性能与各种通信系统的通信质量密切相关。

混频器电路按非线性器件性质的不同,分为无源混频器电路和有源混频器电路。

无源混频器电路结构相对来说比较简单,设计周期也不用太长,有较高的性价比,其中最主要的优点是无源结构混频器不需要电源电压,并且当理想情况下时,并没有静态功耗存在,而且具有好线性度性能。

但是无源混频器也存在很多不足之处,无源混频器电路有插入损耗存在,一般可采用后置有源电路提供足够的增益。

有源混频器需要外接电源来提供一定增益,虽然需要消耗一定的功率,但可以使整个系统的增益在集成电路中得到提高。

有源混频器的转换增益和端口的隔离度都比无源混频器要大的,但是它的噪声系数比较小,而且有源混频器所消耗功率较大,线性度也比无源混频器差。

按照组成混频器的不同电路结构[27],可以分为平衡混频器、单端混频器。

单端混频器电路结构简单,但性能较差。

平衡混频器又可分为单平衡混频器和双平衡混频器两种,它们具有噪声小、灵敏度高、抗干扰能力强及频带宽等优点。

就单平衡结构和双平衡结构而言,双平衡混频器结构具有更好的性能,平衡结构有更好的端口隔离度,本振电压和输入信号电压不会通到中频输出端,也即本振端口和输入是隔离的。

单管跨导型混频电路、单平衡型混频电路和吉尔伯特双平衡型混频电路等是有源混频器比较常见的电路形式。

二极管双平衡型混频电路和无源场效应管混频电路等是无源混频器比较常见的电路形式。

本文设计的下混频器由于采用一级变频,直接从2.4Gz下变频到40M,所以性能肯定是受到影响的,相比于多级变频器,各项指标一般,但是大大降低了成本。

因此在要求并不严苛的情况下,一级混频器拥有比较高的性价比,是比较合适的选择。

在比较几种混频器结构后,决定采用Gilbert混频器作为原型电路结构。

为了能够提供更好地性能,采用电流注入技术,使噪声系数和增益同时得到改善。

.4.2原理分析混频器在接收机系统中主要负责频率的搬移功能,在频率上起加法器或减法器的作用,频域上加减法通过时域上的乘积获得,因此,频率搬移实现的基本理论模型可以描述为:(A cosω1t)(Bcosω2t) =AB2[cos(ω1−ω2)t+cos(ω1+ω2)t] 上式A cosω1t和Bcosω2t分别代表两个输入信号,只要电路中构成这两个信号的乘积,理论上就可以实现频率的搬移功能。

从上式可以看出,混频器模块至少包含三个信号:两个输入信号和一个输出信号,通常而言,混频器的输入信号分别定义为射频信号RF(Radio Frequency),频率记为ωRF和本振信号LO(Local Oscillator),频率记为ωLO,混频器的输出信号定义为中频信号IF (Intermediate Frequency),频率记为ωIF。

所以上式可以变为混频器的模型:(A LO cosωLO t) (A RF cosωRF t) =A LO A RF2[cos(ωLO−ωRF)t+cos(ωLO+ωRF)t] 式中A LO表征本振信号的振幅,A RF表征射频信号的振幅。

从上式可以看出,混频器产生的中频信号包含有两个频率分量:ωLO−ωRF和ωLO+ωRF,混频器的应用领域不同,其他干扰频率分量一般采用滤波器进行滤波,本文讨论的混频器中频输出采用差频分量,即ωLO+ωRF。

当ωIF<ωRF时,混频器称为下变频,输出低频中频信号。

当ωIF>ωRF时,输出高中频信号,本文所提出的混频器设计技术主要应用于下变频设计。

目前,混频器电路主要以下几种方法实现本振信号和射频信号的乘积:利用电路或器件的非线性特性,直接构成电路乘法器和采用开关调制构成信号时域上的乘积。

1)电路或器件的非线性特性实现频率转换。

这类混频器最典型的是二极管混频器,主要利用二极管电压到电流的指数特性。

2)构成电路乘法器。

这类混频器主要是把模拟乘法器的电路结构应用于射频领域的频谱搬移,最为典型的吉尔伯特乘法器的应用,到目前为止,吉尔伯特混频器是应用最为广泛的电路结构。

3)开关调制实现频率和变换。

开关调制混频器数学模型。

S LO,S RF和S IF分别表示本振信号,射频信号和中频信号。

在本振信号的作用下,IF信号以本振信号频率在+S RF和-S RF之间来回切换,若射频信号和本振信号定义如下:S RF=A RF cos(ωRF t)S LO={+1,0≤t<π⋰ωLO−1 ,π⋰ωLO≤t<2π⋰ωLO中频信号为:S IF=S LO S RF将S LO进行傅里叶级数变换展开得中频输出会出现以本振信号奇次谐波为中心的上下边带变频分量。

虽然吉尔伯特电路原是用于模拟乘法器,但是现在,吉尔伯特混频器已发展成为开关型混频器的典型.电路,吉尔伯特单元电路的混频器成为当前混频器领域中最主流的电路结构。

4.3 结构选择混频器结构决定了它的性能,因此根据不同的指标选择最合适的结构显得尤为重要。

本文要求设计高线性度、高增益、低噪声结构简单、功耗低的下变频混频器。

无源混频器结构简单,频带宽,功耗低,而且可以获得很高的线性度,但其他性能得不到保证,显然并不适合本设计。

而有源混频器的变频增益较高,噪声系数小,端口隔离度也比较好,虽然线性度差一些,但是经过合理的设计,还是能得到优化的,所以选择有源混频器。

有源混频器又可以分为单平衡和双平衡,考虑到单平衡虽然易于设计,但是隔离度差,所以选择更复杂一些的双平衡混频器。

其中,Gilbert混频器最为主流。

在传统的基础上,为了提高变频增益,同时具有较低的噪声系数,我们采用选择采用电流注入结构,在跨导级电流不变的情况下,减小开关机电流。

注入电流源用两个PMOS管M7、M8实现,这样可获得较高的IIP3。

双平衡混频器常用电阻作为负载,这里就有一个问题,如果要提高增益,要么提高跨导,幺儿增大负载。

然而无论怎样做,都会使得负载上的压降过大,有可能使得晶体管工作在非饱和区。

为了减少负载上的直流压降,解决电压余度不足的问题,除了使用电流注入的办法,我们采用电容电阻并联的方法作为负载。

综上所述,得到电路图1.1。

图4.1 本设计所采用的电路结构4.4电路建模4.4.1 仿真环境,采用工艺以及仿真项目采用平台为Cadence-Spectre,采用工艺为SMIC-0.18μm,仿真项目为增益G,噪声系数NF,输入1dB压缩点以及输入三阶截止点IIP34.4.2电路结构及参数所设计的混频电路图如4.1所示,各个MOS管和无源器件如表4.1,4.2,4.3所示。

图4.2 混频器电路图表4.1 MOS管参数表4.2 电阻参数表4.3电容参数4.5项目及结果4.5.1仿真偏置(1)电流设置如表4.4所示表4.4 偏置电流设置4.5.2仿真结果(1)变频增益对本振的仿真该仿真通过pss+pac的仿真。

其中pss主要是作本振大信号的周期稳态分析,可以在时变工作点上线性化电路。

pac则在pss仿真后,作为小信号分析。

此处,射频端口设置为50Ω的电阻,dc type。

PAC magnitude设置为1v。

中频输出端口设置为1MΩ,dc type,中频输出端口的设置在以后的仿真中保持不变。

pss仿真和pac仿真的参数设置如图1.3所示。

其中,plo(单位dBm)为本征的功率值。

仿真结果如图4.4所示。

图4.3 pss和pac仿真参数设置图4.4 射频信号为2.4G时变频率增益对本振功率的扫描从仿真的结果来看,在本振功率为-5dBm的情况下,转换增益最大。

(2)变频增益的仿真RF端口设置与上面设置相同,本征端口设置为2.44GHz,-5dBm。

仿真方法依旧是采用pss+pac,只是在pss中不作参数扫面,pss和PAC设置如图1.5所示图4.5pss和 PAC仿真参数设置得到的转换增益曲线如图4.6所示,横轴为输出信号的频率。

图4.6 转换增益曲线从仿真的曲线可以看到,在单个信道中转换增益约为12.89dBm。

(3)噪声系数的仿真同上面的仿真相似,需将RF端口PAC magnitude 1V改设为PAC magnitude(dBm)为-30.仿真使用pss+pnoise仿真,其中pss的仿真设置同上,图1.7给出pnoise的仿真设置。

其中输出选择PORT2,即中频信号输出端口。

输入选择PORT0,即射频信号输入端口。

图4.7 pnoise仿真参数设置仿真结果如图4.8所示。

从图中可以看出,中频为40MHz时噪声系数为17.74dB图4.8 pnoise仿真结果(4)输入1dB压缩点和IIP3的仿真仿真输入1dB压缩点采用PSS仿真,RF端口改为sine type,频率设置为2.4GHz。

Amplitude(dBm)设为prf。

PSS设置如图4.9所示。

图4.9 PSS仿真参数设置得到输入1dB压缩点曲线如图4.10所示。

图4.10 1dB压缩点曲线从图中可以看出1dB压缩点约为-13.7416dB。

仿IIP3时,RF端口设置为”sine”,在“PAC Magnitude(dBm)”栏输入pf作为射频输入功率变量。

然后,PSS和PAC设置如图4.11所示。

图4.11 IIP3仿真器设置对于40M的基波。

2.44G的本振及射频双音信号2.4GHz和2.401GHz,-59和-61的边带代表了中频输出的一次谐波1M(61*40-2401=39M)和3次谐波(2401-59*40=41)。

完成设置进行仿真得到如图4.12所示。

图4.12 IIIP3仿真曲线图由图可见,三阶互调截止点约为-9.59dbB。

4.6 结果分析及改进4.6.1 仿真结果仿真结果如表1.5所示。

表4.5 仿真结果4.6.2 反思及改进(1)噪声系数过大,在没有采用电流注入技术时可以仿到12dB,但是增益太小,可能是PMOS管引入了额外的噪声。

(2)由于时间仓促,本此设计没有设计偏置电路。

偏置电路对混频器核心模块的影响并没有去分析以及仿真印证。

(3)应该在输出端做眼跟随器,防治后级输入阻抗过小降低增益。