射频电路中降低电磁辐射思索论文

- 格式:doc

- 大小:27.00 KB

- 文档页数:7

电磁波实验中的电磁射频辐射防护措施电磁波实验是现代科学研究中重要的一环,通过对电磁波的观测与分析,我们可以了解更多关于宇宙和物质的奥秘。

然而,在进行电磁波实验的过程中,我们必须重视电磁射频辐射带来的潜在危害,采取相应的防护措施,确保实验的安全进行。

首先,对于电磁波实验中产生的射频辐射,我们需要了解其特性。

射频辐射是指高频电磁波辐射,如微波、射频等。

这些高频电磁波具有较大的穿透力和辐射能量,对人体和设备造成的潜在威胁不容忽视。

针对电磁射频辐射,我们可以从多个方面进行防护措施。

首先,实验室环境的设计十分重要。

实验室应选址远离居民区和敏感设备,以减少辐射波对外部环境的影响。

实验室必须有稳定的电源和接地系统,以减少漏电和离子电流的带来的辐射风险。

同时,建议实验室采用混凝土金属屏蔽结构,形成“远离射频区”,有效阻隔射频辐射。

其次,操作者的个人防护也至关重要。

为避免电磁辐射对人体的伤害,实验操作者应佩戴专业的电磁辐射防护服,并正确使用。

电磁辐射防护服通常由导电纤维制成,能够有效阻隔电磁波的穿透。

此外,操作者还应保持正确的姿势和距离,避免过近接触辐射源。

在实验进行时,需要严格遵守操作规程,操作者应避免长时间暴露在辐射区域内。

进一步地,实验设备和仪器的防护也不容忽视。

对于产生强烈高频电磁波的设备,我们需要采取适当的屏蔽措施,以减少其辐射到周围环境的程度。

对于辐射源周围人员和敏感设备,应设置相应的保护壳,以降低电磁辐射的影响。

除了上述方面的防护措施,我们还可以采取一些其他的技术手段来减少电磁射频辐射的影响。

例如,可以使用屏蔽光纤等替代无线信号传输,减少辐射带来的影响。

在实验室的电磁波设置上,合理规划和优化设备的摆放位置,避免产生电磁辐射的交叉干扰。

最后,定期的安全检查和辐射监测也是确保实验室安全的重要手段。

实验室应该配备专业的仪器设备,定期对实验环境中的辐射水平进行监测和评估。

如有超标情况,需及时采取相应的措施,确保辐射水平在安全范围内。

1、引言随着电子系统的日益精密、复杂及多功能化,电子干扰问题日趋严重,它可使系统的性能发生变化、减弱,甚至导致系统完全失灵。

特别是EMI/RFI(电磁干扰/射频干扰)问题,已成为近几年电子产业的热点。

为此,不少国家的专业委员会相继制定了法规,对电子产品的电磁波不泄露、抗干扰能力提出了严格规定,并强制执行。

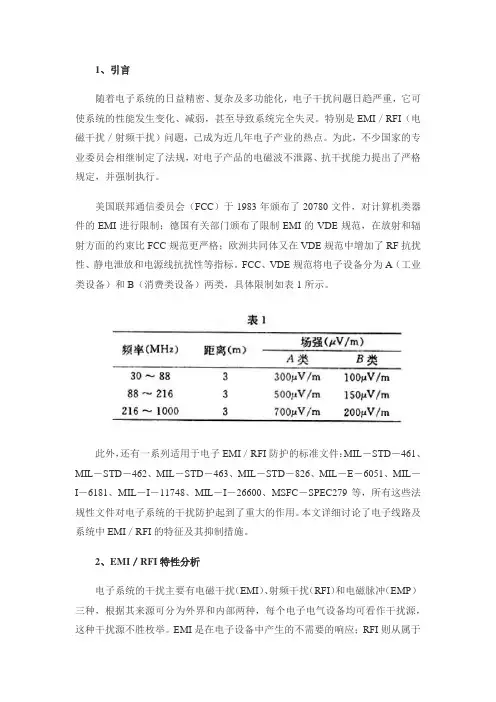

美国联邦通信委员会(FCC)于1983年颁布了20780文件,对计算机类器件的EMI进行限制;德国有关部门颁布了限制EMI的VDE规范,在放射和辐射方面的约束比FCC规范更严格;欧洲共同体又在VDE规范中增加了RF抗扰性、静电泄放和电源线抗扰性等指标。

FCC、VDE规范将电子设备分为A(工业类设备)和B(消费类设备)两类,具体限制如表1所示。

此外,还有一系列适用于电子EMI/RFI防护的标准文件:MIL-STD-461、MIL-STD-462、MIL-STD-463、MIL-STD-826、MIL-E-6051、MIL-I-6181、MIL-I-11748、MIL-I-26600、MSFC-SPEC279等,所有这些法规性文件对电子系统的干扰防护起到了重大的作用。

本文详细讨论了电子线路及系统中EMI/RFI的特征及其抑制措施。

2、EMI/RFI特性分析电子系统的干扰主要有电磁干扰(EMI)、射频干扰(RFI)和电磁脉冲(EMP)三种,根据其来源可分为外界和内部两种,每个电子电气设备均可看作干扰源,这种干扰源不胜枚举。

EMI是在电子设备中产生的不需要的响应;RFI则从属于EMI;EMP是一种瞬态现象,它可由系统内部原因(电压冲击、电源中断、电感转换等)或外部原因(闪电、核爆炸等)引起,能耦合到任何导线上,如电源线和电话线等,而与这些导线相连的电子系统将受到瞬时严重干扰或使系统内的电子电路受到永久性损坏。

图1给出了常见EMI/RFI的干扰源及其频率范围。

图1、常见干扰源及频率范围2.1、干扰途径任何干扰问题可分解为干扰源、干扰接收器和干扰的耦合途径三个方面,即所谓的干扰三要素。

射频电路中的电磁兼容问题分析及解决方案随着现代通讯技术的不断发展,射频电路的应用越来越广泛,但同时也带来了各种电磁兼容性问题。

这些问题严重影响了电路的性能和可靠性,需要采取一些措施来降低电磁干扰和提高电路的电磁兼容性。

本文将从射频电路中的电磁兼容问题入手,分析其原因,并提出一些解决方案。

一、射频电路中的电磁兼容问题在射频电路中,电磁兼容问题常常表现为电磁干扰和电磁泄漏。

电磁干扰(EMI)指电磁场对电路的干扰,可以使电路系统出现误差、噪声、振荡等现象,严重影响电路的性能和可靠性。

电磁泄漏(EMC)则是指电路的辐射和传导干扰影响其他电路设备的工作,如毫米波雷达和微波电子设备等。

二、射频电路中电磁兼容问题的原因射频电路中的电磁兼容问题主要是由以下原因引起的:1、电磁辐射电磁辐射是指电路的信号频率与基波频率相同或者倍频频率接近电磁波向外辐射。

这种辐射会造成电磁泄漏干扰,破坏其他电路设备的正常工作。

2、电磁谐振电磁谐振是指电路中的元器件、线路和电路板产生的电磁场彼此作用产生振荡。

这种振荡会使电路变得不稳定,容易产生电磁干扰。

3、电磁传导电磁传导是指电路中元器件中出现的电磁场通过共同的地或信号线等媒介对周围的干扰。

这种干扰会产生电压干扰和电流干扰,导致电路性能急剧下降。

三、射频电路中电磁兼容问题的解决方案为降低电磁兼容性问题,我们可以采取以下措施:1、选择合适的元器件和材料射频电路中的元器件和材料需要选择品质较好的,这些元器件和材料应具有较高的带宽和品质因子,同时其抗EMI/EMC的性能也要较强。

2、设计合理的线路布局线路布局应尽量简单,可以通过增加两极滤波器、避免电路的环路、尽量缩小线路面积等,降低电路的电磁能散发。

例如,采用单端布线并避免使用复杂的结构,设计较短的布线线路等,可以有效降低电磁兼容性问题。

3、增加电磁隔离屏蔽结构影响电路性能的小波长电磁辐射必须被隔离,这可以通过使用较好的射频电缆,尽量使用电容式/吸收材料垫子和EMC隔离屏蔽等方法来实现。

Electronic Technology •电子技术Electronic Technology & Software Engineering 电子技术与软件工程• 81【关键词】射频电路 EMI 抑制 EMC在信号传输的过程中,射频电路实际上会产生明显的电磁干扰问题。

就射频电路本身来说,并不具备较强的抗干扰能力,同时如果不同的射频电路在相同环境下运行,其相互之间也会出现信号干扰问题。

所以,必须采用恰当的方式,对射频电路的电磁干扰进行合理抑制,保证信号能力高质量实现传输的目的。

1 射频电路EMI抑制的需求分析在射频电路信号传输的过程中,很容易发生EMI 问题,而结合EMI 的三要素,要想实现EMI 抑制的目标,必须明确以下几方面的内容:(1)以干扰源的角度进行分析,射频电路通常都是较高的频段,所以其中会存在高频分量,进而出现较明显的空间辐射能力;(2)以路径耦合的层面进行分析,射频电路在运行过程中,其所产生的EMI 问题,基本上都是通过电磁场、磁场、电场等方式,完成传播的。

(3)以保护敏感设备的视角进行分析,射频电路中包含很多具有敏感特征的器件,如压控振荡器、混频器、射频放大器等,所以就会出现EMI 问题,影响信号传输的质量。

结合以上三方面的分析,可以确定射频电路中EMI 问题是最为常见的、明显的现象,必须将EMC 等技术方式应用在其中,进而有效避免射频电路出现EMI 问题。

2 射频电路EMI抑制和EMC的实践2.1 EMC的设计结合上述对射频电路中EMI 的分析,可以确定EMI 抑制具有较强的必要性、迫切性。

在这样的情况下,相关人员可以将EMC 应用其中,但是需要掌握EMC 的设计方式,进而充分发挥EMC 的作用,实现EMI 抑制的目的。

射频电路EMI 抑制和EMC 文/吕磊 刘小杰 李轶南 尹德森就EMC 的设计来说,其具体的方式主要包含以下几方面:(1)在设计射频电路的环节中,不仅需要保证功能指标的合理性,也必须最大程度对信号的高频分量进行合理降低。

电路电磁辐射与抗干扰设计如何减少电路的辐射和干扰电路的电磁辐射和抗干扰设计是电子系统设计中非常重要的一环。

电磁辐射和干扰对于电子设备的性能和可靠性都有着直接的影响。

本文将讨论电路电磁辐射和干扰的产生原因以及如何有效减少电路的辐射和干扰,以提高电路的性能和可靠性。

一、电路电磁辐射的原因电路的电磁辐射主要来源于电流和电压的不稳定变化以及信号传输过程中所产生的高频噪声。

当电流和电压在电路中快速变化时,就会产生辐射电磁波。

此外,电路中的开关、晶体管等元件在开关过程中也会产生辐射电磁波。

这些辐射电磁波可能对其他电子设备造成干扰,降低设备的性能。

二、电路电磁辐射的影响电磁辐射对电子设备可能造成的影响包括:降低设备的灵敏度和抗干扰能力、增加误码率、干扰周围电子设备等。

在无线通信、雷达、医疗设备等领域尤为重要,对电磁辐射的控制要求严格。

三、减少电路的辐射和干扰的方法1. 地线和电源线的处理: 尽量使用短而粗的导线,以降低线路的电阻和电感,减少辐射和干扰。

此外,地线和电源线应尽可能分离布置,以减少彼此之间的干扰。

2.屏蔽和隔离: 对于特别敏感的电路,可以采用屏蔽罩或隔离罩进行屏蔽和隔离,防止辐射电磁波的泄漏。

3.滤波器的应用: 在电源线和信号线上安装滤波器,可以有效地阻止高频噪声和干扰信号的传播,减少辐射。

4.地线的设计: 地线是电路中非常重要的组成部分,合理的地线设计可以降低辐射电磁波的产生。

在地线的布线过程中,可以采取等距离引出的方法,减少环形地线的产生。

5.降低开关频率: 将高频电路的频率尽量降低,可以减少辐射电磁波的产生。

同时,也可以选择较低频率的元件来进行设计。

6.选择低辐射元件: 在设计过程中,选择低辐射元件可以有效降低电路的辐射。

7.良好的布局设计: 合理的布局设计可以减少线路之间的相互干扰,降低辐射电磁波的产生。

8.综合考虑整个系统: 在设计电路时,需要综合考虑整个系统的特性,尽量减少辐射和干扰。

微波射频电路设计中的电磁兼容性考虑微波射频(RF)电路设计在现代通信和电子系统中扮演着至关重要的角色。

然而,随着设备日益复杂和密集,电磁兼容性(EMC)的考虑变得愈发重要。

本文将探讨在微波射频电路设计中的电磁兼容性问题,并提出解决方案,以确保系统的稳定性和可靠性。

**电磁兼容性简介**电磁兼容性是指不同电子设备之间以及设备与环境之间相互影响的能力。

在微波射频电路设计中,这意味着需要考虑到电磁辐射、电磁干扰和电磁感受性等问题。

如果不加以控制和管理,这些问题可能导致系统性能下降、通信中断甚至设备损坏。

**电磁兼容性考虑因素**1. **电磁辐射:** 微波射频电路中的高频信号会产生电磁辐射,可能干扰周围设备和系统。

因此,设计中需要考虑合适的屏蔽措施,如使用屏蔽罩、地线和滤波器等。

2. **电磁干扰:** 外部电磁干扰可能对微波射频电路造成干扰,影响其正常运行。

因此,应采取措施来减小对外部干扰的敏感度,如优化布局、使用抑制电路和差模输入等。

3. **电磁感受性:** 微波射频电路本身也可能对外部电磁干扰产生敏感性。

因此,设计中需要考虑到提高系统的抗干扰能力,如优化接地设计、降低电路的共模干扰等。

**解决方案**1. **优化布局设计:** 合理布局电路元件,减小信号线路长度,降低电磁辐射和电磁干扰的可能性。

2. **使用屏蔽材料:** 在关键部位使用金属屏蔽罩或屏蔽材料,有效阻挡电磁辐射和外部干扰。

3. **地线设计:** 设计合适的地线系统,确保良好的接地,降低共模干扰和地回路干扰。

4. **滤波器设计:** 在输入输出端口添加滤波器,滤除不需要的频率成分,减小电磁干扰。

5. **差模输入设计:** 使用差模输入电路结构,提高对共模干扰的抑制能力。

**结论**在微波射频电路设计中,电磁兼容性考虑至关重要。

通过合理的设计和措施,可以有效减小电磁辐射、电磁干扰和电磁感受性,确保系统的稳定性和可靠性,为现代通信和电子系统的发展提供良好的保障。

射频论文(5篇模版)第一篇:射频论文关于RFIC技术现状和发展综述Xxx 【摘要】无线通信技术的迅猛发展带动了信息产业的整体发展,作为无线传输设备核心器件的射频集成电路(RFIC)不断朝着高性能、高集成度、低功耗和低成本方向发展。

CMOS 工艺有着先天的优势:高集成度(与基带、数字信号处理模块工艺兼容)、低成本,而且CMOS 随着特征尺寸的缩小,射频性能不断提高,高精度的射频器件模型及RFIC 设计成为当前的研究热点。

近十年来,射频无线移动通信技术的发展显得尤为迅猛。

其中起决定作用之一的技术就是RFIC技术。

随着第三代移动通信体制的开始,对新一代无线通信射频集成电路(RFIC)的性能、材料和工艺等都提出了新的技术要求。

本文总结了无线通信移动终端RFIC的发展历程和现状,对关键技术进行了探讨,,最后展望了未来的发展前景。

【关键词】射频集成电路,CMOS,发展,现状,工艺,材料Status and development of technology on RFICOverviewTao Wen 200808030324 Beijing Union University Institute of information Department of Communication Engineering 【Abstract】Wireless communication technology driven the rapid development of information industry whole development, as wireless transmission equipment core device of radio frequency integrated circuit(RFIC)toward high performance, high integration, low power consumption and low cost development.CMOS technology has advantage of high integration degree:(with a baseband, digital signal processing module processes compatible), low cost, and CMOS as the feature size shrinks, RF continuously improve performance, high precision of the RF device model and RFIC design has become aresearch e nearly ten years, wireless mobile communication technology development is swift and violent.Which plays a decisive role in one of the technology is RFIC technology.With the third generation mobile communication system to start, on a new generation of wireless communication RF integrated circuit(RFIC)performance, materials and process are put forward new requirements.This article summarizes the wireless communication mobile terminal RFIC development course and the present situation, the key technologies are discussed, finally, forecasts the future development foreground.【Key words】radio frequency integrated circuit, CMOS, development, current situation, technology, material引言:射频集成电路(RF IC,radio frequency integrated circuits)在近十年内得到广泛重视,并在无线通信领域取得快速发展。

电路中的电磁辐射减小辐射干扰与抗干扰措施电路中的电磁辐射:减小辐射干扰与抗干扰措施电磁辐射在现代电子设备中普遍存在,它不仅会对电路本身造成干扰,还可能对周围的设备和人体健康产生不良影响。

因此,减小电路中的电磁辐射、降低辐射干扰、采取抗干扰措施成为电子工程师和研究人员的重要任务。

本文将探讨一些常见的电磁辐射减小和抗干扰措施。

1. 电磁辐射的来源和危害电磁辐射的主要来源包括电源线、信号传输线以及电子设备本身的内部部件。

辐射主要体现在电磁波的无线电频段上,其中包括无线电、微波和红外线等。

长期暴露在电磁辐射环境下可能对人体健康产生不良影响,如引起电离辐射、热效应以及生物电磁效应等。

2. 电磁辐射减小的方法为减小电磁辐射带来的干扰,我们可以采取以下方法:2.1 电源线滤波通过在电源线中添加滤波器,可以有效地滤除电源中的高频噪声,减小电磁辐射。

这样的滤波器通常使用电感元件和电容元件的组合,能够在一定频率范围内抑制噪声。

2.2 信号线屏蔽对于信号传输线,我们可以采取屏蔽的方法来减小电磁辐射。

屏蔽线通常由导电材料制成,例如金属丝编织层、金属箔等,能够有效地抵挡外界的干扰信号。

2.3 地线和屏蔽地面良好的接地系统可以有效地减小电磁辐射。

通过建立良好的地线和屏蔽地面,可以将电流导向地,减少电磁辐射。

3. 抗干扰措施除了减小电磁辐射的方法外,我们还可以采取一些抗干扰措施来应对外界干扰。

3.1 电磁屏蔽在设计电路时,我们可以采用电磁屏蔽技术,将敏感部件包裹在金属屏蔽罩中,有效地隔离外界的电磁干扰。

3.2 降噪电源设计设计降噪电源对于电路抗干扰非常重要。

采用稳压电源或是添加滤波器等措施,可以将电源干扰降到最低。

3.3 接地设计良好的接地设计可以有效地减少共模干扰。

要保证接地系统的导通性,并避免接地回路中的回流电流。

4. 结论在电路设计和应用过程中,减小电磁辐射的问题是不可忽视的。

通过使用滤波器、屏蔽线、良好的接地系统等方法,可以有效地减小电磁辐射带来的干扰。

射频辐射的危害和预防范文射频辐射是当今社会普遍存在的一种电磁辐射形式,其来源包括手机、微波炉、电视机、无线路由器等家电设备。

然而,射频辐射对人体健康可能带来一定的危害。

为了更好地预防射频辐射的潜在伤害,我们需要了解其危害和采取相应的预防措施。

首先,射频辐射会对人体产生热效应。

许多家电设备在运行时会产生射频电磁场,使人体组织受到加热。

长时间接触过量的射频辐射可能导致热量积累,对人体产生不利影响。

严重情况下,可能引起中暑甚至神经系统损伤。

其次,长期暴露在射频辐射中可能对人体的生殖系统造成一定影响。

研究表明,男性长时间使用手机时,其精子的数量和活力明显下降。

而女性更容易出现月经不调、乳腺疾病等问题。

此外,射频辐射还在一定程度上增加了癌症的发病风险,特别是脑部肿瘤的发生。

为了预防射频辐射对人体健康的潜在伤害,我们可以采取以下几种措施:第一,减少使用射频辐射源。

我们可以适量减少使用手机、电视等射频辐射较强的家电设备。

尽量采用有线网络而不是无线网络,以减少无线设备的辐射程度。

第二,远离射频辐射源。

当使用手机时,可以使用耳机来减少辐射对头部的直接影响。

此外,避免将手机放置在靠近身体的地方,可以有效降低电磁辐射对人体的影响。

第三,合理安置电器设备。

在家庭布局中,尽量将无线路由器等设备放置在远离人体活动区域的地方,避免辐射对人体的直接影响。

第四,加强个人防护措施。

选择低辐射的电器设备,尽量避免接触高辐射强度的设备。

外出时,可以选择佩戴抗辐射的衣物或使用抗辐射的产品来减少辐射对身体的影响。

第五,定期进行辐射检测。

可以请专业机构对家庭中的电器设备进行辐射检测,了解辐射情况,并根据检测结果来采取相应的防护措施。

总之,射频辐射对人体健康带来的潜在危害不可忽视。

为了减少对人体的影响,我们应该采取相应的预防措施。

通过减少使用射频辐射源、远离射频辐射源、合理安置电器设备、加强个人防护措施和定期进行辐射检测,可以降低射频辐射对健康的潜在风险。

电磁辐射污染与防治摘要:电磁辐射污染直接威胁人类健康。

本文介绍了电磁辐射的物理特性,污染源的分类以及传播途径,指出了电磁辐射对人体的危害及对电子设备的干扰,最后给出一些对电磁辐射污染的防治措施。

关键词:电磁辐射;污染源;危害;防治1、电磁辐射的物理特性任何交流电在其周围空间都会产生交变的电场,交变的电场又产生交变的磁场,交变的磁场又反过来会产生新的交变电场。

这种交变的电场与交变的磁场相互垂直、以源为中心向周围空间交替的产生且以一定的速度传播的波,称为电磁辐射(也称电磁波)。

确切的说电磁辐射是一个包括广播频率(220MHz~3600MHz)、电视频率(30MHz~300 MHz)和无线电频率(30MHz以下)的广泛的波。

从波动学的观点来描述电磁辐射时其基本物理量有:波长:沿着波的传播方向,两个相邻的同相位质点间的距离;单位为米(m)。

周期:物体完成一次全振动所需的时间;T单位为秒(s)。

频率:单位时间内所完成的周期数;单位为赫兹(Hz)。

三者之间的关系为:f=1/T=c/λ。

在远离场源的地方,电场强度与磁场强度在量值上的关系:ε01/2E=?1/2H式中ε=8.85×10-12库仑2/牛顿·米2,是真空中的介电常数;μ0=4π×10-7牛顿/安培2,是真空中的磁导率。

E=(μ/ε0)1/2H=377H,E⊥H且都与传播方向垂直。

2、电磁辐射污染源的分类影响人类生活环境的电磁辐射根据其污染源大致可分为两大类:天然电磁辐射污染源和人为电磁辐射污染源。

2.1天然电磁辐射污染源天然的电磁辐射污染来自于地球的热辐射、太阳热辐射、宇宙射线、雷电等,是由自然界某些自然现象所引起的(表1:天然电磁辐射污染源)。

表1天然电磁辐射污染源分类来源大气与空气污染源自然界的火花放电、雷电、台风、高寒地区飘雪、火山喷发……太阳电磁场源太阳黑子活动与黑体放射……宇宙电磁场源银河系恒星的爆发、宇宙间电子的移动……2.2人为电磁辐射污染源人为电磁辐射污染源产生于人工制造的若干系统,如:电子设备、电气装置等,主要来自广播、电视、雷达、通讯基站及电磁能在工业、科学、医疗和生活中的应用设备。

如何解决电路中的电磁辐射问题电磁辐射是当电流通过导线、电缆或电子器件时产生的一种辐射现象。

在现代电子设备和通信系统中,电磁辐射问题日益突出,它不仅对设备自身的正常运行产生影响,还可能对周围环境和人体健康造成潜在威胁。

因此,解决电路中的电磁辐射问题至关重要。

本文将探讨一些解决方案,帮助我们更好地应对电磁辐射问题。

一、电路布局设计电路布局是解决电磁辐射问题的首要步骤。

合理的电路布局可以降低电磁辐射水平。

以下是一些电路布局设计的注意事项:1. 分隔和隔离:将电路模块分隔和隔离,避免不同模块之间的电磁干扰。

同时,尽量将信号线与电源线分开布置,以减少串扰。

2. 地线规划:合理规划地线可以有效降低电磁辐射。

使用大面积的地面层、减少地线走线长度,选择合适的接地点和接地方式,可以提高系统的抗干扰能力。

3. 电源线管理:合理布置电源线,尽量使用滤波器和金属屏蔽材料,以降低电源线上的电磁辐射。

二、屏蔽措施屏蔽是一种常见且有效的解决电磁辐射问题的手段。

以下是几种常见的屏蔽措施:1. 金属屏蔽:使用金属屏蔽材料(如铜箔、铝箔等)将电路封装和隔离起来,阻止电磁波的传播。

这样可以有效减少电磁辐射对周围环境和其他设备的干扰。

2. 磁性屏蔽:使用磁性材料(如铁氧体)制作磁屏蔽罩或磁屏蔽套,吸收电磁波,减少电磁辐射。

3. 屏蔽壳设计:在电路板设计阶段,可以将敏感电路封装在屏蔽壳内,从而有效减少电磁辐射。

三、滤波器的应用滤波器可以有效地降低电磁辐射的水平。

以下是几种常见的滤波器:1. EMI滤波器:EMI滤波器是一种用于抑制高频噪声和电磁辐射的器件。

它可以将高频噪声滤除,保证电路的正常运行,减少电磁辐射。

2. LC滤波器:LC滤波器是一种利用电感和电容的特性来滤除电磁波的器件。

通过正确选择电感和电容的数值,可以有效降低电磁辐射水平。

四、地线和屏蔽材料的选择正确选择地线和屏蔽材料对于解决电磁辐射问题非常重要。

以下是一些选择地线和屏蔽材料的建议:1. 地线选择:选择低阻抗的地线,以确保地线的有效接地。

关于射频电子设备的电磁兼容性设计的思考【摘要】在现今科技发展下,电子设备设计不再是将信号线正确连接这么单纯,射频电子设备上的电磁兼容成为必须要考虑的因素,也即整合射频电子设备上各种不同种类的信号,使各信号不会互相干扰。

本文首先探讨了电子设备的电磁兼容性概述,进而分析了射频电子设备电磁兼容性的系统布局与系统设计。

【关键词】电子设备;电磁兼容;系统布局;硬件架构一、电子设备的电磁兼容性概述近年来科技快速的发展,各式各样的电子产品无不追求轻薄短小,而电子设备的制程也趋向缩小化与多层板,如何在有限空间内进行电子设备布局(layout)和解决电磁干扰(electromagnetic interference,EMI)相关问题已成为工程师重要的技术。

目前电子设备布局设计时需注意阻抗匹配(impedance matching)、信号完整性(signal integrity,SI)、电源完整性(power integrity,PI),并以低成本达到良好的电磁兼容(electromagnetic compatibility,EMC)成为主要研究方向。

常见电子设备布局须注意的效应包括布线与贯孔间的串扰、数位与类比元件摆放位置、电路布线的长度、贯孔对高速电路的影响,其中布线与贯孔设计最容易产生干扰问题,好的布线与贯孔设计能减少传输线间的串扰,进一步提升信号的品质。

一般传统的设计流程,在设计的过程中往往只考虑信号完整性、电源完整性,却常常忽略了电子设备上传输线所造成的电磁干扰问题,往往需要花费时间在电磁干扰的纠错方面。

二、射频电子设备电磁兼容性的系统布局随着电路技术突飞猛进,射频电子产品的操作频率越来越高,使得电磁干扰问题成为设计的一大挑战,因此本文将描述电子设备的电磁干扰布局设计原理。

(一)电磁干扰来源当一个电磁干扰问题发生时,有三个元素需特别注意,第一为能量的来源,第二为被能量干扰的接受者,第三为在能源与接受者之间的耦合路径。

通讯产品电路设计中的电磁波辐射和辐射抗扰性问题研究 1 引言随着科学技术的飞速发展,作为高科技产品的代表之一——通讯产品,其发展速度日新月异,从传统的传送单纯话音的窄带业务到传送话音、数据和视频等的综合宽带业务,对信号传输质量和传输速度的要求也越来越高,这就不可避免地给通讯产品带来了许多电磁兼容性(EMC )问题,特别是通讯产品的电磁波辐射和辐射抗扰性问题百表现尤为突出。

通过对本公司通讯产品的电磁波辐射和辐射抗扰性问题进行详细地分析,在通讯产品的电路设计阶段总结出一系列解决此类问题的方法,下面逐一进行详细论述。

2 差模辐射和共模辐射要想解决电路中的电磁波辐射和辐射抗扰性问题,首先应了解辐射的机理,在通讯产品中,通常辐射的根源在其数字电路部分,而数字电路的辐射按其方式可分为差模辐射和共模辐射。

差模辐射是由于电流流过电路中的导线环路造成的,如图1所示。

这些环路相当于正 在工作的小天线,向空间辐射磁场。

差模辐射用小环天线产生的辐射来模拟时,设电流为I ,面积为S 的小环,在自由空 间为r 的远场,测得的电场为:θsin )/1)((106.131216r SI f E -⨯= (式1)其中E ——电场)/(m V f ——频率)(HzS ——面积)(2m I ——电流)(Ar ——距离)(m θ——测量天线与辐射平面的夹角)(︒式1适用于放置在自由空间且表面无反射的小环,通讯产品在进行测试时并非处于自由空间,而是在地面上进行的,附加的地面反射会使测得的辐射增加6dB 。

因此,考虑到这一因素,式1必须乘上系数2。

如果对地面反射作出修正并假设为最大辐射方向,则式1可改写为:)/1)((10263216r SI f E -⨯= (式2)由式2可以看出,差模辐射与环路电流和环面积成正比,与电流频率的平方成正比。

共模辐射是由于电路中存在不希望的电压降造成的,此电压降使系统中某些部分处于高电位的共模电压,当外部电缆与系统连接时,外部电缆在共模电压的作用下被激励,形成辐射电场的天线,如图2所示。

电子电路设计中的电磁辐射控制方法在电子电路设计中,电磁辐射控制是一个非常重要的问题,特别是在高频高速电路设计中更是至关重要。

电子设备中的电磁辐射不仅会对设备的正常工作产生干扰,还可能对周围的设备或者人体造成危害。

因此,如何有效地控制电磁辐射成为电子电路设计中必须要考虑的问题之一。

首先,在电子电路设计中,我们可以采取一些控制方法来降低电磁辐射。

其中,布线设计是一个非常关键的环节。

在进行电路布线时,尽量避免在信号线上形成回路,因为回路会增加电路的共模噪声,导致电磁辐射增加。

此外,尽量减少信号线的长度,采用屏蔽线和差分信号线也是降低电磁辐射的有效方法。

其次,在电子电路设计中,接地设计也是至关重要的一环。

合理的接地设计可以有效地减少电磁辐射。

在设计接地时,应尽量减小接地回路的面积,避免接地回路形成大回路,从而减少电磁辐射。

此外,接地回路的布线也应尽量短,减小回路的面积。

此外,在电子电路设计中,使用滤波器也是控制电磁辐射的有效手段。

通过在电路中加入合适的滤波器,可以滤除高频噪声信号,减少电路的电磁辐射。

常用的滤波器包括LC滤波器和RC滤波器,可以根据具体情况选择适合的滤波器。

同时,在电子电路设计中,合理选择元器件也是控制电磁辐射的重要手段。

选择低损耗、低辐射的元器件可以有效减少电路的电磁辐射。

此外,还可以在电路板中加入屏蔽罩,将电路进行有效地屏蔽,减少电磁辐射的扩散。

总的来说,电磁辐射控制在电子电路设计中是非常重要的一环,通过合理的布线设计、接地设计、滤波器的使用以及选择合适的元器件,可以有效地降低电磁辐射,保证电子设备的正常工作并减少对周围环境的干扰。

在实际的电子电路设计过程中,我们需要综合考虑以上因素,通过不断优化方案,达到控制电磁辐射的目的。

电力设备电磁辐射控制与减小方法研究随着科技的发展,电力设备在我们生活中扮演着越来越重要的角色。

然而,由于电力设备在运行过程中会产生电磁辐射,这种辐射对人体健康产生一定的影响。

因此,控制和减小电力设备电磁辐射已经成为一个热门的研究领域。

本文将探讨电力设备电磁辐射产生的原因以及相关的控制与减小方法。

电力设备电磁辐射的产生主要是由于设备中的电流与电压的变化会产生磁场和电场。

这些磁场和电场会形成电磁波,并由设备的导线以及其他电气元件传播出去。

在传播的过程中,电磁波会与周围的环境发生相互作用,从而产生电磁辐射。

而这种电磁辐射对于人体健康的影响主要包括两个方面:热效应和非热效应。

热效应是指电磁辐射导致的温度升高,这主要是因为电磁波与人体组织产生摩擦而产生的。

这种摩擦会导致组织的温度升高,从而对人体产生一定的危害。

而非热效应则是指电磁辐射对生物体细胞、DNA等产生的非热性影响。

具体的非热效应影响还需要进一步的研究与探讨。

为了控制和减小电力设备的电磁辐射,一种常见的方法是通过设计和改进设备的结构。

例如,可以采用屏蔽材料来减小电磁辐射的传播,或者采用合适的接地措施来降低电磁场的强度。

同时,还可以通过改进设备的电路设计,减小电流和电压的变化,从而控制电磁辐射的产生。

此外,合理布局电力设备也是减小电磁辐射的重要方法。

通过优化设备的布置以及导线的走向,可以减少电磁波的传播路径,从而降低辐射的强度。

另外,对于大型电力设备,还可以采用远离人口密集区的方式来减小辐射对人体的影响。

除了设备结构和布局的改进,还可以通过使用辐射防护材料来减小电磁辐射。

这些材料可以吸收或反射电磁波,起到减弱电磁辐射的作用。

常见的辐射防护材料有金属屏蔽材料和电磁波吸收材料等。

这些材料可以应用在设备外壳以及设备周围的环境中,从而减小电磁辐射对周围环境的影响。

此外,加强电磁辐射监测和评估也是减小电磁辐射的重要手段。

通过对电力设备产生的电磁辐射进行实时监测和评估,可以及时发现和解决潜在的辐射问题。

射频电路中降低电磁辐射的思索

摘要:本文分析了不同应用目的和背景下设备对接地设计的要求,并通过实例阐述了接地技术在高速电路设计中的应用。

射频电路pcb设计的关键在于如何减少辐射能力以及如何提高抗干扰能力,只有通过优化电路板的层间距设计以及布局布线或者其他的降低电源、地噪声的方法等来解决电源完整性问题,同时抑制emc/emi。

关键词:射频串扰pcb板emc/emi

随着通信技术的发展,手持无线射频电路技术运用越来越广,如:无线寻呼机、手机、无线pda等,其中的射频电路的性能指标直接影响整个产品的质量。

这些掌上产品的一个最大特点就是小型化,而小型化意味着元器件的密度很大,这使得元器件(包括smd、smc、裸片等)的相互干扰十分突出。

一、设计emg、emi的技巧

一般emi/emc设计时需要同时考虑辐射(radiated)与传导(conducted)两个方面。

前者归属于频率较高的部分(>30mhz)后者则是较低频的部分(<30mhz),所以不能只注意高频而忽略低频的部分。

一个好的emi/emc设计必须一开始布局时就要考虑到器件的位置,pcb迭层的安排,重要联机的走法,器件的选择等,如果这些没有事前有较佳的安排,事后解决则会事倍功半,增加成本。

例如时钟产生器的位置尽量不要靠近对外的连接器,高速信号尽量走内层并注意特性阻抗匹配与参考层的连续以减少反射,器件所推的

信号之斜率(slew rate)尽量小以减低高频成分,选择去耦合(decoupling/bypass)电容时注意其频率响应是否符合需求以降

低电源层噪声。

另外,注意高频信号电流之回流路径使其回路面积尽量小(也就是回路阻抗loop impedance尽量小)以减少辐射,还可以用分割地层的方式以控制高频噪声的范围。

最后,适当的选择pcb与外壳的接地点(chassis ground)。

以下就pcb板的设计技巧提供几个降低电路产生的电磁辐射效应。

1、注意高频器件摆放的位置,不要太靠近对外的连接器。

2、尽可能选用信号斜率(slew rate)较慢的器件,以降低信号所产生的高频成分。

3、注意高速信号的阻抗匹配,走线层及其回流电流路径(rcttlrn current path),以减少高频的反射与辐射。

4、在各器件的电源管脚放置足够与适当的去耦合电容以缓和电源层和地层上的噪声。

特别注意电容的频率响应与温度的特性是否符合设计所需。

5、对外的连接器附近的地可与地层做适当分割,并将连接器的地就近接到chassis ground。

6、可适当运用ground guard/shunt traces在一些特别高速的信号旁。

但要注意guard]shunt traces对走线特性阻抗的影响。

7、电源层比地层内缩20h,h为电源层与地层之间的距离。

二、降低串扰的几点建议

在电路板尺寸固定的情况下,如果设计中需要容纳更多的功能,

就往往需要提高pcb的走线密度,但是这样有可能导致走线的相互干扰增强,同时走线过细也使阻抗无法降低,在设计高速高密度pcb 时,串扰(crosstalkinterference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。

以下提供几个注意的地方:

1、控制走线特性阻抗的连续与匹配。

2、走线间距的大小。

一般常看到的间距为两倍线宽。

可以透过仿真来知道走线间距对时序及信号完整性的影响,找出可容忍的最小间距。

不同芯片信号的结果可能不同。

3、选择适当的端接方式。

4、避免上下相邻两层的走线方向相同,甚至有走线正好上下重迭在一起,因为这种串扰比同层相邻走线的情形还大。

5、利用盲埋孔(blind/buried via)来增加走线面积。

但是pcb 板的制作成本会增加。

在实际执行时确实很难达到完全平行与等长,不过还是要尽量做到。

6、可以预留差分端接和共模端接,以缓和对时序与信号完整性的影响。

三、如何通过安排迭层来减少pcb设计时emi问题

首先,emi要从系统考虑,单凭pcb无法解决问题。

层叠对emi 来讲,我认为主要是提供信号最短回流路径,减小耦合面积,抑制差模干扰。

另外地层与电源层紧耦合,适当比电源层外延。

对抑制共模干扰有好处。

1、布局总原则:元器件应尽可能同一方向排列,通过选择pcb 进入熔锡系统的方向来减少甚至避免焊接不良的现象;根据经验元器件间最少要有0.5mm的间距才能满足元器件的熔锡要求,若pcb 板的空间允许,元器件的间距应尽可能宽。

对于双面板一般应设计一面为smd及smc元件,另一面则为分立元件。

2、布局中应注意:

①首先确定与其它pcb板或系统的接口元器件在pcb板上的位置,必须注意接口元器件间的配合问题(如元器件的方向等)。

②因为掌上用品的体积都很小,元器件间排列很紧凑,因此对于体积较大的元器件,必须优先考虑,确定出相应位置,并考虑相互间的配合问题。

③认真分析电路结构,对电路进行分块处理(如高频放大电路、混频电路及解调电路等),尽可能将强电信号和弱电信号分开,将数字信号电路和模拟信号电路分开,完成同一功能的电路应尽量安排在一定的范围之内,从而减小信号环路面积;各部分电路的滤波网络必须就近连接,这样不仅可以减小辐射,而且可以减少被干扰的几率,根据电路的抗干扰能力。

④根据单元电路在使用中对电磁兼容性敏感程度不同进行分组。

对于电路中易受干扰部分的元器件在布局时还应尽量避开干扰源(比如来自数据处理板上cpu的干扰等)。

3、元器件的布局

由于smt一般采用红外炉热流焊来实现元器件的焊接,因而元

器件的布局影响到焊点的质量,进而影响到产品的成品率。

而对于射频电路pcb设计而言,电磁兼容性要求每个电路模块尽量不产生电磁辐射,并且具有一定的抗电磁干扰能力,因此,元器件的布局还直接影响到电路本身的干扰及抗干扰能力,这也直接关系到所设计电路的性能。

因此,在进行射频电路pcb设计时除了要考虑普通pcb设计时的布局外,主要还须考虑如何减小射频电路中各部分之间相互干扰、如何减小电路本身对其它电路的干扰以及电路本身的抗干扰能力。

根据经验,对于射频电路效果的好坏不仅取决于射频电路板本身的性能指标,很大部分还取决于与cpu处理板间的相互影响,因此,在进行pcb设计时,合理布局显得尤为重要。

4、布线

在基本完成元器件的布局后。

就可开始布线了。

布线的基本原则为:在组装密度许可情况下后,尽量选用低密度布线设计,并且信号走线尽量粗细一致,有利于阻抗匹配。

对于射频电路,信号线的走向、宽度、线间距的不合理设计,可能造成信号信号传输线之间的交叉干扰;另外,系统电源自身还存在噪声干扰,所以在设计射频电路pcb时一定要综合考虑,合理布线。

布线时,所有走线应远离pcb板的边框(2mm左右),以免pcb板制作时造成断线或有断线的隐患。

电源线要尽中能宽,以减少环路电阻,同时,使电源线、地线的走向和数据传递的方向一致,以提

高抗干扰能力;所布信号线应尽可能短,并尽量减少过孔数目;各元器件问的连线越短越好,以减少分布参数和相互间的电磁干扰;对于不相容的信号线应量相互远离,而且尽量避免平行走线,而在正向两面的信号线应用互垂直;布线时在需要拐角的地址方应以135。

角为宜,避免拐直角。

布线时与焊盘直接相连的线条不宜太宽,走线应尽量离开不相连的元器件,以免短路;过孔不腚画在元器件上,且应尽量远离不相连的元器件,以免在生产中出现虚焊、连焊、短路等现象。

在射频电路pcb设计中,电源线和地线的正确布线显得尤其重要,合理的设计是克服电磁干扰的最重要的手段。

pcb上相当多的干扰源是通过电源和地线产生的,其中地线引起的噪声干扰最大。

地线容易形成电磁干扰的主要原因于地线存在阻抗。

当有电流流过地线时,就会在地线上产生电压,从而产生地线环路电流,形成地线的环路干扰。

当多个电路共用一段地线时,就会形成公共阻抗耦合,从而产生所谓的地线噪声。

因此,在对射频电路pcb的地线进行布线时应该做到:

①首先,对电路进行分块处理,射频电路基本上可分成高频放大、混频、解调、本振等部分,要为各个电路模块提供一个公共电位参考点即各模块电路各自的地线,这样信号就可以在不同的电路模块之间传输。

然后,汇总于射频电路pcb接人地线的地方,即汇总于总地线。

由于只存在一个参考点。

因此没有公共阻抗耦合存在,从而也就没有相互干扰问题。

②数字区与模拟区尽可能地线进行隔离,并且数字地与模拟地要分离,最后接于电源地。

③在各部分电路内部的地线也要注意单点接地原则,尽量减小信号环路面积,并与相应的滤波电路的地址就近相接。

④在空间允许的情况下,各模块之间最好能以地线进行隔离,防止相互之间的信号耦合效应。

四、小结

射频电路pcb设计的关键在于如何减少辐射能力以及如何提高抗干扰能力,合理的布局与布线是设计射频电路pcb的保证。

文中所述方法有利于提高射频电路pcb设计的可靠性,解决好电磁干扰问题,进而达到电磁兼容的目的。