12位逐次逼近寄存器型ADC转换器设计

- 格式:doc

- 大小:1.82 MB

- 文档页数:25

一种12位1M S-s含冗余位SAR ADC的设计一种12位1M S/s含冗余位SAR ADC的设计摘要:模数转换器(ADC)在现代电子系统中起着至关重要的作用,其中逐次逼近型(SAR)ADC是一种常见的架构。

本文介绍了一种新颖的12位1M采样率的SAR ADC设计,该设计采用了冗余位和多级比较器的结构,以提高转换精度和速度。

通过对ADC电路及其工作原理的详细说明,充分展现了该设计的优势和性能。

1. 引言模数转换器(ADC)是将连续的模拟信号转换为离散的数字信号的关键部件。

SAR ADC是目前最常用的ADC架构之一,其原理是通过比较参考电压与待测信号,逐位逼近地确定数字代码。

2. SAR ADC的工作原理SAR ADC的主要组成部分包括采样保持电路(S/H)和逼近逻辑电路。

S/H电路用于将连续的模拟信号抽样成离散的采样值,并在每个时钟周期前锁存。

逼近逻辑电路根据每一位的比较结果,逐步逼近待测信号的数字表示。

3. 冗余位和多级比较器的设计为了提高转换精度和速度,本设计使用了冗余位和多级比较器结构。

冗余位用于在每一位上进行额外的比较,以消除由于比较误差引入的非线性失真。

多级比较器结构则可以减小每个比较器的比较范围,提高转换速度。

4. ADC电路细节该SAR ADC的电路采用了12位的并行比较器结构,其中每一位采用了4级比较器。

并行比较器的输出通过加权网络反馈给参考电压发生器和逼近逻辑电路,以实现逐位逼近。

5. 性能评估通过电路仿真和性能评估,我们对这种SAR ADC的性能进行了全面的分析。

结果表明,该ADC设计能够实现12位精度的转换,采样率为1M S/s,同时具有较低的功耗和较高的转换速度。

6. 结论本文介绍了一种12位1M S/s含冗余位SAR ADC的设计。

通过采用冗余位和多级比较器的结构,提高了ADC的转换精度和速度。

通过电路仿真和性能评估,验证了该设计的优势和性能。

这种设计在数字信号处理、通信系统和传感器等领域有着广泛的应用前景综上所述,本文介绍了一种基于冗余位和多级比较器结构的12位1M S/s SAR ADC的设计。

上海交通大学硕士学位论文基于S O C系统的12位SARADC 的设计DESIGN OF A 12 BIT SUCCESSIVE APPROXIMATION REGISTER ADC IN SOC SYSTEM硕士姓名:沈奇臻专业:电路与系统学号: 1060349010指导教师:戎蒙恬上海交通大学二零零八年十二月DESIGN OF A 12 BIT SUCCESSIVE APPROXIMATION REGISTER ADC IN SOC SYSTEMByShen QizhenADVISOR: Prof. Rong MengtianA THESIS SUBMITTED TOSHANGHAI JIAO TONG UNIVERSITYIN PARTIAL FULFILLMENT OF THE REQUIREMENTSFOR THE DEGREEOF MASTER OF SCIENCEDepartment of Electrical Engineering ofShanghai Jiao Tong UniverisityDecember 2008II基于S O C系统的12位SARADC 的设计摘 要在现在的各种应用SoC系统中,由于系统的高性能、低功耗、低成本要求,一定会把数模转换器(ADC)模块作为一个必不可少的组成部分和其他的模拟模块以及数字模块一起集成于一块芯片上,这已经是种必然的趋势。

正是由于这个原因,一种能够与数字工艺兼容的ADC的设计就变得很必要。

SARADC是一种常见的ADC的结构,由于其本身的小尺寸低功耗的特点,非常适合应用于SoC系统。

本文设计的就是这样一个应用于SoC系统的,能够面向触摸屏应用的ADC模块。

它基于TSMC 0.18um 的1P5M工艺,总共包括了模拟电路中的比较器电路、DAC电路、触摸屏驱动电路,输入通道选择电路以及数字电路的移位逻辑控制电路和时钟频率转换电路。

针对高速低功耗抖动要求,本文给出一种电流按比例缩放结构的DAC结构,并采用温度码和二进制码的分段组合,在明显提高DAC的精度,降低电路的失配和毛刺现象的同时减小芯片的面积和功耗。

12位adc电压转换公式12位ADC电压转换公式随着科技的不断发展,电子技术的发展日新月异,数字电路技术得到了广泛应用。

在数字电路中,ADC(模数转换器)是一种将模拟信号转换成数字信号的设备,经常用于电压、电流、温度、压力等模拟量的测量和控制。

ADC的使用使得模拟信号处理成为了更为可靠和方便的数值处理。

在实际应用中,我们经常会遇到12位ADC电压转换公式的问题。

下面,我们将详细介绍12位ADC电压转换公式的意义、计算方法以及应用。

1. 什么是12位ADC电压转换公式?12位ADC电压转换公式是一种将ADC输出的数字信号转换回原始电压信号的计算方法。

在12位ADC中,数字信号的精度为12位,即最大输出值为4095(2^12 - 1),而电压范围则与ADC的参考电压有关。

在实际应用中,我们经常需要将ADC的数字信号转化为对应的电压信号,以便对被测电路的电压进行准确测量和控制。

此时,我们需要使用12位ADC电压转换公式。

2. 如何计算12位ADC电压转换公式?在实际应用中,12位ADC电压转换公式通常有两种计算方法:一种是使用加减乘除等基本算法进行计算,另一种是通过公式进行计算。

方法一:基本算法计算假设ADC的参考电压为Vref,输出的数字信号为Vout,则原始电压信号为:V = Vout * Vref / 4095其中,V为原始电压信号,Vout为ADC的数字输出信号,Vref为ADC的参考电压。

例如,假设ADC的参考电压为5V,输出的数字信号为2048,则原始电压信号为:V = 2048 * 5V / 4095 = 2.5V方法二:公式计算使用公式计算12位ADC电压转换公式需要使用一组系数,这组系数被称为理论参考值。

理论参考值根据ADC的参考电压和精度进行计算,其公式为:理论参考值 = 参考电压 / (2^精度)例如,假设ADC的参考电压为5V,精度为12位,则理论参考值为:理论参考值 = 5V / (2^12) = 0.0012207V计算原始电压信号的公式为:V = Vout * 理论参考值例如,假设ADC的参考电压为5V,输出的数字信号为2048,则原始电压信号为:V = 2048 * 0.0012207V = 2.4999836V3. 12位ADC电压转换公式的应用12位ADC电压转换公式广泛应用于电压、电流、温度、压力等模拟量的测量和控制中。

模数转换器ADC12的工作原理及使用//0>. 微控设计网中国MSP430单片机专业网站MSP430外围模块功能简介[4]作者:利尔达模数转换器ADC12的工作原理及使用基于模拟前端信号处理与控制技术的专业论坛、网站//. 微控设计网中国MSP430单片机专业网站MSP430F14X和44X系列单片机内嵌入一个高精度12位ADC转换模块。

该转换模块具有采样速率高,(最大采样速率达二十万次每秒,这无疑提高了测量精度)。

另外MSP430系列中的FE427也具有ADC模块功能,该模块中的16位ADC是采用∑-△转换技术来将模拟信号数字化的。

因此这两个模块转换的原理是有差别的,具体使用参见芯片参考手册。

在此讲座中只介绍MSP430F44X、14X系列的ADC转换模块。

从该模块电路看出,其模式转换是采用逐次逼近的方法来实现测量的。

该电路分5大功能模块组成,在配置上这5个模块都可以独立配置。

五五大大模块模块分析分析::1、带有采样/保持功能的ADC内核该采样器是以电菏为转换辅助量的及采用电荷重分布技术的逼近型ADC,其特点是高效经济。

其核心为1权电容网络。

其采样过程是一个电容充电过程。

其保持就是根据电容中的电菏不变实现在比较寄存器中的总电荷量在逐次逼近,随着逐次逼近过程的进行,权电容网络中的各电容两端的电压在不断变化,因而导致总电荷量在每个电容之间不断重新分布。

该原理要比传统逼近型ADC中控制精密电阻的相对精度要容易,因此实现较为经济,同时消除了电阻网络中因温度变化引起的阻值失配。

EXIT基于模拟前端信号处理与控制技术的专业论坛、网站//. 微控设计网中国MSP430单片机专业网站由于A/D转换的原理是基于电荷再分配,当内部开关切换输入信号进行采样时,会产生流入或流出电流,但这种电流由于外部的等效时间常数很小而不会影响转换精度。

但如果外部的阻抗很大,在确定的采样时间内,这些瞬变的电流就会影响采样的精度。

ADC的结构方案概述ADC,即模数转换器(Analog-to-Digital Converter),是将模拟信号转换为数字信号的一种电子设备。

在现代电子技术中,ADC广泛应用于各个领域,如通信、控制系统、医疗设备等。

ADC的结构设计有多种方案,本文将对其中的几种典型结构进行概述和介绍。

1.逐次逼近型ADC逐次逼近型ADC是最常见的一种结构方案。

它采用一个逐次逼近算法,从最高位开始逐步逼近输入信号的大小。

该结构主要包括一个比较器、一个数字-模拟转换器和一个数字逻辑控制器。

在每个时钟周期内,逻辑控制器生成一个比较阈值,并将其与输入信号进行比较。

根据比较结果,控制器调整阈值,逐步逼近输入信号的大小,直至达到所需精度。

逐次逼近型ADC的优点是结构简单、实现容易。

缺点是转换速度较慢,适用于低速应用场景。

2.并行型ADC并行型ADC是一种高速的转换器结构方案。

它使用多个比较器并行工作,将输入信号划分成多个子区间,然后分别进行转换。

每个子区间由一个比较器和一个数字-模拟转换器处理。

最后,将各个子区间的数字结果合并,得到最终的转换结果。

并行型ADC的优点是高速、高精度,适用于需要高速转换的应用。

缺点是硬件成本高,布线复杂。

3. Sigma-Delta型ADCSigma-Delta型ADC是一种低速高精度的转换器方案,常用于声音和音频信号的数字化处理。

它利用了噪声和过采样的技术,将输入信号与一个高频的参考信号进行混合,并通过一个积分运算器对混合信号进行积分平均。

通过高频参考信号的累积效应,有效抑制了噪声对转换结果的影响。

最后,通过一个数字滤波器对输出进行滤波,得到最终的数字结果。

Sigma-Delta型ADC的优点是高精度、抗干扰能力强。

缺点是转换速度较慢,不适用于高速应用。

4.均匀量化型ADC均匀量化型ADC是一种基于均匀量化原理的转换器方案。

它采用一个多电平比较器和一个分级量化器进行转换。

多电平比较器将输入信号与一组参考电平进行比较,然后将比较结果转化为数字码。

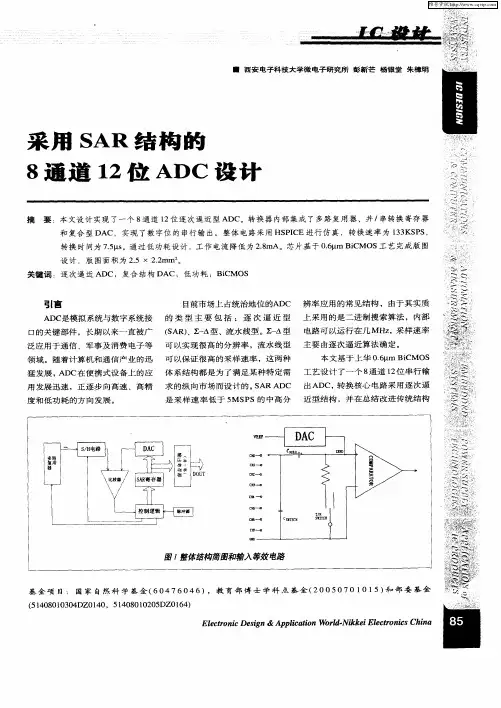

逐次逼近寄存器型ADC设计报告组员(学号):王迪(********)高超(20083507)韩吉祥(20083506)曹天一(20083510)专业(年级):集成电路设计与集成系统课程名称:逐次逼近寄存器型ADC提交日期:一、组员分工:二、项目设计要求:设计一个12bit逐次逼近寄存器型模数转换器SAR ADC 三、项目参数要求:四、项目设计内容:1. 逐次逼近寄存器型模数转换器(SAR ADC)整体结构:2. 逐次逼近寄存器型模数转换器(SAR ADC)的特点及应用:特点:中级转换速度,低功耗,高精度,小尺寸应用:便携式仪表、笔输入量化器,工业控制和数据/信号采集器等3. 逐次逼近寄存器型模数转换器(SAR ADC)工作原理:SAR ADC其基本结构如图1所示,包括采样保持电路(S/H)、比较器(COMPARE)、数/模转换器(DAC)、逐次逼近寄存器(SAR REGISTER)和逻辑控制单元(SAR LOGIC)。

模拟输入电压V IN由采样保持电路采样并保持,为实现二进制搜索算法,首先由SAR LOGIC控制N位寄存器设置在中间刻度,即令最高有效位MSB为“1”电平而其余位均为“0”电平,此时数字模拟转换器DAC输出电压V DAC为0.5V REF,其中V REF为提供给ADC的基准电压。

由比较器对V IN 和V DAC进行比较,若V IN>V DAC,则比较器输出“1”电平,N位寄存器的MSB 保持“1”电平;反之,若V IN<V DAC,则比较器输出“0”电平,N位寄存器的MSB被置为“0”电平。

一次比较结束后,MSB被置为相应的电平,同时逻辑控制单元移至次高位并将其置“1”,其余位置“0”,进行下一次比较,直至最低有效位LSB比较完毕。

整个过程结束,即完成了一次模拟量到数字量的转换,N 位转换结果存储在寄存器内,并由此最终输出所转化模拟量的数字码。

4. 逐次逼近寄存器型模数转换器(SAR ADC)各子模块设计:子模块1:比较器(COMPARE)(1)电路结构:(给出电路结构图)(2)工作原理:电路为两级运算放大器,第一级是电流镜做负载的差分放大器。

12位高精度低功耗SAR ADC设计李晓兴;杨丽娟;杨靖文【摘要】本文基于华润上华0.18um CMOS工艺,设计了一款200kS/s、12bit 高精度低功耗逐次逼近型模数转换器(Successive Approximation Register ADC,SAR ADC)。

本文采用线性度高的栅压自举开关提高精度;采用改进型分段电容结构,并提出非单调开关切换方案,减小了面积和功耗;采用动态比较器减小功耗;采用改进异步时序,减小关键路径延时。

前仿结果表明:在200kS/s采样速率下有效位数为11.1bit,信号噪声失真比为68.5dB,平均电流11.7uA。

%A 200kS/s, 12bit high precision low power SAR ADC is designed in this paper using CSMC 0.18um process. Bootstrapped switch with high linearity is adopted to improve the accuracy; Improved segmented capacitive structures and non-monotonic switching scheme are proposed in order to reduce the area and power consumption; Dynamic comparator is used to lower the static power consumption; Improved asynchronous timing can reduce the delay of the critical path. The simulation results show that: when sampling speed is 200kS/s, the effective number of bits is 11.1bit, signal to noise and distortion is 68.5dB and the average current is 11.7uA.【期刊名称】《电子世界》【年(卷),期】2016(000)024【总页数】3页(P15-16,18)【关键词】逐次逼近型模数转换器;改进分段电容结构;非单调开关切换;改进异步时序【作者】李晓兴;杨丽娟;杨靖文【作者单位】东南大学信息科学与工程学院;东南大学信息科学与工程学院;东南大学信息科学与工程学院【正文语种】中文逐次逼近型模数转换器(SAR ADC)以其低功耗、小面积、结构简单等优点被广泛应用于现代超大规模集成电路与片上系统中,此外,SAR ADC功耗随采样速率而改变,这对于低功耗应用或者不需要连续采集数据的应用非常有利[1],因而,开展高精度低功耗SAR ADC的研究与设计,对低功耗的系统设计和应用具有重要意义。

前言A/D转换模块是单片机的高功能模块,用于对模拟信号进行数字转换,本文以STC8H8K64U单片机为例(原理与其他51单片机并无差别),该单片机A/D模块为16通道12位。

A/D转换模块的结构STC8H的这个单片机A/D转换模块输入通道有16个(通道越多,同时可以接收的模拟量就越多),分别为ADC0——AD C15,其中ADC15用于测试内部1.19V基准电压,工作时,各个输入通道都工作在高阻状态。

关于位数:12位是用于精度,位数越多,精度越高,以5v电压为例,当一位时,只能分成两份,2.5v以上是1,2.5v以下为0,当两位时,可以分成4份,也就是1.25v,2.5v,3.75v,5v为分界,提高了精度,以此类推。

该单片机A/D转换模块由多路选择开关、比较器、逐次比较寄存器、12位数字模拟转换器(D/A转换模块)、A/D转换结果寄存器、A/D转换模块控制寄存器以及A/D转换模块配置寄存器构成。

A/D转换模块的分类按转化原理分类:逐次逼近型、双积分型、并行/串行比较型、压频转换型等按转化速度分类:超高速<=1ns、高速<=20us、中速<=1ms、低速<=1s。

按转化位数分类:8、12、14、16。

目前主要有逐次比较型转换器(最常用的)和双积分型转换器,故接下来主要讲解逐次比较型转换器。

逐次比较型转换器逐次比较型模拟数字转换器根据逐次比较的逻辑,从最高位(MSB)开始,逐次对每一个输入的电压模拟量与内部D/A转换器输出进行比较,多次比较之后,使得转换得到的数字量逼近输入模拟量对应值,直到A/D转换结束。

下图为逐次比较型转换器原理图A/D转换模块的参考电压源该A/D转换模块的电源与单片机电源是同一个,但A/D模块有独立的参考电压源输入端。

当测量精度要求不高时,可以直接使用单片机的工作电压,高精度时使用精准的参考电压。

A/D转换模块的控制A/D转换模块主要由ADC_CONTR、ADCCFG、ADC_RES、ADC_RESL和A/D 转换模块时序控制寄存器ADC TI M以及控制A/D转换的有关中断的控制寄存器进行控制和管理。

高精度模/数转换器(ADC)的设计1.芯片概述MAX11325是12/10位、500kHz全线性带宽、高速、低功耗、串行输出逐次逼近型(SAR)模/数转换器(ADC),采用外部基准。

MAX11325可从外部连接集成复用器的输出和ADC输入,简化信号调理电路。

MAX11325提供内部和外部时钟模式,在内部和外部时钟模式下均支持扫描工作。

内部时钟模式下,器件的平均计算功能可有效提高SNR;外部时钟模式下采用SampleSet™术,允许用户设置模拟输入通道的顺序。

SampleSet架构为多通道应用提供更灵活的排序功能,减轻微控制器或DSP (控制单元)的通信负荷。

提供连接多路复用器输出和ADC输入的外部引脚,简化多路信号的信号调理设计。

内部时钟模式下,集成FIFO支持高速数据采样,并保持数据以便在任意时刻、以较低的时钟速率读取数据。

这种模式下,器件还支持内部平均计算,以提高嘈杂环境下的SNR。

器件的模拟输入通道可以配置为单端输入、全差分输入或伪差分输入(相对于一个公共输入)。

MAX11325采用2.35V至3.6V单电源供电,在1Msps采样速率下仅消耗5.4mW功率。

MAX11325包括自动关断(AutoShutdown™)、快速唤醒功能和高速3线串口。

器件具有全关断模式,优化电源管理设计。

16MHz、3线串口可直接连接到SPI、QSP™和MICROWIRE®器件,无须外部逻辑转换。

优异的动态范围,低压、低功耗设计以及使用便捷、小尺寸封装等优势,使得这些转换器非常适合便携式电池供电数据采集系统,以及其它要求低功耗、空间紧凑的应用。

MAX11325采用32引脚、5mm x 5mm、TQFN封装,工作在-40°C至+125°C温度范围。

2.关键特性•提供扫描模式、内部平均和内部时钟•16路先入/先出(FIFO)•SampleSet:用户定义通道顺序,最大长度为256•输入引脚◦允许任何单端、差分和伪差分对组合输入•模拟多路复用器具有真正的差分采样/保持◦16/8/4通道单端输入•12/8/4通道全差分输入•15/8/4通道相对于公共端的伪差分输入•外部可连接多路复用器输出和ADC输入•两个软件可选的双极性输入范围◦±VREF+/2、±VREF+•灵活的输入配置,可访问所有通道•高精度◦±1 LSB INL、±1 LSB DNL、无丢码•100kHz输入频率下保证70dB SINAD•1.5V至3.6V数字I/O电源•2.35V至3.6V供电电压•更长的电池寿命,适用于便携应用◦3V供电、1Msps下,功耗5.4mW•全关断模式下,电流损耗2µA•外部差分基准(1V至VDD)•16MHz、3线SPI/QSPI/MICROWIRE/DSP兼容接口•-40°C至+125°C、较宽的工作温度范围•节省空间的32引脚、5mm x 5mm、TQFN封装•1Msps转换速率,无流水线延迟3.简单应用•电池供电仪表•高速闭环系统•高速数据采集系统•工业控制系统•医疗仪表•便携系统4.芯片结构MAX11325引脚配置如下图所示引脚说明AIN 负向输入有源低转换启动输入SCLK 串行时钟输入,时钟数据的串行接口低电平有效片选输入。

模数转换器(ADC)的几种主要类型现在的软件无线电、数字图像采集都需要有高速的A/D采样保证有效性和精度,一般的测控系统也希望在精度上有所突破,人类数字化的浪潮推动了A/D转换器不断变革,而A/D转换器是人类实现数字化的先锋。

A/D转换器发展了30多年,经历了多次的技术革新,从并行、逐次逼近型、积分型ADC,到近年来新发展起来的∑-Δ型和流水线型ADC,它们各有其优缺点,能满足不同的应用场合的使用。

逐次逼近型、积分型、压频变换型等,主要应用于中速或较低速、中等精度的数据采集和智能仪器中。

分级型和流水线型ADC主要应用于高速情况下的瞬态信号处理、快速波形存储与记录、高速数据采集、视频信号量化及高速数字通讯技术等领域。

此外,采用脉动型和折叠型等结构的高速ADC,可应用于广播卫星中的基带解调等方面。

∑-Δ型ADC主应用于高精度数据采集特别是数字音响系统、多媒体、地震勘探仪器、声纳等电子测量领域。

下面对各种类型的ADC作简要介绍。

1.逐次逼近型逐次逼近型ADC是应用非常广泛的模/数转换方法,它包括1个比较器、1个数模转换器、1个逐次逼近寄存器(SAR)和1个逻辑控制单元。

它是将采样输入信号与已知电压不断进行比较,1个时钟周期完成1位转换,N位转换需要N个时钟周期,转换完成,输出二进制数。

这一类型ADC的分辨率和采样速率是相互矛盾的,分辨率低时采样速率较高,要提高分辨率,采样速率就会受到限制。

优点:分辨率低于12位时,价格较低,采样速率可达1MSPS;与其它ADC相比,功耗相当低。

缺点:在高于14位分辨率情况下,价格较高;传感器产生的信号在进行模/数转换之前需要进行调理,包括增益级和滤波,这样会明显增加成本。

2.积分型ADC积分型ADC又称为双斜率或多斜率ADC,它的应用也比较广泛。

它由1个带有输入切换开关的模拟积分器、1个比较器和1个计数单元构成,通过两次积分将输入的模拟电压转换成与其平均值成正比的时间间隔。

doi:10.3969/j.issn.1003-3106.2023.06.023引用格式:田芮谦,宋树祥,赵媛,等.12bit100MS/sFlash SAR混合模数转换器设计[J].无线电工程,2023,53(6):1421-1429.[TIANRuiqian,SONGShuxiang,ZHAOYuan,etal.Designofa12bit100MS/sFlash SARHybridAnalog to DigitalConverter[J].RadioEngineering,2023,53(6):1421-1429.]12bit100MS/sFlash SAR混合模数转换器设计田芮谦1,2,宋树祥1,2,赵 媛1,2,岑明灿1,2,蔡超波1,2,蒋品群1,2(1.广西师范大学电子与信息工程学院/集成电路学院,广西桂林541004;2.广西高校集成电路与微系统重点实验室,广西桂林541004)摘 要:针对传统逐次逼近型模数转换器(SuccessiveApproximationRegisterAnalog to DigitalConverter,SARADC)采样率和能量效率低等问题,设计了一款快闪型(Flash)与逐次逼近型(SAR)相结合的新型混合架构模数转换器。

利用快闪型ADC一个时钟周期内可以转换出多个数字码的优势,提高了ADC的采样率。

采用新型混合开关切换策略与分段电容阵列技术相结合提升了ADC的能量效率,减小了版图面积。

同时,电路采用预放大动态锁存比较器以降低噪声和失调对ADC性能的影响。

采用SMIC0.11μm工艺后,仿真结果表明,在1.2V的工作电压下,当采样速率为100MS/s,输入信号频率为45.04MHz时,输出信号的信号噪声失真比(Signal to Noise and DistortionRadio,SNDR)为69.26dB,无杂散动态范围(Spurious freeDynamicRange,SFDR)为82.10dB,有效位数(EffectiveNumbersofBits,ENOB)达到11.21bit,功耗为5.72mW,版图尺寸为380μm×110μm。

一种带自校准的12-bit SAR-ADC设计许卫明;张金萍;刘俐;庄志伟【摘要】逐次逼近型模数转换器(SAR-ADC)相比较于其他类型的ADC,具有结构简单、功耗低、所占面积小等优点,在移动终端、可穿戴设备以及物联网传感器中被广泛使用.但随着科技的进步,应用场景往往会对SAR-ADC的精度提出更高的要求.基于UMC 110 nm CMOS工艺设计了一款采用RC混合结构且带自校准功能的12-bit SAR-ADC,提高了转换精度、减小了电路面积.其自校准结构相比较于传统的SAR-ADC能够在消除比较器失调的同时将误差量化,以此可判断失调是否被校准完毕,从而判断在该工艺下此ADC性能是否满足需求.【期刊名称】《电子与封装》【年(卷),期】2019(019)007【总页数】4页(P20-23)【关键词】模数转换器;RC混合结构;自校准;逐次逼近【作者】许卫明;张金萍;刘俐;庄志伟【作者单位】中科芯集成电路有限公司,江苏无锡214072;中科芯集成电路有限公司,江苏无锡214072;中科芯集成电路有限公司,江苏无锡214072;中科芯集成电路有限公司,江苏无锡214072【正文语种】中文【中图分类】TN4021 引言近年来,随着数字信号处理技术在电子系统上的广泛应用,对CMOS工艺生产的ADC的速度和精度提出了更高的要求,ADC的性能以及实现方式直接影响了整个电路系统处理物理信号的范围以及制作成本,因此一个功耗低、速度快、精度高、面积小的ADC就显得尤为重要[1]。

伴随着半导体技术的发展,目前市面上比较常见的ADC有以下几种:双积分型、闪速型、流水线型、逐次逼近型(SAR)以及∑-Δ型等,它们可以满足精度和速度的不同需求[2]。

逐次逼近ADC(SAR-ADC)具有中等转换速度和精度,同时也具备功耗低、面积小、受工艺参数波动影响小等特点[3],所以越来越多的应用到很多不同场景。

传统的SAR-ADC中由于存在大规模的二进制电容阵列,会造成很大的面积以及功耗浪费,因此,在实际设计中需要降低电容阵列中的电容数量,比较便捷的方式是采用分段电容阵列或者RC混合结构 [4]。

12位逐次比较型A/D转换器AD574A是美国模拟数字公司(Analog)推出的单片高速12位逐次比较型A/D转换器,内置双极性电路构成的混合集成转换显片,具有外接元件少,功耗低,精度高等特点,并且具有自动校零和自动极性转换功能,只需外接少量的阻容件即可构成一个完整的A/D转换器,其主要功能特性如下:分辨率:12位非线性误差:小于±1/2LBS或±1LBS 转换速率:25us 模拟电压输入范围:0—10V和0—20V,0—±5V和0—±10V两档四种电源电压:±15V和5V 数据输出格式:12位/8位芯片工作模式:全速工作模式和单一工作模式AD574A的引脚说明:[1]. Pin1(+V)——+5V电源输入端。

[2]. Pin2( )——数据模式选择端,通过此引脚可选择数据纵线是12位或8位输出。

[3]. Pin3( )——片选端。

[4]. Pin4(A0)——字节地址短周期控制端。

与端用来控制启动转换的方式和数据输出格式。

须注意的是,端TTL电平不能直接+5V或0V连接。

[5]. Pin5( )——读转换数据控制端。

[6]. Pin6(CE)——使能端。

[7]. Pin7(V+)——正电源输入端,输入+15V电源。

[8]. Pin8(REF OUT)——10V基准电源电压输出端。

[9]. Pin9(AGND)——模拟地端。

[10]. Pin10(REF IN)——基准电源电压输入端。

[11]. Pin(V-)——负电源输入端,输入-15V电源。

[12]. Pin1(V+)——正电源输入端,输入+15V电源。

[13]. Pin13(10V IN)——10V量程模拟电压输入端。

[14]. Pin14(20V IN)——20V量程模拟电压输入端。

[15]. Pin15(DGND)——数字地端。

[16]. Pin16—Pin27(DB0—DB11)——12条数据总线。

逐次逼近寄存器型ADC设计报告组员(学号):刘秀春20083511贾明20083431李强20083444王紫彤20083526专业(年级):集成电路设计2008级课程名称:数模混合集成电路设计提交日期:2011年12月22日一、组员分工:序 号 组 员承 担 工 作1 刘秀春 比较器、SAR (设计,仿真,电路图,版图)2 贾明 采样保持电路、时钟(设计,仿真,电路图,版图)3 李强 DAC (设计,仿真,电路图,版图)4王紫彤MOS 开关、运算放大电路(设计,仿真,电路图,版图)二、项目设计要求:设计一个12bit 逐次逼近寄存器型模数转换器SAR ADC三、项目参数要求:分 辨 率 12bit 采样频率 100KHz 功 耗 < 2mW 电源电压 2.5V 面 积 < 3mm 2 工作温度 0~80℃ 工艺技术0.25um四、项目设计内容:1. 逐次逼近寄存器型模数转换器(SAR ADC )整体结构:2. 逐次逼近寄存器型模数转换器(SAR ADC )的特点及应用: 特点:中级转换速度,低功耗,高精度,小尺寸Analog InS/HDAC SAR LOGICV DACV COMPVinSAR REGISTERCOMPARE图1 逐次逼近寄存器型模数转换器工作原理框图应用:便携式仪表、笔输入量化器,工业控制和数据/信号采集器等3. 逐次逼近寄存器型模数转换器(SAR ADC)工作原理:SAR ADC其基本结构如图1所示,包括采样保持电路(S/H)、比较器(COMPARE)、数/模转换器(DAC)、逐次逼近寄存器(SAR REGISTER)和逻辑控制单元(SAR LOGIC)。

模拟输入电压V IN由采样保持电路采样并保持,为实现二进制搜索算法,首先由SAR LOGIC控制N位寄存器设置在中间刻度,即令最高有效位MSB为“1”电平而其余位均为“0”电平,此时数字模拟转换器DAC输出电压V DAC为0.5V REF,其中V REF为提供给ADC的基准电压。

由比较器对V IN和V DAC进行比较,若V IN>V DAC,则比较器输出“1”电平,N位寄存器的MSB保持“1”电平;反之,若V IN<V DAC,则比较器输出“0”电平,N位寄存器的MSB 被置为“0”电平。

一次比较结束后,MSB被置为相应的电平,同时逻辑控制单元移至次高位并将其置“1”,其余位置“0”,进行下一次比较,直至最低有效位LSB比较完毕。

整个过程结束,即完成了一次模拟量到数字量的转换,N位转换结果存储在寄存器内,并由此最终输出所转化模拟量的数字码。

4. 逐次逼近寄存器型模数转换器(SAR ADC)各子模块设计:子模块1:比较器(COMPARE)(1)电路结构:图中所示的是两级运放比较器,左端的恒流源电路时产生一个40uA 的电流,然后通过电流镜镜像到比较器的内部,经M6、M7组成的第二级运放输出比较结果。

(2)工作原理:电路结果:经比较器比较后,当Vg1>Vg2时,比较值为0,就会生成一个比刚才小一点的电压继续比较。

当Vg1<Vg2时,那么比较值为1,就会生成一个高一点的电压比较器电路是将一个模拟信号与另一个模拟信号进行比较,根据比较结果输出一个二进制信号,来达到逐次逼近的目的,实际上,比较器完成的是模数转换中量化的过程,可见比较器的优劣直接影响着模数转换器的性能。

(3)参数设定:利用sweep语句对m8管进行扫描,其他的管子参数值固定。

从功能图中可以看到管子的尺寸影响不大,在精度仿真图第二个标尺所对应的曲线精度满足设计要求而且管子尺寸相对较小,即w=2u,所以经过扫描后各管子尺寸如表所示。

器件名称参数值器件名称参数值m1 w=3u l=1u m5 w=8u l=1um2 w=3u l=1u m6 w=60u l=1um3 w=14u l=1u m7 w=10u l=1um4 w=14u l=1u m8 w=2u l=1uc 30ff m9 w=8u l=1uibias 40uA(4) 仿真网表:a响应仿真.lib 'mix025_1.l' tt Vdd vdd 0 2.5vVg1 g1 0 1vVg2 g2 0 PULSE (0 2.5 0 1n 1n 0.2u 0.4u) m1 d1 g1 s1 0 nch w=3u l=1u m2 d2 g2 s1 0 nch w=3u l=1um3 d1 d1 vdd vdd pch w=14u l=1u m4 d2 d1 vdd vdd pch w=14u l=1u m5 s1 g5 0 0 nch w=8u l=1um6 d6 d2 vdd vdd pch w=60u l=1u m7 d6 g5 0 0 nch w=10u l=1u m8 g5 g5 0 0 nch w=2u l=1u ibias vdd g5 40uA c d2 0 30ff .tran 1n 1u.print tran v(d6) v(g2,g1) .endb 、功能仿真.lib 'mix025_1.l' tt Vdd vdd 0 2.5vVg1 g1 0 pwl 0 1.25v 1us 2.0v 2.3us 2.2v 4.5us 1.2v 5us 1.8vVg2 g2 0 sin 1.25 1.25 1500k m1 d1 g1 s1 0 nch w=3u l=1u m2 d2 g2 s1 0 nch w=3u l=1um3 d1 d1 vdd vdd pch w=14u l=1u m4 d2 d1 vdd vdd pch w=14u l=1u m5 s1 g5 0 0 nch w=8u l=1um6 d6 d2 vdd vdd pch w=60u l=1u m7 d6 g5 0 0 nch w=10u l=1u m8 g5 g5 0 0 nch w=2u l=1u ibias vdd g5 40uA c d2 0 30ff .tran 1n 10u.print tran v(d6) v(g2) v(g1) .endc 、精度仿真.lib 'mix025_1.l' tt Vdd vdd 0 2.5v Vg1 g1 0 1vVg2 g2 0 pwl 0 0.9994v 10u 1.001v m1 d1 g1 s1 0 nch w=3u l=1u m2 d2 g2 s1 0 nch w=3u l=1um3 d1 d1 vdd vdd pch w=14u l=1u m4 d2 d1 vdd vdd pch w=14u l=1u m5 s1 g5 0 0 nch w=8u l=1u m6 d6 d2 vdd vdd pch w=60u l=1u m7 d6 g5 0 0 nch w=10u l=1u m8 g5 g5 0 0 nch w=2u l=1u ibias vdd g5 40uA c d2 0 30ff .tran 1n 10u.print tran v(d6) v(g2) v(g1) .end(5) 仿真结果: a、响应仿真图中上面的方波为输出out,下面的方波为输入vg2与输入vg1之差。

根据图计算得tPLH=1.74n tPHL=15.76n ,由公式tp=tPLH+tPHL/2计算响应延时tp=8.25n。

b、功能仿真图中方波为输出out ,正弦波为输入vg2, 第三条曲线为输入vg1。

当vg2>vg1时输出out 为高电平,当vg2<vg1时输出out为低电平,测试信号范围为0V~2.5V。

c、精度仿真图中第一条曲线为输出out , 第二条曲线为输入vg2 , 第三条曲线为输入vg1。

精度设计指标值为不大于0.6mv,在图中第二个标尺为测量位置,精度可达到0.5mv,满足设计要求。

(6) 版图:版图的总面积约为49.86u m×90.54um=4514.3um2子模块2:采样保持电路(S/H)(1)电路结构:(2)工作原理当K为低电平时传输门导通,输入信号in经传输门向电容C1充电,忽略运算放大器的输入电流时,充电结束后V out=-Vin,此时电容上的电压也等于Vout,这样就对输入信号进行了采样;。

当K为高电平时传输门关闭,由于C1上的电压在一段是假内保持不变,所以Vout保持不变,从而采样进来的信号保持了下来。

(3)参数设定:见参考文献[5]器件名称 参数值 器件名称 参数值m1 w=15u l=1u m7 w=15u l=1u m2 w=3u l=1u m8 w=3u l=1u m3 w=15u l=1u m9 w=15u l=1u m4 w=3u l=1u m10 w=3u l=1u m5 w=4.5u l=1u m11 w=94u l=1u m6 w=4.5u l=1u m12 w=14u l=1u C1 1pf C2 3pf C3 3pfi130uA(4)仿真网表:*SH.lib'mix025_1.l'ttvin in gnd sin 1.25v 1.25v 95kVk k gnd PULSE (2.5 0 0 0.1n 0.1n 1u 10u) C1 2 gnd 1pF C2 8 out 3pF C3 out gnd 3pF i1 vdd 5 30uA vdd vdd gnd 2.5m1 3 k vdd vdd pch L=1u W=15u m2 3 k gnd gnd nch L=1u W=3u m3 2 k in vdd pch L=1u W=15u m4 2 3 in gnd nch L=1u W=3u m5 5 5 gnd gnd nch L=1u W=4.5u m6 6 5 gnd gnd nch L=1u W=4.5u m7 7 7 vdd vdd pch L=1u W=15u m8 7 out 6 gnd nch L=1u W=3u m9 8 7 vdd vdd pch L=1u W=15u m10 8 2 6 gnd nch L=1u W=3um11 out 8 vdd vdd pch L=1u W=94u m12 out 5 gnd gnd nch L=1u W=14u .tran 10ns 40us 10ns .print v(in) v(k) v(out) .end(5)仿真结果:第一次采样范围为1.26V~1.99V ,保持值为1.99V ,第二次采样范围为0.97V~1.62V,保持值为1.62V 。

第一条曲线为输出out,第二条曲线为K 的输入信号,第三条曲线为输入采样信号。

当K 为低电平时传输门导通,对输入信号进行采样;当K 为高电平时传输门关闭,对采样进来的信号进行保持。