3.4高速存储器

• 采取加速CPU和存储器之间有效传输的特殊措 施,可以通过下列几种途径实现: • (1)主存储器采用更高速的技术来缩短存储器的 读出时间,或加长存储器的字长; • (2)采用并行操作的双端口存储器; • (3)在CPU和主存储器之间插入一个高速缓冲存 储器(),以缩短读出时间; • (4)在每个存储器周期中存取几个字;

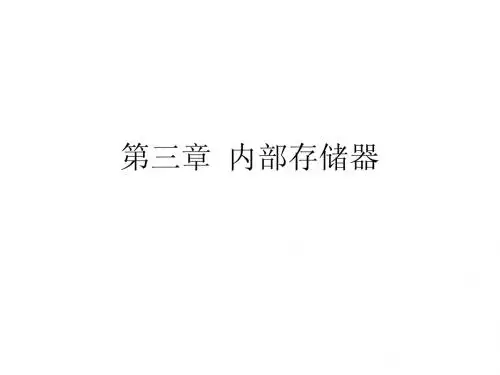

SRAM

8KB

A0 A12

R/W A0 A10 A11 A12 A13 A14 A15

MREQ

A0 A12

A0 A12

A0 A12

A0 A10

Y0

A

Y1 Y2

B

Y3

C

Y4

Y5 Y6 Y7

74LS138 主存储器组成与CPU的连接图

计算机组成原理

高速存储器

存储器构成: 存储元——存储体——存储器

提高:高性能的主存储器EDRAM 闪速存储器

问:奔腾主存的最大物理地址空间为多少?

232×64=4×230×64 =4×230×8×8=32GB

3.3 只读存储器和闪速存储器

1、只读存储器:ROM、光擦可编程只读存储器EPROM、

2、闪速存储器:是一种高密度、非易失性的读/写半导体存储器。

[例3]: 已知CPU的地址总线16根( A15-A0 ,A0为低位),双向数据 总线8根(D7-D0),控制总线中与主存有关的信号有MREQ(允许 访存,低电平有效),R/W(高电平为读命令,低电平为写命令)。 主存地址空间分配如下:0-8191为系统程序区,由只读存储芯 片组成;8192-32767为用户程序区;最后(最大地址)2K地址空间 为系统程序工作区。上述地址为十进制,按字节编址。现有如下存 储器芯片: EPROM:8K × 8位(控制端仅有CS) SRAM:16K × 1位, 2K × 8位, 4K × 8位, 8K × 8位 请从上述芯片中选择适当芯片设计该计算机主存储器, 画出主存储器逻辑框图,注意画出选片逻辑 (可选用门电路及3:8译码器74LS138) 与CPU的连接,说明选哪些存储器芯片, 选多少片。