西北工业大学课件 时序电路(5)序列信号发生器

- 格式:pdf

- 大小:401.16 KB

- 文档页数:10

序列信号发生器的分析与研究摘要信号发生器用来产生频率为20Hz~200kHz的正弦信号(低频)。

除具有电压输出外,有的还有功率输出。

所以用途十分广泛,可用于测试或检修各种电子仪器设备中的低频放大器的频率特性、增益、通频带,也可用作高频信号发生器的外调制信号源。

另外,在校准电子电压表时,它可提供交流信号电压。

在数字信号的传输和数字系统的测试中,有时需要用到一组特定的串行数字信号,我们通常把这种串行数字信号叫做序列信号。

而产生序列信号的电路则称为序列信号发生器。

本文主要是通过序列信号发生器的原理、产生方式和分类,以及对电路进行设计仿真等几方面阐述了序列信号发生器分析与研究关键词:序列信号发生器电路仿真移位寄存器目录1、绪论·····················- 1 -1.1、信号发生器的简介:················- 1 -1.1.1、信号发生器简介:················· - 1 -1.1.2、信号发生器的工作原理:·············· - 1 -1.1.3、信号发生器的结构················· - 1 -1.1.4、信号发生器的分类················· - 2 -1.1.5、信号发生器的应用:················ - 2 -2、序列发生器的分析:················- 4 -2.1、序列信号发生器的介绍···············- 4 -2.2、序列信号发生器的工作原理:············- 4 -2.3、序列信号发生器的分类:··············- 4 -2.3.1、移位型序列信号发生器··············· - 4 -2.3.2、计数型序列信号发生器··············· - 5 -3、序列信号发生器的设计···············- 7 -3.1、序列信号发生器的设计:··············- 7 -3.2、序列信号发生器的实现步骤·············- 7 -3.3、器件及相关介绍:················- 13 -3.3.1、所用器件:···················- 13 -3.3.2、所用器件的介绍:················- 13 -4、结论····················- 21 -致谢·····················- 22 -参考资料···················- 23 -1、绪论1.1、信号发生器的简介:1.1.1、信号发生器简介:凡是产生测试信号的仪器,统称为信号源,也称为信号发生器,它用于产生被测电路所需特定参数的电测试信号。

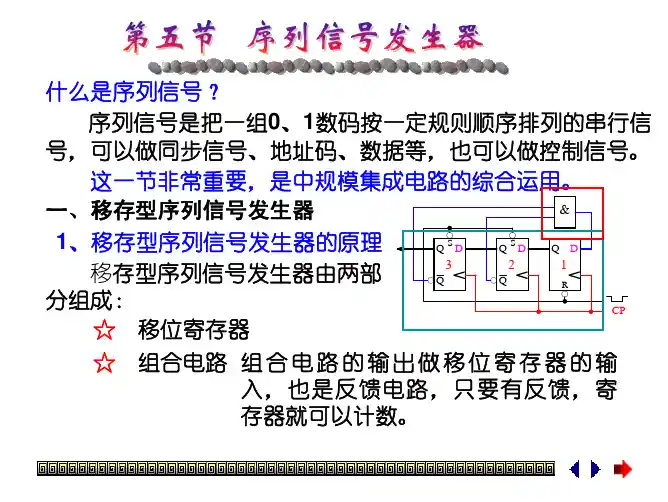

数字电路与系统东南大学信息科学与工程学院第七章常用时序逻辑电路模块及应用寄存器和移位寄存器计数器序列信号发生器◆在数字系统测试和数字信号传输时,会用到一些串行的周期性数字信号,这种串行的周期性数字信号称为序列信号;◆序列信号是在时钟脉冲作用下产生的一串周期性的二进制信号;◆在序列信号的一个周期中,包含的二进制数据位数称为序列长度;◆能产生序列信号的电路称为序列信号发生器;◆序列信号发生器的设计分为两种情况:给定序列信号设计电路;给定序列长度设计电路;给定序列信号设计电路:◆对于给定的序列信号,设计发生器电路一般有两种结构:⏹计数型序列信号发生器;⏹移存型序列信号发生器;(1)计数型序列信号发生器◆计数型序列信号发生器的结构如图:◆计数型序列信号发生器特点是:所产生的序列信号的长度等于计数器的模值,并可根据需要产生一个或多个序列信号;计数型序列信号发生器的设计方法:◆首先构成与序列长度P相同的一个模P计数器;◆选择适当的数据选择器,把要产生的序列按规定的顺序加在数据选择器的数据输入端;◆地址输入端与计数器的输出端适当地连接在一起;◆还可以把输出序列作为计数器的输出,也就是在计数器的基础上增加一个输出函数,输出所需要的序列;例:计数器74161和数据选择器构成一个01100011序列发生器;◆由于序列长度P=8,74161构成模8计数器;◆数据选择器产生序列;◆如图:逻辑图:◆用74161及门电路构成的01010序列信号发生器及状态表◆在这里,Z的输出没有采用最简表达式Q0,是因为如果采用Q0,就会存在100变为101短暂的时刻在输出上出现毛刺(为什么?)(2)移存型序列信号发生器◆移存型序列信号发生器结构如图;◆它是以移位寄存器作为存储器件,移位寄存器的级数n应该满足2n大于等于序列长度;例:用移位寄存器构成的“00010111”序列信号发生器,该序列是左边0先输出,1最后输出。

◆序列信号长度为8,至少应该使用3位移位寄存器;◆我们把移位寄存器的工作状态列出来:序列发生器的状态转移表:例:用移位寄存器构成的“000101”序列信号发生器;◆给定的序列长度为6,因此,移位寄存器的位数应该大于等于3;◆如果选3,列状态转移表如右图所示:◆可以看出,当状态为010时,有两种转移:101和100;◆因此,必须增加移位寄存器的位数,取4;◆状态转移为:◆状态转移表◆逻辑图已知序列长度设计序列信号发生器:◆M序列码发生器是一种反馈移位型结构的电路,它由n位移位寄存器加异或反馈网络组成,其序列长度M=2n-1;◆只有一个多余状态,即全0状态,所以称为最长线性序列码发生器;◆由于其结构已定型,且反馈函数和连接形式都有一定的规律,因此利用查表的方式就可以设计出M序列码发生器电路;◆部分M序列码的反馈函数F和移位寄存器位数n的对应见下页表;◆给定一个序列信号长度M,根据M=2n-1求出n;相应的反馈函数F;◆M序列的反馈函数表:例:采用双向移位寄存器74194设计产生M=7的M序列码◆根据M=2n-1,确定n=3;◆再查表可得反馈函数F=Q2⊕Q3;◆在74194中是Q1⊕Q2逻辑图为:逻辑图修改为:7.3 序列信号发生器②利用全0 状态重新置数,从而实现自启动:◆设计M序列码发生器的关键在于查表获得反馈函数,在设计的时候需要注意全0项的处理;◆加全0 校正项和利用全0 状态置数可以保证电路的自启动性。

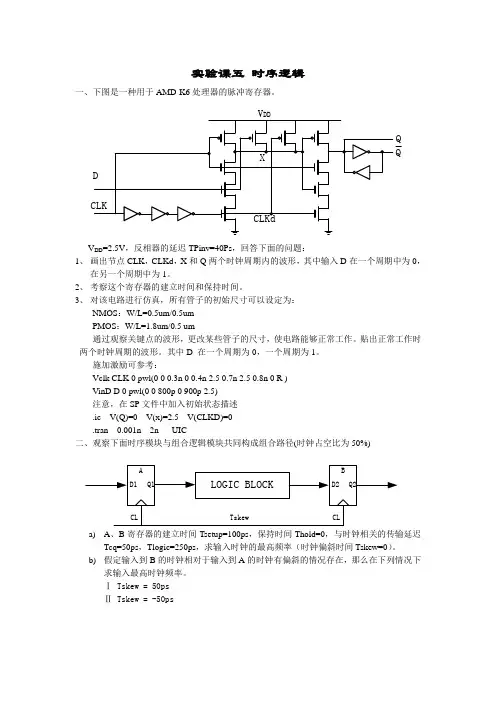

实验课五 时序逻辑一、下图是一种用于AMD-K6处理器的脉冲寄存器。

DDQ QV DD =2.5V ,反相器的延迟TPinv=40Ps ,回答下面的问题:1、 画出节点CLK ,CLKd ,X 和Q 两个时钟周期内的波形,其中输入D 在一个周期中为0,在另一个周期中为1。

2、 考察这个寄存器的建立时间和保持时间。

3、 对该电路进行仿真,所有管子的初始尺寸可以设定为:NMOS :W/L=0.5um/0.5um PMOS :W/L=1.8um/0.5 um通过观察关键点的波形,更改某些管子的尺寸,使电路能够正常工作。

贴出正常工作时两个时钟周期的波形。

其中D 在一个周期为0,一个周期为1。

施加激励可参考:Vclk CLK 0 pwl(0 0 0.3n 0 0.4n 2.5 0.7n 2.5 0.8n 0 R ) VinD D 0 pwl(0 0 800p 0 900p 2.5)注意,在SP 文件中加入初始状态描述 .ic V(Q)=0 V(x)=2.5 V(CLKD)=0 .tran 0.001n 2n UIC二、观察下面时序模块与组合逻辑模块共同构成组合路径(时钟占空比为50%)a) A 、B 寄存器的建立时间Tsetup=100ps ,保持时间Thold=0,与时钟相关的传输延迟Tcq=50ps ,Tlogic=250ps ,求输入时钟的最高频率(时钟偏斜时间Tskew=0)。

b) 假定输入到B 的时钟相对于输入到A 的时钟有偏斜的情况存在,那么在下列情况下求输入最高时钟频率。

Ⅰ Tskew = 50ps Ⅱ Tskew = -50ps三、下图是一种形式的RS触发器。

RS1、 交叉耦合的反相器的阈值电压已经被预置为V DD /2左右,求能够保证触发器正常工作的尺寸系数N ,即,当V S 变化到V DD 或0时,V ⎺Q = V DD /2。

V DD =2.5v 。

VTn=0.43V ,Kn ’= 115×10-6A/V 2,λ=0.06 V -1VTp=-0.4V ,Kp ’= -30×10-6A/V 2,λ=-0.1 V-12、M4、M5的尺寸为W/L=0.5um/0.5um ,对该SR 触发器进行功能仿真,若有必要可以适当调节参数使该触发器能够正常工作。

课程设计任务书学生:险峰专业班级:电子科学与技术1002班指导教师:屏工作单位:信息工程学院题目: 序列信号发生器要求完成的主要任务:1设计一个有限状态机,用以产生输出序列“1110101101”由左开始。

(1)画出状态转换图;(2)使用VHDL语言编程;(3)使用EPM7128SLC84-15芯片(4)检测输出序列信号2将所设计的整个系统写入CPLD 器件中,加上需要的外围电路在实验箱上实现整个系统的硬件搭建,并调试出结果。

时间安排:1、2012 年 12月 17日集中,作课程设计的任务布置。

2、2012 年 12月18日至2012 年 12月21日,进行课程设计,软件编程、仿真和调试。

3、2012 年 12月22日,机房检查仿真结果,验证设计的可行性和正确性。

4、2012 年 12月23日,熟悉实验平台和试验箱。

5、2012 年 12月24日至2012年 12月26日,进行设计的硬件调试。

6、2012 年 12月27日至2012年 12月28日,实验室检查设计成果,现场演示硬件实物,提交设计说明书及答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (II)Abstract (III)绪论 (1)1.EDA的简述 (2)1.1EDA技术的概念 (2)1.2VHDL语言 (2)1.3 Quartus II的概述 (2)2.设计指标要求 (3)3.序列发生器的设计 (3)3.1状态转化图 (3)3.2设计方案论证 (4)3.2.1方案一 (4)3.2.2方案二 (5)3.2.3方案三 (5)3.3仿真图 (7)3.4实物演示结果 (8)4.心得体会 (8)5 致 (10)6.参考文献 (11)附录1: (12)附录2: (14)附录3: (15)摘要序列信号是把一组0、1数码按一定规则顺序排列的串行信号,可以做同步信号、地址码、数据等,也可以做控制信号,而序列发生器就是产生一系列特定的信号的仪器。