•8

6.1.4

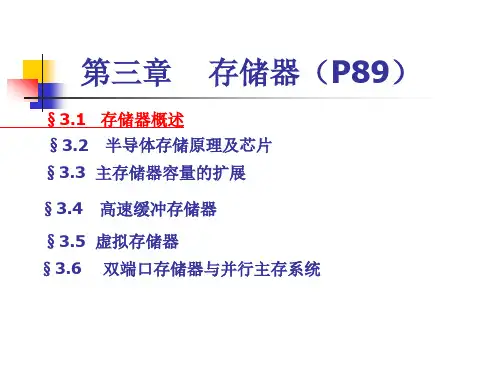

二、动态存储器 1. DRAM的存储元 单管动态存储元电路如图6.3所示。 2. DRAM的外部特性 图6.4所示为2164A的引脚图,其引脚功能如下: A0~A7:地址输入线。DRAM芯片在构造上的特点是 芯片上的地址引脚是复用的。两次送到芯片上去的地址分 别称为行地址和列地址。在相应的锁存信号控制下,它们 被锁存到芯片内部的行地址锁存器和列地址锁存器中。 DIN和DOUT:芯片的数据输入、输出线。 RAS:行地址锁存信号。 CAS:列地址锁存信号。 WE:写允许信号。当它为低电平时,允许将数据写入。 反之,当WE=l时,可以从芯片读出数据。

存储系统分为两个存储体,如图6.19所示。 对于16位的CPU为此也都设置了用于存储体选择的两个 控制 信号和。表6.3描述了这两个引脚和所选择的存储体。 在Intel系列的CPU通过产生独立的写信号来选择每个存 储体的写操作,如图6.20所示。

图6.21描述了一个8086存储系统的连接图。

•23

6.4.2 32位机的存储系统

•13

0111 101

该片6264的地址范围为:

0111 1010 0000 0000 0000=3E000H

到

0011 1111 1111 1111 1111=3FFFFH

若将图6.9中的“与非”门改为“或”门,如图6.10所 示,则6264的地址范围就变成84000H~85FFFH。

二、部分地址译码方式

在构成一个实际的存储器时,往往需要同时进行位扩 展和字扩展才能满足存储容量的需求。扩展时需要的芯片 数量可以这样计算:要构成一个容量为MN位的存储器, 若使用pk位的芯片(p<M,k<N),则构成这个存储器需 要(M/p)(N/k)个这样的存储器芯片。 例6-1 用Intel 2164构成容量为128KB的内存。 分析:由于2164是64K×1的芯片,所以首先要进行位扩 展。用8片2164组成64KB的内存模块,然后再用两组这样 的模块进行字扩展。所需的芯片数为(128/64)×(8/1) =16片。 连接示意图如图6.18所示。