通信软件设计-第5章 状态机实例-2011

- 格式:ppt

- 大小:864.00 KB

- 文档页数:80

状态机编程例程

状态机编程是一种用于描述系统行为的方法,它基于一组状态和状态之间的转换规则来实现。

在状态机中,系统的行为由当前状态和输入决定,并且根据定义好的转换规则来进行状态的转移。

在状态机编程中,首先需要定义系统的状态和输入。

状态可以是系统的某种运行状态或者某种条件的判断结果,而输入则是触发状态转移的外部事件或条件。

系统的状态和输入可以根据实际需求进行定义,以满足具体的业务逻辑。

接下来,需要定义状态之间的转换规则。

转换规则描述了在某个状态下,系统接收到某个输入后应该转移到哪个状态。

转换规则可以使用条件语句或者表格来表示,以便清晰地描述状态之间的关系。

在实际编程中,可以使用代码来实现状态机。

首先,需要定义系统的状态和输入,并使用变量来保存当前状态。

然后,根据定义好的转换规则,编写代码来处理输入,并根据当前状态和输入来更新系统的状态。

最后,根据系统的状态来执行相应的操作或输出结果。

状态机编程可以应用于各种场景,例如游戏开发、网络通信、控制系统等。

通过使用状态机编程,可以简化系统的设计和实现,提高代码的可读性和可维护性。

同时,状态机编程也能够更好地反映系统的行为逻辑,使程序的执行流程更加清晰和可预测。

状态机编程是一种用于描述系统行为的方法,它通过定义系统的状

态和输入以及状态之间的转换规则来实现。

在实际编程中,可以使用代码来实现状态机,并根据系统的状态来执行相应的操作。

通过使用状态机编程,可以简化系统的设计和实现,提高代码的可读性和可维护性,同时也能够更好地反映系统的行为逻辑。

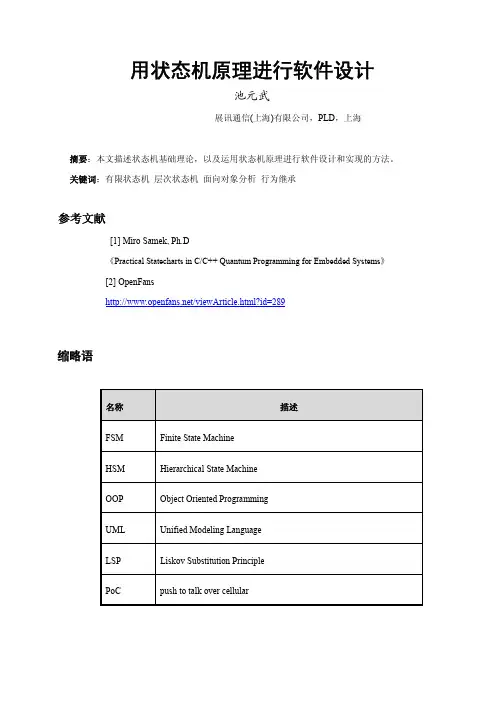

用状态机原理进行软件设计池元武展讯通信(上海)有限公司,PLD,上海摘要:本文描述状态机基础理论,以及运用状态机原理进行软件设计和实现的方法。

关键词:有限状态机层次状态机面向对象分析行为继承参考文献[1] Miro Samek, Ph.D《Practical Statecharts in C/C++ Quantum Programming for Embedded Systems》[2] OpenFans/viewArticle.html?id=289缩略语名称描述StateMachineFSM FiniteHSM Hierarchical State MachineOOP Object Oriented ProgrammingUML Unified Modeling LanguageLSP Liskov Substitution PrinciplePoC push to talk over cellular目录第1章引言................................................................................................................................................1-1第2章 FSM概念......................................................................................................................................2-12.1 FSM定义.........................................................................................................................................2-12.2 FSM要素.........................................................................................................................................2-12.2.1 State(状态)......................................................................................................................2-12.2.2 Guard(条件)......................................................................................................................2-12.2.3 Event(事件)......................................................................................................................2-12.2.4 Action(动作)....................................................................................................................2-12.2.5 Transition(迁移).......................................................................................................2-22.3 FSM图示.........................................................................................................................................2-2 第3章 FSM设计方法..............................................................................................................................3-13.1 C Parser(注释分析程序)..................................................................................................................3-13.2 Calc(计算器)程序举例.....................................................................................................................3-2 第4章 HSM概念......................................................................................................................................4-14.1 programming-by-difference(按照差异编程)..............................................................................4-14.2 HSM图示.........................................................................................................................................4-14.3 HSM分析和OOP分析...................................................................................................................4-24.3.1 state inheritance and class inheritance(状态层次和类层次)..........4-24.3.2 Entry/Exit Actions and Construction/Destruction(进入/退出状态和构造/析构类).............................................................................................................................................4-34.3.3 programming-by-difference(按照差异编程)....................................................................4-34.3.4 abstraction(抽象)........................................................................................................4-4 第5章 HSM设计方法..............................................................................................................................5-15.1继续进行Calc设计......................................................................................................................5-15.2继承关系是否合理.........................................................................................................................5-35.2.1 Transition迁移执行顺序..............................................................................................5-4 第6章 HSM在实际工程的应用..............................................................................................................6-66.1 PoC Audio Player..............................................................................................................................6-66.2 PoC Call Control...............................................................................................................................6-7 第7章 FSM实现......................................................................................................................................7-17.1 nestted switch statement(嵌套switch)........................................................................................7-17.2 state table(状态表)................................................................................................................7-2-i-7.3 Function Address As State(用函数指针作为状态).....................................................7-37.4 QFSM frame(QFSM框架)..........................................................................................................7-5 第8章 HSM实现......................................................................................................................................8-1第9章附录 (1)-ii-图目录图2-1 Keyboard FSM in UML format 1...............................................................................................2-2 图2-2 Keyboard FSM in UML format 2...............................................................................................2-3 图3-1 C comment parser (CParser) FSM..............................................................................................3-2 图3-2 Basic Calc Example....................................................................................................................3-3 图3-3 Basic Calc FSM..........................................................................................................................3-4 图3-4 Basic Calc FSM add “Result” state............................................................................................3-5 图3-5 Basic Calc FSM add “Result” state and Cancel event................................................................3-6 图3-6 Simple Calc HSM.......................................................................................................................3-7 图 4-2 HSM conception.........................................................................................................................4-2 图5-1 substate of operandX..................................................................................................................5-1 图5-2 Full Calc HSM............................................................................................................................5-3 图5-3 State Tree of Calc.......................................................................................................................5-5 图 6-1 HSM of audio Player..................................................................................................................6-7 图6-2 HSM of Call Control..................................................................................................................6-8-i-第1章引言20多年以前,David Harel创造了状态机理论来描述复杂的交互系统。

状态机电路设计状态机(STATE MACHINE)可以说是一个广义时序电路,触发器,计数器,移位寄存器都算是它的特殊功能的一种.在电子设计自动化应用当中,状态机经常是担任CPU的功能,从某种意义上讲状态机的应用让系统具有了智能化的功能,业界为状态机和CPU的功能一直争论不休,不过事实是更多人倾向于状态机,认为状态机的功能比CPU 强大.下面将带领大家认识一下状态机的基本设计思想.传统的逻辑电路设计在描述状态机的表示上,以状态图(STATE DIAGRAM)方式最为清晰且容易理解.根据输入,输出及状态关系,状态图可以分为:1.输入&状态&输出(输出仅与状态有关)以下面图形为例,若目前状态机处于状态S0时,输入为0则状态机将维持状态S0不变,若输入改为1则下个状态改成状态S1,但不论输入是什么,此时输出均为0.这种输出与状态有关,而与输入无关的状态机类型,称为More状态机.编程实现其功能如下:--***********************状态机*********************重点提示整个状态机的电路描述分成两个PROCESS命令语句完成.第一个PROCESS:负责感测时钟脉冲信号CP在上升沿变化之际,作目前状态(PresentState)切换至下个状态(NextState)的动作.第二个PROCESS:负责感测输入(DIN)值,目前状态(PresentState)值,由CASE-WHEN语句决定输出(OP)和下个状态(NextState)值.--*********************************************************LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;--*********************************************************ENTITY CH6_5_1 ISPORT(CP :IN STD_LOGIC; --CLOCKDIN:IN STD_LOGIC; --I/P SignalOP :OUT STD_LOGIC --O/P Signal);END CH6_5_1;--*********************************************************ARCHITECTURE A OF CH6_5_1 ISTYPE STATE IS (S0,S1,S2,S3); --State Type DeclareSIGNAL PRESENTSTATE :STATE; --Present StateSIGNAL NEXTSTATE :STATE; --Next StateBEGINSWITCHTONEXTSTATE:PROCESS(CP)BEGINIF CP'EVENT AND CP='1' THENPRESENTSTATE<=NEXTSTATE;END IF;END PROCESS SWITCHTONEXTSTATE;CHANGESTATEMODE:PROCESS(DIN,PRESENTSTATE)BEGINCASE PRESENTSTATE ISWHEN S0=> --STATE S0IF DIN='0' THEN --INPUT=0NEXTSTATE<=S0;ELSENEXTSTATE<=S1;END IF;OP<='0'; --OUTPUTWHEN S1=> --STATE S1IF DIN='1' THEN --INPUT=1NEXTSTATE<=S1;ELSENEXTSTATE<=S2;END IF;OP<='0'; --OUTPUTWHEN S2=> --STATE S2IF DIN='1' THEN --INPUT=1NEXTSTATE<=S2;ELSENEXTSTATE<=S3;END IF;OP<='0'; --OUTPUTWHEN S3=> --STATE S3IF DIN='1' THEN --INPUT=1NEXTSTATE<=S0;ELSENEXTSTATE<=S1;END IF;OP<='0'; --OUTPUTWHEN OTHERS=> --Initial StateNEXTSTATE<=S0;OP<='0'; --OUTPUTEND CASE;END PROCESS CHANGESTATEMODE;END A;--*********************************************************程序说明:(1)上述的状态编码方式,使用默认的Binary编码.(2)在第二个PROCESS内的CASE-WHEN语句里,最后一个WHEN OTHERS 作用在电路起始状态,亦即--将状态初始设定为S0.2.输入&状态&输出(输出与状态,输入背景有关)下面图形的动作和上图相似,但是输出是会随输入不同而有所改变,例如目前状态是S3,若输入是0则输出为0且下个状态更换成S1,而输入为1则输出为1且下个状态更换成S0.这种输出与状态及输入皆有关系者,称为Mealy状态机.程序实现功能如下:--***************************************************************************** LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;--***************************************************************************** ENTITY CH6_5_2 IS--CLOCKSTD_LOGIC;:INPORT(CPDIN:INSignal--I/PSTD_LOGIC;:OUTSTD_LOGICOP);END CH6_5_2;--***************************************************************************** ARCHITECTURE A OF CH6_5_2 ISTYPE STATE IS (S0,S1,S2,S3); --State Type Declare--PRESENT:STATE;STATEPRESENTSTATESIGNAL--NEXTSTATE:STATE;NEXTSTATESIGNALBEGINSWITCHTONEXTSTATE:PROCESS(CP) --PRESENTSTATE->NEXTSTATEBEGINIFCP='1'THENCP'EVENTANDPRESENTSTATE<=NEXTSTATE;ENDIF;END PROCESS SWITCHTONEXTSTATE;CHANGESTATEMODE:PROCESS(DIN,PRESENTSTATE)BEGINCASE PRESENTSTATE ISWHEN S0=> --STATE S0--INPUT=0THENIFDIN='0'NEXTSTATE<=S0;OP<='0'; --OUTPUTELSENEXTSTATE<=S1;OP<='1'; --OUTPUTEND IF;WHEN S1=> --STATE S1THEN--INPUT=1IFDIN='1'NEXTSTATE<=S1;OP<='1'; --OUTPUTELSENEXTSTATE<=S2;OP<='0'; --OUTPUTEND IF;WHEN S2=> --STATE S2--INPUT=1THENIFDIN='1'NEXTSTATE<=S2;OP<='0'; --OUTPUTELSENEXTSTATE<=S3;OP<='1'; --OUTPUTEND IF;WHEN S3=> --STATE S3--INPUT=1THENDIN='1'IFNEXTSTATE<=S0;OP<='1'; --OUTPUTELSENEXTSTATE<=S1;OP<='0'; --OUTPUTEND IF;StateWHENOTHERS=> --InitialNEXTSTATE<=S0;OP<='0'; --OUTPUTCASE;ENDEND PROCESS CHANGESTATEMODE;END A;程序说明:程序写法是与CH6_5_!相似,不过在处理输出OP部分,需按照输入的信号情况,作判断输出,这部分可程序的注释部分看出.。

状态机思路在单片机程序设计中的应用状态机的概念状态机是软件编程中的一个重要概念。

比这个概念更重要的是对它的灵活应用。

在一个思路清晰而且高效的程序中,必然有状态机的身影浮现。

比如说一个按键命令解析程序,就可以被看做状态机:本来在A状态下,触发一个按键后切换到了B状态;再触发另一个键后切换到C状态,或者返回到A状态。

这就是最简单的按键状态机例子。

实际的按键解析程序会比这更复杂些,但这不影响我们对状态机的认识。

进一步看,击键动作本身也可以看做一个状态机。

一个细小的击键动作包含了:释放、抖动、闭合、抖动和重新释放等状态。

同样,一个串行通信的时序(不管它是遵循何种协议,标准串口也好、I2C也好;也不管它是有线的、还是红外的、无线的)也都可以看做由一系列有限的状态构成。

显示扫描程序也是状态机;通信命令解析程序也是状态机;甚至连继电器的吸合/释放控制、发光管(LED)的亮/灭控制又何尝不是个状态机。

当我们打开思路,把状态机作为一种思想导入到程序中去时,就会找到解决问题的一条有效的捷径。

有时候用状态机的思维去思考程序该干什么,比用控制流程的思维去思考,可能会更有效。

这样一来状态机便有了更实际的功用。

程序其实就是状态机。

也许你还不理解上面这句话。

请想想看,计算机的大厦不就是建立在“0”和“1”两个基本状态的地基之上么?状态机的要素状态机可归纳为4个要素,即现态、条件、动作、次态。

这样的归纳,主要是出于对状态机的内在因果关系的考虑。

“现态”和“条件”是因,“动作”和“次态”是果。

详解如下:①现态:是指当前所处的状态。

②条件:又称为“事件”。

当一个条件被满足,将会触发一个动作,或者执行一次状态的迁移。

③动作:条件满足后执行的动作。

动作执行完毕后,可以迁移到新的状态,也可以仍旧保持原状态。

动作不是必需的,当条件满足后,也可以不执行任何动作,直接迁移到新状态。

④次态:条件满足后要迁往的新状态。

“次态”是相对于“现态”而言的,“次态”一旦被激活,就转变成新的“现态”了。

用状态机原理进行软件设计池元武展讯通信(上海)有限公司,PLD,上海摘要:本文描述状态机基础理论,以及运用状态机原理进行软件设计和实现的方法。

关键词:有限状态机层次状态机面向对象分析行为继承参考文献[1] Miro Samek, Ph.D《Practical Statecharts in C/C++ Quantum Programming for Embedded Systems》[2] OpenFans/viewArticle.html?id=289缩略语目录第1章引言 (3)第2章FSM概念 (3)2.1 FSM定义 (3)2.2 FSM要素 (3)2.3 FSM图示 (4)第3章FSM设计方法 (5)3.1 C Parser(注释分析程序) (5)3.2 Calc(计算器)程序举例 (6)第4章HSM概念 (11)4.1 programming-by-difference(按照差异编程) (11)4.2 HSM图示 (12)4.3 HSM分析和OOP分析 (12)第5章HSM设计方法 (14)5.2 继承关系是否合理 (15)第6章HSM在实际工程的应用 (17)6.1 PoC Audio Player (17)6.2 PoC Call Control (18)第7章FSM实现 (19)7.1 nested switch statement(嵌套switch语句) (20)7.2 state table(状态表) (22)7.3 Function Address As State(用函数指针作为状态) (23)7.4 QFSM frame(QFSM框架) (25)第8章HSM实现 (28)第9章附录 (31)第1章引言20多年以前,David Harel创造了状态机理论来描述复杂的交互系统。

随后,状态机理论赢得了广泛的接受,并且被引入到许多软件系统中,最突出的是被引入到UML中作为其一个组成部分。