第5章习题参考答案

- 格式:doc

- 大小:648.00 KB

- 文档页数:16

一、名词解释重商主义幼稚产业贸易保护主义超保护贸易主义新贸易保护主义二、单选题1.重商主义起源于()世纪至()世纪欧洲资本主义原始积累时期。

A.12 15 B.14 16 C.15 17 D.16 182.重商主义分为早期和晚期,早期以()论为中心,其代表人物是()。

A.贸易差额斯塔福 B.贸易差额托马斯•孟C.货币差额托马斯•孟 D.货币差额斯塔福3.晚期重商主义理论被称为()。

A.货币价值论B.贸易差额论C.财富价值论 D.货币差额论4.李斯特认为,采取贸易保护政策,从短期看,消费者的利益将()。

A.遭受损失B.得到保护C.不会改变D.增加5.凯恩斯主义认为,()可为一国带来黄金,可以扩大支付手段,压低利息率,刺激物价上涨,扩大投资,这有利于国内危机的缓和与扩大就业量。

A.贸易平衡B.贸易逆差C.贸易顺差D.贸易赤字6.与自由贸易主义学说不同,保护幼稚产业的理论主张,在经济发展的过程中,比较优势是()。

A.动态的B.劣势中较小的劣势C.不可改变的D.由生产成本决定的7.世贸组织的有关协议规定,为保护人类、动植物的生命及健康,为保存有限的天然资源,()。

A.不允许对贸易加以限制 B.鼓励天然资源自由贸易C.不允许天然资源的进出口贸易D.允许对贸易加以限制8.各种各样的经济贸易同盟,几乎无一例外地(),严重削弱了世界范围内的贸易自由化。

A.在内部实行严格保护而对外实行自由贸易B.在内部实行自由贸易而对外实行严格的保护C.在内部和外部都实行严格的保护D.在内部和外部都实行自由贸易三、简答题1.早期重商主义和晚期重商主义有哪些异同?2.保护幼稚产业的理论主要观点是什么?3.超保护贸易主义有哪些政策主张?4.新贸易保护主义有哪些表现?课外思考实践题1.2008年全球金融危机爆发以后,有哪些主要国家采取了哪些措施实施了贸易保护主义?2.新的贸易保护主义对我国的对外贸易产生了什么影响?你认为我们应采取哪些措施应对这些挑战?参考答案:一、名词解释1、重商主义:重商主义(mercantilism)也称作“商业本位”,是15—17世纪欧洲资本原始积累时期代表商业资本利益的经济思想和政策体系;是西方国际贸易理论史上最早的贸易保护理论学说;主张国家干预经济生活,禁止金银输出,增加金银输入。

第五章习题参考答案一、填空题1、MCS-51有5个中断源,2个中断优先级,优先级由软件填写特殊功能寄存器 IP 加以选择。

2、外中断请求标志位是 IE0 和 IE1 。

3、 RETI 指令以及任何访问 IE 和 IP 寄存器的指令执行过后,CPU不能马上响应中断。

4、8051单片机响应中断后,产生长调用指令LCALL,执行该指令的过程包括:首先把 PC的内容压入堆栈,以进行断点保护,然后把长调用指令的16位地址送 PC ,使程序执行转向程序存储器中的中断地址区。

二、选择题:1、在中断服务程序中,至少应有一条( D )。

A、传送指令B、转移指令C、加法指令D、中断返回指令2、要使MCS-51能够响应定时器T1中断,串行接口中断,它的中断允许寄存器IE的内容应是( A )。

A、 98HB、 84HC、 42HD、 22H3、MCS-51响应中断时,下列哪种操作不会发生( A )A、保护现场B、保护PCC、找到中断入口D、保护PC转入中断入口4、MCS-51中断源有( A )A、 5个B、 2个C、 3个D、6个5、计算机在使用中断方式与外界交换信息时,保护现场的工作应该是( C )A、由CPU自动完成B、在中断响应中完成C、应由中断服务程序完成D、在主程序中完成6、MCS-51的中断允许触发器内容为83H,CPU将响应的中断请求是( D )。

A、 INT0,INT1B、 T0,T1C、 T1,串行接口D、 INT0,T07、若MCS-51中断源都编程为同级,当它们同时申请中断时,CPU首先响应( B )。

A、 INT1B、 INT0C、 T1D、T08、当CPU响应串行接口中断时,程序应转到( C )。

A、 0003HB、 0013HC、 0023HD、 0033H9、执行MOV IE,#03H后,MCS-51将响应的中断是( D )。

A、 1个B、 2个C、 3个D、0个10、外部中断1固定对应的中断入口地址为( C )。

习题五一. 思考题⒈半导体存储器主要分为哪几类?简述它们的用途和区别。

答:按照存取方式分,半导体存储器主要分为随机存取存储器RAM(包括静态RAM和动态RAM)和只读存储器ROM(包括掩膜只读存储器,可编程只读存储器,可擦除只读存储器和电可擦除只读存储器)。

RAM在程序执行过程中,能够通过指令随机地对其中每个存储单元进行读\写操作。

一般来说,RAM中存储的信息在断电后会丢失,是一种易失性存储器;但目前也有一些RAM 芯片,由于内部带有电池,断电后信息不会丢失,具有非易失性。

RAM的用途主要是用来存放原始数据,中间结果或程序,与CPU或外部设备交换信息。

而ROM在微机系统运行过程中,只能对其进行读操作,不能随机地进行写操作。

断电后ROM中的信息不会消失,具有非易失性。

ROM通常用来存放相对固定不变的程序、汉字字型库、字符及图形符号等。

根据制造工艺的不同,随机读写存储器RAM主要有双极型和MOS型两类。

双极型存储器具有存取速度快、集成度较低、功耗较大、成本较高等特点,适用于对速度要求较高的高速缓冲存储器;MOS型存储器具有集成度高、功耗低、价格便宜等特点,适用于内存储器。

⒉存储芯片结构由哪几部分组成?简述各部分的主要功能。

答:存储芯片通常由存储体、地址寄存器、地址译码器、数据寄存器、读\写驱动电路及控制电路等部分组成。

存储体是存储器芯片的核心,它由多个基本存储单元组成,每个基本存储单元可存储一位二进制信息,具有0和1两种状态。

每个存储单元有一个唯一的地址,供CPU访问。

地址寄存器用来存放CPU访问的存储单元地址,该地址经地址译码器译码后选中芯片内某个指定的存储单元。

通常在微机中,访问地址由地址锁存器提供,存储单元地址由地址锁存器输出后,经地址总线送到存储器芯片内直接进行译码。

地址译码器的作用就是用来接收CPU送来的地址信号并对它进行存储芯片内部的“译码”,选择与此地址相对应的存储单元,以便对该单元进行读\写操作。

第五章 统计量及其分布习题5.11. 某地电视台想了解某电视栏目(如:每日九点至九点半的体育节目)在该地区的收视率情况,于是委托一家市场咨询公司进行一次电话访查. (1)该项研究的总体是什么? (2)该项研究的样本是什么? 解:(1)总体是该地区的全体用户;(2)样本是被访查的电话用户.2. 某市要调查成年男子的吸烟率,特聘请50名统计专业本科生作街头随机调查,要求每位学生调查100名成年男子,问该项调查的总体和样本分别是什么,总体用什么分布描述为宜?解:总体是任意100名成年男子中的吸烟人数;样本是这50名学生中每一个人调查所得到的吸烟人数;总体用二项分布描述比较合适.3. 设某厂大量生产某种产品,其不合格品率p 未知,每m 件产品包装为一盒.为了检查产品的质量,任意抽取n 盒,查其中的不合格品数,试说明什么是总体,什么是样本,并指出样本的分布. 解:总体是全体盒装产品中每一盒的不合格品数;样本是被抽取的n 盒产品中每一盒的不合格品数;总体的分布为X ~ b (m , p ),x m x qp x m x X P −⎟⎟⎠⎞⎜⎜⎝⎛==}{,x = 0, 1, …, n , 样本的分布为nn x m x n x m x x m x n n q p x m q p x m q p x m x X x X x X P −−−⎟⎟⎠⎞⎜⎜⎝⎛⎟⎟⎠⎞⎜⎜⎝⎛⋅⎟⎟⎠⎞⎜⎜⎝⎛====L L 2211212211},,,{ ∑∑⋅⎟⎟⎠⎞⎜⎜⎝⎛===−=∏ni tni tx mn x ni i q px m 111.4. 为估计鱼塘里有多少鱼,一位统计学家设计了一个方案如下:从鱼塘中打捞出一网鱼,计有n 条,涂上不会被水冲刷掉的红漆后放回,一天后再从鱼塘里打捞一网,发现共有m 条鱼,而涂有红漆的鱼则有k 条,你能估计出鱼塘里大概有多少鱼吗?该问题的总体和样本又分别是什么呢? 解:设鱼塘里有N 条鱼,有涂有红漆的鱼所占比例为Nn , 而一天后打捞出的一网鱼中涂有红漆的鱼所占比例为m k,估计mk N n ≈,故估计出鱼塘里大概有kmnN ≈条鱼;总体是鱼塘里的所有鱼;样本是一天后再从鱼塘里打捞出的一网鱼. 5. 某厂生产的电容器的使用寿命服从指数分布,为了了解其平均寿命,从中抽出n 件产品测其使用寿命,试说明什么是总体,什么是样本,并指出样本的分布. 解:总体是该厂生产的全体电容器的寿命;样本是被抽取的n 件电容器的寿命;总体的分布为X ~ e (λ ),p (x ) = λ e λ x ,x > 0,样本的分布为11212(,,,)e e e enin i x x x x n n p x x x λλλλλλλλ=∑=⋅=L L ,x i > 0.6. 美国某高校根据毕业生返校情况纪录,宣布该校毕业生的年平均工资为5万美元,你对此有何评论? 解:返校的毕业生只是毕业生中一部分特殊群体,样本的抽取不具有随机性,不能反应全体毕业生的情况.习题5.21. 以下是某工厂通过抽样调查得到的10名工人一周内生产的产品数149 156 160 138 149 153 153 169 156 156 试由这批数据构造经验分布函数并作图. 解:经验分布函数0,138,0.1,138149,0.3,149153,()0.5,153156,0.8,156160,0.9,160169,1,169.n x x x F x x x x x <⎧⎪≤<⎪⎪≤<⎪=≤<⎨⎪≤<⎪≤<⎪⎪≥⎩ 作图略.2. 下表是经过整理后得到的分组样本组序 1 2 3 4 5分组区间 (38,48] (48,58] (58,68] (68,78] (78,88] 频数 3 4 8 3 2试写出此分布样本的经验分布函数.解:经验分布函数0,37.5,0.15,37.547.5,0.35,47.557.5,()0.75,57.567.5,0.9,67.577.5,1,77.5.n x x x F x x x x <⎧⎪≤<⎪⎪≤<⎪=⎨≤<⎪⎪≤<⎪≥⎪⎩3. 假若某地区30名2000年某专业毕业生实习期满后的月薪数据如下:909 1086 1120 999 1320 1091 1071 1081 1130 1336 967 1572 825 914 992 1232 950 775 1203 1025 1096 808 1224 1044 871 1164 971 950 866 738(1)构造该批数据的频率分布表(分6组); (2)画出直方图. 解:(1)最大观测值为1572,最小观测值为738,则组距为15727381406d −=≈, 区间端点可取为735,875,1015,1155,1295,1435,1575, 频率分布表为 组序 分组区间 组中值 频数 频率 累计频率 1 (735, 875] 805 6 0.2 0.2 2 (875, 1015] 945 8 0.2667 0.4667 3 (1015, 1155] 1085 9 0.3 0.7667 4 (1155, 1295] 1225 4 0.1333 0.95 (1295,0.96672 0.066671435]13651 0.03333150516 (1435,1575]合计30 1(2)作图略.4.某公司对其250名职工上班所需时间(单位:分钟)进行了调查,下面是其不完整的频率分布表:所需时间频率0~10 0.1010~20 0.2420~3030~40 0.1840~50 0.14 (1)试将频率分布表补充完整.(2)该公司上班所需时间在半小时以内有多少人?解:(1)频率分布表为组序分组区间组中值频数频率累计频率10] 5 25 0.1 0.11 (0,20] 15 60 0.24 0.342 (10,30] 25 85 0.34 0.683 (20,40] 35 45 0.18 0.864 (30,50] 45 35 0.14 15 (40,合计250 1(2)上班所需时间在半小时以内有25 + 60 + 85 = 170人.5.40种刊物的月发行量(单位:百册)如下:5954 5022 14667 6582 6870 1840 2662 45081208 3852 618 3008 1268 1978 7963 20483077 993 353 14263 1714 11127 6926 2047714 5923 6006 14267 1697 13876 4001 22801223 12579 13588 7315 4538 13304 1615 8612 (1)建立该批数据的频数分布表,取组距为1700(百册);(2)画出直方图.解:(1)最大观测值为353,最小观测值为14667,则组距为d = 1700,区间端点可取为0,1700,3400,5100,6800,8500,10200,11900,13600,15300,频率分布表为组序分组区间组中值频数频率累计频率1700] 850 9 0.225 0.2251 (0,25509 0.225 0.453400]2 (1700,42505 0.125 0.5755100]3 (3400,59504 0.1 0.6756800]4 (5100,76504 0.1 0.7758500]5 (6800,1 0.025 0.893506 (8500,10200]1 0.025 0.825110507 (10200,11900]3 0.075 0.9127508 (11900,13600]4 0.1 11445015300]9 (13600,合计30 1(2)作图略.6.对下列数据构造茎叶图472 425 447 377 341 369 412 399400 382 366 425 399 398 423 384418 392 372 418 374 385 439 408429 428 430 413 405 381 403 479381 443 441 433 399 379 386 387 解:茎叶图为34 135369, 6377, 2, 4, 9382, 4, 5, 1, 1, 6, 7399, 8, 2400, 5, 3412, 9, 8, 8, 3, 9425, 5, 3, 8, 9, 8439, 0, 3447, 3, 14546472, 97.根据调查,某集团公司的中层管理人员的年薪(单位:千元)数据如下:40.6 39.6 37.8 36.2 38.838.6 39.6 40.0 34.7 41.738.9 37.9 37.0 35.1 36.737.1 37.7 39.2 36.9 38.3试画出茎叶图.解:茎叶图为34.735. 136.2, 7, 937.0, 1, 738. 639.6, 6, 240.6, 8, 041.742.43.844.9, 545. 4习题5.31.在一本书上我们随机的检查了10页,发现每页上的错误数为:4 5 6 0 3 1 4 2 1 4试计算其样本均值、样本方差和样本标准差.解:样本均值3)41654(101=+++++=L x ; 样本方差7778.3])34()31()36()35()34[(91222222≈−+−++−+−+−=L s ;样本标准差9437.17778.3≈=s .2. 证明:对任意常数c , d ,有11()()()()()()n niiiii i x c y d x x y y n x c y d ==−−=−−+−−∑∑.证:∑∑==−+−−+−=−−ni i i n i i i d y y y c x x x d y c x 11)]())][(()[())((∑=−−+−−+−−+−−=ni i i i i d y c x d y x x y y c x y y x x 1)])(())(())(())([())(()()()()())((111d y c x n x x d y y y c x y y x x ni i ni i ni i i −−+−−+−−+−−=∑∑∑===))(())(())((00))((11d y c x n y y x x d y c x n y y x x ni i i ni i i −−+−−=−−+++−−=∑∑==.3. 设x 1 , …, x n 和y 1 , …, y n 是两组样本观测值,且有如下关系:y i = 3 x i − 4,i = 1, …, n ,试求样本均值x和y 间的关系以及样本方差2x s 和2y s 间的关系.解:4343431)43(111111−=−=⎟⎟⎠⎞⎜⎜⎝⎛−=−==∑∑∑∑====x x n n x n x n y n y ni i n i i n i i n i i ; 212121229(19)]43()43[(11)(11x n i i n i i n i i ys x x n x x n y y n s =−−=−−−−=−−=∑∑∑===. 4. 记∑==n i i n x n x 11,∑=−−=n i i n x x n s 122)(11,n = 1, 2, …,证明 )(1111n n n n x x n x x −++=++,21221)(111n n nn x x n s n n s −++−=++. 证:)(111111111111111111n n n n n n n i i n i i n x x n x x n x n n x n x n n n x n x −++=+++=++⋅+=+=+++=+=+∑∑; ⎥⎦⎤⎢⎣⎡−+−−=−=++=+=++∑∑21112112121))(1()(1)(1n n n i n i n i n i n x x n x x n x x n s ⎥⎦⎤⎢⎣⎡−+⋅+−−+−=++=∑2122112)()1(1)1()()(1n n n n n i n i x x n n x x x x n 2122112)(111)(1)(11)1(1n n n n n n i n i x x n s n n x x n n x x n n n −++−=⎥⎦⎤⎢⎣⎡−++−−−=++=∑.5. 从同一总体中抽取两个容量分别为n , m 的样本,样本均值分别为1x , 2x ,样本方差分别为21s , 22s ,将两组样本合并,其均值、方差分别为x , s 2,证明:12nx mx x n m+=+,)1)(()(1)1()1(22122212−++−+−+−+−=m n m n x x nm m n s m s n s . 证:m n x m x n x x m n x x m n x m j j n i i m j j n i i ++=⎟⎟⎠⎞⎜⎜⎝⎛++=⎟⎟⎠⎞⎜⎜⎝⎛++=∑∑∑∑====211211121111; ⎥⎦⎤⎢⎣⎡−+−−+=∑∑==m j jn i i x x x x m n s 1221212()(11 ⎥⎦⎤⎢⎣⎡−+−+−+−−+=∑∑==221222211211)()()()(11x x m x x x x n x x m n m j j n i i ⎥⎥⎦⎤⎢⎢⎣⎡⎟⎠⎞⎜⎝⎛++−+−+⎟⎠⎞⎜⎝⎛++−+−−+=221222221121)1()1(11m n x m x n x m s m m n x m x n x n s n m n 2212222122221)()()(111)1()1(m n x x mn x x nm m n m n s m s n +−+−⋅−++−+−+−=)1)(()(1)1()1(2212221−++−+−+−+−=m n m n x x nm m n s m s n . 6. 设有容量为n 的样本A ,它的样本均值为A x ,样本标准差为s A ,样本极差为R A ,样本中位数为m A .现对样本中每一个观测值施行如下变换:y = ax + b ,如此得到样本B ,试写出样本B 的均值、标准差、极差和中位数.解:b x a b x n a nb x a n b ax n y n y A ni i n i i n i i n i i B +=+⋅=+=+==∑∑∑∑====11111)(1)(11;A n i A i n i A i n iB i B s a x x n a b x a b ax n y y n s ||)(11||)(11)(11121212=−−⋅=−−+−=−−=∑∑∑===; R B = y (n ) − y (1) = a x (n ) + b − a x (1) − b = a [x (n ) − x (1)] = a R A ; 当n 为奇数时,b am b ax y m A n n B +=+==⎟⎠⎞⎜⎝⎛+⎟⎠⎞⎜⎝⎛+5.021215.0,当n 为偶数时,b am b x x ab ax b ax y y m A n n n n n n B +=++=+++=+=⎟⎠⎞⎜⎝⎛+⎟⎠⎞⎜⎝⎛⎟⎠⎞⎜⎝⎛+⎟⎠⎞⎜⎝⎛⎟⎠⎞⎜⎝⎛+⎟⎠⎞⎜⎝⎛5.01221221225.0][2][21][21,故m B 0.5 = a m A 0.5 + b .7. 证明:容量为2的样本x 1 , x 2的方差为2212)(21x x s −=. 证:221212221221222112)(214)(4)(])2()2[(121x x x x x x x x x x x x s −=−+−=+−++−−=. 8. 设x 1 , …, x n 是来自U (−1, 1) 的样本,试求)(X E 和Var(X .解:因X i ~ U (−1, 1),有0211)(=+−=i X E ,3112)11()(Var 2=+=i X ,故0)(1)1()(11===∑∑==ni i n i i X E n X n E X E ,n n nXnX n X ni in i i 31311)(Var 11Var )(Var 2121=⋅⋅==⎟⎟⎠⎞⎜⎜⎝⎛=∑∑==. 9. 设总体二阶矩存在,X 1 , …, X n 是样本,证明X X i −与)(j i X X j ≠−的相关系数为 − (n − 1) − 1.证:因X 1 , X 2 , …, X n 相互独立,有Cov (X l , X k ) = 0,(l ≠ k ), 则),(Cov ),(Cov ),(Cov ),(Cov ),(Cov X X X X X X X X X X X X j i j i j i +−−=−−)(Var ),1(Cov )1,(Cov 0X X X nX n X j j i i +−−= 22221111)(Var )(Var 1)(Var 1σσσσnn n n X X n X n j i −=+−−=+−−=,且)1,(Cov 21),(Cov 2)(Var )(Var )(Var 22i i i i i X nX n X X X X X X −+=−+=−σσ)(Var 1212222X X nn n n j −=−=−+=σσσσ,故11111)(Var )(Var ),(Cov ),(Corr 222−−=−⋅−−=−⋅−−−=−−n nn n n n X X X X X X X X X X X X j i j i j i σσσ. 10.设x 1 , x 2 ,…, x n 为一个样本,∑=−−=ni i x x n s 122)(11是样本方差,试证: 22)()1(1s x x n n ji j i =−−∑<. 证:因⎟⎟⎠⎞⎜⎜⎝⎛−−=−−=∑∑==21212211)(11x n x n x x n s n i i n i i , 则⎟⎟⎠⎞⎜⎜⎝⎛−+=−+=−=−∑∑∑∑∑∑∑∑∑∑∑==========<n i n j j i n i n j j n i n j i n i n j j i j i n i n j j i j i j i x x x x x x x x x x x x 1111211211221122221)2(21)(21)( 221212111212)1(2221221s n n x n x n x n x n x n x x x n x n n i i n i i n i n j j i n j j n i i −=⎟⎟⎠⎞⎜⎜⎝⎛−=⎟⎟⎠⎞⎜⎜⎝⎛⋅−=⎟⎟⎠⎞⎜⎜⎝⎛−+=∑∑∑∑∑∑======, 故22)()1(1s x x n n ji j i =−−∑<. 11.设总体4阶中心矩ν4 = E [X − E (X )]4存在,试对样本方差∑=−−=ni i X X n S 122(11,有 2442442442)1(3)1()2(2)1()()Var(−−+−−−−−=n n n n n S σνσνσν,其中σ 2为总体X 的方差.证:因⎥⎦⎤⎢⎣⎡−−−−=−−−−=∑∑==212122)()(11)]()[(11µµµµX n X n X X n S n i i n i i ,其中µ = E (X ), 则⎥⎦⎤⎢⎣⎡−−−−=∑=21222)()(Var )1(1)Var(µµX n X n S n i i⎭⎬⎫⎩⎨⎧−+⎟⎟⎠⎞⎜⎜⎝⎛−−−⎥⎦⎤⎢⎣⎡−−=∑∑==])(Var[)(,)(Cov 2)(Var )1(12212122µµµµX n X n X X n n i i n i i ⎭⎬⎫⎩⎨⎧−+−−−−−=∑∑==22122122)Var())(,)Cov((2)Var()1(1µµµµX n X X n X n n i i n i i , 因E (X i − µ)2 = σ 2,E (X i − µ)4 = ν4,则)(})({}])([)({)Var(441224122412σνσνµµµ−=−=−−−=−∑∑∑===n X E X E X ni ni i i ni i ,因E (X i − µ) = 0,221)Var()(σµnX X E ==−,且当i ≠ j 时,X i − µ 与X j − µ 相互独立, 则∑∑==−−−−−=−−ni i i ni i X E X E X X E X X 12222122})()(])()[({))(,)Cov((µµµµµµ∑∑==⎪⎭⎪⎬⎫⎪⎩⎪⎨⎧⋅−⎥⎥⎦⎤⎢⎢⎣⎡⎟⎟⎠⎞⎜⎜⎝⎛−⋅−=ni nk k i n X n X E 1222121)(1)(σσµµ∑∑=≠⎭⎬⎫⎩⎨⎧−⎥⎦⎤⎢⎣⎡−⋅−+−=n i i k k i i n X E X E X E n1422421)()()(1σµµµ)(11])1([144142242σνσσσν−=⎭⎬⎫⎩⎨⎧−−⋅+=∑=n n n nni ,且224122421)(1])([)()Var(⎥⎦⎤⎢⎣⎡−⎥⎦⎤⎢⎣⎡−=−−−=−∑=σµµµµn X n E X E X E X n i i42221441)()(24)(1σµµµn X X X E n j i j i n i i −⎥⎦⎤⎢⎣⎡−−⎟⎟⎠⎞⎜⎜⎝⎛+−=∑∑<= 42221441)()(6)(1σµµµn X E X E X E n j i j i ni i −⎥⎦⎤⎢⎣⎡−−+−=∑∑<= 42443424444222442)3(11])1(3[11261σσνσσνσσσνn n n n n n n n n n n +−=−−+=−⎥⎦⎤⎢⎣⎡⋅⎟⎟⎠⎞⎜⎜⎝⎛⋅+=, 故⎭⎬⎫⎩⎨⎧⎥⎦⎤⎢⎣⎡+−+−⋅−−−=4244324444222)3(1)(12)()1(1)Var(σσνσνσνn n n n n n n S⎭⎬⎫⎩⎨⎧+−+−−−−=444444422)3(1)(2)()1(1σσνσνσνn n n 2442442444444442)1(3)1()2(2)1()()3(1)2(2)()1(1−−+−−−−−=⎭⎬⎫⎩⎨⎧−+−−−−=n n n n n n n n σνσνσνσνσνσν. 12.设总体X 的3阶矩存在,设X 1 , X 2 ,…, X n 是取自该总体的简单随机样本,X 为样本均值,S 2为样本方差,试证:nS X 32),Cov(ν=,其中ν3 = E [X − E (X )]3.证:因⎥⎦⎤⎢⎣⎡−−−−=−−−−=∑∑==212122)()(11)]()[(11µµµµX n X n X X n S n i i n i i ,其中µ = E (X ), 则⎟⎟⎠⎞⎜⎜⎝⎛⎥⎦⎤⎢⎣⎡−−−−−=−=∑=21222)()(11,Cov ),Cov(),Cov(µµµµX n X n X S X S X n i i ⎥⎦⎤⎢⎣⎡−−−−−−=∑=))(,Cov())(,Cov(11212µµµµX X n X X n n i i , 因0)()(=−=−µµi X E X E ,E (X i − µ)2 = σ 2,E (X i − µ)3 = ν3,且当i ≠ j 时,X i − µ 与X j − µ 相互独立,则∑∑∑∑====−−=⎟⎟⎠⎞⎜⎜⎝⎛−−=−−n i i i ni i n k k ni i X X n X X n X X 1212112))(,Cov(1)(,)(1Cov ))(,Cov(µµµµµµ331231])()()([1ννµµµ=⋅=−−−−=∑=n nX E X E X E n n i i i i , 且31232)(1)()()())(,Cov(⎥⎦⎤⎢⎣⎡−=−−−−=−−∑=n i i X n E X E X E X E X X µµµµµµ323313313311)(1)(1ννµµn n n X E n X E n n i i n i i =⋅=−=⎥⎦⎤⎢⎣⎡−=∑∑==,故n nn n n n n S X 333232111111),Cov(νννν=−⋅−=⎟⎠⎞⎜⎝⎛⋅−−=. 13.设1X 与2X 是从同一正态总体N (µ, σ 2)独立抽取的容量相同的两个样本均值.试确定样本容量n ,使得两样本均值的距离超过σ 的概率不超过0.01. 解:因µ==)()(21X E X E ,nX X 221)Var()Var(σ==,1X 与2X 相互独立,且总体分布为N (µ, σ 2),则0)(21=−=−µµX X E ,n n n X X 222212)Var(σσσ=+=−,即⎟⎟⎠⎞⎜⎜⎝⎛−n N X X 2212,0~σ, 因01.0222212}|{|21≤⎟⎟⎠⎞⎜⎜⎝⎛Φ−=⎥⎥⎦⎤⎢⎢⎣⎡⎟⎟⎠⎞⎜⎜⎝⎛Φ−=>−n n X X P σσσ,有995.02≥⎟⎟⎠⎞⎜⎜⎝⎛Φn ,5758.22≥n ,故n ≥ 13.2698,即n 至少14个.14.利用切比雪夫不等式求抛均匀硬币多少次才能使正面朝上的频率落在 (0.4, 0.6) 间的概率至少为0.9.如何才能更精确的计算这个次数?是多少?解:设⎩⎨⎧=,,0,,1次反面朝上第次正面朝上第i i X i 有X i ~ B (1, 0.5),且正面朝上的频率为∑==ni i X n X 11,则E (X i ) = 0.5,Var (X i ) = 0.25,且5.0(=X E ,n X 25.0)(Var =, 由切比雪夫不等式得n nX P X P 2511.025.01}1.0|5.0{|}6.04.0{2−=−≥<−=<<,故当9.0251≥−n时,即n ≥ 250时,9.0}6.04.0{≥<<X P ;利用中心极限定理更精确地计算,当n 很大时∑==ni i X n X 11的渐近分布为正态分布25.0,5.0(n N , 则)2.0()2.0()25.05.04.0(25.05.06.0()4.0()6.0(}6.04.0{n n nnF F X P −Φ−Φ=−Φ−−Φ=−=<<9.01)2.0(2≥−Φ=n ,即95.0)2.0(≥Φn ,64.12.0≥n ,故当n ≥ 67.24时,即n ≥ 68时,9.0}6.04.0{≥<<X P .15.从指数总体Exp (1/θ ) 抽取了40个样品,试求X 的渐近分布.解:因θ==)((X E X E ,2401)(Var )(Var θ==n X X ,故X 的渐近分布为)401,(2θθN .16.设X 1 , …, X 25是从均匀分布U (0, 5) 抽取的样本,试求样本均值X 的渐近分布.解:因25)()(==X E X E ,1211225)05()(Var )(Var 2=×−==n X X ,故X 的渐近分布为)121,25(N . 17.设X 1 , …, X 20是从二点分布b (1, p ) 抽取的样本,试求样本均值X 的渐近分布.解:因p X E X E ==)((,20)1()(Var )(Var p p n X X −==,故X 的渐近分布为20)1(,(p p p N −.18.设X 1 , …, X 8是从正态分布N (10, 9) 中抽取的样本,试求样本均值X 的标准差.解:因89)(Var )(Var ==n X X ,故X 的标准差为423)(Var =X . 19.切尾均值也是一个常用的反映样本数据的特征量,其想法是将数据的两端的值舍去,而用剩下的当中的值为计算样本均值,其计算公式是][2])[()2]([)1]([αααααn n X X X X n n n n −+++=−++L ,其中0 < α < 1/2是切尾系数,X (1) ≤ X (2) ≤ … ≤ X (n ) 是有序样本.现我们在高校采访了16名大学生,了解他们平时的学习情况,以下数据是大学生每周用于看电视的时间:15 14 12 9 20 4 17 26 15 18 6 10 16 15 5 8 取α = 1/16,试计算其切尾均值.解:因n α = 1,且有序样本为4, 5, 6, 8, 9, 10, 12, 14, 15, 15, 15, 16, 17, 18, 20, 26,故切尾均值8571.12)20865(216116/1=++++−=L x . 20.有一个分组样本如下:区间 组中值 频数 (145,155) 150 4 (155,165) 160 8 (165,175) 170 6 (175,185) 180 2试求该分组样本的样本均值、样本标准差、样本偏度和样本峰度.解:163)2180617081604150(201=×+×+×+×=x ;2338.9]2)163180(6)163170(8)163160(4)163150[(1912222=×−+×−+×−+×−=s ; 因81]2)163180(6)163170(8)163160(4)163150[(20122222=×−+×−+×−+×−=b , 144]2)163180(6)163170(8)163160(4)163150[(20133333=×−+×−+×−+×−=b ,14817]2)163180(6)163170(8)163160(4)163150[(20144444=×−+×−+×−+×−=b ,故样本偏度1975.02/3231==b b γ,样本峰度7417.032242−=−=b b γ.21.检查四批产品,其批次与不合格品率如下:批号批量不合格品率1 100 0.052 300 0.063 250 0.04 4 150 0.03试求这四批产品的总不合格品率.解:046875.0)03.015004.025006.030005.0100(8001=×+×+×+×=p . 22.设总体以等概率取1, 2, 3, 4, 5,现从中抽取一个容量为4的样本,试分别求X (1) 和X (4) 的分布. 解:因总体分布函数为⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎨⎧≥<≤<≤<≤<≤<=,5,1,54,54,43,53,32,52,21,51,1,0)(x x x x x x x F则F (1) (x ) = P {X (1) ≤ x } = 1 − P {X (1) > x } = 1 − P {X 1 > x , X 2 > x , X 3 > x , X 4 > x } = 1 − [1 − F (x )]4⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎨⎧≥<≤<≤<≤<≤<=,5,1,54,625624,43,625609,32,625544,21,625369,1,0x x x x x x且F (4) (x ) = P {X (4) ≤ x } = P {X 1 ≤ x , X 2 ≤ x , X 3 ≤ x , X 4 ≤ x } = [F (x )]4⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎨⎧≥<≤<≤<≤<≤<=,5,1,54,625256,43,62581,32,62516,21,6251,1,0x x x x x x故X (1) 和X (4) 的分布为6251625156256562517562536954321)1(P X ; 6253696251756256562515625154321)4(PX . 23.设总体X 服从几何分布,即P {X = k } = pq k − 1,k = 1, 2, …,其中0 < p < 1,q = 1 − p ,X 1, X 2, …, X n 为该总体的样本.求X (n ) , X (1)的概率分布.解:因k k kj j q qq p pqk X P −=−−==≤∑=−11)1(}{11,k = 1, 2, …,故n k n k ni i ni i n n n q q k X P k X P k X P k X P k X P )1()1(}1{}{}1{}{}{111)()()(−==−−−=−≤−≤=−≤−≤==∏∏;且nk k n ni i ni i q q k X P k X P k X P k X P k X P −=>−−>=>−−>==−==∏∏)1(11)1()1()1(}{}1{}{}1{}{.24.设X 1 , …, X 16是来自N (8, 4) 的样本,试求下列概率(1)P {X (16) > 10}; (2)P {X (1) > 5}.解:(1)1616161)16()16()]2810([1)]10([1}10{1}10{1}10{−Φ−=−=≤−=≤−=>∏=F X P X P X P i i = 1 − [Φ(1)]16 = 1 − 0.841316 = 0.9370;(2)3308.09332.0)]5.1([285(1[)]5(1[}5{}5{16161616161)1(==Φ=−Φ−=−=>=>∏=F X P X P i i . 25.设总体为韦布尔分布,其密度函数为⎪⎭⎪⎬⎫⎪⎩⎪⎨⎧⎟⎟⎠⎞⎜⎜⎝⎛−=−mmm x mx m x p ηηηexp ),;(1,x > 0, m > 0, η > 0. 现从中得到样本X 1 , …, X n ,证明X (1) 仍服从韦布尔分布,并指出其参数. 解:总体分布函数mm mmx xt xmt xt mm xt t mtt t p x F ⎟⎟⎠⎞⎜⎜⎝⎛−⎟⎟⎠⎞⎜⎜⎝⎛−⎟⎟⎠⎞⎜⎜⎝⎛−⎟⎟⎠⎞⎜⎜⎝⎛−−−=−=⎟⎟⎠⎞⎜⎜⎝⎛===∫∫∫ηηηηηηe1e d ed ed )()(00010,x > 0,则X (1) 的密度函数为111(1)11()[1()]()eeemmmmx x x m m m n n n mmmxmnxp x n F x p x n ηηηηη⎛⎞⎛⎞⎛⎞⎛⎞−−−−−−−−⎜⎟⎜⎟⎜⎟−⎝⎠⎝⎠⎝⎠=−=⋅==,故X (1) 服从参数为⎟⎟⎠⎞⎜⎜⎝⎛m n m η,的韦布尔分布. 26.设总体密度函数为p (x ) = 6 x (1 − x ), 0 < x < 1,X 1 , …, X 9是来自该总体的样本,试求样本中位数的分布. 解:总体分布函数3203223)23(d )1(6d )()(x x t t t t t t t p x F xxx−=−=−==∫∫,0 < x < 1,因样本容量n = 9,有样本中位数)5(215.0x x m n ==⎟⎠⎞⎜⎝⎛+,其密度函数为)1(6)231()23(!4!4!9)()](1[)]([!4!4!9)(432432445x x x x x x x p x F x F x p −⋅+−−⋅=−⋅=. 27.证明公式∫∑−−=−−−−=−⎟⎟⎠⎞⎜⎜⎝⎛110)1()!1(!!)1(p r n r rk k n k dx x x r n r n p p k n ,其中0 ≤ p ≤ 1. 证:设总体X 服从区间(0, 1)上的均匀分布,X 1, X 2, …, X n 为样本,X (1), X (2), …, X (n )是顺序统计量,则样本观测值中不超过p 的样品个数服从二项分布b (n , p ),即最多有r 个样品不超过p 的概率为∑=−+−⎟⎟⎠⎞⎜⎜⎝⎛=>rk kn k r p p k n p X P 0)1()1(}{,因总体X 的密度函数与分布函数分别为⎩⎨⎧<<=.,0;10,1)(其他x x p ⎪⎩⎪⎨⎧≥<≤<=.1,1;10,;0,0)(x x x x x F则X (r + 1)的密度函数为⎪⎩⎪⎨⎧<<−−−=−−−=−−−−+.,0,10,)1()!1(!!)()](1[)]([)!1(!!)(111其他x x x r n r n x p x F x F r n r n x p r n r r n r r 故∫∑−−+=−−−−=>=−⎟⎟⎠⎞⎜⎜⎝⎛11)1(0)1()!1(!!}{)1(p r n r r rk kn k dx x x r n r n p X P p p k n . 28.设总体X 的分布函数F (x )是连续的,X (1), …, X (n )为取自此总体的次序统计量,设ηi = F (X (i )),试证: (1)η1 ≤ η2 ≤ … ≤ ηn ,且ηi 是来自均匀分布U (0, 1)总体的次序统计量;(2)1)(+=n iE i η,)2()1()1()Var(2++−+=n n i n i i η,1 ≤ i ≤ n ; (3)ηi 和ηj 的协方差矩阵为⎟⎟⎟⎟⎠⎞⎜⎜⎜⎜⎝⎛+−+−+−+−2)1(2)1(2)1(2)1(22212111n a a n a a n a a n a a 其中11+=n i a ,12+=n j a . 注:第(3)问应要求i < j . 解:(1)首先证明Y = F (X )的分布是均匀分布U (0, 1),因分布函数F (x )连续,对于任意的y ∈ (0, 1),存在x ,使得F (x ) = y , 则F Y ( y ) = P {Y = F (X ) ≤ y } = P {F (X ) ≤ F (x )} = P {X ≤ x } = F (x ) = y , 即Y = F (X )的分布函数是⎪⎩⎪⎨⎧≥<≤<=.1,1;10,;0,0)(y y y y y F Y可得Y = F (X )的分布是均匀分布U (0, 1),即F (X 1), F (X 2), …, F (X n )是均匀分布总体U (0, 1)的样本, 因分布函数F (x )单调不减,ηi = F (X (i )),且X (1) ≤ X (2) ≤ … ≤ X (n )是总体X 的次序统计量, 故η1 ≤ η2 ≤ … ≤ ηn ,且ηi 是来自均匀分布U (0, 1)总体的次序统计量; (2)因均匀分布U (0, 1) 的密度函数与分布函数分别为⎩⎨⎧<<=.,0;10,1)(其他y y p Y ⎪⎩⎪⎨⎧≥<≤<=.1,1;10,;0,0)(y y y y y F Y则ηi = F (X (i ))的密度函数为⎪⎩⎪⎨⎧<<−−−=−−−=−−−−.,0,10,)1()!()!1(!)()](1[)]([)!()!1(!)(11其他y y y i n i n y p y F y F i n i n y p i n i Y in Y i Y i即ηi 服从贝塔分布Be (i , n − i + 1),即Be (a , b ),其中a = i ,b = n − i + 1,故1)(+=+=n i b a a E i η,)2()1()1()1()()Var(22++−+=+++=n n i n i b a b a ab i η,1 ≤ i ≤ n ; (3)当i < j 时,(ηi , ηj )的联合密度函数为z y Y Y j n Y i j Y Y i Y ij z p y p z F y F z F y F j n i j i n z y p <−−−−−−−−−−=I )()()](1[)]()([)]([)!()!1()!1(!),(111011I )1()()!()!1()!1(!<<<−−−−−−−−−−=z y j n i j i z y z y j n i j i n , 则∫∫∫∫−−−+∞∞−+∞∞−−⋅−−−−−=⋅=1001)1()()!()!1()!1(!),()(z j n i j i ij j i dy z z y z y dz j n i j i n dydz z y p yz E ηη, 令y = zu ,有dy = zdu ,且当y = 0时,u = 0;当y = z 时,u = 1,则∫∫⋅−−=−⋅−−−−−−−1101)()()1()1()(zdu zu z zu z z dy z z y z y i j i j n zj n i j ij n j j n j i j i j j n z z j i j i i j i B z z du u u z z z −+−+−−−−−−=−+⋅−=−⋅−=∫)1(!)!1(!),1()1()1()1(1111,即∫−+−−−−−−−=101)1(!)!1(!)!()!1()!1(!)(dz z z j i j i j n i j i n E jn j j i ηη )1,2(!)!1(!)!()!1()!1(!+−+−−⋅−−−−=j n j B j i j i j n i j i n)2)(1()1()!2()!()!1(!)!1(!)!()!1()!1(!+++=+−+⋅−−⋅−−−−=n n j i n j n j j i j i j n i j i n , 可得)2()1()1(11)2)(1()1()()()(),Cov(2++−+=+⋅+−+++=−=n n j n i n j n i n n j i E E E j i j i j i ηηηηηη, 因11+=n i a ,12+=n j a , 则2)1()2()1()1(),Cov(212+−=++−+=n a a n n j n i j i ηη, 且2)1()2()1()1()Var(112+−=++−+=n a a n n i n i i η,2)1()2()1()1()Var(222+−=++−+=n a a n n j n j jη, 故ηi 和ηj 的协方差矩阵为⎟⎟⎟⎟⎠⎞⎜⎜⎜⎜⎝⎛+−+−+−+−=⎟⎟⎠⎞⎜⎜⎝⎛2)1(2)1(2)1(2)1()Var(),Cov(),Cov()Var(22212111n a a n a a n a a n a a j j i j i i ηηηηηη. 29.设总体X 服从N (0, 1),从此总体获得一组样本观测值x 1 = 0, x 2 = 0.2, x 3 = 0.25, x 4 = −0.3, x 5 = −0.1, x 6 = 2, x 7 = 0.15, x 8 = 1, x 9 = −0.7, x 10 = −1.(1)计算x = 0.15(即x (6))处的E [F (X (6))],Var[F (X (6))]; (2)计算F (X (6))在x = 0.15的分布函数值.解:(1)根据第28题的结论知1)]([)(+=n iX F E i ,)2()1()1()](Var[2)(++−+=n n i n i X F i ,且n = 10, 故116)]([)6(=X F E ,2425121156)](Var[2)6(=××=X F ; (2)因F (X (i ))服从贝塔分布Be (i , n − i + 1),即这里的F (X (6))服从贝塔分布Be (6, 5),则F (X (6))在x = 0.15的分布函数值为∫−⋅=15.00456)1(!4!5!10)15.0(dx x x F , 故根据第27题的结论知0014.085.015.0101)1(!4!5!10)15.0(501015.00456=××⎟⎟⎠⎞⎜⎜⎝⎛−=−⋅=∑∫=−k k k k dx x x F . 30.在下列密度函数下分别寻求容量为n 的样本中位数m 0.5的渐近分布.(1)p (x ) = 6x (1 − x ),0 < x < 1;(2)⎭⎬⎫⎩⎨⎧−−=222)(exp π21)(σµσx x p ; (3)⎩⎨⎧<<=.,0;10,2)(其他x x x p (4)||e 2)(x x p λλ−=.解:样本中位数m 0.5的渐近分布为⎟⎟⎠⎞⎜⎜⎝⎛⋅)(41,5.025.0x p n x N ,其中p (x )是总体密度函数,x 0.5是总体中位数, (1)因p (x ) = 6x (1 − x ),0 < x < 1,有35.025.003205.023)23()1(6)(5.05.05.0x x x x dx x x x F x x −=−=−==∫,则x 0.5 = 0.5,有nn p n 91)5.05.06(41)5.0(4122=×××=⋅, 故样本中位数m 0.5的渐近分布为⎟⎠⎞⎜⎝⎛n N 91,5.0;(2)因⎭⎫⎩⎨⎧−−=222)(exp π21)(σµσx x p ,有0.5 = F (x 0.5) = F (µ), 则x 0.5 = µ ,有n n p n 2ππ2141)(41222σσµ=⎟⎟⎠⎞⎜⎜⎝⎛×=⋅, 故样本中位数m 0.5的渐近分布为⎟⎟⎠⎞⎜⎜⎝⎛n N 2π,2σµ;(3)因⎩⎨⎧<<=.,0;10,2)(其他x x x p 有25.00205.05.05.02)(5.0x x xdx x F x x ====∫, 则215.0=x ,有n n p n 8121241214122=⎟⎠⎞⎜⎝⎛××=⎟⎠⎞⎜⎝⎛⋅, 故样本中位数m 0.5的渐近分布为⎟⎠⎞⎜⎝⎛n N 81,21; (4)因||e 2)(x x p λλ−=,有0.5 = F (x 0.5) = F (0),则x 0.5 = 0,有2221241)0(41λλn n p n =⎟⎠⎞⎜⎝⎛×=⋅, 故样本中位数m 0.5的渐近分布为⎟⎠⎞⎜⎝⎛21,0λn N .31.设总体X 服从双参数指数分布,其分布函数为⎪⎩⎪⎨⎧≤>⎭⎬⎫⎩⎨⎧−−−=.,0;,exp 1)(µµσµx x x x F其中,−∞ < µ < +∞,σ > 0,X (1) ≤ … ≤ X (n )为样本的次序统计量.试证明)(2)1()1()(−−−−i i X X i n σ服从自由度为2的χ 2分布(i = 2, …, n ). 注:此题有误,讨论的随机变量应为)(2)1()1()(−−+−i i X X i n σ.证:因(X (i − 1), X (i ))的联合密度函数为z y i n i i i z p y p z F y F i n i n z y p <−−−−−−=I )()()](1[)]([)!()!2(!),(2)1( z y in i z y z y i n i n <<−−⎭⎬⎫⎩⎨⎧−−⋅⎭⎬⎫⎩⎨⎧−−⋅⎥⎦⎤⎢⎣⎡⎭⎬⎫⎩⎨⎧−−⎥⎦⎤⎢⎣⎡⎭⎬⎫⎩⎨⎧−−−−−=µσµσσµσσµσµI exp 1exp 1exp exp 1)!()!2(!2z y i n i z y y i n i n <<+−−⎥⎦⎤⎢⎣⎡⎭⎬⎫⎩⎨⎧−−⎥⎦⎤⎢⎣⎡⎭⎬⎫⎩⎨⎧−−−⎭⎬⎫⎩⎨⎧−−−−=µσµσµσµσI exp exp 1exp )!()!2(!122,则T = X (i ) − X (i − 1)的密度函数为∫+∞∞−−⋅⋅+=dy t y y p t p i i T 1),()()1(∫∞++−−⎥⎦⎤⎢⎣⎡⎭⎬⎫⎩⎨⎧−+−⎥⎦⎤⎢⎣⎡⎭⎬⎫⎩⎨⎧−−−⎭⎬⎫⎩⎨⎧−−−−=µσµσµσµσdy t y y y i n i n i n i 122exp exp 1exp )!()!2(!∫∞+−+−+−⎥⎦⎤⎢⎣⎡⎭⎫⎩⎨⎧−−−⎥⎦⎤⎢⎣⎡⎭⎬⎫⎩⎨⎧−−−⎥⎦⎤⎢⎣⎡⎭⎬⎫⎩⎨⎧−−⎥⎦⎤⎢⎣⎡⎭⎬⎫⎩⎨⎧−−−=µσµσσµσµσσy d y y t i n i n i i n i n exp )(exp 1exp exp )!()!2(!2112∫−−⎥⎦⎤⎢⎣⎡⎭⎬⎫⎩⎨⎧−−−=−+−+−012112)()1(exp )!()!2(!du u ut i n i n i i n i n σσσ∫−+−−⎭⎬⎫⎩⎨⎧+−−−−=1021)1()1(exp )!()!2(!du u ut i n i n i n i i n σσ )1,2()1(exp )!()!2(!−+−⎭⎬⎫⎩⎨⎧+−−−−=i i n B t i n i n i n σσ⎭⎬⎫⎩⎨⎧+−−+−=−+−⋅⎭⎬⎫⎩⎨⎧+−−−−=σσσσt i n i n n i i n t i n i n i n )1(exp 1!)!2()!1()1(exp )!()!2(!,t > 0,可得T i n X X i n S i i σσ2)1()(2)1()1()(+−=−+−=−的密度函数为⎭⎬⎫⎩⎨⎧−=+−⋅⎭⎬⎫⎩⎨⎧−+−=+−⋅⎟⎟⎠⎞⎜⎜⎝⎛+−=2exp 21)1(22exp 1)1(2)1(2)(s i n s i n i n s i n p s p T S σσσσ,s > 0, 故)(2)1()1()(−−+−=i i X X i n S σ服从参数为21的指数分布,也就是服从自由度为2的χ 2分布. 32.设总体X 的密度函数为⎩⎨⎧<<=.,0;10,3)(2其他x x x p X (1) ≤ X (2) ≤ … ≤ X (5)为容量为5的取自此总体的次序统计量,试证)4()2(X X 与X (4)相互独立.z −证:因总体X 的密度函数和分布函数分别为⎩⎨⎧<<=.,0;10,3)(2其他x x x p ⎪⎩⎪⎨⎧≥<≤<=.1,1;10,;0,0)(3x x x x x F 则(X (2), X (4))的联合密度函数为)4()2(I )()()](1[)]()([)]([!1!1!1!5),()4()2(1)4(1)2()4(1)2()4()2(24x x x p x p x F x F x F x F x x p <−−⋅⋅=103)4(3)2(3)4(2)4(5)2(102)4(2)2(3)4(3)2(3)4(3)2()4()2()4()2(I )1)((1080I 33)1)((120<<<<<<−−=⋅⋅−−=x x x x x x x x x x x x x x x ,设)4()2(1X X Y =,Y 2 = X (4),有X (2) = Y 1Y 2,X (4) = Y 2,则(X (2), X (4))关于( Y 1 , Y 2 )的雅可比行列式为21221)4()2(1),(),(y y y y y x x J ==∂∂=,且0 < X (2) ≤ X (4) < 1对应于0 < Y 1 < 1, 0 < Y 2 < 1,可得(Y 1 , Y 2 )的联合密度函数为210,10323213222521221242121I )1]()([)(1080||),(),(y y y y y y y y J y y y p y y p y y ⋅−−=⋅=<<<<103211210315121I )1(I )1(1080<<<<−⋅−=y y y y y y ,由于(Y 1 , Y 2 , …, Y n )的联合密度函数p ( y 1 , y 2)可分离变量, 故)4()2(1X X Y =与Y 2 = X (4)相互独立.33.(1)设X (1)和X (n )分别为容量n 的最小和最大次序统计量,证明极差R n = X (n ) − X (1)的分布函数∫+∞∞−−−+=dy y p y F x y F n x F n R n )()]()([)(1其中F ( y )与p ( y )分别为总体的分布函数与密度函数;(2)利用(1)的结论,求总体为指数分布Exp (λ)时,样本极差R n 的分布. 注:第(1)问应添上x > 0的要求. 解:(1)方法一:增补变量法因(X (1), X (n ))的联合密度函数为z y n z y n n z p y p y F z F n n z p y p y F z F n n z y p <−<−−−=−−=I )()()]()()[1(I )()()]()([)!2(!),(221, 对于其函数R n = X (n ) − X (1),增补变量W = X (1),⎩⎨⎧−==.;y z r y w 反函数为⎩⎨⎧+==.;r w z w y 其雅可比行列式为11101==J ,则R n 的密度函数为∫+∞∞−>−+−+−=dw r w p w p w F r w F n n r p r n R n 02I )()()]()()[1()(,故R n = X (n ) − X (1)的分布函数为∫∫∫∞−+∞∞−>−∞−+−+−==x r n x R R dw r w p w p w F r w F n n dr dr r p x F n n 02I )()()]()()[1()()(∫∫+∞∞−∞−>−+−+−=xr n dr r w p w p w F r w F n n dw 02I )()()]()()[1(∫∫+∞∞−−+−+−=xn dr r w p w F r w F dw w p n n 02)()]()([)()1(∫∫+∞∞−−+−+−=xn r w dF w F r w F dw w p n n 02)()]()([)()1(∫+∞∞−−−+−⋅−=x n w F r w F n dw w p n n 01)]()([11)()1(∫+∞∞−−−+=dw w p w F x w F n n )()]()([1 ∫+∞∞−−−+=dy y p y F x y F n n )()]()([1,x > 0;方法二:分布函数法因(X (1), X (n ))的联合密度函数为z y n z y n n z p y p y F z F n n z p y p y F z F n n z y p <−<−−−=−−=I )()()]()()[1(I )()()]()([)!2(!),(221, 故R n = X (n ) − X (1)的分布函数为∫∫+∞∞−+∞−=≤−==xy n n n R dz z y p dy x X X R P x F n ),(}{)(1)1()(∫∫+∞∞−+−−−=xy yn dz z p y p y F z F dy n n )()()]()([)1(2∫∫+∞∞−+−−⋅−=xy yn z F d y F z F y p dy n n )]([)]()([)()1(2∫∫+∞∞−−+∞∞−+−−+=−−⋅⋅−=dy y p y F x y F n y F z F n y p dy n n n x y y n )()]()([)]()([11)()1(11,x > 0;(2)因指数分布Exp (λ)的密度函数与分布函数分别为⎩⎨⎧≤>=−.0,0;0,e )(x x x p x λλ ⎩⎨⎧≤>−=−.0,0;0,e 1)(x x x F x λ故R n = X (n ) − X (1)的分布函数为∫∫+∞−−−+−+∞∞−−⋅−−−=−+=01)(1e )]e 1()e 1[()()]()([)(dy n dy y p y F x y F n x F y n y x y n R n λλλλ101011)e 1()(e 1)e 1(e )1()e 1()(e −−+∞−−−+∞−−−−−−=⎟⎠⎞⎜⎝⎛−⋅−=−⋅−=∫n x n y n x y n x n y n n d n λλλλλλ,x > 0.34.设X 1 , …, X n 是来自U (0, θ ) 的样本,X (1) ≤ … ≤ X (n ) 为次序统计量,令)1()(+=i i i X X Y ,i = 1, …, n − 1,Y n = X (n ) ,证明Y 1 , …, Y n 相互独立.。

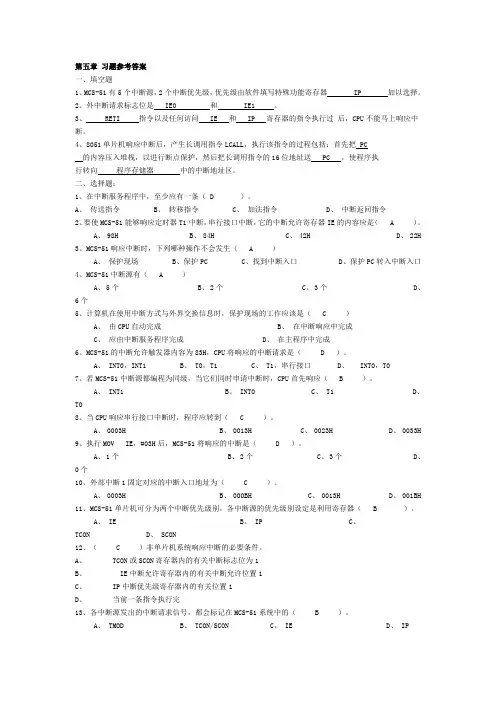

结构力学 第五章习题 参考答案2005级 TANG Gui-he (整理)5-1 试用结点法计算图示桁架各杆的内力。

5-2 试用结点法计算图示桁架各杆的内力。

解:由整体平衡条件可解得支座反力 F A =1.5F F B =1.5F 取结点A 为隔离体,如图,用数解法可解得 F A C =-2.12F F A B =1.5F 同理,依次取结点B 、C 、 D 、E 为隔离体,并由对称性可得各杆的内力如图。

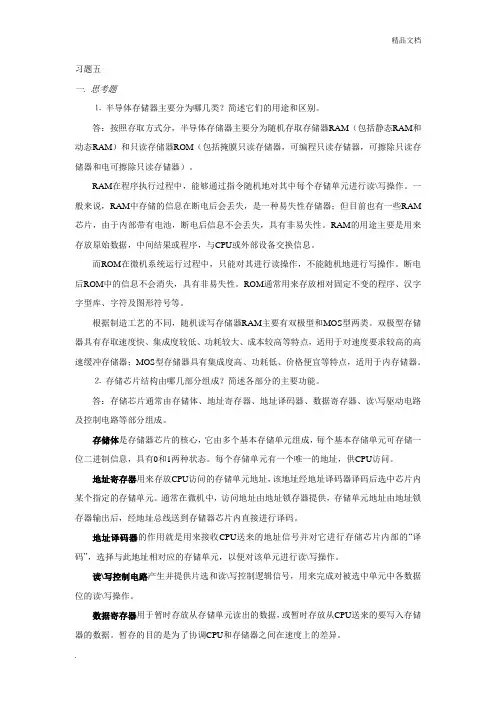

4 * 8m60k N60k N6M 2MA B C D E FG H 解:由 M H =0 可得支座F a y=75kN.由 F Y=0 得 F h y=45kN 取 A 结点为隔离体,利用数解法可得 F N AB=-100kN. F NAC=125kN. 再取 C 点为隔离体,利用投影法和力平衡 可得 F N BC=-50,F NCE=103.1kN.同理依次取 B , D , E , G , F 可得各杆内力(如图所标)AC-60k N -90k N -100k N 45k N75k N125k N 75k N 42.4k N61.8k N 103.1k N -60k N -50k N -30k N55-4试判断图示桁架中的零杆。

解:图中红色的杆件为零杆在杆中标有 为零杆其中用到K 型和T 型结构判断原理5-5试用截面法计算图示桁架中指定杆件的内力。

2解:(1)求出支座竖向反力为2.5F (↑),(2)作截面I -I ,由∑M A=0得: 2.5F ×15-10F -5F +6F N 1=0 → F N 1=-3.75F (3)由∑M B=0得: 2.5F ×10-F ×5-F N 2×6=0 → F N 2=3.33F (4)利用勾股定理求出A B 杆长7.8F N 4x =5F N 4/3.84 由∑M C=0得: 2.5F ×10-5F +F N 1×6+6×5F N 4/7.8=0 → F N 4=0.65F (5)取结点B 为分析对象,由∑F Y=0得: F N 4×6/7.8+F N 3=0 → F N 3=-0.5F5-6试用截面法计算图示桁架中指定杆件的内力。

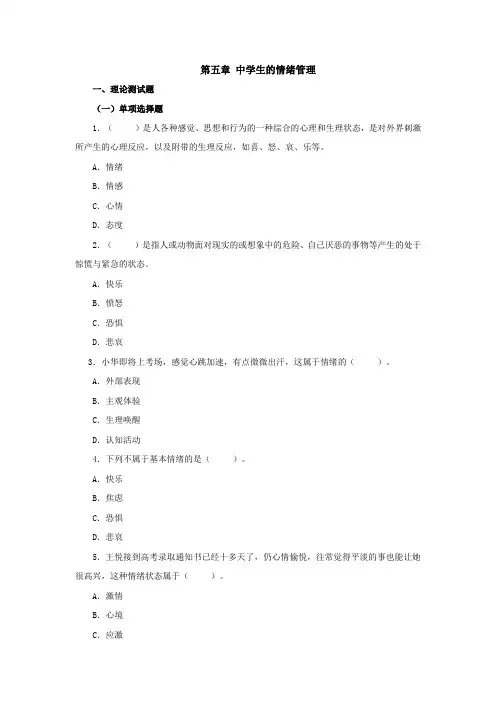

第五章中学生的情绪管理一、理论测试题(一)单项选择题1.()是人各种感觉、思想和行为的一种综合的心理和生理状态,是对外界刺激所产生的心理反应,以及附带的生理反应,如喜、怒、哀、乐等。

A.情绪B.情感C.心情D.态度2.()是指人或动物面对现实的或想象中的危险、自己厌恶的事物等产生的处于惊慌与紧急的状态。

A.快乐B.愤怒C.恐惧D.悲哀3.小华即将上考场,感觉心跳加速,有点微微出汗,这属于情绪的()。

A.外部表现B.主观体验C.生理唤醒D.认知活动4.下列不属于基本情绪的是()。

A.快乐B.焦虑C.恐惧D.悲哀5.王悦接到高考录取通知书已经十多天了,仍心情愉悦,往常觉得平淡的事也能让她很高兴,这种情绪状态属于()。

A.激情B.心境C.应激6.“情急生智”所描述的一种情绪状态是()。

A.心境B.理智C.应激D.激情7.“忧者见之则忧,喜者见之则喜”,这是受一个人的()影响所致。

A.激情B.心境C.应激D.热情8.()是一种猛烈、迅疾和短暂的情绪,类似于平时说的激动。

A.快乐B.应激C.心境D.激情9.狂喜、恐惧的情绪状态属于()。

A.激情B.热情C.应激D.心境10.学生临考的怯场属于()。

A.应激B.心境C.激情D.热情11.车祸、地震、水灾等突如其来的灾难引起的情绪体验是()。

A.心境B.激情C.应激12.晓东在解决了困扰他许久的数学难题后出现的喜悦感属于()。

A.道德感B.理智感C.美感D.效能感13.求知欲属于()。

A.道德感B.理智感C.美感D.应激14.“先天下之忧而忧,后天下之乐而乐”是()。

A.道德感B.理智感C.美感D.热情15.当同学们获悉本班取得学校合唱比赛第一名的成绩时欣喜若狂。

他们的情绪状态属于()。

A.心境B.激情C.应激D.热情16.当人们遇到突然出现的事件或意外发生危险时,为了应付这类瞬息万变的紧急情境,就得果断地采取决定。

这种情况属于()。

A.激情B.应激C.快乐D.心境17.()用因素分析的方法,提出人类具有8~11种基本情绪,它们是兴趣、惊奇、痛苦、厌恶、愉快、愤怒、恐惧、悲伤、害羞、轻蔑、自罪感。

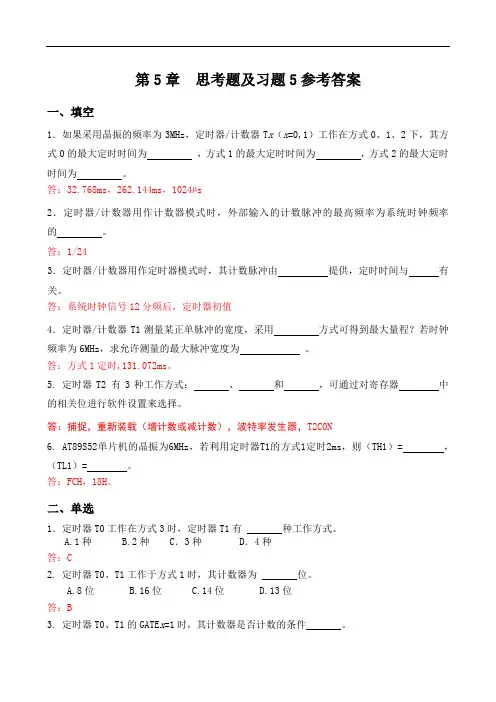

第5章思考题及习题5参考答案一、填空1.如果采用晶振的频率为3MHz,定时器/计数器T x(x=0,1)工作在方式0、1、2下,其方式0的最大定时时间为,方式1的最大定时时间为,方式2的最大定时时间为。

答:32.768ms,262.144ms,1024µs2.定时器/计数器用作计数器模式时,外部输入的计数脉冲的最高频率为系统时钟频率的。

答:1/243.定时器/计数器用作定时器模式时,其计数脉冲由提供,定时时间与有关。

答:系统时钟信号12分频后,定时器初值4.定时器/计数器T1测量某正单脉冲的宽度,采用方式可得到最大量程?若时钟频率为6MHz,求允许测量的最大脉冲宽度为。

答:方式1定时,131.072ms。

5. 定时器T2 有3种工作方式:、和,可通过对寄存器中的相关位进行软件设置来选择。

答:捕捉,重新装载(增计数或减计数),波特率发生器,T2CON6. AT89S52单片机的晶振为6MHz,若利用定时器T1的方式1定时2ms,则(TH1)= ,(TL1)= 。

答:FCH,18H。

二、单选1.定时器T0工作在方式3时,定时器T1有种工作方式。

A.1种B.2种 C.3种D.4种答:C2. 定时器T0、T1工作于方式1时,其计数器为位。

A.8位B.16位C.14位D.13位答:B3. 定时器T0、T1的GATE x=1时,其计数器是否计数的条件。

A. 仅取决于TR x状态B. 仅取决于GATE位状态C. 是由TR x和INT x两个条件来共同控制D. 仅取决于INT x的状态答:C4. 定时器T2工作在自动重装载方式时,其计数器为位。

A.8位B. 13位C.14位D. 16位答:D5. 要想测量INT0引脚上的正单脉冲的宽度,特殊功能寄存器TMOD的内容应为。

A.87HB. 09HC.80HD. 00H答:B三、判断对错1.下列关于T0、T1的哪些说法是正确的。

A.特殊功能寄存器SCON,与定时器/计数器的控制无关。

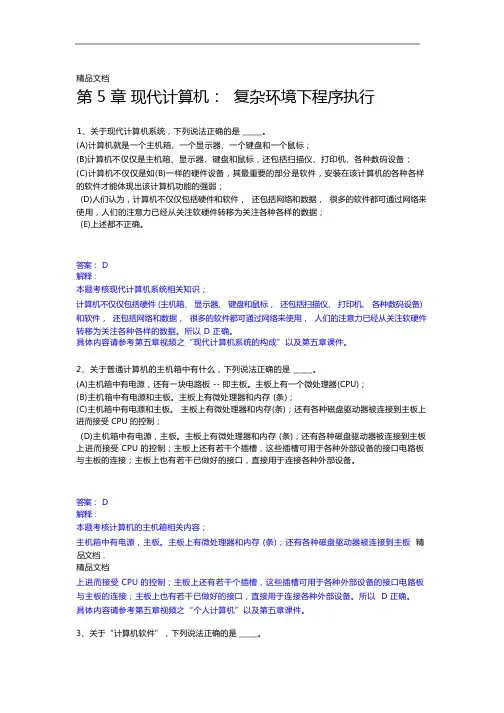

精品文档第 5 章现代计算机:复杂环境下程序执行1、关于现代计算机系统,下列说法正确的是 _____。

(A)计算机就是一个主机箱、一个显示器、一个键盘和一个鼠标;(B)计算机不仅仅是主机箱、显示器、键盘和鼠标,还包括扫描仪、打印机、各种数码设备;(C)计算机不仅仅是如(B)一样的硬件设备,其最重要的部分是软件,安装在该计算机的各种各样的软件才能体现出该计算机功能的强弱;(D)人们认为,计算机不仅仅包括硬件和软件,还包括网络和数据,很多的软件都可通过网络来使用,人们的注意力已经从关注软硬件转移为关注各种各样的数据;(E)上述都不正确。

答案: D解释:本题考核现代计算机系统相关知识;计算机不仅仅包括硬件 (主机箱、显示器、键盘和鼠标,还包括扫描仪、打印机、各种数码设备) 和软件,还包括网络和数据,很多的软件都可通过网络来使用,人们的注意力已经从关注软硬件转移为关注各种各样的数据。

所以 D 正确。

具体内容请参考第五章视频之“现代计算机系统的构成”以及第五章课件。

2、关于普通计算机的主机箱中有什么,下列说法正确的是 _____。

(A)主机箱中有电源,还有一块电路板 -- 即主板。

主板上有一个微处理器(CPU);(B)主机箱中有电源和主板。

主板上有微处理器和内存 (条);(C)主机箱中有电源和主板。

主板上有微处理器和内存(条);还有各种磁盘驱动器被连接到主板上进而接受 CPU 的控制;(D)主机箱中有电源,主板。

主板上有微处理器和内存 (条);还有各种磁盘驱动器被连接到主板上进而接受 CPU 的控制;主板上还有若干个插槽,这些插槽可用于各种外部设备的接口电路板与主板的连接;主板上也有若干已做好的接口,直接用于连接各种外部设备。

答案: D解释:本题考核计算机的主机箱相关内容;主机箱中有电源,主板。

主板上有微处理器和内存 (条);还有各种磁盘驱动器被连接到主板精品文档.精品文档上进而接受 CPU 的控制;主板上还有若干个插槽,这些插槽可用于各种外部设备的接口电路板与主板的连接;主板上也有若干已做好的接口,直接用于连接各种外部设备。

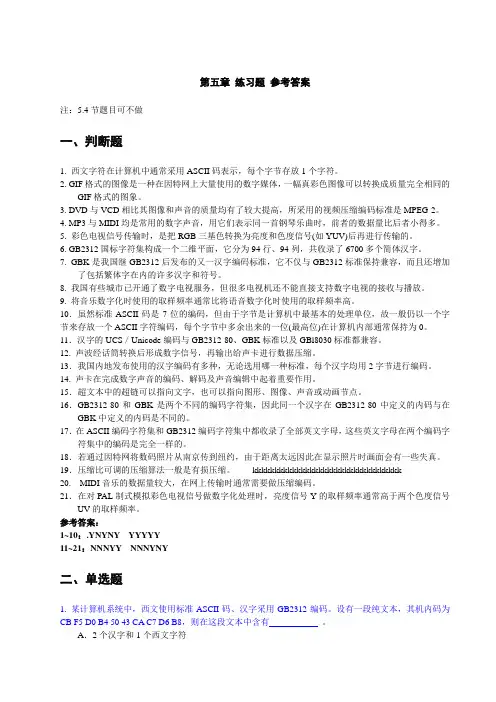

第五章练习题参考答案注:5.4节题目可不做一、判断题1. 西文字符在计算机中通常采用ASCII码表示,每个字节存放1个字符。

2. GIF格式的图像是一种在因特网上大量使用的数字媒体,一幅真彩色图像可以转换成质量完全相同的GIF格式的图象。

3. DVD与VCD相比其图像和声音的质量均有了较大提高,所采用的视频压缩编码标准是MPEG-2。

4. MP3与MIDI均是常用的数字声音,用它们表示同一首钢琴乐曲时,前者的数据量比后者小得多。

5. 彩色电视信号传输时,是把RGB三基色转换为亮度和色度信号(如YUV)后再进行传输的。

6. GB2312国标字符集构成一个二维平面,它分为94行、94列,共收录了6700多个简体汉字。

7. GBK是我国继GB2312后发布的又一汉字编码标准,它不仅与GB2312标准保持兼容,而且还增加了包括繁体字在内的许多汉字和符号。

8. 我国有些城市已开通了数字电视服务,但很多电视机还不能直接支持数字电视的接收与播放。

9. 将音乐数字化时使用的取样频率通常比将语音数字化时使用的取样频率高。

10.虽然标准ASCII码是7位的编码,但由于字节是计算机中最基本的处理单位,故一般仍以一个字节来存放一个ASCII字符编码,每个字节中多余出来的一位(最高位)在计算机内部通常保持为0。

11.汉字的UCS/Unicode编码与GB2312-80、GBK标准以及GBl8030标准都兼容。

12. 声波经话筒转换后形成数字信号,再输出给声卡进行数据压缩。

13.我国内地发布使用的汉字编码有多种,无论选用哪一种标准,每个汉字均用2字节进行编码。

14. 声卡在完成数字声音的编码、解码及声音编辑中起着重要作用。

15.超文本中的超链可以指向文字,也可以指向图形、图像、声音或动画节点。

16.GB2312-80和GBK是两个不同的编码字符集,因此同一个汉字在GB2312-80中定义的内码与在GBK中定义的内码是不同的。

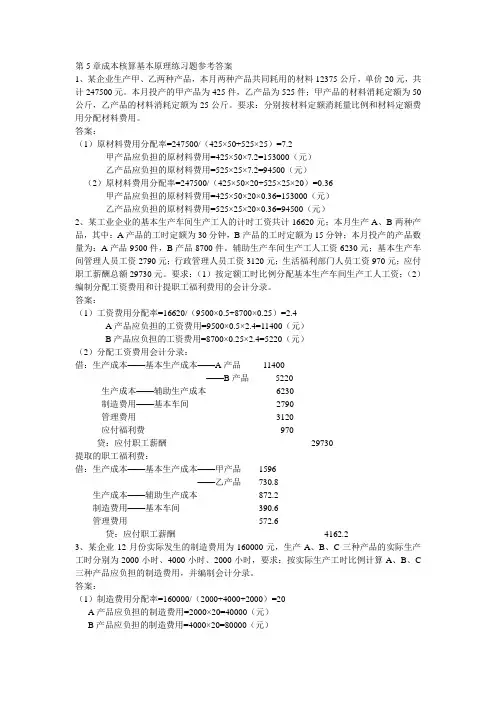

第5章成本核算基本原理练习题参考答案1、某企业生产甲、乙两种产品,本月两种产品共同耗用的材料12375公斤,单价20元,共计247500元。

本月投产的甲产品为425件,乙产品为525件;甲产品的材料消耗定额为50公斤,乙产品的材料消耗定额为25公斤。

要求:分别按材料定额消耗量比例和材料定额费用分配材料费用。

答案:(1)原材料费用分配率=247500/(425×50+525×25)=7.2甲产品应负担的原材料费用=425×50×7.2=153000(元)乙产品应负担的原材料费用=525×25×7.2=94500(元)(2)原材料费用分配率=247500/(425×50×20+525×25×20)=0.36甲产品应负担的原材料费用=425×50×20×0.36=153000(元)乙产品应负担的原材料费用=525×25×20×0.36=94500(元)2、某工业企业的基本生产车间生产工人的计时工资共计16620元;本月生产A、B两种产品,其中:A产品的工时定额为30分钟,B产品的工时定额为15分钟;本月投产的产品数量为:A产品9500件,B产品8700件。

辅助生产车间生产工人工资6230元;基本生产车间管理人员工资2790元;行政管理人员工资3120元;生活福利部门人员工资970元;应付职工薪酬总额29730元。

要求:(1)按定额工时比例分配基本生产车间生产工人工资;(2)编制分配工资费用和计提职工福利费用的会计分录。

答案:(1)工资费用分配率=16620/(9500×0.5+8700×0.25)=2.4A产品应负担的工资费用=9500×0.5×2.4=11400(元)B产品应负担的工资费用=8700×0.25×2.4=5220(元)(2)分配工资费用会计分录:借:生产成本——基本生产成本——A产品11400——B产品5220生产成本——辅助生产成本6230制造费用——基本车间2790管理费用3120应付福利费970贷:应付职工薪酬29730提取的职工福利费:借:生产成本——基本生产成本——甲产品1596——乙产品730.8生产成本——辅助生产成本872.2制造费用——基本车间390.6管理费用572.6贷:应付职工薪酬4162.23、某企业12月份实际发生的制造费用为160000元,生产A、B、C三种产品的实际生产工时分别为2000小时、4000小时、2000小时,要求:按实际生产工时比例计算A、B、C 三种产品应负担的制造费用,并编制会计分录。

第五章习题参考答案3.给定一个单位立方体,一个顶点在(0,0,0),相对的另一个顶点在(1,1,1),过这两个顶点连接一条直线,将单位立方体绕该直线旋转θ角,试导出变换矩阵。

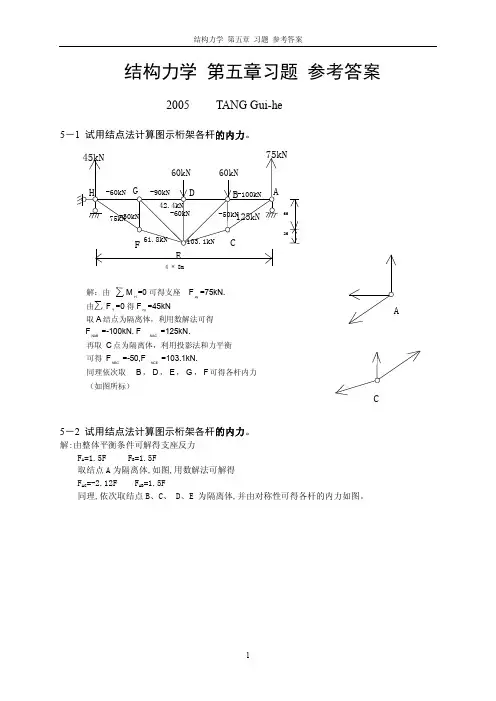

解答:需进行以下复合变换:⑴绕Z轴旋转-45。

角,变换矩阵为:/220 0T1= 2/20 00 1 00 0 1⑵绕Y轴旋转2)角,变换矩阵为:/30 30T2= 0 1 0 030 300 0 0 1⑶绕X轴旋转θ角,变换矩阵为:1 0 0 0T3= 0 cosθs i nθ00 -sinθc o sθ00 0 0 1⑷绕Y轴旋转2)角,变换矩阵为:/30 30T4= 0 1 0 030 300 0 0 1⑸绕Z 轴旋转45。

角,变换矩阵为:/2/20 0 T5= 2/20 0 0 0 1 00 0 0 1 故最后的变换矩阵为: T=T1T2T3T4T5=1/32/3cos θ+ 1/3/3s i n1/3c o s θθ+- 1/3/3s i n 1/3c o s θθ-- 0 1/33sin 1/3cos θθ-- 1/32/3c o s θ+ 1/3/3s i n1/3c o s θθ+- 01/33sin 1/3cos θθ+- 1/3/3s i n1/3c o s θθ-- 1/32/3c o s θ+ 00 0 0 1 6.编程绘制第5题中三棱锥的正等轴测和正二测图。

同上类似,只是变换矩阵改为T 正等=0.70700.40800.70700.4080000.816001-⎡⎤⎢⎥--⎢⎥⎢⎥⎢⎥⎣⎦和T 正二=⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎣⎡---1000943.0000312.00354.00118.00935.07.编程绘制第5题中三棱锥的斜等测和斜二测投影图。

同上类似,变换矩阵改为:T 斜等=⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎣⎡-1001000707.00707.00001T斜二=⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎣⎡-1001000354.00354.000018.编程绘制第5题中三棱锥的立体一点、二点和三点透视图。

第五章习题参考答案与提示第五章数理统计初步习题参考答案与提示1.在总体中随机抽取一长度为36的样本,求样本均值)3.6,52(~2NXX落50.8到53.8之间的概率。

答案与提示:由于)/,(~2nNXσμ,所以{50.853.8}0.8293PX<<=。

2.在总体中随机抽取一长度为100的样本,问样本均值与总体均值的差的绝对值大3的概率是多少?)20,8(~2NX答案与提示:由于2~(,/XNnμσ),所以{83}0.1336PX−>=3.设为来自总体n XXX,,,21)(~λPX的一个样本,X、分别为样本均值和样本方差。

求2SXD及。

2ES答案与提示:此题旨在考察样本均值的期望、方差以及样本方差的期望与总体期望、总体方差的关系,显然应由定理5-1来解决这一问题。

2,DXDXESnnλλ===。

4.设是来自正态总体的随机样本,。

试确定、b使统计量4321XXXX,,,)30(2,N243221)32()2(XXbXXaX−+−=a X服从分布,并指出其自由度。

2χ答案与提示:依题意,要使统计量X服从分布,则必需使及服从标准正态分布。

解得2χ)2(212/1XXa−)32(432/1XXb−a=1/45;b=1/117。

5.设X和Y独立同分布和分别是来自N()032,,921XXX,,,921YYY,,,X和Y 的简单抽样,试确定统计量UXXYY=++++112929 所服从的分布。

答案与提示:应用t分布的定义,得UXXYY=++++191292~()t96.设随机变量~()Xtn(1n> ),试确定统计量21YX=所服从的分布。

答案与提示:先由t分布的定义知nVUX=,再利用F分布的定义即可。

—1—第五章习题参考答案与提示)1,(~12nFXY=。

7.设总体X服从正态分布,而是来自总体)2,0(2N1521,,,XXX X的简单随机样本,试确定随机变量)(221521121021XXXXY++++=所服从的分布。

第五章酸碱平衡课后习题参考答案1解:共轭碱:CN -;H 2AsO 4-;NO 2-;F -;H 2PO 4-;IO 3-;H 4IO 6-;[Al(OH)2(H 2O)4]2+;[Zn(OH)(H 2O)5]+。

2解:共轭酸:HCOOH ;PH 4+;HClO ;HS -;HCO 3-;H 2SO 3;HP 2O 73-;HC 2O 4-;C 2H 4(NH 2)(NH 3+);CH 3(NH 3+)。

3解:酸:H 3AsO 3;H 3PO 3; 碱:SO 32-;Cr 2O 72-;NH 2-NH 2;BrO -; 两性:H 2C 2O 4-;HCO 3-;H 2PO 4-;HS -。

4解:(1)查表得:50℃时的K θw =5.31×10-14; ∴ 7141030.21031.5][--+⨯=⨯==θW K H pH=6.64同理:100℃时的K θw =5.43×10-13; ∴ 7131037.71043.5][--+⨯=⨯==θW K H pH=6.13(2)[H +]=0.20 pH=0.699(3)[OH -]=8.0×10-3 pH=11.90(4)[H +]=0.05×0.1÷1=5×10-3 pH=2.30(5)333102.15.0100.14.01021.0][---+⨯=⨯⨯+⨯⨯=H pH=2.92 (6)[H +]=0.1/2=0.05 pH=1.30(7)5461005.521010][----⨯=+=OH pH=14-4.30=9.70(8)[OH -]=(0.1-0.01)/2=0.045 pH=12.65 8解:(1)酸HClO 2---共轭碱ClO 2-;碱NO 2----共轭酸HNO 2;7.16100.6100.1)()(]][][[]][][[]][[]][[422222222222=⨯⨯====--+-+---HNO K HClO K H NO HClO H ClO HNO NO HClO ClO HNO K a a (2)HPO 42-(酸)—PO 43-(碱);HCO 3-(碱)—H 2CO 3(酸)671332143332434321007.1102.4105.4)()(]][[]][[------⨯=⨯⨯===CO H K PO H K HCO HPO PO CO H K a a (3)NH 4+(酸)—NH 3(碱);CO 32-(碱)—HCO 3-(酸)82.11108.1107.4100.1)()(]][[]][[51114322423433=⨯⨯⨯⨯===---+-+-CO H K NH K CO NH NH HCO K a a (4)HAc(酸)—Ac -(碱);OH -(碱)—H 2O(酸)9145108.110108.1)(]][[][⨯=⨯===----W a K HAc K OH HAc Ac K (5)HAc(酸)—Ac -(碱);NH 3(碱)—NH 4+(酸)414554341024.310108.1108.1)()(]][[]][[⨯=⨯⨯⨯===---++-NH K HAc K HAc NH NH Ac K a a (6)H 2PO 4-(酸)—HPO 42-(碱);PO 43-(碱)—HPO 42-(酸)5138433432344224241038.1105.4102.6)()(]][[]][[⨯=⨯⨯===------PO H K PO H K PO PO H HPO HPO K a a 15解:由缓冲溶液公式得: ∴ C 酸=0.28(mol/L )所需体积为250×0.28÷6=11.7(ml )18解:(1)刚好中和为NH 4Cl 溶液。

40第5章自测题与习题参考答案第5章放大电路中的反馈自测题5.1填空题1.一放大电路的电压放大倍数为40dB,而加入负反馈后变为6dB,它的反馈深度为dB。

2.已知放大电路的输入电压为1mV,输出电压为1V。

当引入电压串联负反馈以后,若要求输出电压维持不变,则输入电压必须增大到10mV,此时的反馈深度为,反馈系数为。

3.在电压串联负反馈放大电路中,已知A u80,负反馈系数F u1%,U o15V,则U id,U f,U i。

4.有一负反馈放大电路的开环放大倍数|A|为100,若|A|变化10%,则闭环放大倍数|A|变化1%,这个放大电路的闭环放大倍数f |A|为,反馈系数F f为。

5.某电压串联负反馈放大电路,开环放大倍数4|A|10,反馈系数u|F|0.001。

u则闭环放大倍数|A|为,若因温度降低,静态点Q下降,使|Au|下降10%,uf此时的闭环放大倍数|A|为。

uf6.欲通过交流负反馈的方法将某放大电路的上限频率由f H0.5MHz提高到不低于5MHz,则引入的反馈深度|1AF|至少为;若要求引入上述反馈后,闭环增益不低于60dB,则基本放大电路的开环放大倍数至少为。

7.已知某直接耦合放大电路的中频放大倍数为100,上限截止频率f H4kHz处的放大倍数为;若给该放大电路引入负反馈后的上限截止频率变为f Hf5kHz,则此放大电路的中频放大倍数变为;引入的反馈系数F为。

8.某电压串联负反馈电路,当中频输入信号U i3mV时,U o150mV。

而在无反馈的情况下,U i3mV时,U o3V,则该负反馈电路的反馈系数为,反馈深度为;若无反馈时的通频带为5kHz,则引入反馈后的通频带变为。

模拟电子技术基础419.在负反馈放大电路中,当环路放大倍数20lg|AF|0dB时,相移oAF245。

由此可知,该电路可能处于状态。

答案:1.34dB。

2.10,0.009。

3.0.1875V,0.15V,0.3375V。

第五章习题参考答案一、名词解释1. 内在稳定器:又称自动稳定器。

是指某些财政制度由于其本身的特点,具有自动调节经济,使经济稳定的机制,其内容包括所得税制度、转移支付制度和农产品价格保护制度。

2. 挤出效应:是指政府支出增加所引起的私人消费或投资的减少,以政府支出代替了私人支出。

3. 法定存款准备金率:中央银行以法律形式规定的商业银行在所吸收的存款中必须保留的准备金的比率,用rd 表示。

4. 基础货币:基础货币包括公众持有的通货与商业银行持有的超额准备金以及商业银行存入中央银行的法定准备金总额。

由于基础货币会派生出货币,因此是一种高能量的或者说活动力强大的货币,又被称为高能货币或强力货币。

5. 公开市场业务:指中央银行通过在金融市场上买卖国债和有价证券,来调节货币供应量的一种政策行为。

6.凯恩斯极端:在LM 曲线呈水平状态时,挤出效应为0。

财政政策效果最大。

7.宏观经济政策;是指国家或政府有意识有计划地运用一定的政策工具,调节控制宏观经济的运行,以达到一定的政策目标。

8.超额准备金:银行实际贷款与其贷款能力的差额即没有贷放出去的款项。

二 选择题DAACC CDDCA1.D .宏观经济政策的目标主要包括充分就业、物价稳定、经济增长和国际收支平衡四大目标。

2.A .经济中存在失业,则说明应当采取扩张性财政政策或货币政策,而扩张性财政政策包括增加政府支出和减少税收等。

3.A. 紧缩性货币政策即在经济繁荣时期, 由于总需求大于总供给,政府可以通过减少政府支出和增加税收来抑制总需求。

4.C .紧缩性货币政策即在经济繁荣时期,由于总需求大于总供给,经济中存在通货膨胀,经济增长速度过快,中央实行提高法定准备金率、提高再贴现率、中央银行实施卖出业务等政策从而达到减少货币供给量、提高利息率、压制消费和投资从而减少总需求、降低通货膨胀的目的。

5.C.因为政府支出乘数、货币需求对产出的敏感程度和投资需求对利率的敏感程度越大,挤出效应越大;只有货币需求对利率的敏感程度与挤出效应具有反向作用。

第五章习题参考答案习题1. 已知柱截面尺寸b ×h =350mm×350mm ,柱的计算长度m 50=l ,轴向力设计值N =1600kN 。

混凝土,纵向受力钢筋为HRB400级,试计算其配筋。

解:由题意知:2c N/mm 9.11=f ,2y y N/mm 360='=f f3.14350/5000/0==b l ,查表得:913.0=ϕ23y c s mm 5.13953603503509.11913.09.01016009.0=⨯⨯-⨯⨯='-='f A f N A ϕ选配纵筋8C 16,实配纵筋面积A s ′=1608mm 2ρ′= %31.13503501608'=⨯=A A s >ρ′min =0.6%, 满足配筋率要求。

按构造要求,选配箍筋A 8@200。

习题2. 现浇圆形截面柱,其计算长度m 3.40=l ,承受设计轴向力N =2100kN ,混凝土采用C20,纵筋采用6根直径为20mm 的HRB335钢筋,螺旋箍筋用HPB300级,若柱截面直径为400mm 时,试求柱螺旋箍筋用量。

解:由题意知,该柱需配螺旋箍筋。

基本参数:2c N/mm 6.9=f ,HRB335,2y y N/mm 300='=f f ,HPB300,2y y N/mm 270='=f f ,75.10400/4300/0==d l ,查表得:945.0=ϕ纵筋6B 20,实际A s ′=1884mm 2一类环境,c =25mm ,混凝土核心截面直径为mm 330102252400cor =⨯-⨯-=d混凝土核心截面面积为222corcor mm 5.85486433014.34=⨯==d A π23ys y cor c ss0mm 56.17542701218843005.854866.99.01021002)(9.0=⨯⨯⨯-⨯-⨯=''+-=f A f A f NA α因A ss0>0.25 A s ′=0.25×1884=471mm 2,满足构造要求。

第5章习题参考答案1.请在括号内填入适当答案。

在CPU中:(1)保存当前正在执行的指令的寄存器是(IR );(2)保存当前正在执行的指令地址的寄存器是(AR )(3)算术逻辑运算结果通常放在(DR )和(通用寄存器)。

2.参见图5.15的数据通路。

画出存数指令“STO Rl,(R2)”的指令周期流程图,其含义是将寄存器Rl的内容传送至(R2)为地址的主存单元中。

标出各微操作信号序列。

解:STO R1, (R2)的指令流程图及为操作信号序列如下:STO R1, (R2)R/W=RDR O, G, IR iR2O, G, AR iR1O, G, DR iR/W=W3.参见图5.15的数据通路,画出取数指令“LAD (R3),R0”的指令周期流程图,其含义是将(R3)为地址主存单元的内容取至寄存器R2中,标出各微操作控制信号序列。

解:LAD R3, (R0)的指令流程图及为操作信号序列如下:PC O , G, AR i R/W=R DR O , G, IR iR 3O , G, AR i DR O , G, R 0iR/W=R LAD (R3), R04.假设主脉冲源频率为10MHz ,要求产生5个等间隔的节拍脉冲,试画出时序产生器的逻辑图。

解:5.如果在一个CPU 周期中要产生3个节拍脉冲;T l =200ns ,T 2=400ns ,T 3=200ns ,试画出时序产生器逻辑图。

解:取节拍脉冲T l 、T 2、T 3的宽度为时钟周期或者是时钟周期的倍数即可。

所以取时钟源提供的时钟周期为200ns ,即,其频率为5MHz.;由于要输出3个节拍脉冲信号,而T 3的宽度为2个时钟周期,也就是一个节拍电位的时间是4个时钟周期,所以除了C 4外,还需要3个触发器——C l 、C 2、C 3;并令211C C T *=;321C C T *=;313C C T =,由此可画出逻辑电路图如下:6.假设某机器有80条指令,平均每条指令由4条微指令组成,其中有一条取指微指令是所有指令公用的。

已知微指令长度为32位,请估算控制存储器容量。

解:80条指令,平均每条指令由4条微指令组成,其中有一条公用微指令,所以总微指令条数为80 (4-1)+1=241条微指令,每条微指令32位,所以控存容量为:24132位7.某ALU器件是用模式控制码M S3 S2 S1 C来控制执行不同的算术运算和逻辑操作。

下表列出各条指令所要求的模式控制码,其中y为二进制变量,φ为0或l任选。

试以指令码(A,B,H,D,E,F,G)为输入变量,写出控制参数M,S3,S2,S l,C的逻辑表达式。

1yy解:由表可列如下逻辑方程M=GS3=H+D+FS2=A+B+D+H+E+F+GS1=A+B+F+GC=H+D+Ey+Fy8.某机有8条微指令I1—I8,每条微指令所包含的微命令控制信号如下表所示。

a—j分别对应10种不同性质的微命令信号。

假设一条微指令的控制字段仅限为8位,请安排微指令的控制字段格式。

解:因为有10种不同性质的微命令信号,如果采用直接表示法则需要10位控制字段,现控制字段仅限于8位,那么,为了压缩控制字段的长度,必须设法把一个微指令周期中的互斥性微命令组合在一个小组中,进行分组译码。

经分析,(e,f,h)和(b,i,j)、或(d,i,j)和(e,f,h)、或(g,b,j)和(i,f,h)均是不可能同时出现的互斥信号,所以可将其通过2:4译码后输出三个微命令信号(00表示该组所有的微命令均无效),而其余四个微命令信号用直接表示方式。

因此可用下面的格式安排控制字段。

e f h b i j或:e f h d i j或:f h i bg j9.微地址转移逻辑表达式如下: μA 8 = P 1·IR 6·T 4 μA 7 = P 1·IR 5·T 4 μA 6 = P 2·C ·T 4其中μA 8—μA 6为微地址寄存器相应位,P 1和P 2为判别标志,C 为进位标志,IR 5和IR 6为指令寄存器的相应位,T 4为时钟周期信号。

说明上述逻辑表达式的含义,画出微地址转移逻辑图。

解:μA 8 = P 1·IR 6·T 4 表示微地址的第8位在P 1有效时,用IR 6设置 μA 7 = P 1·IR 5·T 4 表示微地址的第7位在P 1有效时,用IR 5设置 μA 6 = P 2·C ·T 4 表示微地址的第6位在P 2有效时,用进位标志C 设置, 地址转移逻辑图如下:QQSETCLRDQQSETCLRDQQSETCLRDT 2μAR 8μAR 7μAR 6T 4P 1IR 5IR 6CP 287610.某计算机有如下部件,ALU ,移位器,主存M ,主存数据寄存器MDR ,主存地址寄存器MAR ,指令寄存器IR ,通用寄存器R 0R 3,暂存器C 和D 。

(1)请将各逻辑部件组成一个数据通路,并标明数据流动方向。

(2)画出“ADD R1,R2”指令的指令周期流程图。

解:(1) 设该系统为单总线结构,暂存器C 和D 用于ALU 的输入端数据暂存,移位器作为ALU 输出端的缓冲器,可对ALU 的运算结果进行附加操作,则数据通路可设计如下:IRPCMDRMARMR 0 R 1 R 2 R 3D移位器CALU+(2) 根据上面的数据通路,可画出“ADD R1,R2”(设R1为目的寄存器)的指令周期流程图如下:ADD R1, R211.已知某机采用微程序控制方式,控存容量为512*48位。

微程序可在整个控存中实现转移,控制微程序转移的条件共4个,微指令采用水平型格式,后继微指令地址采用断定方式。

请问;(1)微指令的三个字段分别应为多少位?(2)画出对应这种微指令格式的微程序控制器逻辑框图。

解:(1) 因为容量为512*48位,所以下址字段需用9位,控制微程序转移的条件有4个,所以判别测试字段需4位或(3位译码),因此操作控制字段的位数48-9-4=35位(或48-9-3=36位)(2)微程序控制器逻辑框图参见教材P.147图5.2312.今有4级流水线,分别完成取指、指令译码并取数、运算、送结果四步操作。

今假设完成各步操作的时间依次为100ns,100ns,80ns,50ns。

请问;(1)流水线的操作周期应设计为多少?(2)若相邻两条指令发生数据相关,而且在硬件上不采取措施,那么第2条指令要推迟多少时间进行?(3)如果在硬件设计上加以改进,至少需推迟多少时间?答:(1) 流水操作周期为max(100,100,80,50)=100ns(2)若相邻两条指令发生数据相关,而且在硬件上不采取措施,那么在第1条指令“送结果”步骤完成后,第2条指令的“取数”步骤才能开始,也就是说,第2条指令要推迟两个操作周期,即200ns才能进行。

(3) 如果在硬件设计上加以改进,采用定向传送的技术,则只要第1条指令完成“运算”的步骤,第2条指令就可以“取数”了,因此至少需推迟100ns 。

13.指令流水线有取指(IF)、译码(ID)、执行(EX)、访存(MEM)、写回寄存器堆(WB)五个过程段,共有20条指令连续输入此流水线。

(1)画出流水处理的时空图,假设时钟周期为100ns 。

(2)求流水线的实际吞吐率(单位时间里执行完毕的指令数)。

(3)求流水线的加速比。

解:(1) 流水处理的空图如下,其中每个流水操作周期为100ns :空间I 1 I 2 I 15 I 16 I 17 I 18 I 19 I 20 I 1 I 2 I 15 I 16 I 17 I 18 I 19 I 20 I 1 I 2 I 3 I 16 I 17 I 18 I 19 I 20 I 1 I 2 I 3 I 4 I 17 I 18 I 19 I 20 I 1 I 2 I 3 I 4 I 5 I 18 I 19 I 20 I 1 I 2 I 3 I 4 I 5 I 6 I 19 I 20123456192021222324时间T(2) 流水线的实际吞吐量:执行20条指令共用5+119=24个流水周期,共2400ns ,所以实际吞吐率为:秒百万条指令/333.8102400209≈⨯-(3) 流水线的加速比为 : 设流水线操作周期为τ,则n 指令串行经过k 个过程段的时间为n*k*τ ;而n 条指令经过可并行的k 段流水线时所需的时间为(k+n-1)*τ;故20条指令经过5个过程段的加速比为: ()17.4195520≈⨯+⨯⨯ττ14.用时空图法证明流水计算机比非流水计算机具有更高的吞吐率。

解:设流水计算机的指令流水线分为4个过程段:IF 、ID 、EX 、WB ,则流水计算机的时空图如下:空间T非流水计算机的时空图:空间I 2时间T由图中可以看出,同样的8个操作周期内,流水计算机执行完了5条指令,而非流水计算机只执行完了2条指令;由此,可看出流水计算机比非流水计算机具有更高的吞吐率。

15.用定量描述法证明流水计算机比非流水计算机具有更高的吞吐率。

证明:设流水计算机具有k 级流水线,每个操作周期的时间为,执行n 条指令的时间为:()τ⨯-+=1n k T ; 吞吐率为:()τ⨯-+=11n k nH而非流水计算机,执行n 条指令的时间为:τ⨯⨯=k n T ; 吞吐率为:τ⨯⨯=k n nH 2()1121-+⨯=⨯-+⨯⨯=n k kn n k k n H H ττ 当n=1时,21H H =;当n>1时,21H H >,即:流水计算机具有更高的吞吐率。

16.判断以下三组指令中各存在哪种类型的数据相关?(1) I 1 LAD R1,A ; M(A)→R1,M(A)是存储器单元 I 2 ADD R2,Rl ; (R2)+(R1)→R2 (2) I 1 ADD R3,R4 ; (R3)+(R4)→R3 I 2 MUL R4,R5 ; (R4)(R5)→R4(3) I 1 LAD R6,B ; M(B)→R6,M(B)是存储器单元I 2 MUL R6,R7 ; (R6) (R7)→R6 解:(1) I 1的运算结果应该先写入R 1,然后再在I 2中读取R 1的内容作为操作数,所以是发生RAW (“写后读”)相关(2) WAR(3) RAW和WAW两种相关17.参考图5.39所示的超标量流水线结构模型,现有如下6条指令序列:I1LAD R1,B ;M(B)→R1,M(B)是存储器单元I2SUB R2,Rl ;(R2)-(R1)→R2I3MUL R3,R4 ;(R3)*(R4)→R3I4ADD R4,R5 ;(R4)+(R5)→R4I5LAD R6,A ;M(A)→R6,M(A)是存储器单元I6ADD R6,R7 ;(R6)+(R7)→R6请画出:(1)按序发射按序完成各段推进情况图。