西北工业大学2007-2008学年第二学期数字逻辑考试试题及答案—A卷

- 格式:doc

- 大小:1.94 MB

- 文档页数:9

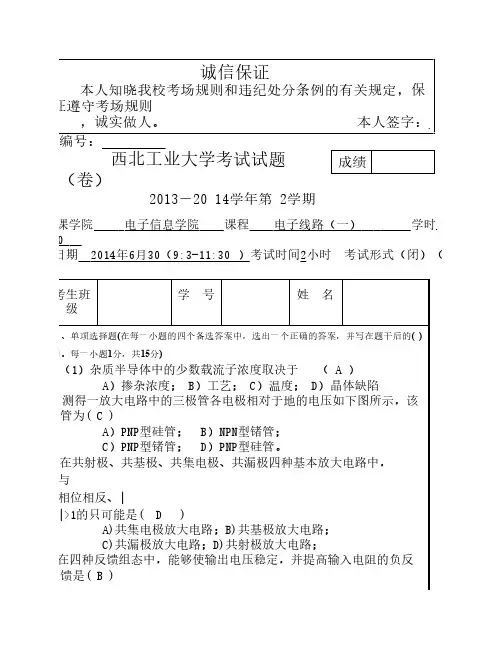

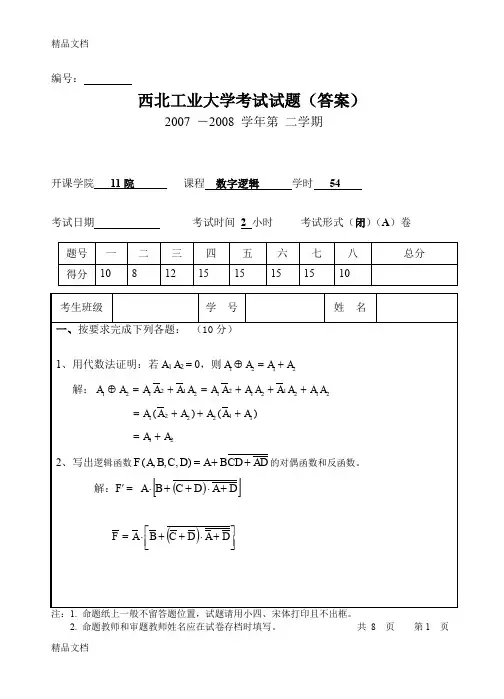

《数字逻辑》期末考试A卷参考答案《数字逻辑》期末考试A卷参考答案一、判断题:下面描述正确的打‘√’,错误的打‘×’(每小题1分,共10分)1、为了表示104个信息,需7位二进制编码[√]2、BCD码能表示0至15之间的任意整数[×]3、余3码是有权码[×]4、2421码是无权码[×]5、二值数字逻辑中变量只能取值0和1,且表示数的大小[×]6、计算机主机与鼠标是并行通信[×]7、计算机主机与键盘是串行通信[√]8、占空比等于脉冲宽度除于周期[√]9、上升时间和下降时间越长,器件速度越慢[√]10、卡诺图可用来化简任意个变量的逻辑表达式[×]二、写出图中电路的逻辑函数表达式。

(每小题5分,共10分)1、F=A B四、填空题(每空1分,共20分)1、一个触发器可表示__1__位二进制码,三个触发器串接起来,可表示__3__ 位二进制数。

2、欲表示十进制的十个数码,需要__4__个触发器。

3、寄存器中,与触发器相配合的控制电路通常由_门电路_(选择提示:门电路、触发器、晶体二极管)构成。

4、一个五位的二进制加法计数器,由00000状态开始,问经过75个输入脉冲后,此计数器的状态为__01011_。

5、四位移位寄存器可以寄存四位数码,若将这些数码全部从串行输出端输出,需经过__3__个时钟周期。

6、_RS_触发器存在输入约束条件,_主从JK_触发器会出现一次翻转现象。

7、负跳沿触发翻转的主从JK触发器的输入信号应该在CP为_低电平_时加入,在CP为_高电平_时输入信号要求稳定不变。

8、正跳沿触发翻转的D触发器的输入信号在CP _上升沿_前一瞬间加入。

9、由与非门组成的基本RS触发器当输入R=0,S=0时,同向输出端Q=__1__,反向输出端Q=__1__,当_R、S同时由0变1_时,输出不定状态。

10、T触发器是由_JK_触发器的数据输入端短接而成。

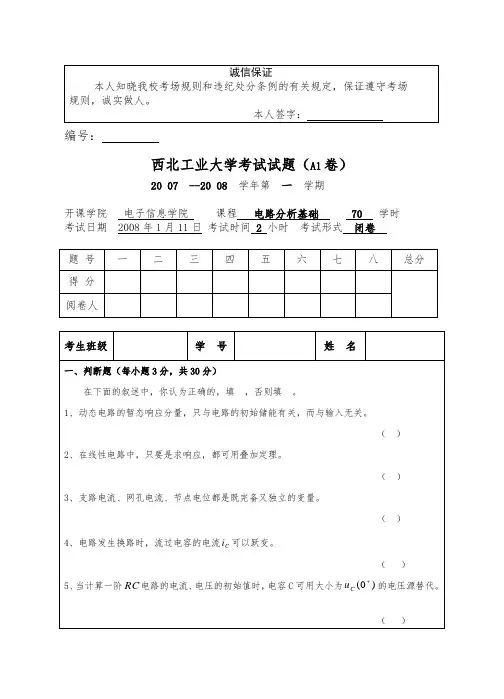

编号:

西北工业大学考试试题(A1卷)

20 07 --20 08 学年第 一 学期

开课学院 电子信息学院 课程 电路分析基础 70 学时 考试日期 2008年1月11日 考试时间 2 小时 考试形式 闭卷

一、判断题(每小题3分,共30分)

在下面的叙述中,你认为正确的,填,否则填。

1、动态电路的暂态响应分量,只与电路的初始储能有关,而与输入无关。

( )

2、在线性电路中,只要是求响应,都可用叠加定理。

( )

3、支路电流、网孔电流、节点电位都是既完备又独立的变量。

( )

4、电路发生换路时,流过电容的电流C i 可以跃变。

( )

5、当计算一阶RC 电路的电流、电压的初始值时,电容C 可用大小为)0(

C u 的电压源替代。

( )

八、(10分)图7所示电路,求H 参数矩阵,并说明二端口网络的互易性。

+

-

+

-Ω1Ω

1Ω

12

U 2

2U

图 7

07-08电路A1(70)卷参考答案

一、每小题3分,共30分

1、 2、√ 3、 4、√ 5、√ 6、√ 7、 8、√ 9、 10、√

二、10分

A i 3=; V u s 3=

三、10分

A i 6:36V ='; A i A 1:3=''; A i 7=; W P 144=

四、10分

2.0=n ; W P m 5.2=

五、10分

V U S

0200∠=

六、10分。

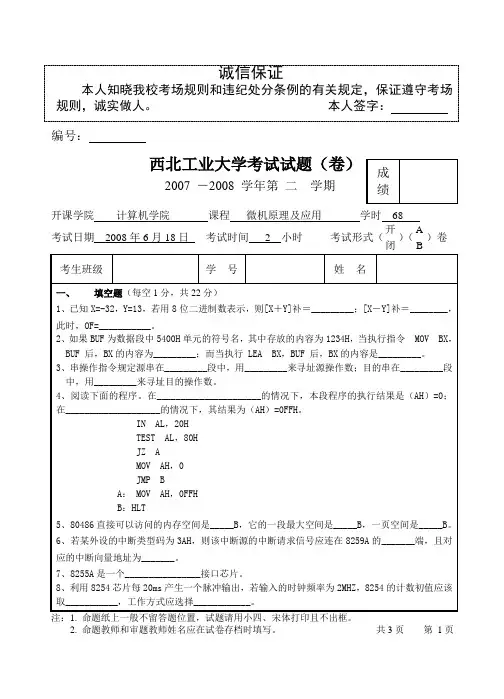

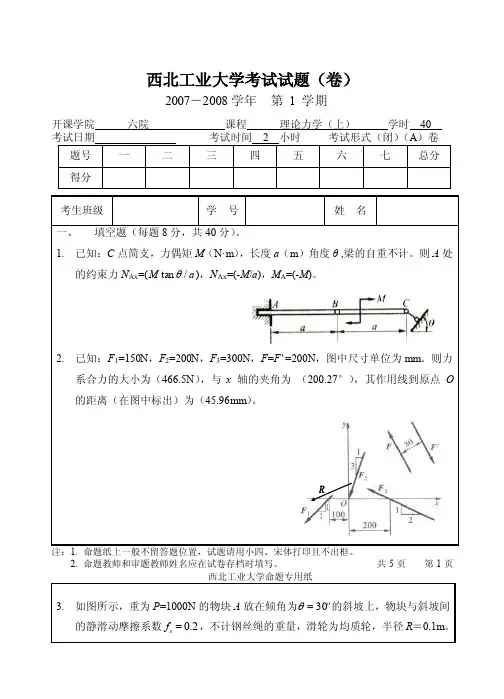

西北工业大学考试试题(卷)2007-2008学年第1 学期开课学院六院课程理论力学(上)学时40R2. 命题教师和审题教师姓名应在试卷存档时填写。

共5页第1页a CP N BN AyN AxP西北工业大学命题专用纸西北工业大学命题专用纸x’y’图中v E 为滑块E 的绝对速度,v ED 为E 相对于D 的相对速度,由速度合成定理 v E =v D +v ED 得,23243cos /vv v v D E =⨯==β,4212sin v v v v E ED =⨯=⋅=β可以得到D 点的法向加速度a Dn 和切向加速度a Dt 的方向和大小以及E 相对于D 的法向相对加速度a EDn 的方向和大小,各加速度的方向见图所示。

b v b b v b OD a OCOCDn 16333169sin 222222=⨯=⋅=⋅=γωω bv b b v b OD a OC OC D 833833sin 2222=⨯=⋅=⋅=γαατbv b v b vDE va EDEDEDn 16116sin 2//2222=⨯===β 假设E 相对于D 的法向相对加速度a EDt 的方向以及E 的绝对加速度a E 方向如图所示。

由加速速度合成定理 a E =a Dn +a Dt +a EDn +a EDt由于E 水平运动,所以在垂直方向上的加速度分量等于零ββττcos )(sin )(⋅-=⋅+ED D n D ED n a a a a解得 bv a E D t 2432=所以, bv a a a a a ED DnD EDnE 2437sin )(cos )(2=⋅-+⋅+=ββττ。

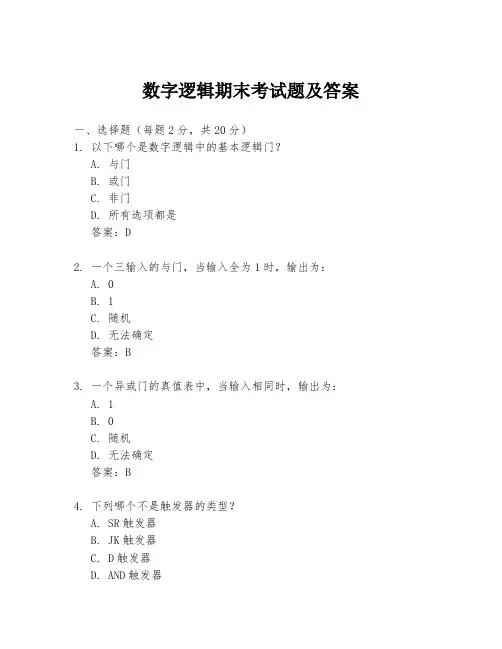

数字逻辑期末考试题及答案一、选择题(每题2分,共20分)1. 以下哪个是数字逻辑中的基本逻辑门?A. 与门B. 或门C. 非门D. 所有选项都是答案:D2. 一个三输入的与门,当输入全为1时,输出为:A. 0B. 1C. 随机D. 无法确定答案:B3. 一个异或门的真值表中,当输入相同时,输出为:A. 1B. 0C. 随机D. 无法确定答案:B4. 下列哪个不是触发器的类型?A. SR触发器B. JK触发器C. D触发器D. AND触发器答案:D5. 在数字电路中,同步计数器和异步计数器的主要区别在于:A. 计数范围B. 计数速度C. 计数精度D. 计数方式答案:B6. 一个4位二进制计数器,其最大计数值为:A. 15B. 16C. 32D. 64答案:A7. 以下哪个不是数字逻辑设计中常用的简化方法?A. 布尔代数简化B. 卡诺图简化C. 逻辑门替换D. 逻辑表简化答案:C8. 在数字电路中,一个信号的上升沿指的是:A. 信号从0变为1的瞬间B. 信号从1变为0的瞬间C. 信号保持不变D. 信号在变化答案:A9. 一个D触发器的Q输出端在时钟信号上升沿时:A. 保持不变B. 翻转状态C. 跟随D输入端D. 随机变化答案:C10. 以下哪个不是数字逻辑中的状态机?A. Moore机B. Mealy机C. 有限状态机D. 无限状态机答案:D二、填空题(每空2分,共20分)11. 在布尔代数中,逻辑与操作用符号______表示。

答案:∧12. 一个布尔函数F(A,B,C)=A∨B∧C的最小项为______。

答案:(1,1,1)13. 在数字电路设计中,卡诺图是一种用于______的工具。

答案:布尔函数简化14. 一个4位二进制加法器的输出端最多有______位。

答案:515. 一个同步计数器在计数时,所有的触发器都______时钟信号。

答案:接收16. 一个JK触发器在J=K=1时,其状态会发生______。

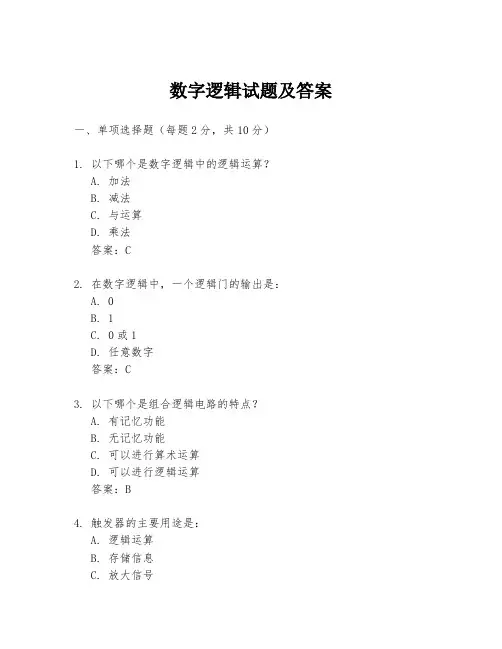

数字逻辑试题及答案一、单项选择题(每题2分,共10分)1. 以下哪个是数字逻辑中的逻辑运算?A. 加法B. 减法C. 与运算D. 乘法答案:C2. 在数字逻辑中,一个逻辑门的输出是:A. 0B. 1C. 0或1D. 任意数字答案:C3. 以下哪个是组合逻辑电路的特点?A. 有记忆功能B. 无记忆功能C. 可以进行算术运算D. 可以进行逻辑运算答案:B4. 触发器的主要用途是:A. 逻辑运算B. 存储信息C. 放大信号D. 转换信号答案:B5. 一个4位二进制计数器可以计数到:A. 8B. 16C. 32D. 64答案:B二、多项选择题(每题3分,共15分)1. 下列哪些是数字逻辑中常用的逻辑门?A. 与门B. 或门C. 非门D. 异或门E. 与非门答案:ABCDE2. 在数字逻辑中,以下哪些可以作为信号的表示?A. 电压B. 电流C. 电阻D. 电容E. 电感答案:AB3. 以下哪些是数字电路的基本组成元素?A. 逻辑门B. 电阻C. 电容D. 触发器E. 运算放大器答案:ABD4. 在数字逻辑中,以下哪些是常见的电路类型?A. 组合逻辑电路B. 时序逻辑电路C. 模拟电路D. 混合信号电路E. 微处理器答案:ABD5. 以下哪些是数字电路设计时需要考虑的因素?A. 电路的复杂性B. 电路的功耗C. 电路的可靠性D. 电路的成本E. 电路的尺寸答案:ABCDE三、填空题(每题2分,共10分)1. 在数字逻辑中,一个逻辑门的输出状态取决于其_________。

答案:输入状态2. 一个D触发器的输出在时钟信号的_________沿触发。

答案:上升沿3. 一个4位二进制计数器的计数范围是从_________到_________。

答案:0000到11114. 一个逻辑电路的输出是其输入的_________。

答案:逻辑函数5. 在数字逻辑中,使用_________可以表示一个逻辑函数的真值表。

答案:卡诺图四、简答题(每题5分,共15分)1. 描述一个典型的组合逻辑电路的工作原理。

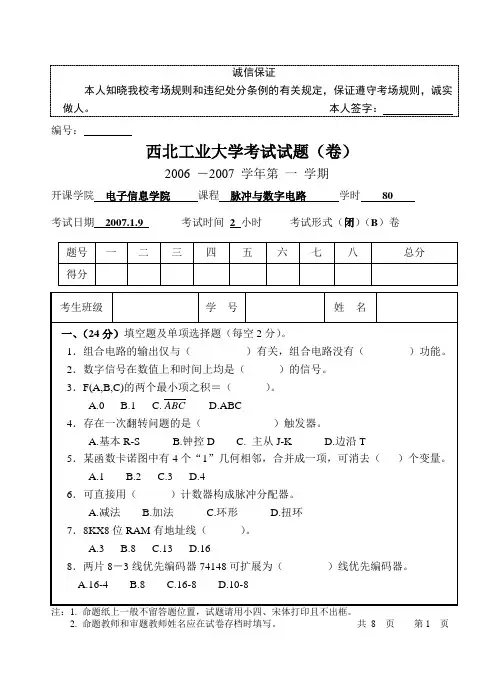

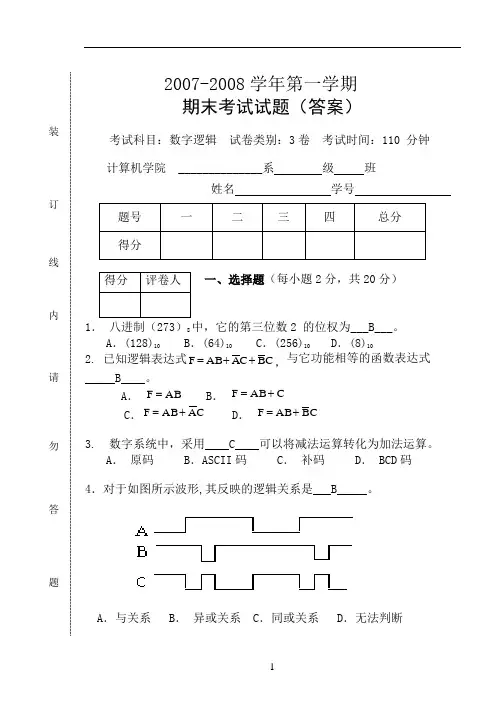

2007-2008学年第一学期期末考试试题(答案)考试科目:数字逻辑 试卷类别:3卷 考试时间:110 分钟 计算机学院 ______________系 级 班姓名 学号题号 一 二 三 四 总分 得分一、选择题(每小题2分,共20分)1. 八进制(273)8中,它的第三位数2 的位权为___B___。

A .(128)10B .(64)10C .(256)10D .(8)102. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。

A .AB F = B .C AB F += C .C A AB F +=D . C B AB F +=3. 数字系统中,采用____C____可以将减法运算转化为加法运算。

A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断得分 评卷人装订线 内请勿答题5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误6. 与逻辑函数D C B A F +++= 功能相等的表达式为___C_____。

A . D CB A F +++=B . DC B A F +++= C .D C B A F = D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。

8. 如图所示电路,若输入CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。

A . 500KHzB .200KHzC . 100KHzD .50KHz9.下列器件中,属于时序部件的是_____A_____。

A.计数器 B.译码器 C.加法器 D.多路选择器10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。

数字逻辑期末考试试卷含答案一、选择题(共10题,每题2分,共20分)在下列选项中选择正确答案,并在答题卡上填写对应答案的字母。

1. 逻辑门是数字电路中最基本的组成单元,它由多个电子器件组合而成,能够实现逻辑运算。

下列不属于逻辑门的是:A. 与门B. 或门C. 非门D. 电容门2. 在数字电路中,最简单的存储单元是:A. 寄存器B. 计数器C. 缓存器D. 锁存器3. 二进制数是由二个字符0和1组成的数,它在计算机中占有重要地位。

下面哪个是5的十进制表示?A. 101B. 0101C. 110D. 00001014. 半加器是指具有两个输入端和两个输出端的二进制加法器。

下列选项中,不属于半加器的是:A. 异或门B. 与门C. 或门D. 非门5. 在数字电路中,集成电路是指将多个电子器件集成到一个芯片上,以实现特定功能。

下列选项中不属于集成电路的是:A. 与门B. 或门C. 霍尔开关D. 计数器6. 在计算机中,ALU指的是运算器,负责进行各种算术和逻辑运算。

下面哪个选项不属于ALU的功能?A. 加法运算B. 乘法运算C. 与门逻辑运算D. 异或门逻辑运算7. 时钟信号是数字电路中常见的同步信号,用于控制电路的工作时间。

下列选项中,不属于时钟信号的是:A. 脉冲信号B. 方波信号C. 高电平信号D. 低电平信号8. 译码器是指将输入的数字代码转换为特定信号输出,用于对输入数字进行解码。

下面哪个选项不属于译码器?A. 74LS138B. 74LS74C. 74LS47D. 74LS869. 在数字电路中,多路选择器是一种常用的逻辑电路,具有多个输入和一个输出。

下列选项中不属于多路选择器的是:A. 2:1选择器B. 4:1选择器C. 8:1选择器D. 16:1选择器10. D触发器是一种常用的时序元件,能够存储一个比特的数据。

下列选项中,不属于D触发器的是:A. RS触发器B. JK触发器C. T触发器D. D触发器与门二、填空题(共5题,每题4分,共20分)根据题目所给条件,在答题卡上填写正确的答案。

西北工业大学航空学院德语(一外)2007理论力学1997,2000,2002——2004,2007腐蚀防护2007自动控制原理1995——1996,2000——2007(2001——2006有答案)信号与系统2002——2007(注:2006年试卷共4页,缺第1页)材料科学基础2003——2010(2010为回忆版)(2005——2009有答案)飞机总体设计原理2003——2004,2007材料力学2003——2004,2007数字电子技术2003,2007数字电路2004空气动力学2003——2004,2007空中交通管理基础2003——2004,2007结构有限元分析基础2007流体力学2003——2004,2007机械振动基础2007自动化检测技术2007航天学院日语(一外)2007德语(一外)2007自动控制原理1995——1996,2000——2007(2001——2006有答案)航天器与导弹控制原理2007飞行器飞行力学2007气体动力学2007飞行器结构力学2007火箭发动机原理2007数字电子技术2003,2007数字电路2004材料力学2003——2004,2007航海学院水声学原理2003——2004,2007噪声与振动控制2007理论力学1997,2000,2002——2004,2007流体力学2003——2004,2007自动控制原理1995——1996,2000——2007(2001——2006有答案)模拟电子技术2003——2004,2007数字信号处理2002——2004,2007通信原理2001——2004,2007(2002有答案)微弱信号检测技术2007信号检测与估计2003——2004,2007动力装置原理2007微机原理及应用2000——2004,2007(2000——2003有答案)[说明:2003年试卷名称为“微型计算机原理”]信号与系统2002——2007(注:2006年试卷共4页,缺第1页)塑性成形原理2003——2004材料学院材料科学基础2003——2010(2010为回忆版)(2005——2009有答案)陶瓷工艺原理2007材料力学2003——2004,2007塑性成形原理2003——2004机电学院设计理论2007工业设计2007电工技术与电子技术2007工业设计基础2003——2004电子技术基础1996——1997,2004,2007设施规划与设计2007汽车理论基础2007数控机床2007机械设计2003——2004,2007机械原理1996,2001,2003——2004微机原理及应用2000——2004,2007(2000——2003有答案)[说明:2003年试卷名称为“微型计算机原理”]电路1998——1999电路基础2001——2004,2007数字电子技术2003,2007数字电路2004电力电子技术2003——2004,2007机械加工工艺学2003——2004,2007计算机辅助管理2002——2004,2007计算机辅助制造2003——2004,2007C语言2003C语言程序设计2004塑性成形原理2003——2004力学与土木建筑学院建筑历史2007建筑设计原理2007道面工程2007理论力学1997,2000,2002——2004,2007材料力学2003——2004,2007结构力学(土建)2003——2004,2007钢筋混凝土结构2007道面工程2007动力与能源学院德语(一外)2007自动控制原理1995——1996,2000——2007(2001——2006有答案)传热学2003——2004,2007工程流体力学2003——2004,2007工程热力学2002——2004,2007叶轮机械原理2007信号与系统2002——2007(注:2006年试卷共4页,缺第1页)电子技术基础1996——1997,2004,2007电工技术与电子技术2007数字电子技术2003,2007数字电路2004模拟电子技术2003——2004,2007电子信息学院电路1998——1999电路基础2001——2004,2007模拟电子技术2003——2004,2007信号与系统2002——2007(注:2006年试卷共4页,缺第1页)通信原理2001——2004,2007(2002有答案)数字电子技术2003,2007数字电路2004自动控制原理1995——1996,2000——2007(2001——2006有答案)数字信号处理2002——2004,2007电磁场与电磁波2002——2004,2007武器运筹学2007航空火力控制原理2007随机信号分析2003——2004教育学专业基础综合(全国统考试卷)2007——2008自动化学院德语(一外)2007自动控制原理1995——1996,2000——2007(2001——2006有答案)电路1998——1999电路基础2001——2004,2007计算机网络2007概率论2004,2007概率论与数理统计2003系统工程概论2007交通工程导论2007惯性导航原理2007传感器原理2007电机学2007电力电子技术2003——2004,2007电子技术基础1996——1997,2004,2007机电控制元件与系统2007微机原理及应用2000——2004,2007(2000——2003有答案)[说明:2003年试卷名称为“微型计算机原理”]C语言2003C语言程序设计2004医学图像处理2007计算机学院计算机专业基础2004,2007计算机组成与系统结构2001——2003计算方法2003——2004计算机综合技术2004编译原理2000——2002操作系统1999——2002数据结构1998——1999,2002软件综合技术2004离散数学2000——2002理学院高等代数2007数学分析2002,2007数学分析与高等代数2003——2004量子力学2002——2004,2007电动力学2007光学2003——2004,2007有机化学2004,2007数学(理学)2007普通物理2007数字电子技术2003,2007数字电路2004物理化学(凝聚态物理、材料物理与化学、材料学、材料加工工程、应用化学专业)2007物理化学(物理化学、药剂学专业)2007高分子化学2007高分子物理2007环境化学2007管理学院运筹学2003——2007(2005有答案)(注:2005年试卷共6页,缺第6页;2005年答案共6页,缺第6页)管理经济学2003——2004,2007管理学2002——2004,2007计算机辅助管理2002——2004,2007计算机辅助制造2003——2004,2007人文与经法学院俄语(一外)2007日语(一外)2007法语(一外) 2007英语水平测试2002——2004,2007英语写作知识与技能2002英语语言学测试2003英语语言学基础2002英语综合知识测试2004,2007英语(一外)2007德语水平考试(含语法、词汇、阅读、翻译及写作)2007综合知识考试(含德国国情, 语言学与德语文学基础知识)2007 法学综合2007马克思主义发展史2007政治学原理2007,2010(2010为回忆版)中国近现代史2007中国特色社会主义理论与实践2007经济法2007教育学专业基础综合(全国统考试卷)2007——2008现代西方经济学2007艺术史2007艺术专业综合理论2007行政管理学2007,2010(2010为回忆版)软件学院计算机组成与系统结构2001——2003计算方法2003——2004计算机专业基础2004,2007计算机综合技术(含操作系统、计算机组成原理)2004,2007 编译原理2000——2002操作系统1999——2002数据结构1998——1999,2002软件综合技术(含数据结构、C++程序设计)2004,2007离散数学2000——2002生命科学院生物综合2007分子生物学2007生物医学工程综合2007有机化学2004,2007物理化学(凝聚态物理、材料物理与化学、材料学、材料加工工程、应用化学专业)2007物理化学(物理化学、药剂学专业)2007。