LVDS接口设计

- 格式:doc

- 大小:52.50 KB

- 文档页数:3

LVDS原理及设计指南LVDS全称为低压差分信号(Low Voltage Differential Signaling),是一种高速串行接口技术,广泛应用于电子设备中进行高速数据传输。

LVDS主要通过两对差分信号进行数据传输,其中一对信号传输高电平信号,另一对信号传输低电平信号,通过差分运算来提高抗干扰能力和抗噪声能力,以实现高质量的数据传输。

LVDS的工作原理如下:1.发送端:将输入信号通过电流驱动压缩成低压差分信号,并通过双绞线传输给接收端。

2.传输线路:使用双绞线进行数据传输,利用差分运算来抵消传输线上的共模噪声和反射噪声。

3.接收端:对接收到的低压差分信号进行解码,还原成原始的输入信号。

设计LVDS接口时需要注意以下几点:1.信号线路的设计:为了保证信号的完整性和稳定性,需要控制信号线的阻抗匹配,减小信号线的长度和延迟,并避免信号线与高频噪声信号线的交叉和平行布线。

2.布线和PCB设计:保持信号线的长度均匀,并尽量使用同一层或相邻层进行差分信号线布线,以减小信号线之间的不平衡和串扰。

3.电源和接地:为了提供噪声的抑制和信号的稳定性,需要使用低噪声电源和低阻抗接地。

4.EMI抑制:由于LVDS接口传输速率高,会引起较大的电磁辐射干扰,因此需要在设计中加入适当的EMI抑制措施,如电磁屏蔽、地线设计和滤波器等。

5.信号匹配:为了保证所发送信号的完整性和稳定性,需要将发送端与接收端之间的差分阻抗匹配,以最大限度地减小信号反射和串扰。

总之,LVDS是一种高速串行接口技术,通过差分运算进行数据传输,具有抗噪声和抗干扰能力强的特点。

在设计LVDS接口时需注意信号线路的设计、布线和PCB设计、电源和接地、EMI抑制以及信号匹配等方面,以保证高质量的数据传输。

完整版)LVDS接口详解LVDS输出接口是一种数字视频信号传输方式,它利用低压差分信号技术接口,在两条PCB走线或一对平衡电缆上通过差分进行数据的传输。

相比于TTL接口,LVDS输出接口具有高速率、低噪声、远距离、高准确度等优点,因此在17in及以上液晶显示器中得到了广泛的应用。

LVDS接口电路由驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)组成。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过柔性电缆传送到液晶面板侧的LVDS接收器。

LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

在数据传输过程中,LVDS接口采用差分信号对的形式进行传输,每个数据传输通道或时钟传输通道的输出都为两个信号(正输出端和负输出端)。

这种方式不仅可以提高数据传输速率,还可以减少电磁干扰和功耗,使得LVDS输出接口更加稳定可靠。

不同种类的液晶显示器的驱动板上的LVDS发送器并不相同。

有些LVDS发送器是一片或两片独立的芯片,例如DS90C383;而有些则是集成在主控芯片中,例如主控芯片gm5221内部集成了LVDS发送器。

LVDS输出接口也分为四种类型,其中第一种是单路6位LVDS输出接口。

这种接口电路采用单路方式传输,每个基色信号(即RGB三色中的其中任何一种颜色)采用6位数据(XOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-),共18位RGB(6bit X 3(RGB3色))数据,因此也被称为18位或18bit LVDS接口。

第二种是双路6位LVDS输出接口。

在这种接口电路中,两个基色信号(例如红色和绿色)共用一条传输线,而蓝色信号则使用另一条传输线,每个基色信号采用6位数据,因此也被称为双路18位或18bit LVDS接口。

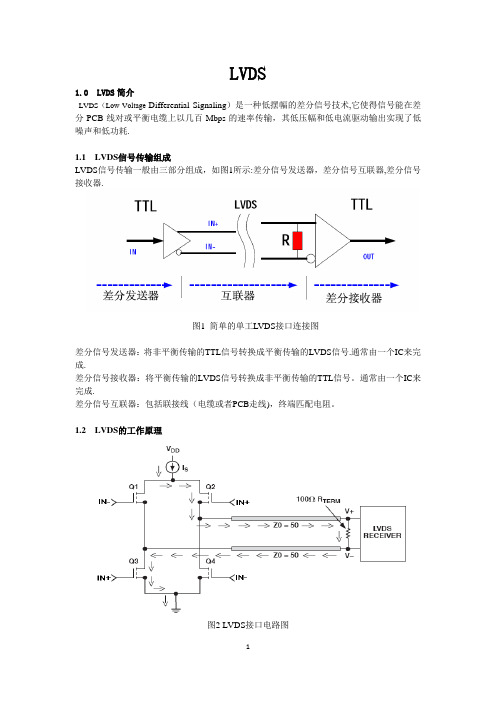

LVDS1.0 LVDS简介LVDS(Low Voltage Differential Signaling)是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗.1.1 LVDS信号传输组成LVDS信号传输一般由三部分组成,如图1所示:差分信号发送器,差分信号互联器,差分信号接收器.图1 简单的单工LVDS接口连接图差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号.通常由一个IC来完成.差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成.差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

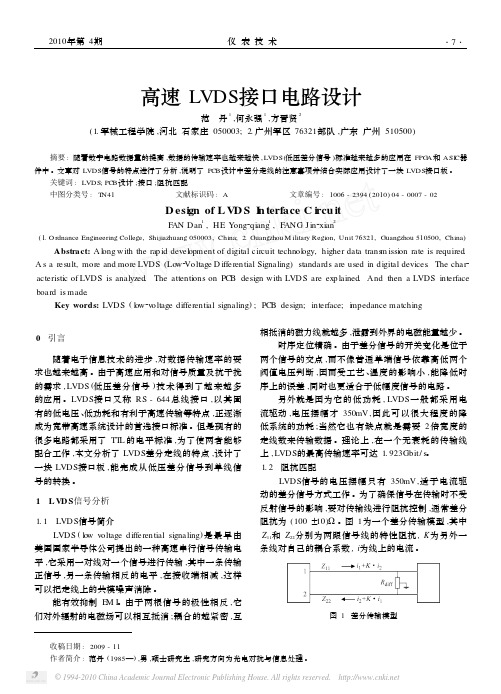

1.2 LVDS的工作原理图2 LVDS接口电路图如图2所示,LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3。

5mA),LVDS 接收器具有很高输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生生大约350mV的电压。

驱动器的输入为两个相反的电平信号,四个nMOS管的尺寸工艺是完全相同的.当输入为“1”时,标号IN+的一对管子导通,另一对管子截止,电流方向如图2,并产生大约350mV的压降;反之,输入为“0”时,电流反向,产生大约350mV的压降.这样根据流经电阻的电流方向,就把要传输的数字信号(CMOS信号)转换成了电流信号(LVDS信号)。

接受端可以通过判断电流的方向就得到有效的逻辑“1”和逻辑“0"状态。

从而实现数字信号的传输过程。

由于MOS管的开关速度很高,并且LVDS的电压摆幅低(350mV),因此可以实现高速传输.其电平特性如下图所示1.3 LVDS的国际标准LVDS是目前高速数字信号传输的国际通用接口标准,国际上有两个工业标准定义了LVDS:ANSI/TIA/EIA(American National Standards Institute/Telecommunications Industry Association/Electronic Industries Association)和IEEE(Institute for Electrical and Electronics Engineering)。

收稿日期:2009-11 作者简介:范丹(1985—),男,硕士研究生,研究方向为光电对抗与信息处理。

高速LVDS 接口电路设计范 丹1,何永强1,方晋贤2(1.军械工程学院,河北石家庄050003;2.广州军区76321部队,广东广州510500) 摘要:随着数字电路数据量的提高,数据的传输速率也越来越快,LVDS (低压差分信号)标准越来越多的应用在FPG A 和ASI C 器件中。

文章对LVDS 信号的特点进行了分析,说明了PC B 设计中差分走线的注意事项并结合实际应用设计了一块LVDS 接口板。

关键词:LVDS;PC B 设计;接口;阻抗匹配中图分类号:T N41 文献标识码:A 文章编号:1006-2394(2010)04-0007-02D esi gn of L V D S I n terface C i rcu itF AN Dan 1,HE Yong 2qiang 1,F ANG J in 2xian2(1.O rdnance Engineering College,Shijiazhuang 050003,China;2.Guangzhou M ilitary Regi on,Unit 76321,Guangzhou 510500,China )Abstract:A l ong with the rap id devel opment of digital circuit technol ogy,higher data trans m issi on rate is required .A s a result,more and more LVDS (Low 2Voltage D ifferential Signaling )standards are used in digital devices .The char 2acteristic of LVDS is analyzed .The attenti ons on PCB design with LVDS are exp lained .And then a LVDS interface board is made .Key words:LVDS (l ow 2v oltage differential signaling );PCB design;interface;i m pedance matching0 引言随着电子信息技术的进步,对数据传输速率的要求也越来越高。

lvds接口电路emi设计思路LVDS(Low Voltage Differential Signaling)是一种差分信号传输技术,广泛应用于高速数字信号传输中,特别适用于需要长距离传输高速数据的场景,如液晶显示器、计算机内部总线、医疗设备等。

然而,由于其高速传输和低功耗的特点,LVDS接口电路设计必须注重电磁兼容性(EMI)的问题。

EMI问题是由电路中的高速信号和电源噪声引起的,主要表现为辐射和传导两种模式。

辐射是指高速信号通过信号线辐射出的电磁波,可能干扰附近的设备或导致自身受到外界干扰;传导是指高速信号通过共模和差模传导途径进入其他信号线或供电线,干扰其他电路元件的正常工作。

因此,LVDS接口电路的EMI设计需要从以下几个方面考虑:1.布线和地引线设计:在LVDS接口电路设计中,布局和布线是非常重要的。

为了减少信号线的长度和面积,应尽量将信号线紧凑排列,并使用对称布局。

另外,地引线的设计也是关键,要保证低噪声接地和地引线干扰的最小化。

通常采用单独的地平面层或小洞式接地方式。

2.差分线路设计:LVDS接口电路一般使用差分信号传输,差分信号具有抗干扰能力强的特点。

因此,在PCB设计中要注意使差分信号线与附近的信号线和电源线保持一定的距离,以降低传导干扰。

3.终端的阻抗匹配:LVDS接口中的终端阻抗匹配能够减少信号反射和辐射,提高信号质量。

终端阻抗应与传输线的特性阻抗匹配。

常用的阻抗为100欧姆。

4.电源滤波:电源滤波是减少传导干扰的重要手段之一。

在设计LVDS接口电路的电源电路时,应加入合适的滤波电容和电感,以消除电源噪声。

5.电磁屏蔽:对于经过布线和终端匹配等措施后仍然存在辐射干扰的问题,可以采用电磁屏蔽的方法。

常见的电磁屏蔽方式有添加屏蔽罩、使用屏蔽连接器等。

6.地线设计:地线设计是减少辐射干扰的重要环节。

在布线过程中,应尽量使地线和信号线保持平行的走向,并避免穿过信号线打断其连续性。

另外,增加地线的宽度和厚度有助于提高信号的传输质量和抑制干扰。

常见LVDS屏接口定义讲解很多初学者对于如何区分屏的接口类型很是头疼,是LVDS屏,TTL屏还是RSDS 屏?总是很难搞清出。

如何快速识别出液晶屏的接口类型则需要一些经验的,下面从屏的屏线接口的样式来对接口类型做出分类的介绍,帮助大家快速识别屏的接口类型。

以下方法是个人认识,不足之处请大家谅解。

(1)TTL屏接口样式:D6T(单6位TTL):31扣针,41扣针。

对应屏的尺寸主要为笔记本液晶屏(8寸,10寸,11寸,12寸),还有部分台式机屏15寸为41扣针接口。

S6T(双6位TTL):30+45针软排线,60扣针,70扣针,80扣针。

主要为台式机的14寸,15寸液晶屏。

D8T(单8位TTL):很少见S8T(双8位TTL):有,很少见80扣针(14寸,15寸)(2)LVDS屏接口样式:D6L(单6位LVDS):14插针,20插针,14片插,30片插(屏显基板100欧姆电阻的数量为4个)主要为笔记本液晶屏(12寸,13寸,14寸,15寸)D8L(单8位LVDS):20插针(5个100欧姆)(15寸)S6L(双6位LVDS):20插针,30插针,30片插(8个100欧姆)(14寸,15寸,17寸)S8L(双8位LVDS):30插针,30片插(10个100欧姆电阻)(17寸,18寸,1 9寸,20寸,21寸)(3)RSDS屏接口样式:50排线,双40排线,30+50排线。

主要为台式机(15寸,17寸)液晶屏。

上面我们知道了屏的型号和接口了,但是我们还不知道这个是多少位的屏和多少的供电,为了让大家轻松搞会这一步,我们拿一个单6位LVDS的屏来解析一下,此款屏的型号为:LP141X3(20针插接口)屏接口定义在液晶屏的规格书里面都有这一个页面这里面出现了两组数据每组中都有一对时钟信号,这个屏我们就能看出这是一个30针双8位屏,屏的供电为5V。

常见的LVDS接口定义20PIN单6定义:1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16空17空18空19空20空每组信号线之间电阻为(数字表100欧左右)指针表20-100欧左右(4组相同阻值)20PIN双6定义:1:电源2:电源3:地4:地5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3-18:RO3+19:CLK1- 20:CLK1+每组信号线之间电阻为(数字表100欧左右)指针表20-100欧左右(8组相同阻值)20PIN单8定义:1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16:R3- 17:R3+每组信号线之间电阻为(数字表100欧左右)指针表20-100欧左右(5组相同阻值)30PIN双8定义:1:电源2:电源3:电源4:空5:空6:空7:地8:R0- 9:R0+ 10:R1- 11:R1+ 12:R2- 13:R2+ 14:地15:CLK- 16:CLK+ 17:地18:R3- 1 9:R3+ 20:RB0- 21:RB0+ 22:RB1- 23:RB1+ 24:地 25:RB2- 26:R B2+ 27:CLK2-28:CLK2+ 29:RB3- 30:RB3+每组信号线之间电阻为(数字表100欧左右)指针表20-100欧左右(10组相同阻值)一般14PIN、20PIN、30PIN为LVDS接口,15寸(含15寸)以下多为3.3V供电17(含17)以上多为5V供电。

LVDS接口电路基本原理1 LVDS接口电路的基本结构 (1)2 LVDS接口电路驱动器原理 (2)3 LVDS接口电路差分传输线 (4)3.1 差分线的阻抗匹配 (4)3.2 差分线的端接 (5)3.3 差分信号的布线 (6)4 LVDS接口电路接收器原理 (7)5 LVDS信号的测试 (8)5.1 选择示波器的要求 (8)5.2探头的选择 (9)1 LVDS接口电路的基本结构一个简单的LVDS传输系统由一个驱动器和一个接收器通过一段差分阻抗为100Ω的导体连接而成。

如图1所示,驱动器的电流源(通常为3.5mA)来驱动差分线对,由于接收器的直流输入阻抗很高,驱动器电流大部分直接流过100Ω的终端电阻,从而在接收器输入端产生的信号幅度大约350mV 。

通过驱动器的开关,改变直接流过电阻的电流的有无,从而产生“1”和“0”的逻辑状态。

在最新生产的LVDS接收器中,100Ω左右的电阻甚至被直接集成在片内输入端上,如MAXIM公司的MAX9121/9122等。

图1 LVDS接口电路基本结构2 LVDS接口电路驱动器原理The Telecommunications Industry Association(TIA)颁布了一个标准,规定了用于转换二进制信号的LVDS接口电路的电气规格。

LVDS技术利用低电压差分信号来产生高速、低功率的数据传输。

差分信号的使用消除了共模噪声,因此确保了数据的传输速度以及抗噪性能。

如果想了解LVDS标准的详细信息,请查阅“Electrical Characteristics of Low Voltage Differential Signaling(LVDS)Interface Circuits”,TIA/EIA-644(March 1996)。

图2-1举例说明了一个通过一对差分连线115连接到一个LVDS接收器110的LVDS发生器100。

LVDS发生机100将一个数字的输入信号D_IN转换成为一对在差分输出终端TX_A和TX_B上的相反的LVDS输出信号。

第27卷 第5期 武汉理工大学学报・信息与管理工程版 Vol .27No .52005年10月 JOURNAL OFWUT (I N FORMATI O N &MANAGE MENT ENGI N EER I N G ) Oct .2005文章编号:1007-144X (2005)05-0189-04收稿日期:2005-05-15.作者简介:彭 勇(1982-),男,山东滕州人,武汉理工大学信息工程学院硕士研究生.基金项目:湖北省自然科学基金资助项目(2004ABA045).LVDS 的接口电路设计彭 勇,黄秋元(武汉理工大学信息工程学院,湖北武汉430070)摘 要:LVDS 是一种小振幅差分信号技术,使用这种技术传输速率可以达到数百兆,甚至更高;LVDS 具有更低的功耗、更好的噪声性能和更可靠的稳定性。

简要地介绍了LVDS 的原理及优势,分析了LVDS 接口设计要注意的问题,着重研究了LVDS 与LVPECL 、C ML 间的接口设计;同时给出了不同耦合方式下的电路设计图。

关键词:LVDS;C ML;LVPEC L;直流耦合;交流耦合中图法分类号:T N75 文献标识码:A1 引 言对于高速电路,尤其是高速数据总线,常用的器件一般有ECL 、BT L 和GT L 等。

这些器件的工艺成熟,应用也较为广泛,但都存在一个共同的弱点,即功耗大。

此外,采用单端信号的BT L 和GT L 器件,电磁辐射也较强。

目前,NS 公司率先推出的C MOS 工艺的低电压差分信号器件,即LVDS 给了人们另一种选择。

2 L VD S 技术简介LVDS (Low Voltage D ifferential Signaling )是一种小振幅差分信号技术,使用非常低的幅度信号(约350mV )通过一对差分PCB 走线或平衡电缆传输数据。

它允许单个信道传输速率达到每秒数百兆比特,其特有的低振幅及恒流源模式驱动只产生极低的噪声,消耗非常小的功率。

一种lvds接口电路设计与实现LVDS,即低电压差分信号,是一种传输高速数字信号的技术,在大容量数据传输领域得到广泛应用。

其特点是高速、低功耗、抗干扰能力强等,因此在液晶显示器、图像处理、医疗设备等领域得到了广泛应用。

本文将介绍一种LVDS接口电路的设计与实现,旨在为读者提供一种实用性强、性能稳定的电路设计方法。

一、设计原理本电路采用FPGA控制器与LVDS转换芯片结合的方式,实现了高速信号的传输和转换。

其主要原理如下:1. FPGA控制器生成高速数据信号本电路采用FPGA控制器作为数据信号发生器,提供高速数据信号作为输入信号。

在FPGA中,可以通过VHDL或Verilog语言实现高速数据发生器的设计。

产生的高速数据信号通过输出端口输出到LVDS转换芯片的输入端口。

2. LVDS转换芯片将信号转换为LVDS格式LVDS转换芯片是本电路必不可少的关键部件,它可以将FPGA输出的高速数据信号转换为LVDS格式的差分信号。

LVDS信号由一对反向的信号线组成,分别为正向传输线和反向传输线,通过大小电流的差分信号来传输数据。

LVDS信号特点是传输速率高、功耗低、抗干扰能力强等。

3. LVDS差分信号在接收端恢复为原信号在接收端,又通过LVDS接收芯片对差分信号进行解码,恢复出原始信号。

接收端的LVDS接收芯片与发射端的LVDS转换芯片需要匹配,以确保差分信号的传输质量和可靠性。

二、硬件设计1. FGA控制器的选型与设计在本电路中,FPGA控制器作为高速数据信号发生器,需选择具有高速IO接口、低功耗、可编程性好的器件。

目前在市场上常见的FPGA控制器系列有Xilinx Virtex、Spartan、Artix、Kintex等,以及ALTERA的Cyclone、Stratix等等。

具体在设计过程中,要根据自身需要选择适合的FPGA控制器。

本设计选用Xilinx Spartan-6系列的FPGA器件,其主要特点如下:(1)高速IO引脚数量多,速度快:支持高达3.2Gbps的数据传输速率,单向IO引脚数量高达830个,双向IO引脚数量高达384个。

LVDS的接口电路设计

丁宏伟

摘要:LVDS是一种小振幅差分信号技术,使用这种技术传输速率可以达到数百兆,甚至更高; LVDS具有更低的功耗、更好的噪声性能和更可靠的稳定性。

简要地介绍了LVDS的原理及优势,分析了LVDS接口设计要注意的问题。

关键词:LVDS;接口;PCB

中图分类号:TP336 文献标志码:A

引言

LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS这种技术的核心是采用极低的电压摆幅(约350 mV)高速差动传输数据,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。

1 LVDS驱动器和接收器工作原理

LVDS定义在2个国际标准中: IEEE P1596.3 (1996 年3 月通过) , 主要面向SC I ( ScalableCoherent Interface) ,定义了LVDS的电特性,还定义了SC I协议中包交换时的编码; ANSI /EIA -644 (1995年11月通过) ,主要定义了LVDS的电特性,并建议了655 Mb / s的最大速率和1. 823Gb / s的无失真媒质上的理论极限速率。

在2个标准中都指定了与物理媒质无关的特性,这保证了LVDS能成为多用途的接口标准[ 1]。

如图1所示,LVDS电路由驱动器和接收器以及终端匹配电阻组成。

M1、M2、M3和M4是尺寸、工艺相同的NMOS管开关。

驱动器的输出接在阻值为100Ω的终端电阻上,构成回路。

驱动器工作时,NMOS开关M1和M4以及M2和M3在CMOS信号的作用下轮流导通和截止,在输出端产生±3.5 mA的回路电流。

绝大部分驱动电流将流经100Ω的终端电阻,并在接收器输入端产生大约350 mV的压降。

当驱动状态反转时,流经电阻的电流方向改变,于是在接收端产生了一个有效“0”或“1”的逻辑状态。

从而把一个CMOS信号转换成了LVDS[ 2]。

图1 LVDS电路的工作示意图

在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

所谓信号对,是指LVDS接口电路中,每一个数据传输通道或时钟传输通道的输出都为两个信号(正输出端和负输出端)。

LVDS的驱动和接收不依赖于供电规格,从而可以保持同样的信号电平和性能。

LVDS的信号电平只有PECI 电压摆幅的一半,是TTI /CMOS电平的1/1O。

LVDS提供低功耗的解决方案,其负载终端电阻的功耗仅为1.2 mW。

电流驱动模式也降低了系统的功耗。

2 LVDS的应用模式

2.1 单向点对点(point-to-point)

这是典型的应用模式,每个点到点连接的差分对由一个驱动器、互连器和接收器组成。

驱动器和接收器主要完成TTL信号和LVDS信号之问的转换。

互连器包含电缆、PCB上差分导线对以及匹配电阻。

单向点对点应用模式是芯片问、插件问、机架问通讯的理想接口。

2.2 双向点对点

能通过一对双绞线实现双向的半双工通信。

可以由标准的LVDS的驱动器和接收器构成。

但更好的办法是采用总线LVDS驱动器,即BLVDS,这是为总线两端都接负载而设计的。

2.3 多分支形式(multidrop)

即一个驱动器连接多个接收器。

当有相同的数据要传给多个负载时,可以采用这种应用形式。

2.4 多点结构(multipoint)

此时多点总线支持多个驱动器,也可以采用BLVDS驱动器。

它可以提供双向的半双工通信,但是在任一时刻,只能有一个驱动器工作。

因而发送的优先权和总线的仲裁协议都需要依据不同的应用场合,选用不同的软件协议和硬件方案[ 3 ]。

3 LVDS系统的设计

了解LVDS接口特性后,下面的问题就是如何在设计中应用好LVDS接口产品,充分发挥其技术优点,优化系统设计。

3.1 PCB板的设计

PCB布线总的原则是:阻抗要匹配。

这是非常重要的,差分阻抗的不匹配会产生反射,会减弱信号并增加共模噪声,线路上的共模噪声将得不到差分线路磁场的抵消而产生电磁辐射。

以下是PCB板设计中需注意的问题:

a.至少用4层PCB板,将LVDS信号、地、电源、TTI 信号分层布局;

b.使TTL信号和LVDS信号相互隔离,否则TTL可能会耦合到LVDS线上,最好将TTL和LVDS信号放在由电源、地层隔离的不同层上;

c.保持发送器和接收器尽可能靠近接插件,连线长度愈短愈好[(小于37.6 ram(1.5英寸)],以保证板上噪声不会被带到差分线上,而且避免电路板及电缆线问的交叉EMI干扰;

d.旁路每个LVDS器件,分布式散装电容或表贴电容放在尽量靠近电源和地线引脚处;

e.电源层和地层应使用粗线,保持PCB地线层返回路径宽而短;

f.终端负载用100Ω表贴电阻靠近接收器输入端来匹配传输线的差分阻抗,终端电阻到接收器输入端的距离应小于7 mm;

g.将所有空闲引脚开路(悬空)。

3.2 差分线的设计

a.使用与传输媒质的差分阻抗和终端电阻相匹配的受控阻抗线,并且使差分线对离开集成芯片后立刻尽可能地相互靠近(距离小于10 mm),这样能减少反射并能确保耦合到的噪声为共模噪声;

b.使差分线对的长度相互匹配,以减少信号扭曲,防止引起信号问的相位差而导致电磁辐射;

c.尽量减少过孔和其它会引起线路不连续性的因素;

d.避免使用90°的走线,这将导致阻值的不连续。

3.3 电缆和接插件的选择

a.就减少噪声和提高信号质量而言,平衡电缆(如双绞线对)比非平衡电缆好。

当电缆长度小于0.5 m 时,大部分电缆都能有效工作,距离在0.5 m~10 m之问时,CAT 3(Category 3)双绞线对效果好,距离大于10 m并且要求高速率时,建议使用CAT 5双绞线对。

b.接插件一般选择标准连接器,在连接器上差分信号通常连接在一行中靠近的两个连接脚上。

4 结语

总之,LVDS数据传输标准比传统的RS-232、RS-422等标准有很大的优越性。

用LVDS技术来完成数据传输,将会降低系统设计的复杂度,使系统有很高的可靠性、高数据率、低噪声、低电磁辐射和低成本。

参考文献:

[ 1 ] 赵忠文,曾岱,熊伟. LVDS技术分析和应用设计[ J ]. 指挥技术学院学报, 2001, 12 (6) : 1 - 2.

[ 2 ] 宋正勋,谭宝华. 低压差分信号技术[ J ]. 长春光学精密机械学院学报, 2000, 23 (2) : 2 - 3.

[ 3 ] Stephen Kempainen. Low Voltage Differential Signaling[ J ]. Insight, 2000, 5 (2) : 15 - 20.。