8.7 TLC7524接口电路程序

- 格式:doc

- 大小:25.50 KB

- 文档页数:2

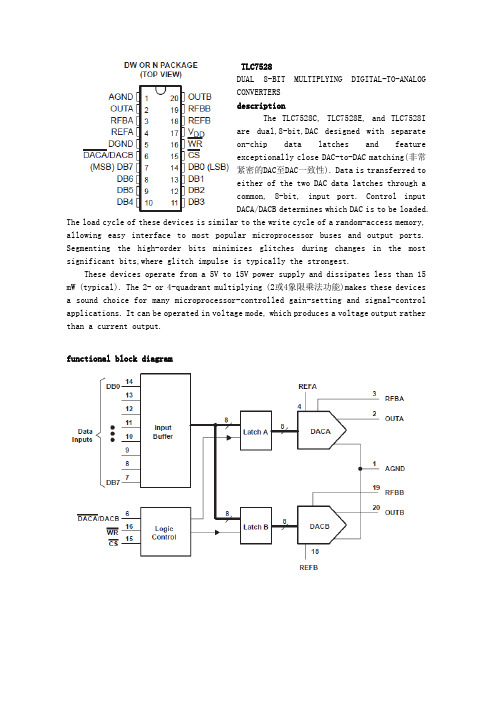

TLC7528DUAL 8-BIT MULTIPLYING DIGITAL-TO-ANALOGCONVERTERSdescriptionThe TLC7528C, TLC7528E, and TLC7528Iare dual,8-bit,DAC designed with separateon-chip data latches and featureexceptionally close DAC-to-DAC matching(非常紧密的DAC至DAC一致性). Data is transferred toeither of the two DAC data latches through acommon, 8-bit, input port. Control inputDACA/DACB determines which DAC is to be loaded. The load cycle of these devices is similar to the write cycle of a random-access memory, allowing easy interface to most popular microprocessor buses and output ports. Segmenting the high-order bits minimizes glitches during changes in the most significant bits,where glitch impulse is typically the strongest.These devices operate from a 5V to 15V power supply and dissipates less than 15 mW (typical). The 2- or 4-quadrant multiplying (2或4象限乘法功能)makes these devices a sound choice for many microprocessor-controlled gain-setting and signal-control applications. It can be operated in voltage mode, which produces a voltage output rather than a current output.functional block diagramoperating sequencerecommended operating conditionselectrical characteristics over recommended operating free-air temperature range, VrefA = VrefB = 10 V, VOA and VOB at 0 V (unless otherwise noted)operating characteristics over recommended operating free-air temperature range, VrefA = VrefB = 10 V, VOA and VOB at 0 V (unless otherwise noted)NOTES:1. OUTA, OUTB load = 100 W, Cext = 13 pF; WR and CS at 0 V; DB0–DB7 at 0 V to VDD or VDD to 0 V.2. Gain error is measured using an internal feedback resistor. Nominal full scale range (FSR) = Vref – 1 LSB.3. Vref = 20 V peak-to-peak, 100-kHz sine wave; DAC data latches loaded with 00000000.4. Temperature coefficient of gain measured from 0°C to 25°C or from 25°C to 70°C.5. VrefA = VrefB = 10 V; OUTA/OUTB load = 100 W, Cext = 13 pF; WR and CS at 0 V; DB0–DB7 at 0 V to VDD orVDD to 0 V.6. Both DAC latches loaded with 11111111; VrefA = 20 V peak-to-peak, 100-kHz sine wave; VrefB = 0; TA = 25°C.7. Both DAC latches loaded with 11111111; VrefB = 20 V peak-to-peak, 100-kHz sine wave; VrefA = 0; TA = 25°C.These devices contain two identical, 8-bit-multiplying D/A converters, DACA and DACB. Each DAC consists of an inverted R-2R ladder, analog switches, and input data latches. Binary-weighted currents are switched between DAC output and AGND, thus maintaining a constant current in each ladder leg independent of the switch state. Most applications require only the addition of an external operational amplifier and voltage reference. A simplified D/A circuit for DACA with all digital inputs low is shown in Figure 1.Figure 2 shows the DACA equivalent circuit. A similar equivalent circuit can be drawn for DACB. Both DACs share the analog ground terminal 1 (AGND). With all digital inputs high, the entire reference current flows to OUTA. A small leakage current (IIkg) flows across internal junctions, and as with most semiconductor devices,doubles every 10°C. Co is due to the parallel combination of the NMOS switches and has a value that depends on the number of switches connected to the output. The range of Co is 50 pF to 120 pF maximum. The equivalent output resistance (ro) varies with the input code from 0.8R to 3R where R is the nominal value of the ladder resistor in the R-2R network. These devices interface to a microprocessor through the data bus, CS, WR, and DACA/DACB control signals. When CS and WR are both low, the TLC7528 analog output, specified by the DACA/DACB control line, responds to the activity on the DB0–DB7 data bus inputs. In this mode, the input latches are transparent and input data directly affects the analog output. When either the CS signal or WR signal goes high, the data on the DB0–DB7 inputs is latched until the CS and WR signals go low again. When CS is high, the data inputs are disabled regardless of the state of the WR signal.The digital inputs of these devices provide TTL compatibility when operated froma supply voltage of 5 V. These devices can operate with any supply voltage in the range from 5 V to 15 V; however, input logic levels are not TTL compatible above 5 V.These devices are capable of performing 2-quadrant or full 4-quadrant multiplication.Figure 3. Unipolar Operation (2-Quadrant MultiplicationNOTES:A. R1, R2, R3, and R4 are used only if gain adjustment is required. See table for recommended values. Make gain adjustment with digital input of 255.B. C1 and C2 phase compensation capacitors (10 pF to 15 pF) are required when using high-speed amplifiers to prevent ringing or oscillation.Figure 4. Bipolar Operation (4-Quadrant Operation)NOTES:A. R1, R2, R3, and R4 are used only if gain adjustment is required. See table in Figure3 for recommended values. Adjust R1 for VOA = 0 V with code 10000000 in DACA latch. Adjust R3 for VOB = 0 V with 10000000 in DACB latch.B. Matching and tracking are essential for resistor pairs R6, R7, R9, and R10.C. C1 and C2 phase compensation capacitors (10 pF to 15 pF) may be required if A1 and A3 are high-speed amplifiers.TCL7528是双路、8位数字—模拟转换器,他设计成具有单独的片内数据锁存器,其特点包括非常紧密的DAC至DAC一致性。

cf745电路工作原理CF745是一种基于Microchip技术的8位Flash单片机,以下是其工作原理:1. 时钟信号:CF745需要一个时钟信号来同步其内部操作。

时钟信号可以通过外部晶体振荡器提供,或者通过内部RC振荡器生成。

2. 存储器:CF745具有内部Flash存储器和RAM存储器。

Flash存储器用于存储程序代码和常量数据,RAM存储器用于存储临时变量和数据。

3. 输入/输出:CF745具有多个通用输入/输出引脚,可以与外部电路或外设连接。

通过配置寄存器,可以将这些引脚配置为输入模式或输出模式,并设置相应的电平。

4. 中断:CF745支持多级中断,并且具有多个中断源可供选择。

当外部事件触发中断源时,CF745将中断标志设置为高,并跳转到相应的中断服务程序执行。

5. 定时器:CF745具有多个定时器,可用于生成定时延迟、测量时间间隔和产生PWM信号等功能。

通过配置寄存器,可以设置定时器的计数模式、时钟源和预分频器等参数。

6. 串口通信:CF745通过串口进行与外部设备的通信。

它支持多种串口协议,如UART、SPI和I2C等。

通过配置寄存器,可以设置串口的波特率、数据位数、校验位和停止位等参数。

7. 算术逻辑单元(ALU):CF745具有一组算术逻辑单元,用于执行算术和逻辑运算。

它支持常见的算术操作(如加法、减法)和逻辑操作(如与、或)等。

8. 控制单元:CF745的控制单元负责对指令进行解码和执行。

它从存储器中读取指令,并根据指令执行相应的操作。

控制单元还管理中断、定时器和外设等各个模块的协调工作。

通过上述组成部分的协同工作,CF745能够执行各种任务,包括数据处理、外设控制、通信和定时等。

它是一种功能强大的单片机,被广泛应用于各种应用领域,如工业自动化、智能家居和消费电子产品等。

A/D、D/A转换电路设计、调试及数据处理实验时间:第11周星期一3 - 4节A/D、D/A转换电路设计、调试及数据处理实验目的1.学习 A/D 转换器原理及接口方法,并掌握 ADC0809 芯片的使用2.学习 D/A 转换器原理及接口方法,并掌握 TLC7528 芯片的使用实验设备PC 机一台,TD-ACC+实验系统一套,i386EX 系统板一块实验内容1.编写实验程序,将-5V ~ +5V 的电压作为 ADC0809 的模拟量输入,将转换所得的 8位数字量保存于变量中。

2.编写实验程序,实现 D/A 转换产生周期性三角波,并用示波器观察波形。

实验原理1.A/D 转换实验转换实验ADC0809 芯片主要包括多路模拟开关和 A/D 转换器两部分,其主要特点为:单电源供电、工作时钟 CLOCK 最高可达到 1200KHz、8 位分辨率,8 个单端模拟输入端,TTL 电平兼容等,可以很方便地和微处理器接口。

TD-ACC+教学系统中的 ADC0809 芯片,其输出八位数据线以及 CLOCK 线已连到控制计算机的数据线及系统应用时钟 1MCLK (1MHz)上。

其它控制线根据实验要求可另外连接 (A、B、C、STR、/OE、EOC、IN0~IN7)。

根据实验内容的第一项要求,可以设计出如图所示的实验线路图。

上图中,AD0809 的启动信号“STR”是由控制计算机定时输出方波来实现的。

“OUT1”表示 386EX 内部 1#定时器的输出端,定时器输出的方波周期=定时器时常。

图中 ADC0809 芯片输入选通地址码 A、B、C 为“1”状态,选通输入通道 IN7;通过单次阶跃单元的电位器可以给 A/D 转换器输入-5V ~ +5V 的模拟电压;系统定时器定时1ms输出方波信号启动 A/D 转换器,并将 A/D 转换完后的数据量读入到控制计算机中,最后保存到变量中。

参考流程:参考程序:请参照随机软件中的 example 目录中 ACC1-1-1.ASM 文件如下:PUBLIC AD0,AD1,AD2,AD3,AD4,AD5,AD6,AD7,AD8,AD9 ;声明全局变量STACK1 SEGMENT STACKDW 256 DUP(?)STACK1 ENDSDATA SEGMENTAD0 DB ? ;存储 A/D 采集的数值,共十个值AD1 DB ?AD2 DB ?AD3 DB ?AD4 DB ?AD5 DB ?AD6 DB ?AD7 DB ?AD8 DB ?AD9 DB ?DATA ENDSCODE SEGMENTASSUME CS:CODESTART: MOV AX,DATA ;将当前的 DATA 赋给数据段 DSMOV DS,AXCALL SYSINTI ;调用系统初始化子程序MOV DX,0F043HMOV AL,076H ;初始化 1#定时器定时 1msOUT DX,ALMOV DX,0F041HMOV AL,0E8H ;写 1#定时器定时常数的低字节OUT DX,ALMOV DX,0F041HMOV AL,03H ;写 1#定时器定时常数的高字节,同时启动 AD 转换 OUT DX,ALMOV CX,000AH ;赋 AD 采样值个数初值为 0AHMOV SI,OFFSET AD0 ;将存放 AD 采样值的首地址赋给 SI 寄存器AGAIN: CALL DELAY ;调延时子程序MOV DX,0300HIN AL,DX ;读 AD 采样值MOV [SI],AL ;将 AD 采样值存放于 SI 中INC SI ;SI 指向下一个采样值对应的单元LOOP AGAIN ;10 个采样值存放完否?没有存完,则继续存MOV CX,000AH ;存放完成后,将 CX 和 SI 还原,赋初值MOV SI,OFFSET AD0JMP AGAIN ;继续DELAY: PUSH CX ;延时子程序MOV CX,3000HDEL1: PUSH AXPOP AXLOOP DEL1POP CXRETSYSINTI:MOV AX,8000H ;系统初始化子程序OUT 23H,AL ;扩展 IO 使能XCHG AL,AHOUT 22H,ALOUT 22H,AXMOV DX,0F402H ;初始化系统片选 CS0#的范围为:300H~30FH MOV AX,000CHOUT DX,AXMOV DX,0F400HMOV AX,0401HOUT DX,AXMOV DX,0F406HMOV AX,0000HOUT DX,AXMOV DX,0F404HMOV AX,3C01HOUT DX,AXMOV DX,0F822H ;初始化管脚配置 P2CFG,配置 CS0#MOV AL,7FHOUT DX,ALMOV DX,0F824H ;初始化管脚配置 P3CFG,配置主片 IRQ7MOV AL,0B2HOUT DX,ALMOV DX,0F832H ;初始化管脚配置 INTCFGMOV AL,0AHOUT DX,ALMOV DX,0F834H ;初始化管脚配置 TMRCFGMOV AL,15H ;将 GATE1 接 VCCOUT DX,ALRETCODE ENDSEND START实验步骤与结果:(1) 打开联机操作软件,参照流程图,在编辑区编写实验程序。

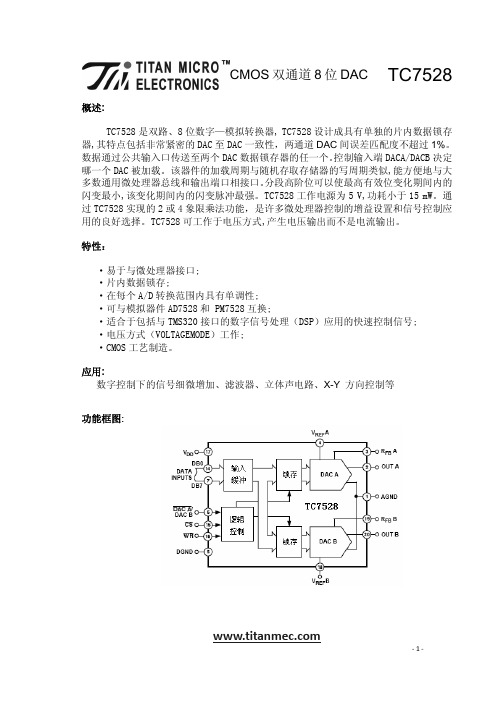

概述:TC7528是双路、8位数字—模拟转换器, TC7528设计成具有单独的片内数据锁存器,其特点包括非常紧密的DAC 至DAC 一致性,两通道DAC 间误差匹配度不超过1%。

数据通过公共输入口传送至两个DAC 数据锁存器的任一个。

控制输入端DACA/DACB 决定哪一个DAC 被加载。

该器件的加载周期与随机存取存储器的写周期类似,能方便地与大多数通用微处理器总线和输出端口相接口。

分段高阶位可以使最高有效位变化期间内的闪变最小,该变化期间内的闪变脉冲最强。

TC7528工作电源为5 V,功耗小于15 mW。

通过TC7528实现的2或4象限乘法功能,是许多微处理器控制的增益设置和信号控制应用的良好选择。

TC7528可工作于电压方式,产生电压输出而不是电流输出。

特性:·易于与微处理器接口; ·片内数据锁存; ·在每个A/D 转换范围内具有单调性; ·可与模拟器件AD7528和 PM7528互换; ·适合于包括与TMS320接口的数字信号处理(DSP)应用的快速控制信号; ·电压方式(VOLTAGEMODE)工作; ·CMOS 工艺制造。

应用:数字控制下的信号细微增加、滤波器、立体声电路、X-Y 方向控制等功能框图:管脚定义:管脚说明:管脚号 符号 说明 1 AGND 模拟电源地 2 OUTA DAC A 路模拟输出端 3 R FB A DAC A 路反馈电阻端 4 V REF A A 路基准电压输入端 5 DGND 数字电源地 6 /DAC A/DAC B DAC 路选择 7~14 DB7(MSB )~ DB0(LSB )八位数据输入高位~低位15 CS 片选线,低电平有效 16 WR 写操作,低电平有效 17 VDD 芯片电源 18 V REF B B 路基准电压输入端 19 R FB B DAC B 路反馈电阻端 20 OUTB DAC B 路模拟输出端规格参数:最大额定范围:(TA = +25°C unless otherwise noted)VDD to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V, +6 V VDD to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V, +6 V AGND to DGND . . . . . . . . . . . . . . . . . . . . . . . . VDD + 0.3 V DGND to AGND . . . . . . . . . . . . . . . . . . . . . . . . VDD + 0.3 V Digital Input Voltage to DGND . . . . . . . –0.3 V, VDD + 0.3 V VPIN2, VPIN20 to AGND . . . . . . . . . . . . . . –0.3 V, VDD + 0.3 V VREF A, VREF B to AGND . . . . . . . . . . . . . . . . . . . . . . . ±5 V VRFB A, VRFB B to AGND . . . . . . . . . . . . . . . . . . . . . . . ±5 V Power Dissipation (Any Package) to +75°C . . . . . . . 450 mW Derates above +75°C by . . . . . . . . . . . . . . . . . . . 6 mW/°C Operating Temperature RangeCommercial (J, K, L) Grades . . . . . . . . . . . –40°C to +85°C Industrial (A, B, C) Grades . . . . . . . . . . . . –40°C to +85°C Extended (S, T, U) Grades . . . . . . . . . . . –55°C to +125°C Storage Temperature . . . . . . . . . . . . . . . .–65°C to +150°C Lead Temperature (Soldering, 10 secs) . . . . . . . . … .+300°C接口逻辑:DAC 部分:两通道的DAC 锁存来自公共的一路8BIT 的数据.控制输入脚DACA/DACB 将会选择哪一路DAC 接受输入脚的8BIT 数据。

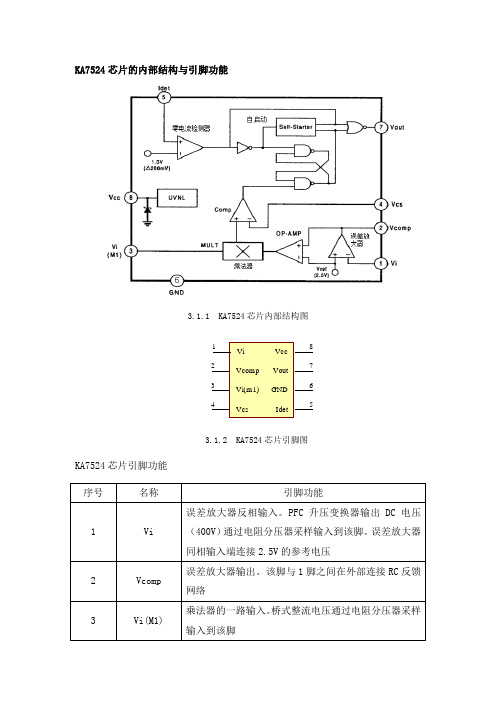

KA7524芯片的内部结构与引脚功能3.1.1 KA7524芯片内部结构图Vi 1Vcomp 2Vi(m1)3Vcs4Idet5GND 6Vout 7Vcc 83.1.2 KA7524芯片引脚图KA7524芯片引脚功能 序号名称引脚功能1Vi误差放大器反相输入。

PFC 升压变换器输出DC 电压(400V )通过电阻分压器采样输入到该脚。

误差放大器同相输入端连接2.5V 的参考电压2Vcomp误差放大器输出。

该脚与1脚之间在外部连接RC 反馈网络3 Vi(M1)乘法器的一路输入。

桥式整流电压通过电阻分压器采样输入到该脚3.2 KA7524的电气特性KA7524芯片集模拟与数字电路于一体,内含误差放大器、一象限乘法器、电流感测比较器、零电流检测器、控制逻辑及推拉式驱动输出级等电路。

KA7524提供必要的功能来实现的电子镇流器控制和SMPS,应用于有源功率因数校正电路设计。

①内部自启动②微功率启动模式③包括欠压锁定电路④内部1%的基准⑤最高输出电流峰值500mA最大额定绝对值TA=25 ℃电气特性所有电压参考GND,除非已指定相位裕度MPH 57电器特性参数符号测试条件最小值典型最大值单位乘数节M1输入电压范围Vi(m1) 0 2 V M2输入电压范围Vi(m2) Vref Vref V 输入偏置电流Ibias -2 -0.5 2 uA乘法器增益Gv Vi(m1)=0.5VVi(m2)=2V0.8 /V乘法器增益稳定STt -0.2 %1电流检测部分输入电压阀值Vth 10 1.3 1.6 V 迟滞Vths 200 mV 输入低钳位电压Vic(L) Idet=0mA 0.95 V 输入高钳位电压Vic(H) Idet=3mA 6.1 7.1 V 输入电流Ii 0.8V<Vdet<6V 5 uA输入钳位二极管Icd Vdet<0.9VVdet>6V3 mA目前的检测部分输入电压(高)Vo(H) Io=-10mAVcc=12V7 9 V输入电压(低)Vo(L) Io=10mAVcc=12V0.8 1.8 V上升时间tr CL=1000PF 100 200 ns 下降时间tf CL=1000PF 90 200 ns 自启动部分自开始时间tss 12 us注意:1.参考不能测试的PKG2.Gv=。

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

Rev. 1.1012014-03-19• 低压降• 较低的温度系数• 高输入电压 (高达 30V)• 静态电流 1μA • 大电流输出:100m A • 输出电压精度:±2%• 封装类型:TO92, SOT89 和 SOT23-5应用领域• 电池供电设备• 通信设备• 音频/视频设备HT75xx-3 系列是一组CMOS 技术实现的三端低功耗高电压稳压器。

输出电流为 100m A 且允许的输入电压可高达 30V 。

具有几个固定的输出电压,范围从 2.1V 到 12.0V 。

CMOS 技术可确保其具有低压降和低静态电流的特性。

尽管主要为固定电压调节器而设计,但这些 IC 可与外部元件结合来获得可变的电压和电流。

选型表注:“xx ”代表输出电压。

Rev. 1.1022014-03-19引脚图nt极限参数电源供应电压 ...................................................−0.3V ~ 33V 储存温度范围 ...............................................−50°C ~ 125°C工作环境温度 .................................................−40°C ~ 85°C注: 这里只强调额定功率,超过极限参数所规定的范围将对芯片造成损害,无法预期芯片在上述标示范围外的工作状态,而且若长期在标示范围外的条件下工作,可能影响芯片的可靠性。

热能信息注:P D 值是在 Ta = 25°C 时测得。

电气特性HT7521-3, +2.1V 输出类型注:在 V IN = V OUT+2V 与一个固定负载条件下使输出电压下降 2%,此时的输入电压减去输出电压就是Dropout 电压。

HT7523-3, +2.3V 输出类型注:在 V IN = V OUT+2V 与一个固定负载条件下使输出电压下降 2%,此时的输入电压减去输出电压就是Dropout 电压。

基于SA7527的LED照明驱动电路的设计第一篇:基于SA7527的LED照明驱动电路的设计基于SA7527的LED照明驱动电路的设计随着社会的发展,人们越来越提倡绿色照明,LED日光灯作为其中一种正在被广泛使用,LED日光灯相对于普通的日光灯具备节能、寿命长、适用性好等特点,因单颗LED的体积小,可以做成任何形状,拥有回应时间短、环保、无有害金属、废气物容易回收、色彩绚丽、发光色彩纯正等优势。

本文通过SA7527设计的一款LED日光灯驱动电路,稳定可靠性比较好,不仅能够降低日光灯的成本,提高它的转化效率,还可以实现恒流恒压输出,同时能驱动不同功率的LED。

一、电路的设计1.电路组成全电路由抗浪涌保护、EMI 滤波、全桥整流、反激式变换器、PWMLED驱动控制器、闭环反馈电路组成,如图1。

图1 基于SA7527的LED驱动电路框图2.主电路分析主电路如图2所示。

从AC220V看去,交流市电入口接有熔丝F1和抗浪涌的压敏电阻RV1,熔丝起到线路输入电路过流保护的作用,压敏电阻RV1用来抑制来自电网的瞬时高电压保护输入线路的安全,之后是EMI滤波器,L1,L2,C1是共模滤波器,L3,L4,C2是差模滤波器,DB107是全桥整流电路,C13是一个电容滤波器,经过整流后的电压(电流)仍然是有脉冲的直流电。

为了减少波动,通常要加滤波器,由R19,C8,D5组成的RCD缓冲电路是为了防止功率管Q1在关断过程中承受大反压,缓冲电路的二极管一般选择快速恢复二极管。

输出滤波器C10,C11,C12并联是为了减少电压纹波。

本电路的特点:(1)宽电压输入范围;(2)恒流/恒压特性;(3)由LM358组成的输出反馈取样与恒流/恒压控制电路,成本低,控制精度高,调试简单;(4)本电路可以驱动不同功率的LED。

3.启动电路的设计启动电路如图2所示。

为了使电路正常启动,应该在整流桥整流后的变压器初级线圈与SA7527的供电电压端8脚之间连接一个启动电阻R20,并在8脚与地之间连接一个启动电容C9。

8.7 TLC7524接口电路程序

见随书所附光盘中文件:TLC7524VHDL程序与仿真。

--文件名:TLC7524.VHD

--功能:产生156.25KHz的正弦波。

--最后修改日期:

library ieee;

use ieee.std_logic_arith.all;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity TLC7524 is

port( clk :in std_logic; --系统时钟rst :in std_logic; --复位信号

data_out:out std_logic_vector(7 downto 0)); --波形数据

end TLC7524;

architecture behav of TLC7524 is

signal b:integer range 0 to 63; --地址计数器

signal q:integer range 0 to 4; --计数器

signal d:integer range 0 to 255; --波形数据寄存器begin

process(clk) --此进程通过对系统时钟的分频,完成的地址计数器的循环计数begin

if rst='1' then b<=0; --复位时,对地址寄存器清零elsif clk'event and clk='1' then

if q=4 then q<=0; --此IF语句完成对系统时钟的5分频if b=63 then b<=0; --此IF语句完成对地址的循环计数

else b<=b+1;

end if;

else q<=q+1;

end if;

end if;

end process;

process(b) --此进程存储了正弦波64个采样点的波形数据begin

case b is

when 00=> d<=255 ; when 01=> d<=254 ;when 02=> d<=252 ;when 03=> d<=249 ; when 04=> d<=245 ; when 05=> d<=239 ;when 06=> d<=233 ;when 07=> d<=225 ; when 08=> d<=217 ; when 09=> d<=207 ;when 10=> d<=197 ;when 11=> d<=186 ; when 12=> d<=174 ; when 13=> d<=162 ;when 14=> d<=150 ;when 15=> d<=137 ; when 16=> d<=124 ; when 17=> d<=112 ;when 18=> d<= 99 ;when 19=> d<= 87 ; when 20=> d<= 75 ; when 21=> d<= 64 ;when 22=> d<= 53 ;when 23=> d<= 43 ;

when 24=> d<= 34 ; when 25=> d<= 26 ;when 26=> d<= 19 ;when 27=> d<= 13 ;

when 28=> d<= 8 ; when 29=> d<= 4 ;when 30=> d<= 1 ;when 31=> d<= 0 ; when 32=> d<= 0 ; when 33=> d<= 1 ;when 34=> d<= 4 ;when 35=> d<= 8 ; when 36=> d<= 13 ; when 37=> d<= 19 ;when 38=> d<= 26 ;when 39=> d<= 34 ;

when 40=> d<= 43 ; when 41=> d<= 53 ;when 42=> d<= 64 ;when 43=> d<= 75 ;

when 44=> d<= 87 ; when 45=> d<= 99 ;when 46=> d<=112 ;when 47=> d<=124 ; when 48=> d<=137 ; when 49=> d<=150 ;when 50=> d<=162 ;when 51=> d<=174 ; when 52=> d<=186 ; when 53=> d<=197 ;when 54=> d<=207 ;when 55=> d<=217 ; when 56=> d<=225 ; when 57=> d<=233 ;when 58=> d<=239 ;when 59=> d<=245 ; when 60=> d<=249 ; when 61=> d<=252 ;when 62=> d<=254 ;when 63=> d<=255 ; when others=> null;

end case;

end process;

data_out<=conv_std_logic_vector(d,8); --正弦波波形数据输出

end behav;。