16位加减计数器

- 格式:docx

- 大小:14.59 KB

- 文档页数:1

三菱FX系列PLC计数器(C)内部计数器高速计数器2016-02-03 来源:网络或本站原创FX2N系列计数器分为内部计数器和高速计数器两类。

1.内部计数器内部计数器是在执行扫描操作时对内部信号(如X、Y、M、S、T等)进行计数。

内部输入信号的接通和断开时间应比PLC的扫描周期稍长。

(1)16位增计数器(C0~C199)??共200点,其中C0~C99为通用型,C100~C199共100点为断电保持型(断电保持型即断电后能保持当前值待通电后继续计数)。

这类计数器为递加计数,应用前先对其设置一设定值,当输入信号(上升沿)个数累加到设定值时,计数器动作,其常开触点闭合、常闭触点断开。

计数器的设定值为1~32767(16位二进制),设定值除了用常数K设定外,还可间接通过指定数据寄存器设定。

下面举例说明通用型16位增计数器的工作原理。

如图1所示,X10为复位信号,当X10为ON时C0复位。

X11是计数输入,每当X11接通一次计数器当前值增加1(注意X10断开,计数器不会复位)。

当计数器计数当前值为设定值10时,计数器C0的输出触点动作,Y0被接通。

此后既使输入X11再接通,计数器的当前值也保持不变。

当复位输入X10接通时,执行RST复位指令,计数器复位,输出触点也复位,Y0被断开。

图1??通用型16位增计数器(2)32位增/减计数器(C200~C234)??共有35点32位加/减计数器,其中C200~C219(共20点)为通用型,C220~C234(共15点)为断电保持型。

这类计数器与16位增计数器除位数不同外,还在于它能通过控制实现加/减双向计数。

设定值范围均为~(32位)。

C200~C234是增计数还是减计数,分别由特殊辅助继电器M8200~M8234设定。

对应的特殊辅助继电器被置为ON时为减计数,置为OFF时为增计数。

计数器的设定值与16位计数器一样,可直接用常数K或间接用数据寄存器D的内容作为设定值。

EDA-16位加法计数器的设计北京理工大学用程序输入方法设计一个16位二进制加法计数器学院:机械xxxx学院专业班级:10机械电子工程x班姓名:陈xx学号: 10xxxxxx指导教师:xxx 老师目录摘要 (1)1 绪论 (2)2 计数器的工作原理 (3)3 设计原理 (4)4 电路系统的功能仿真 (4)6 个人小结 (23)参考文献 (24)摘要计数器是数字系统中使用较多的一种时序逻辑器件。

计数器的基本功能是统计时钟脉冲的个数,即对脉冲实现计数操作。

计数器也可以作为分频、定时、脉冲节拍产生器和脉冲序列产生器使用。

计数器的种类很多,按构成计数器中的各触发器是否使用一个时钟脉冲源来分,可分为同步计数器和异步计数器;按进位体制的不同,可分为二进制计数器、十进制计数器和任意进制计数器;按计数过程中数字增减趋势的不同,可分为加法计数器、减法计数器和可逆计数器;还有可预制数和可编计数器等等。

本次课程设计将利用众多集成电路软件软件中的Quartus II软件,使用VHDL语言编程完成论文《用程序输入方法设计一个16位二进制加法计数器》,调试结果表明,所设计的计数器正确实现了计数功能。

关键词:二进制;加法计数器;VHDL语言1 绪论现代电子设计技术的核心已日趋转向基于计算机的电子设计自动化,即EDA(Electronic Design Automation)技术。

EDA技术就是依赖功能强大的计算机,在集成电路软件平台上,对以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述手段完成的设计文件,自动完成逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

定时器工作原理通电延时型。

只要在定时的时间段内(即1分钟)定时器一直得电,则常开触电就会闭合,只要定时器不断电常开触电就会一直闭合。

定时器断电则常开触电断开101 6.1010116801图6.1定时器/计数器结构框图011011011 0265536216016553621606.2411010110104位用于T0,高4位用于T1的。

:门控位。

GATE=0,只要用软件使TR0(或TR1)置1就能启动定时器/计数器0(或定时器/计数器1);GATE=1,只有在(或)引脚为高电平的情况下,且由软件使TR0(或TR1)置1时,才能启动定时器/计数器0(或定时器/计数器1)工作。

不管GATE处于什么状态,只要TR0(或TR1)=0定时器/计数器便停止工作。

:定时器/计数器工作方式选择位。

C/=0,为定时工作方式;C/=1,为计数工作方式。

、M1:工作方式选择位,确定4种工作方式。

如表6.1所示。

表6.1定时器/计数器工作方式选择【例6.1】设置定时器1工作于方式1,定时工作方式与外部中断无关,则,M0=1,GATE=0,因此,高4位应为0001;定时器0未用,低4位可随意11(因方式3时,定时器1停止计数),一般将其设为0000。

因此,指令形式为:MOV TMOD,#10H/计数器工作方式与程序设计通过对特殊功能寄存器TMOD中的设置M1、M0两位的设置来选择四种工作/计数器0、1和2的工作方式相同,方式3的设置差别较大。

工作方式0工作方式寄存器TMOD中的M1M0为:00。

定时器/计数器T0工作在方式0 16位计数器只用了13位,即TH0的高8位和TL0的低5位,组成一个13 /计数器。

当TL0的低5位计满溢出时,向TH0进位,TH0溢出时,对TF0置位,向CPU申请中断。

定时器/计数器0方式0的逻辑结构如6.2所示。

1013121312213131310612 12130106128 192211310110136.22138103213 16.32502132130 16.401200131300819210001110000085 851 140 01011 011601 6.3121312213161610612 121601061265 53621161166.51216101032130 16.6980012162169800 16.711121610103216 111011000888821202 6.41021688812812288810612 128010612256218186.825006.56.5 6.62115001022321250050050050031130 168031021031203 6.66.923821002561001233201。

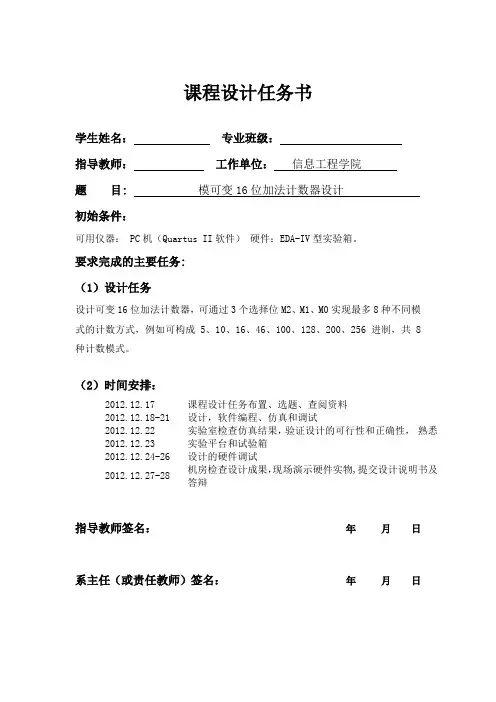

课程设计任务书学生姓名:专业班级:指导教师:工作单位:信息工程学院题目: 模可变16位加法计数器设计初始条件:可用仪器: PC机(Quartus II软件)硬件:EDA-IV型实验箱。

要求完成的主要任务:(1)设计任务设计可变16位加法计数器,可通过3个选择位M2、M1、M0实现最多8种不同模式的计数方式,例如可构成5、10、16、46、100、128、200、256进制,共8种计数模式。

(2)时间安排:2012.12.17 课程设计任务布置、选题、查阅资料2012.12.18-21 设计,软件编程、仿真和调试2012.12.22 2012.12.23 实验室检查仿真结果,验证设计的可行性和正确性,熟悉实验平台和试验箱2012.12.24-26 设计的硬件调试2012.12.27-28 机房检查设计成果,现场演示硬件实物,提交设计说明书及答辩指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要.................................... 错误!未定义书签。

Abstract (II)1 计数器的工作原理 (1)2 设计原理 (3)2.1 整体设计原理 (3)2.2 单元模块的设计 (4)2.2.1 计数模块的设计 (4)2.2.2显示模块的设计 (5)2.2.3分频模块的设计 (5)2.2.4 顶层模块的设计 (5)3 单元模块元件原理图 (6)4 电路系统的功能仿真 (8)5 硬件调试 (10)6 个人小结 (12)参考文献 (13)附录 (14)摘要计数器的种类按照计数器中的触发器是否同时翻转分类,可将计数器分为同步计数器和异步计数器两种,如果按照计数过程中数字增减分类,又可将计数器分为加法计数器、减法计数器和可逆计数器,随时钟信号不断增加的为加法计数器,不断减少的为减法计数器,可增可减的叫做可逆计数器。

计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。

16位计数器的寻址范围16位计数器是一种用于计数的电子装置,它的寻址范围决定了它可以计数的最大数值。

16位计数器可以表示的最大数值是2^16,即65536。

下面我们将围绕这个寻址范围进行详细阐述。

16位计数器的寻址范围从0到65535,一共有65536个不同的地址。

这意味着16位计数器可以表示的数值范围从0到65535。

对于一个16位计数器来说,每当它计数到最大值65535时,它会回到0重新开始计数。

这是因为计数器内部使用二进制来表示数值,当计数器计数到最大值时,再加上1就会发生溢出,导致回到0重新计数。

假设我们使用一个16位计数器来计数某个事件的发生次数,这个计数器可以记录的最大次数就是65536。

也就是说,当事件发生次数超过65536次时,计数器就会回到0重新计数。

在实际应用中,16位计数器可以被用于很多方面。

例如,它可以用于计算机中的时钟计数器,用于计算机的时钟频率;它还可以用于工业自动化中的计数任务,用于记录生产线上某个产品的生产数量;它还可以用于电子游戏中,用于记录玩家的分数等等。

无论在哪个领域使用16位计数器,其寻址范围都是0到65535。

而且,在很多实际应用场景中,这个范围已经足够大,可以满足大部分计数需求。

如果我们需要更大的计数范围,就需要使用更宽的计数器,比如32位计数器或者64位计数器。

这些计数器可以表示更大的数值范围,但同时也会占用更多的存储空间和计算资源。

总结来说,16位计数器的寻址范围是0到65535,它可以表示的最大数值是65535。

无论是在计算机领域、工业自动化还是电子游戏等应用场景中,16位计数器已经能够满足大部分计数需求。

如果需要更大的计数范围,就需要考虑使用更宽的计数器。

1、掌握16位二进制加减可控计数器的设计思想,完成设计;2、熟悉QuartusⅡ对程序进行编译、调试和仿真的过程;3、掌握VHDL语言的表达;4、该计数器含有异步清零和计数使能功能。

二、实验内容和原理1、实验内容:根据实验要求,在QuartusⅡ中从所要实现的功能出发编写实验代码,并进行编译、调试和仿真。

2、实验原理:用IF语句将加、减法计数器连接起来;以MODE作为控制信号,选择进行加法或减法运算;以RST作为异步清零信号,当RST为‘1’时将对计数器清零,即复位,这项操作是独立于CLK的,称异步;以EN作为始能信号,只有EN=1且RST无效(即RST=0),若此时有CLK信号,计数器才工作。

三、实验环境QuartusⅡ软件四、操作方法与实验步骤1、分析二进制加法、减法计数器工作原理,由此设计控制信号,使计数器可控;2、在QuartusⅡ中建立计数器工程,进行程序编写、调试、编译、仿真;3、对实验所得的时序图形进行分析。

五、实验数据记录和处理将程序进行仿真得到的波形图如下所示六、实验结果与分析:从仿真的时序图上可以看出,MODE的电平决定加操作还是减操作;RST为高电平有效,立即的将CQ置零;只有在EN为高电平且RST为低电平的情况下,CQ随着时钟上升沿的到来计数。

七、实验心得与体会通过该实验,我初步掌握了VHDL语言的基本使用方法,熟悉了QuartⅡ软件的操作流程。

八、程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY add16 ISPORT(CLK,RST,EN:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(15 DOWNTO 0);COUT:OUT STD_LOGIC;MODE:IN STD_LOGIC);END add16;ARCHITECTURE behav OF add16 ISBEGINPROCESS(CLK,RST,EN)VARIABLE CQ_IN:STD_LOGIC_VECTOR(15 DOWNTO 0);BEGINIF RST='1' THENCQ_IN:=(OTHERS=>'0');ELSIF CLK'EVENT AND CLK='1' THENIF EN='1' THENIF MODE='1' THENIF CQ_IN<65535 THENCQ_IN:=CQ_IN+1;COUT<='0';ELSE CQ_IN:=(OTHERS=>'0'); COUT<='1';END IF;ELSIF MODE='0' THENIF CQ_IN>0 THENCQ_IN:=CQ_IN-1;COUT<='0';ELSECQ_IN:=(OTHERS=>'1');COUT<='1';END IF;END IF;END IF;END IF;CQ<=CQ_IN;END PROCESS; END behav;。

课题五: FX系列PLC的编程元件【教学目的】:1、理解”软”继电器的概念2、掌握各种”软”继电器的功能使用时注意事项【教学重点】: 掌握各种”软”继电器的功能使用时注意事项【教学难点】: 理解”软”继电器的概念【课型】:新授课【课时】:4课时【讲授内容】不同厂家、不同系列的PLC,其内部软继电器的功能和编号都不相同,因此在编制程序时,必须熟悉所选用PLC的软继电器的功能和编号。

FX系列PLC软继电器编号由字母和数字组成,其中输入继电器和输出继电器用八进制数字编号,其它软继电器均采用十进制数字编号。

一、数据结构及软元件(继电器)概念1、数据结构1)十进制数2)二进制(在FX系列PLC内部,数据是以二进制(BIN)补码的形式存储,所有的四则运算都使用二进制数)。

3)八进制(输入继电器、输出继电器的地址采用八进制)4)十六进制、5)BCD码6)常数K、HK:十进制常数H:十六进制常数2、软元件(编程元件、操作数)1)软元件概念PLC内部具有一定功能的器件(输入、输出单元、存储器的存储单元)。

2)分类:位元件、字元件①位元件X:输入继电器,用于输入给PLC的物理信号;Y:输出继电器,从PLC输出的物理信号;M(辅助继电器)和S(状态继电器):PLC内部的运算标志。

说明:A、位单元只有ON和OFF两种状态,可用“0”和“1”表示。

B、元件可以通过组合使用,4个位元件为一个单元,通用表示方法是由Kn加起始的软元件号组成,n 为单元数。

例如K2 M0表示M0~M7组成两个位元件组(K2表示2个单元),它是一个8位数据,M0为最低位。

②字元件数据寄存器D:模拟量检测以及位置控制等场合存储数据和参数。

字节(BYTE)、字(WORD)、双字(DOUBLE WORD)二、FX系列PLC的编程元件(一)输入继电器(X)作用:用来接受外部输入的开关量信号。

输入端通常外接常开触点或常闭触点。

编号:X000 ~ X007 X010 ~ X017 ·说明:1)输入继电器以八进制编号。

三菱FX系列PLC计数器(C)内部计数器高速计数器2016-02-03 来源:网络或本站原创FX2N系列计数器分为内部计数器和高速计数器两类。

1.内部计数器内部计数器是在执行扫描操作时对内部信号(如X、Y、M、S、T等)进行计数。

内部输入信号的接通和断开时间应比PLC的扫描周期稍长。

(1)16位增计数器(C0~C199)共200点,其中C0~C99为通用型,C100~C199共100点为断电保持型(断电保持型即断电后能保持当前值待通电后继续计数)。

这类计数器为递加计数,应用前先对其设置一设定值,当输入信号(上升沿)个数累加到设定值时,计数器动作,其常开触点闭合、常闭触点断开。

计数器的设定值为1~32767(16位二进制),设定值除了用常数K设定外,还可间接通过指定数据寄存器设定。

下面举例说明通用型16位增计数器的工作原理。

如图1所示,X10为复位信号,当X10为ON时C0复位。

X11是计数输入,每当X11接通一次计数器当前值增加1(注意X10断开,计数器不会复位)。

当计数器计数当前值为设定值10时,计数器C0的输出触点动作,Y0被接通。

此后既使输入X11再接通,计数器的当前值也保持不变。

当复位输入X10接通时,执行RST复位指令,计数器复位,输出触点也复位,Y0被断开。

图1 通用型16位增计数器(2)32位增/减计数器(C200~C234)共有35点32位加/减计数器,其中C200~C219(共20点)为通用型,C220~C234(共15点)为断电保持型。

这类计数器与16位增计数器除位数不同外,还在于它能通过控制实现加/减双向计数。

设定值范围均为-214783648~-+214783647(32位)。

C200~C234是增计数还是减计数,分别由特殊辅助继电器M8200~M8234设定。

对应的特殊辅助继电器被置为ON时为减计数,置为OFF时为增计数。

计数器的设定值与16位计数器一样,可直接用常数K或间接用数据寄存器D的内容作为设定值。

16位计数器的寻址范围计数器是计算机中常用的一种电子元件,用于计数和记录特定事件的发生次数。

而计数器的寻址范围则表示该计数器可以表示的不同数值的范围。

在本文中,我们将探讨16位计数器的寻址范围,并解释其与计算机体系结构的关系。

一、什么是16位计数器?在计算机中,位是表示二进制数字的最小单位,每个位可以表示0或1。

16位计数器即由16个位组成,可以用来表示0到2^16-1的数值范围,也就是0到65535。

二、寻址范围是计数器可以表示的不同数值的范围。

对于16位计数器而言,它的寻址范围为0到65535,共有65536个不同的数值。

三、16位计数器的应用16位计数器的寻址范围对计算机体系结构的设计和应用有着重要的影响。

以下是一些常见的应用场景:1. 计时器:16位计数器可以用于计时器的设计,记录特定事件的发生次数。

例如,可以使用16位计数器来计算特定任务执行的时间。

2. 内存寻址:计算机内存通常被分为不同的地址,每个地址可以存储一个字节(8位)。

16位计数器的寻址范围超过了一个字节的范围,因此可以用于对内存进行寻址。

3. 程序计数器:程序计数器(PC)是计算机中用于存储下一条指令的地址的寄存器。

16位计数器可以用作程序计数器,其寻址范围可以表示存储指令的内存地址。

4. 数据传输:16位计数器可用于数据传输的控制和寻址。

例如,在串行通信中,可以使用16位计数器控制数据传输的起始和终止。

四、其他位数的计数器除了16位计数器,计算机中还常见的有其他位数的计数器。

例如,8位计数器用于表示0到255的范围,32位计数器用于表示0到2^32-1的范围。

不同位数的计数器在寻址范围和应用场景上有所不同,根据具体需要选择合适的计数器位数。

五、总结16位计数器的寻址范围为0到65535,共有65536个不同的数值。

它在计算机体系结构中有着重要的应用,可以用于计时器、内存寻址、程序计数器和数据传输等方面。

此外,根据具体需求,不同位数的计数器也有其特定的应用场景。

FX2N内部计数器16位增计数器(C0~C99)通用型3276716位增计数器(C100~C199断电保持32位增减计数器(C200~C219)通用型±21478364832位增减计数器(C220~C234断电保持高速计数器(C235~C255)单向单计数输入高速计数器(C235~C245单向双计数输入高速计数器(C246~C250高速计数器与内部计数器相比除允许输入频率高之外,应用也更为灵活,高速计数器均有断电保持功能,通过参数设定也可以变成非断电保持。

FX2N有21个高速计数器。

适合用来做高速计数器的PLC端口有X0~X7,X0~X7不能重复使用,即某一个输入端已被某个高速计数器占用,它就不能再用于其他高速计数器,也不能做它用。

其触点动作与32位增减计数器相同,可进行增或减计数。

两个输入端,一个为增计数输入,另一个为减计数输入。

双向高速计数器(C251~C255)数输入通用定时器(自复位)调用计时,为零清除100ms(T0~T199)K取值范围1~32767时间0.1~3276.7s10ms(T200~T245)K取值范围1~32767时间0.01~327.67s积算定时器(手动复位)调用计时,为零保持。

下次调用计时继续。

Rst复时间0.1~3276.7s时间0.001~32.76.s 1ms(T246~T249)100ms(T250~T255)K取值范围1~32767K取值范围1~32767。

实验一

一、实验目的

1、学会使用LPM参数化模块库进行系统设计。

2、学会器件选择及器件的引脚分配

3、了解所选器件的逻辑单元结构

二、实验内容

1、用LPM参数模块化设计方法设计一个16位的加减可控计数器

2、选择合适器件,并进行引脚分配

3、查看器件内部资源使用情况,并对引脚重新进行合理分配

三、实验步骤

1、打开QuartusII,新建一个工程addsub16

3、打开symbol tool,选择megafunctions/arichmetic下的lpm_counter,点击OK

4、修改该宏函数输出的形式及存放目录和名称

5、选择器件,输入数据位数和实现的功能

6选择器件的计数使能

7.选择清零端口

8.可加上输入输出端口

9.选择具体器件

10.进行引脚分配(如果引脚自动分配,可直接进行综合编译)

11.查看器件内部逻辑单元使用情况

12.内部资源调整

13.内部资源调整后重新综合

14.功能仿真达到预期结果。