数电实验报告 实验二 利用MSI设计组合逻辑电路

- 格式:doc

- 大小:3.64 MB

- 文档页数:10

装……订……线组合逻辑电路设计一、实验目的1、掌握用基本门电路实现组合电路的设计方法。

2、掌握实现组合电路的连接及调试方法。

通过功能验证锻炼解决实际问题的能力。

二、实验内容(一)概论设计电路的一般过程:实际逻辑问题→抽象逻辑问题→列真值表→画卡诺图→图形化简→简化表达式→画出逻辑图设计中应该注意的问题:卡诺图或公式化简是实现组合电路设计的关键步骤。

为使电路简单,使用器件最少,往往要对不同的化简方法进行比较,得到一个合理的电路。

对于多输出实现组合电路,为了使得总的逻辑电路最简,在各个输出函数化简时不能孤立地考虑各个输出函数如何化简,而应注意尽可能找出多个输出函数的同类项,使总体设计最简。

(二)实践实验题目实验要求:从实验内容所列的题目中选择一个题目进行设计,设计方法和方案不限。

要求首先进行计算机仿真,实现题目功能。

然后在数字实验系统中完成实际操作。

自行设计测试表格,完成实际电路的测试。

(三)实验设计(1)设计一个四人表决电路要求:四人表决(用电平开关表决,当开关为高电平时表示同意,当开关为低电平时表示反对)时,当多数人通过时(三个以上开关为高电平)用发光二极管显示有效,否则发光二极管显示无效。

试用基本逻辑门设计该电路。

具体电路形式不限。

并在实验台上进行调试及验证。

(2)器材:数字试验系统一台,TTL型集成电路与门74LS11,或门74LS32各一块。

(3)电路设计过程根据设计任务要求建立输入、输出变量,并列出真值表:A、B、C、D为表决输入信号,Q为输出显示信号。

装……订……线三、实验步骤1、选好芯片,并连线布线图2、测试结果真值表根据真值表写出逻辑表达式Q=ABCD+ ABC’D+AB’CD+A’BCD+ABCD=ABC+ABD+ACD+BCD′用逻辑表达式化简法简化逻辑表达式Q=ABC+ABD+ACD+BCD=AB(C+D)+CD(A+B)=ABC′D′+A′B′CD四、实验总结本次实验总体效果较为满意,通过做表决器实验,了解到了芯片的用途,与书本相结合。

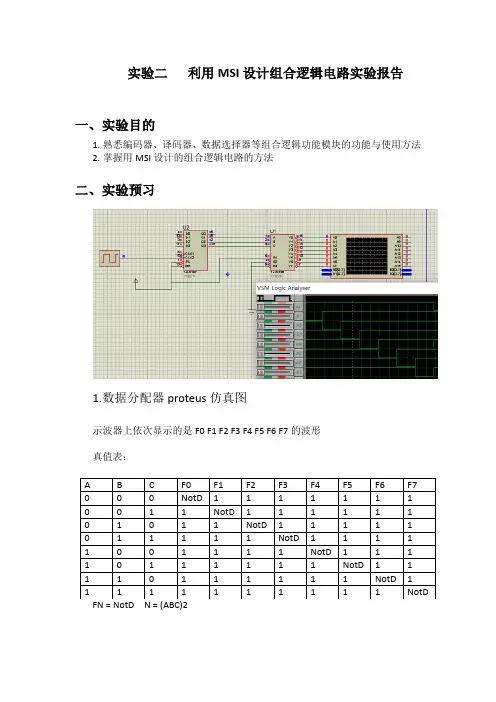

实验二利用 MSI 设计组合逻辑电路实验报告一、实验目的1. 熟悉编码器、译码器、数据选择器等组合逻辑功能模块的功能与使用方法 2. 掌握用 MSI 设计的组合逻辑电路的方法二、实验预习1.数据分配器 proteus 仿真图示波器上依次显示的是 F0 F1 F2 F3 F4 F5 F6 F7 的波形 真值表: A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 FN = NotD C F0 0 NotD 1 1 0 1 1 1 0 1 1 1 0 1 1 1 N = (ABC)2 F1 1 NotD 1 1 1 1 1 1 F2 1 1 NotD 1 1 1 1 1 F3 1 1 1 NotD 1 1 1 1 F4 1 1 1 1 NotD 1 1 1 F5 1 1 1 1 1 NotD 1 1 F6 1 1 1 1 1 1 NotD 1 F7 1 1 1 1 1 1 1 NotD2.LU 逻辑单元 proteus 仿真图通过示波器观察 Q0 Q1 Q2 Q3 和 Y 的波形 真值表: S1 S1 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 S0 S0 0 0 1 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Y A A*B 0 A+B 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 B 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Y 0 0 1 1 0 1 1 1 0 1 1 0 1 1 0 01 10 1A 异或 B NotA3.AU 算术单元设计真值表如下: S 0 0 0 0 1 1 1 1A 0 0 1 1 0 0 1 1B 0 1 0 1 0 1 0 1输出 Y 0 1 1 0 0 1 1 0进/借位 Cn 0 0 0 1 0 1 0 0卡诺图化简如下:根据卡诺图化简所得, 在 Proteus 上进行仿真模拟① 利用卡诺图化简后只使用门电路实现:② 使用 74LS138 实现:③ 使用 74LS151 实现:4.ALU 算术逻辑单元S2 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1S1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0S0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0A 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1C 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1Y 0 0 0 0 0 0 1 1 0 0 1 1 1 1 1 1 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 0 0 1 1 1 1 0 0Cn10100000 0 0 1 0 1 1 1 0 1 1 1 0 0 0 1 0 0 0 0 0 0 0 01 0 1 0 0 1 1 1 0 1 0 1 0 1 1 0 1 0 1 1 0 1 0 1 1 0 0 1 1 0 1 1 0 1 0 1 0 1 1 1 0 0 1 0 1 1 1 1 1 1 1 0 0 0 0 0 1 1 0 0 0 1 1 1 1 0 0 1 0 1 1 1 0 0 1 1 0 1 1 0 1 0 0 1 1 1 0 1 0 1 0 1 1 0 1 1 0 0 1 1 0 1 1 1 1 1 1 1 0 0 0 0 1 1 1 0 0 1 0 1 1 1 0 1 0 0 1 1 1 0 1 1 0 1 1 1 1 0 0 0 1 1 1 1 0 1 0 1 1 1 1 1 0 0 1 1 1 1 1 1 0 真值表如上 S2、S1、S0 为 0 0 0 时 Y=AB S2、S1、S0 为 0 0 1 时 Y=A+B S2、S1、S0 为 0 1 0 时 Y=NotA S2、S1、S0 为 0 1 1 时 Y=NotB S2、S1、S0 为 1 0 0 时 Y=A⊕B S2、S1、S0 为 1 1 1 时 Y=0 当 S2、S1、S0 分别为 101 和 110 时,利用卡诺图化简如下: S2、S1、S0 为 101 时:S2、S1、S0 为 110 时:根据真值表和卡诺图,在 proteus 上进行仿真模拟如下:S2、S1、S0 的控制,通过此处的导线接法改变来控制三、实验原理中规模的器件,如译码器、数据选择器等,它们本身是为实现某种逻辑功能 而设计的,但由于它们的一些特点,我们也可以用它们来实现任意逻辑函数四、实验内容1.数据分配器:波形图如下: (从上到下依次为 clock、 C、B、A、F0、F1、F2、F3、F4、 F5、F6、F7 的波形)clock C B A F0 F1 F2 F3 F4 F5 F6 F7此时 A B C 为 0 0 0 F0 = 0 此时 A B C 为 0 0 1 F1 = 0 .。

msi组合逻辑电路的设计实验报告MSI组合逻辑电路的设计实验报告引言:在现代电子技术中,组合逻辑电路被广泛应用于各种数字系统中,如计算机、通信设备等。

MSI(Medium Scale Integration)组合逻辑电路是一种集成度适中的电路,具有较高的可靠性和性能。

本实验旨在通过设计和实现MSI组合逻辑电路,加深对数字电路设计原理的理解,并掌握实际电路的搭建和测试技巧。

实验目的:1. 理解MSI组合逻辑电路的基本原理和设计方法;2. 学会使用逻辑门、多路选择器、译码器等基本元件进行电路设计;3. 掌握数字电路的搭建和测试技巧;4. 分析电路的功能和性能,并提出改进方案。

实验内容:本实验分为两个部分,分别是设计一个4位全加器和一个4位比较器。

1. 4位全加器设计:全加器是一种常见的组合逻辑电路,用于实现两个二进制数的加法运算。

通过使用逻辑门和多路选择器,可以设计一个4位全加器电路。

首先,根据全加器的真值表,使用逻辑门设计出每一位的和与进位输出。

然后,使用多路选择器将每一位的进位输出与前一位的进位输入相连接,形成级联的全加器电路。

接下来,根据设计的电路原理图,使用数字电路实验箱搭建电路,并连接输入输出信号。

对电路进行测试,验证其功能和性能。

2. 4位比较器设计:比较器是一种用于比较两个二进制数大小的组合逻辑电路。

通过使用译码器和逻辑门,可以设计一个4位比较器电路。

首先,根据比较器的真值表,使用译码器将两个4位二进制数进行解码,得到各位的比较结果。

然后,使用逻辑门将各位的比较结果进行逻辑运算,得到最终的比较结果。

接下来,根据设计的电路原理图,使用数字电路实验箱搭建电路,并连接输入输出信号。

对电路进行测试,验证其功能和性能。

实验结果与分析:通过实验,我们成功设计并实现了4位全加器和4位比较器电路。

经过测试,电路在各种输入情况下均能正常工作,输出结果与预期一致。

然而,我们也发现了一些问题。

首先,电路的延迟时间较长,导致输出信号的响应稍有延迟。

msi组合逻辑电路的设计实验报告Title: Design Experiment Report of MSI Combinational Logic CircuitIntroductionIn the field of digital electronics, MSI (Medium Scale Integration) combinational logic circuits play a crucial role in performing various logical operations. These circuits are designed using basic logic gates such as AND, OR, and NOT gates to create complex logical functions. In this experiment, we aimed to design and implement an MSI combinational logic circuit using basic logic gates and analyze its functionality.Design and ImplementationThe first step in the experiment was to identify the logical function that the MSI combinational logic circuit needed to perform. Based on the given requirements, we selected the appropriate combination of basic logic gates to implement the desired function. The circuit was then designed using a combination of AND, OR, and NOT gates to achieve the desired logical operation.Once the circuit design was finalized, the next step was to implement it on a breadboard using standard logic ICs. The connections were carefully made according to the circuit diagram, and the inputs and outputs were verified to ensure proper functionality. The circuit was then powered up, and the inputs were varied to observe the corresponding outputs.Analysis and ResultsUpon testing the MSI combinational logic circuit, we observed that it accuratelyperformed the desired logical function. The inputs were processed through the circuit, and the outputs were generated as expected based on the logic gates' configuration. The circuit demonstrated the principles of Boolean algebra and logic gates in action, showcasing the power of digital logic in processing binary information.Furthermore, the experiment allowed us to gain insights into the behavior of MSI combinational logic circuits and their applications in digital systems. We also learned about the importance of proper circuit design and implementation techniques to ensure reliable operation.ConclusionIn conclusion, the design and implementation of an MSI combinational logic circuit proved to be a valuable learning experience in the field of digital electronics. The experiment provided hands-on experience in creating complex logical functions using basic logic gates and understanding the principles of digital logic design. The successful operation of the circuit demonstrated the practical application of MSI combinational logic circuits in real-world digital systems. Overall, the experiment enhanced our understanding of digital logic and its significance in modern technology.。

竭诚为您提供优质文档/双击可除组合逻辑电路的设计实验报告篇一:数电实验报告实验二组合逻辑电路的设计实验二组合逻辑电路的设计一、实验目的1.掌握组合逻辑电路的设计方法及功能测试方法。

2.熟悉组合电路的特点。

二、实验仪器及材料a)TDs-4数电实验箱、双踪示波器、数字万用表。

b)参考元件:74Ls86、74Ls00。

三、预习要求及思考题1.预习要求:1)所用中规模集成组件的功能、外部引线排列及使用方法。

2)组合逻辑电路的功能特点和结构特点.3)中规模集成组件一般分析及设计方法.4)用multisim软件对实验进行仿真并分析实验是否成功。

2.思考题在进行组合逻辑电路设计时,什么是最佳设计方案?四、实验原理1.本实验所用到的集成电路的引脚功能图见附录2.用集成电路进行组合逻辑电路设计的一般步骤是:1)根据设计要求,定义输入逻辑变量和输出逻辑变量,然后列出真值表;2)利用卡络图或公式法得出最简逻辑表达式,并根据设计要求所指定的门电路或选定的门电路,将最简逻辑表达式变换为与所指定门电路相应的形式;3)画出逻辑图;4)用逻辑门或组件构成实际电路,最后测试验证其逻辑功能。

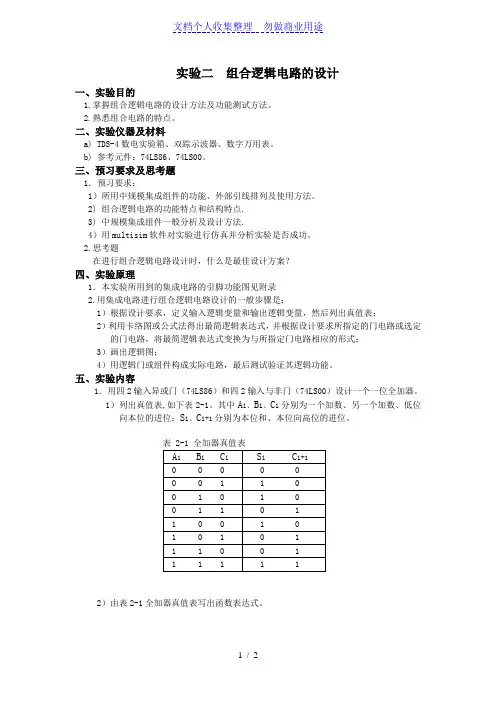

五、实验内容1.用四2输入异或门(74Ls86)和四2输入与非门(74Ls00)设计一个一位全加器。

1)列出真值表,如下表2-1。

其中Ai、bi、ci分别为一个加数、另一个加数、低位向本位的进位;si、ci+1分别为本位和、本位向高位的进位。

2)由表2-1全加器真值表写出函数表达式。

3)将上面两逻辑表达式转换为能用四2输入异或门(74Ls86)和四2输入与非门(74Ls00)实现的表达式。

4)画出逻辑电路图如图2-1,并在图中标明芯片引脚号。

按图选择需要的集成块及门电路连线,将Ai、bi、ci接逻辑开关,输出si、ci+1接发光二极管。

改变输入信号的状态验证真值表。

2.在一个射击游戏中,每人可打三枪,一枪打鸟(A),一枪打鸡(b),一枪打兔子(c)。

实验二组合逻辑电路的设计一、实验目的1.掌握组合逻辑电路的设计方法及功能测试方法。

2.熟悉组合电路的特点。

二、实验仪器及材料a) TDS-4数电实验箱、双踪示波器、数字万用表。

b) 参考元件:74LS86、74LS00。

三、预习要求及思考题1.预习要求:1)所用中规模集成组件的功能、外部引线排列及使用方法。

2) 组合逻辑电路的功能特点和结构特点.3) 中规模集成组件一般分析及设计方法.4)用multisim软件对实验进行仿真并分析实验是否成功。

2.思考题在进行组合逻辑电路设计时,什么是最佳设计方案?四、实验原理1.本实验所用到的集成电路的引脚功能图见附录2.用集成电路进行组合逻辑电路设计的一般步骤是:1)根据设计要求,定义输入逻辑变量和输出逻辑变量,然后列出真值表;2)利用卡络图或公式法得出最简逻辑表达式,并根据设计要求所指定的门电路或选定的门电路,将最简逻辑表达式变换为与所指定门电路相应的形式;3)画出逻辑图;4)用逻辑门或组件构成实际电路,最后测试验证其逻辑功能。

五、实验内容1.用四2输入异或门(74LS86)和四2输入与非门(74LS00)设计一个一位全加器。

1)列出真值表,如下表2-1。

其中A i、B i、C i分别为一个加数、另一个加数、低位向本位的进位;S i、C i+1分别为本位和、本位向高位的进位。

2)由表2-1全加器真值表写出函数表达式。

3)将上面两逻辑表达式转换为能用四2输入异或门(74LS86)和四2输入与非门(74LS00)实现的表达式。

4)画出逻辑电路图如图2-1,并在图中标明芯片引脚号。

按图选择需要的集成块及门电路连线,将A i、B i、C i接逻辑开关,输出Si、Ci+1接发光二极管。

改变输入信号的状态验证真值表。

2.在一个射击游戏中,每人可打三枪,一枪打鸟(A),一枪打鸡(B),一枪打兔子(C)。

规则是:打中两枪并且其中有一枪必须是打中鸟者得奖(Z)。

试用与非门设计判断得奖的电路。

msi组合逻辑电路实验报告MSI组合逻辑电路实验报告引言组合逻辑电路是现代电子技术中的重要组成部分,它由多个逻辑门组成,能够根据输入信号的不同组合产生相应的输出信号。

本次实验旨在通过搭建MSI (Medium Scale Integration)组合逻辑电路,探索其工作原理和应用。

实验背景MSI组合逻辑电路是一种将多个逻辑门集成在一起的电路,常见的MSI芯片有译码器、编码器、多路选择器等。

这些芯片在数字电路设计和计算机体系结构中扮演着重要的角色。

通过实验,我们将深入了解MSI组合逻辑电路的内部结构和功能。

实验目的1. 熟悉MSI组合逻辑电路的基本原理和工作方式;2. 学会使用逻辑门芯片搭建MSI组合逻辑电路;3. 掌握MSI组合逻辑电路在实际应用中的使用方法。

实验步骤1. 准备实验器材和材料:逻辑门芯片、电路板、导线等;2. 根据实验要求,选择适当的逻辑门芯片,并将其插入电路板上的对应位置;3. 按照电路图连接逻辑门芯片之间的输入和输出引脚;4. 检查电路连接是否正确,并确保没有短路或接触不良的情况;5. 接通电源,观察和记录电路的输出结果;6. 根据实验要求,对电路进行调试和优化,确保其正常工作。

实验结果与分析通过实验,我们成功搭建了MSI组合逻辑电路,并观察到了其在不同输入组合下产生的输出结果。

通过对实验数据的分析,我们可以得出以下结论:1. MSI组合逻辑电路具有灵活性和可扩展性。

通过简单的连接和配置,我们可以实现不同的逻辑功能,满足不同的应用需求。

2. MSI组合逻辑电路的性能受到逻辑门芯片的质量和参数的影响。

选择合适的逻辑门芯片对电路的性能和稳定性具有重要意义。

3. 调试和优化是搭建MSI组合逻辑电路的关键步骤。

在实验过程中,我们发现一些连接错误和电路故障,通过仔细检查和调整,最终使电路正常工作。

实验应用MSI组合逻辑电路在实际应用中具有广泛的应用场景,以下是一些常见的应用案例:1. 译码器:将输入的二进制信号转换为对应的输出信号,用于解码和控制信号的生成。

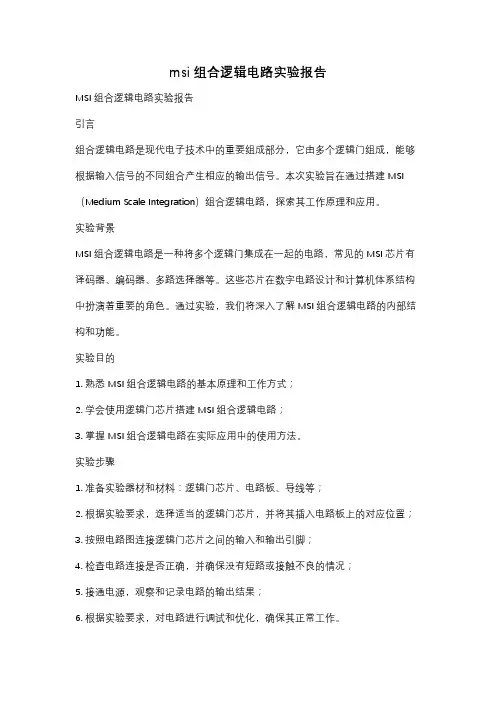

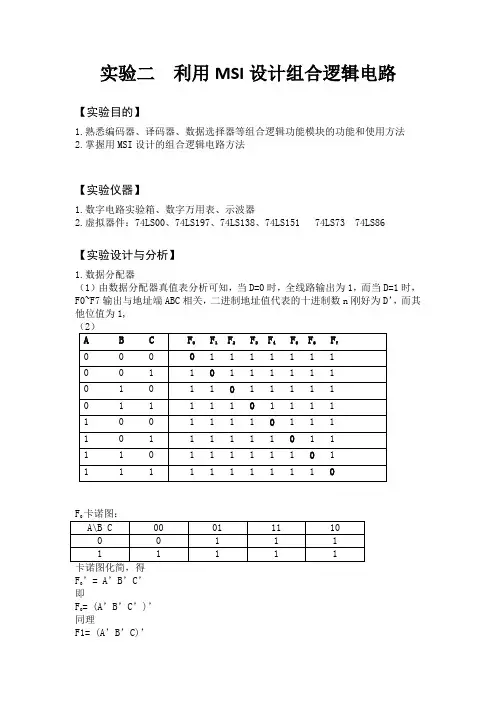

实验二利用MSI设计组合逻辑电路【实验目的】1.熟悉编码器、译码器、数据选择器等组合逻辑功能模块的功能和使用方法2.掌握用MSI设计的组合逻辑电路方法【实验仪器】1.数字电路实验箱、数字万用表、示波器2.虚拟器件:74LS00、74LS197、74LS138、74LS151 74LS73 74LS86【实验设计与分析】1.数据分配器(1)由数据分配器真值表分析可知,当D=0时,全线路输出为1,而当D=1时,F0~F7输出与地址端ABC相关,二进制地址值代表的十进制数n刚好为D’,而其他位值为1,’= A’B’C’F即F= (A’B’C’)’同理F1= (A’B’C)’F3= (A’BC)’F4= (A B’C’)’F5= (AB’C)’F6= (ABC’)’F7= (ABC)’Y O = GsS2’S1’S’即Y 0’= (Gs’S2’S1’S’)’同理Y 1’= (Gs’S2’S1’S)’Y 3’= (Gs’S2’S1S)’Y 4’= (Gs’S2S1’S’)’Y 5’=(Gs’S2S1’S)’Y 6’= (Gs’S2S1S’)’Y 7’= (Gs’S2S1S)’显然当Gs=1时, Y’= F(3)对比(2)中不同Gs条件下译码器和数据分配器的真值表可以发现,当另Gs’与数据输入D信号一致,S2~S0作为地址段输入的A B C,两者真值表一致,即使译码器变成了数据分配器。

Gs输入端有3端,令G1为数据D输入,其他两端接低电平。

(4)电路设计(5)仿真波形2.LU(Logic Unit逻辑单元)设计(1)分析LU功能,得出如下真值表利用74LS151实现数据选择,那么无需计算逻辑表达式,无需卡诺图化简(2)16行真值化简为8行真值若用2组74LS151,可联合成16路输出,若只用1组74LS151,则需要把Y的值与其中一个输入变量联合起来12351X 0=X4=S1X6=X7=S1’故简化成了设计(3)根据(1)&(2)的真值表分析,可以发现有4组输入变量,1组输出变量,其中s1通过把数据输入端的值与S1关联而简化,故利用3组变量实现了16组输出结果。

数电实验报告实验二利用MSI设计组合逻辑电路一、实验目的1. 学习MSI(Medium Scale Integration,即中规模集成电路)的基本概念和应用。

2.掌握使用MSI设计和实现组合逻辑电路的方法。

3.了解MSI的类型、特点及其在实际电路设计中的作用。

二、实验设备与器件1.实验设备:示波器、信号发生器、万用表。

2.实验器件:组合逻辑集成电路74LS151三、实验原理1.MSI的概念MSI是Medium Scale Integration的简称,指的是中规模集成电路。

MSI由几十个至几千个门电路组成,功能比SSI(Small Scale Integration,即小规模集成电路)更为复杂,但比LSI(Large Scale Integration,即大规模集成电路)简单。

2.74LS151介绍74LS151是一种常用的组合逻辑集成电路之一,具有8个输入端和1个输出端。

其功能是从八个输入信号中选择一个作为输出。

利用该器件可以轻松实现数据选择器、多路选择器等功能。

四、实验内容本实验的任务是利用74LS151设计一个简单的多路选择器电路。

具体实验步骤如下:1.将74LS151插入实验板中,注意引脚的正确连接。

2.将信号发生器的输出接入到74LS151的A、B、C三个输入端中,分别作为输入0、输入1、输入2、将示波器的探头分别接到74LS151的输出端Y,记录下不同输入情况下Y的输出情况。

3.分别将信号发生器的输出接入74LS151的D0、D1、D2、D3、D4、D5、D6、D7八个输入端,接通电源,记录下不同输入情况下Y的输出情况。

4.通过以上实验数据,绘制74LS151的真值表。

五、实验结果与数据处理根据实验步骤所述,我们完成了实验,并得到了以下数据:输入0:0000001111001111输入1:1111110010100101输入2:1010101001010101根据这些数据,我们可以绘制74LS151的真值表如下:输入0,输入1,输入2,输出Y--------,--------,--------,--------0,0,0,00,0,1,10,1,0,00,1,1,11,0,0,11,0,1,01,1,0,11,1,1,1六、实验总结通过本次实验,我们学习了MSI的基本概念和应用,初步掌握了使用MSI设计和实现组合逻辑电路的方法。

实验二 组合逻辑电路一、实验目的1、熟悉组合逻辑电路的一些特点及一般分析、设计方法。

2、熟悉中规模集成电路典型的基本逻辑功能和简单应用设计。

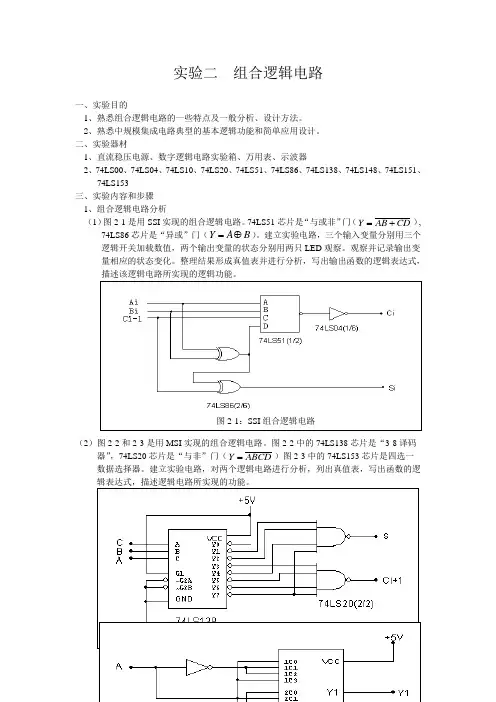

二、实验器材1、直流稳压电源、数字逻辑电路实验箱、万用表、示波器2、74LS00、74LS04、74LS10、74LS20、74LS51、74LS86、74LS138、74LS148、74LS151、 74LS153三、实验内容和步骤 1、组合逻辑电路分析(1)图2-1是用SSI 实现的组合逻辑电路。

74LS51芯片是“与或非”门(CD AB Y +=), 74LS86芯片是“异或”门(B A Y ⊕=)。

建立实验电路,三个输入变量分别用三个 逻辑开关加载数值,两个输出变量的状态分别用两只LED 观察。

观察并记录输出变 量相应的状态变化。

整理结果形成真值表并进行分析,写出输出函数的逻辑表达式, 描述该逻辑电路所实现的逻辑功能。

(2)图2-2和2-3是用MSI 实现的组合逻辑电路。

图2-2中的74LS138芯片是“3-8译码 器”,74LS20芯片是“与非”门(ABCD Y =)图2-3中的74LS153芯片是四选一 数据选择器。

建立实验电路,对两个逻辑电路进行分析,列出真值表,写出函数的逻 辑表达式,描述逻辑电路所实现的功能。

图2-1:SSI 组合逻辑电路图2-2 :MSI 组合逻辑电路(74LS138)2、组合逻辑电路设计(1)SSI 逻辑门电路设计——裁判表决电路举重比赛有三名裁判:一个主裁判A 、两个副裁判B 和C 。

在杠铃是否完全举起裁 决中,最终结果取决于至少两名裁判的裁决,其中必须要有主裁判。

如果最终的裁决 为杠铃举起成功,则输出“有效”指示灯亮,否则杠铃举起失败。

(2)MSI 逻辑器件设计——路灯控制电路用74LS151芯片和逻辑门,设计一个路灯控制电路,要求能够在四个不同的地方都 能任意的开灯和关灯。

四、实验结果、电路分析及电路设计方案1、组合逻辑电路分析 (1)图2-1: 逻辑表达式:)()(11i i i i i i i i i i B A C S B A C B A C ⊕⊕=⊕+=--逻辑功能:实现A i 、B i 、C i-1三个一位二进制数 的加法运算功能,即全加器。

数电实验报告实验二利用MSI设计组合逻辑电路:学号:班级:院系:指导老师:2016年目录实验目的: (2)实验器件与仪器: (2)实验原理: (3)实验内容: (5)实验过程: (6)实验总结: (10)实验:实验目的:1.熟悉编码器、译码器、数据选择器等组合逻辑功能模块的功能与使用方法。

2.掌握用MSI设计的组合逻辑电路的方法。

实验器件与仪器:1.数字电路实验箱、数字万用表、示波器。

2.虚拟器件:74LS00,74LS197,74LS138,74LS151实验原理:中规模的器件,如译码器、数据选择器等,它们本身是为实现某种逻辑功能而设计的,但由于它们的一些特点,我们也可以用它们来实现任意逻辑函数。

1.用译码器实现组合逻辑电路译码器是将每个输入的二进制代码译成对应的输出高、低电平信号。

如3线-8线译码器。

当附加控制门Gs的输入为高电平(S = 1)的时候,可由逻辑图写出。

从上式可看出。

-同时又是S2、S1、S0这三个变量的全部最小项的译码输出。

所以这种译码器也叫最小项译码器。

如果将S2、S1、S0当作逻辑函数的输入变量,则可利用附加的门电路将这些最小项适当的组合起来,便可产生任何形式的三变量组合逻辑函数。

2.用逻辑选择器实现组合逻辑电路数据选择器的功能是从一组输入数据中选出某一个信号输出。

或称为多路开关。

如双四选一数据选择器74LS153Y1和Y2为两个独立的输出端,和为附加控制端用于控制电路工作状态和扩展功能。

A1、A0为地址输入端。

D10、D11、D12、D13或D20、D21、D22、D23为数据输入端。

通过选定不同的地址代码即可从4个数据输入端选出要的一个,并送到输出端Y。

输出逻辑式可写成其简化真值表如下表所示。

S1 A1 A0 Y11 X X 00 0 0 D100 0 1 D110 1 0 D120 1 1 D13从上述可知,如果将A1A0作为两个输入变量,同时令D10、D11、D12、D13为第三个输入变量的适当状态(包括原变量、反变量、0和1),就可以在数据选择器的输出端产生任何形式的三变量组合逻辑电路。

利用MSI设计组合逻辑电路实验报告一、实验目的1、掌握时序电路的设计2、熟练运用JK触发器二、实验仪器及器件1. 数字电路实验箱、数字万用表、示波器。

2. 器件:74LS48,74LS197,74LS153,各种逻辑门三、实验内容内容一:1、问题描述(1)利用JK触发器,设计具备完整功能74LS197的模块电路(2)设计测试系统,能够比较74LS197芯片与自行设计的模块电路具备完全相同的功能2、设计分析(1)关于74LS197MR 是异步清零端;PL是计数和置数控制端;CLK1和CLK2是两组时钟脉冲输入端。

D0~D3 是并行输入数据端;Q0~Q3是计数器状态输出端。

74LS197 具有以下功能:A、清零功能当 MR=0 时,计数器异步清零。

B、置数功能当 MR=1,PL=0,计数器异步置数,预置功能,Q0-Q3与D0-D3一致。

C、PL=MR=1,clock由CLK1输入,CLK2与Q0相连,得到二、四、八、十六分频。

(2)JK触发器本实验中仅使用JK状态相同的情况,即保持和计数翻转。

(3)74ls197中的CLK1和CLK2分别对应于两个JK触发器中的CLK,另外另个JK触发器的CLK与JK触发的Q级联。

3、逻辑图4、比较测试(1)MR为0时,不管CLK1/CLK2如何,均清零。

测试程序如下:波形结果如下:如图中所示,黄色部分为74ls197波形图,蓝色为模块电路波形图。

两波形图一致,输出均为低电平,验证正确。

(2)MR=1,PL=0,并行送数状态,Q与对应D一致测试程序如下:波形结果如下:(3)PL=MR=1,clock由CLK1输入,CLK2与Q0相连,得到二、四、八、十六分频。

测试程序如下:波形结果如下:如图中所示,黄色部分为74ls197波形图,蓝色为模块电路波形图。

两波形图一致,输出均为16进制计数,验证正确。

内容二:1、问题描述(1)利用JK触发器,设计具备完整功能74LS194的模块电路(2)设计测试系统,能够比较74LS194芯片与自行设计的模块电路具备完全相同的功能。

组合逻辑电路的设计实验报告一、实验目的组合逻辑电路是数字电路中较为基础且重要的部分。

本次实验的主要目的是通过设计和实现简单的组合逻辑电路,深入理解组合逻辑电路的工作原理和设计方法,掌握逻辑门的运用,提高逻辑分析和问题解决的能力。

二、实验原理组合逻辑电路是指在任何时刻,输出状态只取决于同一时刻输入信号的组合,而与电路以前的状态无关。

其基本组成单元是逻辑门,如与门、或门、非门等。

通过将这些逻辑门按照一定的逻辑关系连接起来,可以实现各种不同的逻辑功能。

例如,一个简单的 2 输入与门,只有当两个输入都为 1 时,输出才为 1;而 2 输入或门,只要有一个输入为 1,输出就为 1。

组合逻辑电路的设计方法通常包括以下几个步骤:1、分析问题,确定输入和输出变量,并定义其逻辑状态。

2、根据问题的逻辑关系,列出真值表。

3、根据真值表,写出逻辑表达式。

4、对逻辑表达式进行化简和变换,以得到最简的表达式。

5、根据最简表达式,选择合适的逻辑门,画出逻辑电路图。

三、实验设备与器材1、数字电路实验箱2、集成电路芯片:74LS00(四 2 输入与非门)、74LS04(六反相器)、74LS08(四 2 输入与门)、74LS32(四 2 输入或门)等。

3、导线若干四、实验内容与步骤(一)设计一个一位全加器1、分析问题一位全加器有三个输入变量 A、B 和 Cin(低位进位),两个输出变量 S(和)和 Cout(进位输出)。

2、列出真值表| A | B | Cin | S | Cout |||||||| 0 | 0 | 0 | 0 | 0 || 0 | 0 | 1 | 1 | 0 || 0 | 1 | 0 | 1 | 0 || 0 | 1 | 1 | 0 | 1 || 1 | 0 | 0 | 1 | 0 || 1 | 0 | 1 | 0 | 1 || 1 | 1 | 0 | 0 | 1 || 1 | 1 | 1 | 1 | 1 |3、写出逻辑表达式S = A⊕B⊕CinCout = AB +(A⊕B)Cin4、化简逻辑表达式S = A⊕B⊕Cin 已最简Cout = AB +(A⊕B)Cin = AB + ACin + BCin5、画出逻辑电路图使用 74LS00、74LS08 和 74LS32 芯片实现,连接电路如图所示。

msi组合逻辑电路实验报告Title: Experimental Report on MSI Combinational Logic CircuitsIntroductionIn this experiment, we explored the design and implementation of MSI (Medium Scale Integration) combinational logic circuits. These circuits are essential components in digital systems, performing logical operations on input signals to produce output signals. The purpose of this experiment was to gain a better understanding of the principles and applications of MSI combinational logic circuits.Experimental SetupThe experimental setup consisted of various MSI components such as multiplexers, decoders, encoders, and adders. These components were interconnected using breadboards and wires to create different combinational logic circuits. The input signals were generated using switches, and the output signals were observed using LEDs.Experiment 1: MultiplexerThe first part of the experiment involved the construction of a 4-to-1 multiplexer using MSI components. The multiplexer circuit was designed to select one of the four input signals based on the control inputs and output it as the final signal. By varying the control inputs, we were able to observe the different output signals and understand the functioning of the multiplexer. Experiment 2: DecoderNext, we constructed a 3-to-8 decoder using MSI components. The decoder circuit was designed to convert a 3-bit binary input into one of the eight output signals. By inputting different binary combinations, we were able to observe the corresponding output signals and understand the decoding process. Experiment 3: EncoderIn the third part of the experiment, we built a priority encoder using MSI components. The encoder circuit was designed to encode multiple input signals into a single output signal based on their priority. By changing the input signals, we were able to observe the encoding process and understand how priority encoders work.Experiment 4: AdderFinally, we constructed a 4-bit adder using MSI components. The adder circuit was designed to perform binary addition on two 4-bit inputs and produce a 4-bit sum along with a carry output. By inputting different binary numbers, we were able to observe the addition process and understand the functioning of the adder circuit.ConclusionIn conclusion, this experiment provided valuable insights into the design and implementation of MSI combinational logic circuits. By constructing and observing the behavior of multiplexers, decoders, encoders, and adders, we gained a better understanding of their principles and applications in digital systems. This hands-on experience will be beneficial for our future studies andcareers in the field of digital electronics.。

第1篇一、实验目的1. 理解和掌握数字电路的基本原理和组成。

2. 熟悉数字电路实验设备和仪器的基本操作。

3. 培养实际动手能力和解决问题的能力。

4. 提高对数字电路设计和调试的实践能力。

二、实验器材1. 数字电路实验箱一台2. 74LS00若干3. 74LS74若干4. 74LS138若干5. 74LS20若干6. 74LS32若干7. 电阻、电容、二极管等元器件若干8. 万用表、示波器等实验仪器三、实验内容1. 基本门电路实验(1)验证与非门、或非门、异或门等基本逻辑门的功能。

(2)设计简单的组合逻辑电路,如全加器、译码器等。

2. 触发器实验(1)验证D触发器、JK触发器、T触发器等基本触发器的功能。

(2)设计简单的时序逻辑电路,如计数器、分频器等。

3. 组合逻辑电路实验(1)设计一个简单的组合逻辑电路,如4位二进制加法器。

(2)分析电路的输入输出关系,验证电路的正确性。

4. 时序逻辑电路实验(1)设计一个简单的时序逻辑电路,如3位二进制计数器。

(2)分析电路的输入输出关系,验证电路的正确性。

5. 数字电路仿真实验(1)利用Multisim等仿真软件,设计并仿真上述实验电路。

(2)对比实际实验结果和仿真结果,分析误差原因。

四、实验步骤1. 实验前准备(1)熟悉实验内容和要求。

(2)了解实验器材的性能和操作方法。

(3)准备好实验报告所需的表格和图纸。

2. 基本门电路实验(1)搭建与非门、或非门、异或门等基本逻辑电路。

(2)使用万用表测试电路的输入输出关系,验证电路的功能。

(3)记录实验数据,分析实验结果。

3. 触发器实验(1)搭建D触发器、JK触发器、T触发器等基本触发电路。

(2)使用示波器观察触发器的输出波形,验证电路的功能。

(3)记录实验数据,分析实验结果。

4. 组合逻辑电路实验(1)设计4位二进制加法器电路。

(2)搭建电路,使用万用表测试电路的输入输出关系,验证电路的正确性。

(3)记录实验数据,分析实验结果。