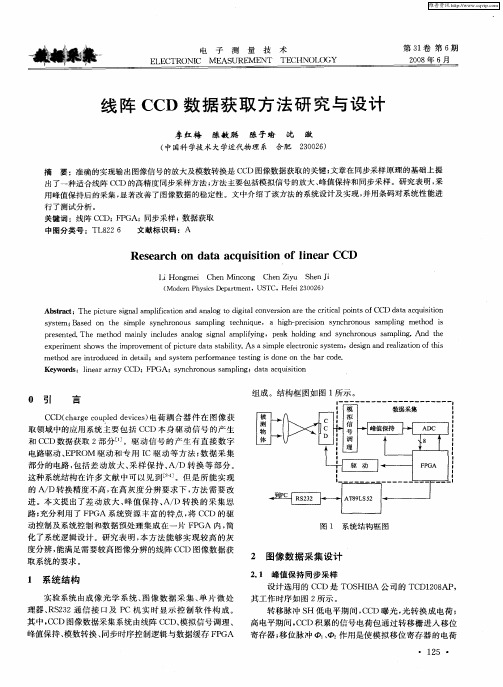

线阵CCD信号采集与处理系统研究

- 格式:pdf

- 大小:187.15 KB

- 文档页数:4

基于TMS320C6711的线阵CCD采集与处理系统基于TMS320C6711的线阵CCD采集与处理系统摘要:一种基于DSP的CCD采集与处理系统。

在该系统中DSP (TMS320C6711)进行高速、大数据量的数字信号处理、MCU (89C52)完成人机界面处理。

文中给出该系统在生物医学工程中的应用:静止悬浮式激光散射法血细胞分类计数仪中光电信号的采集和处理。

将该系统做适当修改,同样也可适用于其它光电信号的采集处理。

关键词:TMS320C6711CCD89C52数据采集数据处理引言TMS320C6711是TI公司推出的DSP芯片。

其数据处理功能非常强大,时钟速度可大100M(或者150M),但是其I/O功能要求有限。

因此,采用MCU(89C52)作为人机接口,构成双CPU(MCU 和DSP)系统。

1系统构成本文所介绍的CCD采集系统是在32位浮点DSP(TMS320C6711)上实现的。

如图1所示:单片机89C52负责接受键盘输入,并在液晶显示器上显示处理的结果信息;CCD在光点转换后的数据通过A/D转换器后在异步FIFO中缓存;DSP是系统的信息处理中心,它读取FIFO中的数据后经过处理,将结果传给89C52,由液晶显示器显示信息。

DSP(TMS320C6711)是整个硬件系统的信号处理中心。

它接受CCD传来的采集信号,加以处理并将结果传给单片机。

DSP还完成对Flash和SDRAM的控制。

MCU(89C52)主要充当人机界面的角色,接受外部键盘的输入,将DSP传输未来的结果用数据和图文的形式在液晶显示器上显示出来。

*8KB的可编程FlashMemory;*可以写/擦1000次以上;*内置256×8位RAM;*32个可编程I/O口。

图3信号双向缓冲器隔离图由于DSP计算能力很强,但I/O控制能力有限,因此89C52的以上性能可以保障系统控制能力,提供人机接口之便。

CCD(TCD132D)是一种新型的固体成像器件。

第30卷 第3期大连海事大学学报V ol.30,N o.3 2004年8月Journal of Dalian Maritime U niversity Aug.,2004文章编号:100627736(2004)0320065204线阵CCD高速图像采集与处理系统Ξ齐国清1,胡晓初2(11大连海事大学信息工程学院,辽宁大连 116026;2.大连市建设工程集团有限公司,辽宁大连 116001)摘要:介绍一种用于铁路轨道缺陷检测的图像采集与处理系统的硬件设计和软件开发.该系统采用高速线阵CC D在高速运动状态下获取轨道表面的清晰图像,CC D摄像头与采集卡之间采用Camera Link方式传递数据,采集板采用LVDS线路接收器DS90CR288接收收据,数据处理系统采用TI浮点DSP-T MS320VC33构成.讨论了在TI的C ode C omposer开发环境下利用C和汇编语言开发VC33应用程序的方法和应当注意的问题.关键词:线阵CC D;图像采集;轨道检测;数字信号处理器中图分类号:T N918.82 文献标识码:A0 引 言高速图像采集与处理系统广泛用于纸币印刷、织物等缺陷检测中,由于被检测物体处于高速运动当中,而缺陷检测要求高清晰度高分辨率的图像,因此用普通摄像设备很难获得满足要求的无模糊图像.线阵CC D摄像设备每次扫描只对一条扫描线成像,利用被摄物体与CC D之间的相对运动通过连续扫描形成二维图像.因此,只要线扫描率足够高,可以消除运动模糊.轨道缺陷视频检测系统,尤其适合采用高速线阵CC D.图像处理数据量大,尤其是实时图像处理对处理器的处理速度要求非常高.DSP具有运算能力强、速度快的特点,适合于实时处理系统.本文介绍利用TI浮点DSP-T MS320VC33实现的嵌入式线阵CC D图像采集与处理系统.1 系统组成系统组成如图1所示.包括CC D摄像头、Camera Link接收器,图像缓冲存储器、DSP、DSP程序和数据存储器以及由ISP实现的时序控制电路等.1.1 线阵CC D本系统中采用的是德国BA LSER公司线阵CC D2L101.在自由扫描状态下,L101k按预先设定的线扫频率自动重复扫描.L101直接输出数字信号,输出数据为8位或10位,输出信号采用LVDS 模式,L101b采用Channel Link标准,L101k采用Camera Link标准,也可以利用BA LSER公司提供的接口转换器BIC转换成RS644LVDS格式.1.2 Camera Link技术Camera Link技术的核心是美国NS(National Semiconductor)提出的一种高速数据传输方法———Channel Link技术,该技术主要用于数字图像数据的高速传输.两者均采用LVDS信号模式,但比先前的传输方法-RS644(RS422的LVDS模式)具有明显的优点.LVDS(Low Voltage Differ2 ential Signaling)是最近发展起来的一种利用低电压差分信号模式传输技术.LVDS信号Ξ收稿日期:20042042071作者简介:齐国清(19602),男,辽宁凌海人,教授.图1 系统组成框图为以+1.2V 为基准300mV 差分形式,LVDS 低电压摆幅差分模式具有高速传输数据时交叉干扰小、E MI 干扰小等优点.Channel Link 采用LVDS 方式传输数据,但是将28位数据转换成串行方式在4对线路上传输,再用另外一对线路传输时钟信号,最高传输率可达2.38G b/s ,传输距离可达10m.NS 的LVDS 发送器DS90CR287完成并行TT L/C M OS 信号到LVDS 信号的转换,LVDS 线路接收器DS90CR288将LVDS 信号还原成并行TT L/C M OS 信号.1.3 DSP 图像采集与处理系统CC D 输出图像数据经Camera Link 连线以串行方式接口连到图像采集板,由LVDS 线路接收器DS90CR288将其恢复成并行TT L/C M OS 信号,并分离出8位图像数据和像素时钟信号PixClk 及行有效信号Line Valid.每512行构成一幅图像保存在由512k ×8位SRAM (CY 7C1049)构成的输入图像缓冲存储器BRAM 当中,图像的写入控制信号和地址由ISP 根据PixClk 和Line Valid 信号产生.处理器采用TI 的32位浮点DSP C3x 系列的最新产品———T MS320VC33.由于DSP 片内存储器仅有34k ×32位,远远不能满足系统的要求,在片外设置了4个存储区:512k ×8位输入图像缓冲存储器BRAM (1片CY 7C1049),占用DSP 系统中的地址为0C00000H~0CFFFFFH ,512k ×8位的图像存储器IRAM (1片CY 7C1049),地址为600000H ~6FFFFFH ,固化程序的512k ×8位EPROM ,地址为000000H ~3FFFFFH ,256k ×32位的程序存储器PRAM (2片CY 7C1041),地址为400000H ~4FFFFFH ,256k ×32位的数据存储器DRAM (2片CY 7C1041,地址为500000H ~5FFFFFH ,以及作为开关量输出的存储器映射I O 口,对应的地址为0E00000H ~0EFFFFFH.程序固化在8位的EPROM (或F LASH )中,系统加电时由DSP 内的BootLoader 程序自动加载到DSP 片内RAM 或PRAM 中运行.地址译码及时序控制信号的产生由一片ISP (ispLS2128VE )来完成.T MS320VC33需要3.3V (DVDD )和1.8V (C VDD )两种电源供电,利用TI 的电源芯片TPS767D318可以直接产生3.3V 和1.8V 并同时产生DSP 加电复位信号RESET.12MH z 外部时钟直接加到DSP 的EXTC LK 端,C LK M D1和C LK M D0均接高电平,使DSP 内部P LL 工作在5倍频状态,产生120MH z 内部时钟信号H1.2 DSP 软件开发VC33的外部存储器及DM A 、定时器和串行通信口等外部接口设备都是在相应的控制寄存器的控制下工作的,因此程序开始运行前要对这些控制寄存器进行适当的设置.外部存储器控制寄存器(存储器映射地址为808064h )中的WTC NT 域(7~5位)用来设定DSP 对外存储器进行操作时插入的等待周期数,以适应不同速度的存储器.WTC NT 的默认值时111,即插入7个等待周期,若不需要插入这么多等待周期,则应当在程序开始处首先将外部存储器控制寄存器的WTC NT 设为相应的值.本系统中DSP 时钟频率为120MH z ,对应的指令周期约为8.3ns ,而外部存储器CY 7C1041和CY 7C1049的读写周期为20ns ,因此需要插入2个等待周期.决定EPROM (F LASH )的等待周期的总线控制寄存器控制字已经和程序代66 大连海事大学学报 第30卷 码一起写到了EPROM中.TI的浮点DSP集成开发软件C ode C om poser 支持用C语言开发程序,使用C编译器时应注意堆(Heap)和栈(Stack)的长度的设定.C编译器支持malloc()函数进行存储器的动态分配,动态存储器的分配是在堆中进行的.C编译器使用一个专用的未初始化的段.sysmem来构造堆.堆的默认长度为1k,若程序中需要进行动态分配存储器的空间大于1k,则应当在linker的2heap选项中设定堆的大小.C编译器用栈保存函数调用时传递参数和返回地址、分配局部变量及保存临时结果, C编译器使用一个专用的未初始化的段.stack来构造栈,C编译器为栈设的默认长度也是1k.C编译器并不检测栈的溢出,因此应当保证栈足够大.若程序中需要更长的栈,例如程序中使用了较大的局部数组变量,则应当在linker的2stack选项中设定栈的大小.而程序中的全局变量和静态变量在.bss段中分配.由于系统的存储器空间有限,堆、栈及.bss段都要在数据存储器中分配,因此堆和栈的长度要根据程序的实际需要合理设定.C编译器默认的存储模式为small m odel,即存储全局变量和静态变量的.bss段小于64k.此时C 编译器只在程序开始运行时设定DP寄存器值,使其指向.bss段的开始处,在程序运行过程中访问static变量、global变量及constant table时不再修改DP值.因此,当.bss段的实际长度大于64k时,必须选择big m odel.这样,C编译器每次访问.bss 段中全局变量和静态变量时会自动设置DP值,否则将得不到正确的地址.在汇编程序中定义的局部的符号变量(symbol)一般是与代码一起在. text段分配存储单元的,而.bss段与.text段一般是分别在不同的RAM中.因此在汇编程序中交替访问C变量和汇编程序中定义的symbol时,每次都要设置DP寄存器的值,才能得到正确的地址.在C程序中也可以访问汇编程序中定义的变量和常量.下例中在汇编的.bss段将var说明为global的(下划线表示是C变量)在C中将其说明为extern的就可以访问该变量.asm program:.bss -v ar,1.global-var......C proram:extern int var;var=1;......在C程序中访问汇编程序中定义的常量则与访问汇编变量不同.汇编变量在符号表(symbol table)中存放的是该变量的存储地址,而对于常量符号表中存放的是该常量的值.编译器无法区分符号表中哪一个是地址,哪一个是值.若在C中直接读汇编常量(by name),则编译器将该常量的值当作地址再去读对应的存储单元的值.为了避免这种错误,可在C中使用取地址符号(&)得到汇编常量的地址.若-x为汇编常量,在C中用&x 获得x的值.下面程序中在汇编程序中定义了长度为1000的常数表table-size,并将其声明为global型的.在C程序中借助强制类型转换(cast)获得其地址并赋给T ABLE-SIZE.asm program:-table-size .set 1000.global-table-size ......C proram:extern int table-size;#define T ABLE-SIZE((int)(&table-size))for(int=0;i<T ABLE-SIZE;i++) ......TI浮点DSP C3x/4x的C编译器支持ANSI C 的int型及float等数据类型,但应注意与PC机WI NDOWS或DOS系统下C的对应的数据类型含义并不完全相同.C3x存储器宽度为32位,char、short、int及long型均为32位,而且只占一个存储单元.float型和double等价,也各占一个存储单元.而在PC机中,由于存储器的宽度为8位,不同数据类型占据的存储单元数不相同.ANSI C的操作符sizeof可以测出一个数据类型所占的存储单元数.例如,若int为16位整数,则sizeof(int)= 2.而在C3x的C中sizeof(int)= 1.因此,在DSP 与PC机之间交换数据时,应注意数据类型的含义不同引起的存储区别.通过仿真器可以利用C 的文件操作函数对主机的文件进行读写.例如,利用这种方式可以从主机读取图像文件,读取bm p 文件的文件头BIT M APFI LEHE ADER结构和BIT M API NFOHE ADER结构时,由于bm p文件的文件头包含不同的数据类型,赋给DSP中相应的C 变量时,应将若干个字节合并在一起.例如, BIT M APFI LEHE ADER的前两个字节为W ORD型76第3期 齐国清,等:线阵CC D高速图像采集与处理系统 b fT ype ,其后的4个字节为DW ORD 型b fSize.利用下面方法可以将从打开文件中读进的前两个字节合并一起赋给变量b fT ype ,其后4个字节赋给变量b fSize.BIT M APFI LEHE ADER b f ;char tem p2[2];char tem p4[4];.........fpi =fopen (“c :\c33test \bm ptest \test.bm p ”,“rb +”);fread (tem p2,1,2,fpi );b f.b fT ype =tem p2[0]+(tem p2[1]<<8);fread (tem p4,1,4,fpi );b f.b fSize =tem p4[0]+(tem p4[1]<<8)+(tem p4[2]<<16)+(tem p4[3]<<24);.........C 程序调用汇编函数时有两种不同的参数传递方式,即寄存器方式和栈方式.C 编译器的默认方式为栈方式.在栈方式下,实时运行支持库可选rts30.lib ,若采用寄存器参数传递参数方式,则实时运行支持库应选rts30r.lib ,而且编译选项中的运行模式选项应选-mr.C3x 的linker 生成的目标文件(.out 文件)是C OFF 格式的,在仿真状态下可直接将.out 文件加载到DSP 内部RAM 或目标板上的SRAM.若要将程序固化到EPROM 或F LASH ,则由于常用的E 2PROM 编程器不接受C OFF 格式文件,需利用TI 提供的格式转换工具hex30将其转换成常用的hex 格式.固化程序中需提供程序的入口地址,即加载后程序运行的开始地址.对于C 代码,程序的入口地址为-c -int00,-c -int00的地址可以在连接时生成的map 文件中找到,并在运行hex30时在命令行用-e 选项提供给格式转换工具.运行hex30时还需要由一个cmd 文件提供总线控制寄存器控制字、ROM 芯片宽度、存储器字宽度等参数.3 结束语本文介绍了为铁路轨道缺陷视频检测系统开发的线阵CC D 图像采集与处理设备该系统利用TI 的浮点DSP -T MS320VC33实现了对BA LSER 公司线阵CC D -L101输出数据的采集与处理.在实际应用中,由于要求进行连续采集与处理,因此一个DSP 不能满足要求.在实验中.我们采用了两个DSP 并行工作的方式,实现了图像的连续采集与处理.若物体运动速度更快或图像处理算法更复杂时则采用更多个DSP 并行处理,或采用性能更强的DSP ,如TI 的64x 系列DSP.参 考 文 献:[1]柴雪松,杨凤春,罗 林.轨道视频检查系统[J ].中国铁路,2001(6),59260.[2]BA LSER L100b Series User ’s Manual[Z].Basler Vision T echnologies ,2001.[3]T MS320C3x User ’s G uide[Z].T exas Instruments Incorporated ,1997.Line scan CCD high speed image acquisition and processing systemQI G uo 2qing 1,HU X iao 2chu 2(rmation Technol.College ,Dalian Maritime Univ.,Dailan 116026,China ;2.Dalian C onstruction Eng.G roup C o.Ltd.,Dalian 116001,China )Abstract :An image acquisition and processing system designed for rail track flaw detection is presented.The system em ploys line scan CC D to acquire the clear image of the rail track surface under high speed m oving condition.The image data are trans ferred to the acquisition board in Camera Link format and the board receives the image data with National Semiconductor ’s line receiver DS90CR288.The image processing system is based on TI ’s floating -point DSP T MS320VC33.S oftware development techniques using TI ’s C ode C om poser with C and assembly language are als o discussed.K ey w ords :line scan CC D ;image acquisition ;rail track flaw detection ;digital signal process or86 大连海事大学学报 第30卷 。

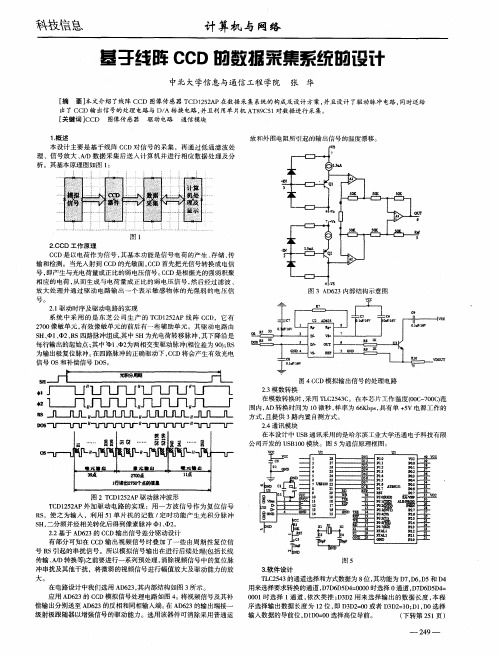

线阵CCD数据采集论文1系统硬件电路设计1.1TCD1208AP驱动电路TCD1208AP是一种二相双沟道线阵CCD图像传感器芯片,其驱动信号如图2所示。

四路驱动信号分别为:转移脉冲SH,复位脉冲RS,时钟脉冲Φ1、Φ2。

SH为高电平时信号电荷转移到CCD模拟移位寄存器,SH跳变为低电平后在时钟脉冲Φ1、Φ2交变作用下OS逐个按位输出像元电压信号,随后发出RS脉冲去掉信号输出缓冲器中的残余电荷为下一像元电压输出做准备。

根据传感器结构安排,TCD1208AP在一个采样周期中首先输出40个哑元信号,之后输出2160个有效像元输出,其后又输出12个哑元信号后一个输出周期结束,因此一个采样周期中至少包含2212次时钟信号交变和2212个复位脉冲RS。

CCD传感器对驱动信号的频率有严格要求[2],其时钟特性如表1所示。

STM32驱动信号产生方法有两种:a.设定通用定时器产生;b.直接设置IO口模拟。

第一种方法计时准确,通过设置相应定时器的预分频寄存器精度可达0.05μs,但通用定时器同步困难,需要使用中断来实现,操作困难且由于CCD交变时钟信号工作频率高而难以保证准确同步[3]。

系统采用库函数直接设置CPU寄存器控制IO口的方法输出驱动信号,通过设置锁相环PLL,STM32的指令执行速度高达72MHz,克服了以往单片机直接驱动频率低的问题。

IO跳变时间只有28ns,采用CPU空指令_nop()延时,精度为13ns,完成一个采样周期最快只需5ms 左右,通过库函数设置相应GPIO口的GPIOx_BSRR寄存器实现相应端口同时输出高或低电平可以确保各端口满足驱动信号同步性要求。

通过分析TCD1208AP驱动信号时序图可以看出除去SH中断位在一个Φ1或Φ2周期内可以将信号分为6种状态[4],如图3所示,Φ1、Φ2相位相反,周期为2倍的RS。

因此可以采用循环状态分割法让STM32周期性的输出大于1106(2212/2)个Φ1周期内的这6种状态即可完成一次采样。

基于嵌入式Linux的线阵CCD数据采集系统的开题报告1.引言随着现代科技的不断发展以及各种应用领域的需求不断增加,线阵CCD技术已经广泛应用于图像的数字化、精度的提高以及自动化控制等领域。

为了实现对线阵CCD图像数据的高效采集、处理和存储等功能,需要开发一种基于嵌入式Linux的线阵CCD数据采集系统。

2.研究目标本项目的主要研究目标是设计和实现基于嵌入式Linux的线阵CCD数据采集系统。

具体研究内容包括:(1)通过对线阵CCD的原理及其接口特性进行分析,设计适配线阵CCD的硬件电路系统;(2)选择合适的嵌入式Linux操作系统并搭建相应的开发环境;(3)实现线阵CCD数据的采集、处理和存储功能,包括时序控制、数字信号处理、存储设备的选择等;(4)进行系统调试和测试,验证系统的正确性和可靠性;(5)撰写系统开发文档并进行总结。

3.研究方法本项目的主要研究方法包括:(1)文献调研:通过查阅相关文献及资料,了解线阵CCD的原理及其接口特性,确定系统硬件电路系统和软件开发方案;(2)硬件设计:根据线阵CCD的接口特性和系统性能要求,设计适配线阵CCD的硬件电路系统,包括时序控制电路、数据输入输出电路、时钟电路等;(3)嵌入式Linux平台选择和软件开发:选择合适的嵌入式Linux操作系统,搭建相应的开发环境,采用开源软件库和工具进行系统开发,实现系统软件的设计和开发;(4)系统调试和测试:进行系统功能测试、性能测试和稳定性测试,发现和解决系统存在的问题,保证系统的正确性和可靠性;(5)文档撰写和总结:将系统开发的过程和结果撰写成系统开发文档,并进行总结和归纳,为后续类似项目提供参考。

4.预期成果完整的基于嵌入式Linux的线阵CCD数据采集系统,包括硬件电路系统和软件系统,实现如下功能:(1)实现对线阵CCD数据的高效采集、处理和存储,满足系统性能要求;(2)具有稳定性和可靠性,可长时间连续工作;(3)具有一定扩展性和可移植性,适应不同应用场景的需求。