Cadence扩大其在低功耗领域的领先地位,实现早期动态功耗分析与Pre-RTL探索

- 格式:doc

- 大小:4.08 KB

- 文档页数:1

cadence calculator器件参数Cadence Calculator是一款广泛被使用的集成电路设计工具,它拥有许多功能强大的器件参数,使得电路设计人员能够更加轻松地设计和评估电子器件的性能。

以下是一些关于Cadence Calculator的重要器件参数的详细介绍。

1.器件尺寸:器件尺寸是指器件所占的物理空间大小。

对于集成电路来说,器件尺寸的小大直接影响了芯片的密度和性能。

Cadence Calculator提供了各种不同尺寸的器件,用户可以根据自己的需求选择适合的尺寸。

2.器件功耗:器件功耗是指器件在工作状态下所消耗的电能。

对于移动设备和电池供电的应用来说,器件功耗是一个至关重要的参数。

Cadence Calculator提供了器件的功耗模型,可以帮助设计人员预测器件在不同工作条件下的功耗。

3.器件频率响应:器件频率响应是指器件对输入信号的频率变化所显示出的反应。

对于滤波器和放大器等应用来说,器件的频率响应是一个关键参数。

Cadence Calculator提供了用于计算频率响应的工具,可以帮助设计人员评估器件的频率特性。

4.器件电压特性:器件的电压特性描述了器件在不同电压下的行为。

对于模拟电路设计来说,器件的电压特性是一个非常重要的参数。

Cadence Calculator可以根据器件的物理结构和材料特性,计算器件在不同电压下的电流密度、电场分布和电势分布等信息。

5.器件温度特性:器件的温度特性描述了器件在不同温度下的行为。

对于高温环境或需要长时间稳定工作的应用来说,器件的温度特性是一个关键参数。

Cadence Calculator提供了器件的热传导模型,可以帮助设计人员评估器件在不同温度下的性能。

6.器件噪声特性:器件的噪声特性描述了器件在工作过程中产生的非期望信号。

对于低噪声电路设计来说,器件的噪声特性是一个重要参数。

Cadence Calculator提供了用于计算器件噪声的工具,可以帮助设计人员评估器件的噪声性能。

高科技企业开发复杂的芯片,封装和单板努力克服由于飞速增长的IC速度和数据传输速率联合引起的供电电压的降低,更高密度,越来越小型化的结构引起的电源完整性和信号完整性问题。

同时,更高的I/O数目,多堆叠的芯片和封装以及更高的电气性能约束都使得IC封装物理设计更加复杂。

Cadence具有突破型进展的解决方案,基于Sigrity专利技术,解决这些设计挑战。

该解决方案致力于完整的电源供电系统分析跨越了芯片,封装和单板;系统级的信号完整性(SI)分析,包含高速信号传输同步反转噪声和单个和多个芯片封装,最先进的3D封装以及系统级封装(SiPs)的高级物理设计。

Power Integrity电源完整性Cadence 电源完整性(PI)解决方案,基于Sigrity技术,提供signoff级别精度的PCB和IC封装的AC和DC电源分析。

每个工具都能与Cadence Allegro® PCB 和IC封装物理设计解决方案无缝集成。

Sigrity PowerSIIC封装和PCB设计快速准确的全波电磁场分析作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带S参数提取以及频域仿真。

Sigrity™ PowerSI®可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压超标等问题,从而帮助用户发现或改善潜在的设计风险。

PowerSI可以方便的提取封装和PCB的各种网络参数(S/Y/Z),并对复杂的空间电磁谐振问题产生可视化的输出。

PowerSI能与当前主流的物理设计数据库如PCB, IC封装和系统级封装(SiP)进行无缝连接。

主要功能• 为IC封装和PCB的电源分配网络(PDN)的可靠设计提供指导• 可以分析板上任意结构的电磁耦合特性,为器件/去耦电容的放置位置以及过孔的排布提供依据• 可以提取IC封装电源网络与信号网络的阻抗(Z)参数及散射(S)参数,研究电源的谐振频率以及输入阻抗,或研究信号的插入损耗及反射系数,为精确分析电源和信号的性能提供依据; 为时域SSN仿真提供可靠的宽带网络参数模型• 分析整板远场和近场的EMI/EMC性能,全三维显示复杂的近场辐射水平,为解决板级的EMI/EMC问题提供依据• 分析板上任意位置的谐振特性,找出系统在实际工作时电源平面上的谐振及波动特性,为电源的覆铜方式及去耦电容的放置位置提供依据• 支持叠层以及其他物理设计参数的假定(What-if)分析,快速评估设计参数对系统性能的影响• 基于专利算法的精确直流求解引擎(PowerDC),可支持从直流(DC)到宽频段的精确模型提取• 与三维(3D)IC封装设计和板级设计工具无缝集成优势与特点• 专业的频域分析工具,致力于Package/PCB全面的信号完整性、电源完整性、EMI/EMC的分析,有10年的历史,经过数以千计的设计产品验证,成熟可靠• 算法稳定可靠,即使对不规则的平面结构也能精确求解• 提供智能的多CPU、多任务分布式计算能力,可以把一个大型的复杂任务分配给多个CPU或多台计算机同步完成,从而大大提高了仿真效率。

《Cramming more components onto integrated circuits》——读书报告本篇论文发表于1965年,这个年代处于晶体管逐步退出历史舞台,集成电路慢慢由军用走到了商业化。

作者Gordon E. Moore展望了集成电子学的未来,预言十年后每个硅片内能集成的电子部件的数目可达65000个,然后谈论了集成电子学的目前发展及未来趋势、其学说的建立、可靠性、成本曲线,证明了与晶体管相比集成化更能节省空间,产量的增加与散热的问题,最后谈论了我们在什么情况下需要最大集成化与集成化对于线性系统的影响。

具体内容如下:集成电子学的未来:集成化的优势将带来电子学的突飞猛进的发展,并且推动这门科学应用到一些新的领域中。

集成电路将产生诸如家庭计算机、汽车上的自动控制、个人便携互联设备的奇迹。

电子手表仅需要一个屏幕的大小在今天已经成为了可能。

其最大的潜力在于大系统的产品。

在电话互联方面,在数字过滤器里的集成电路将为多路复用的设备划分通道。

集成电路也将改变电话线路与处理数据的能力。

计算机也会以完全不同的方式组织构成,例如,由集成电子学应用的存储器会不再像以前集中在一个中心单元而是分布在整个机器中。

像目前已经存在的机器将会以更低的成本生产并且生产周期也会变短。

当下与未来。

通过运用集成电子学,我的意思是各种各样与像目前的微电子学以及附属的技术将导致呈献给用户的电子功能部件是一个不可再简化功能部件。

这些技术最早是在1950年开始调查研究的,此项调查研究的目标是最小化电子功能部件使能够以最小化的重量封装更多的复杂电子功能部件能在有限的空间内。

这样相关的途径有针对个别部件的微型组件技术、薄膜结构和半导体集成电路。

每一种途径高速并融合着发展以至于彼此互相借鉴技术。

很多研究员相信未来的方法将是多种丰富方法的混合。

半导体集成电路的倡导已经用来改善薄片电阻器的特征,其途径是直接使用这样的薄片到有源的半导体衬底基片上。

公司概述Cadence是全球电子设计自动化(EDA领先企业,从事软件与硬件设计工具、芯片知识产权与设计服务,目前正致力于EDA产业的转型。

Cadence把此次转型构想命名为EDA360,因为它将包含设计过程中的所有方面,并关注最终产品的可盈利性。

这种应用驱动型方法,能在创建、集成与优化电子设计方面帮助我们的客户以更低的成本和更高的质量完成硅芯片、片上系统设备、以及完整的系统实现。

Cadence Design System, Inc.公司成立于1988年,总部位于美国加州圣荷塞,其设计中心、研发中心和销售部门分布于世界各地。

CADENCE中国1992年Cadence 公司进入中国大陆市场,迄今已拥有大量的集成电路 (IC 及系统设计客户群体。

在过去的二十年里,Cadence公司在中国不断发展壮大,建立了北京、上海、深圳分公司以及北京研发中心、上海研发中心,并于2008年将亚太总部设立在上海,Cadence中国现拥有员工400余人。

北京研发中心和上海研发中心主要承担美国公司总部EDA软件研发任务,力争提供给用户更加完美的设计工具和全流程服务。

Cadence在中国拥有强大的技术支持团队,提供从系统软硬件仿真验证、数字前端和后端及低功耗设计、数模混合RF 前端仿真与DFM以及后端物理验证、SiP封装以及PCB设计等技术支持。

我们的销售方案中还包括提供专业设计服务,VCAD团队为用户提供高质量、有效的设计和外包服务。

把世界顶尖的产品技术和服务融入中国,成为中国电子行业最亲密合作伙伴,和中国电子高科技产业共同腾飞是Cadence 在中国的坚定信念。

市场与趋势Cadence服务于产值达2万亿美元的全球电子市场,其中包括产值超过3000亿美元的半导体市场。

我们的主要垂直市场领域包括:有线与无线通讯;工业、医疗与汽车电子;计算机与消费电子,比如多媒体和个人娱乐设备。

这些领域占全球电子设备营收和半导体营收的90%以上。

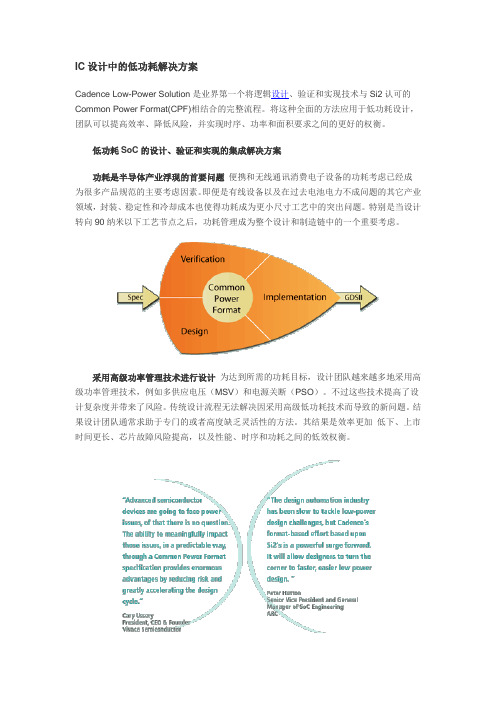

IC设计中的低功耗解决方案Cadence Low-Power Solution是业界第一个将逻辑设计、验证和实现技术与Si2认可的Common Power Format(CPF)相结合的完整流程。

将这种全面的方法应用于低功耗设计,团队可以提高效率、降低风险,并实现时序、功率和面积要求之间的更好的权衡。

低功耗SoC的设计、验证和实现的集成解决方案功耗是半导体产业浮现的首要问题便携和无线通讯消费电子设备的功耗考虑已经成为很多产品规范的主要考虑因素。

即便是有线设备以及在过去电池电力不成问题的其它产业领域,封装、稳定性和冷却成本也使得功耗成为更小尺寸工艺中的突出问题。

特别是当设计转向90纳米以下工艺节点之后,功耗管理成为整个设计和制造链中的一个重要考虑。

采用高级功率管理技术进行设计为达到所需的功耗目标,设计团队越来越多地采用高级功率管理技术,例如多供应电压(MSV)和电源关断(PSO)。

不过这些技术提高了设计复杂度并带来了风险。

传统设计流程无法解决因采用高级低功耗技术而导致的新问题。

结果设计团队通常求助于专门的或者高度缺乏灵活性的方法。

其结果是效率更加低下、上市时间更长、芯片故障风险提高,以及性能、时序和功耗之间的低效权衡。

业界第一套完整的低功耗解决方案为帮助设计团队采用高级功耗降低技术,Cadence 开发了低功耗芯片设计、验证和实现的第一套完整的解决方案。

Cadence Low-Power Solution结合了一批来自多种Cadence平台的技术,这些先进的产品都应用了Common Power Format (CPF)——这是Si2认可的规格,用于在设计过程初期确定节能技术,这使他们可以分享和复用智能的低功耗设计。

Cadence Low-Power Solution的优点包括:·降低风险:将手动调整的需要降到最低,使用强劲的验证方法,设计团队可以消除源自功能和结构缺陷的芯片故障风险。

·更高的效率和更快的上市时间:高度集成和自动化帮助设计团队维持高生产力水平。

SMIC-Cadence参考流程2.1基于 Cadence 的 SoC Encounter 解决方案和一个公开源代码的处理器, SMIC-Cadence 参考流程应用了受业界广泛认可的 ARM ( Artisan ) 130 纳米单元库来演示如何设计和开发一款对功耗进行优化的芯片。

针对最新的 SMIC 0.13 微米 1P8M 标准工艺,流程采用了ARM 的单元库, SMIC 的 IO 库和一些其他相应的 IP 。

SMIC-Cadence 参考流程 2.1 版是一个从 RTL 到 GDSII 的完整流程。

包括了数字设计中必需的几个阶段:前端(逻辑综合、仿真、形式验证),后端(基于 SoCE 的布局布线)和验证等三大部分。

针对深亚微米设计中常见的电源分配、时序收敛、信号完整性和如何减小芯片面积等常见问题,流程对所有关键步骤都进行了相应优化。

针对 SMIC130nm 标准工艺,和 Artisan 提供的高阈值电压和标准阈值电压的两种单元库,参考流程充分利用了这两种不同特性单元来优化芯片的功耗。

对于时序不敏感的路径, SoC Encounter 采用高阈值电压单元管来替代标准阈值电压单元管的方法,从而达到很好地控制漏电电流,降低芯片待机功耗的目的。

SMIC-Cadence 参考流程 2.1 版提供了一条快捷、有效、低风险的设计路径。

利用流程提供的完整 TCL 脚本,用户可以方便再现 RTL-to-GDSII 的设计过程。

以下是流程中用到的主要 Cadence 工具: RTL Compiler, First Encounter, Global Physical Synthesis (GPS), NanoRoute, Incisive Conformal, VoltageStorm PE, Fire & Ice QX, CeltIC, Virtuoso Chip Editor, 和 Assura 。

FARADAY 选择CADENCE VOLTAGESTORM 用于高级65 纳米低功耗签收Cadence 设计系统公司与领先的ASIC 和硅智产(SIP)无晶圆IC 设计公司智原科技宣布智原已经采用Cadence® VoltageStorm® 功率分析技术进行低功耗签收,并支持智原的尖端低功耗设计。

智原使用VoltageStorm 的静态和动态功率分析检验其高级低功耗设计技术,包括功率门控、去耦合电容优化和多电源多电压(MSMV)规划。

智原有一套现成的功率分析解决方案,目前已经成功发展到90 纳米级别。

不过由于意识到了65 纳米及以下级别低功耗签收带来的新技术挑战,智原对目前市面上所有商用的功率分析和电压降解决方案进行了深入的评估。

VoltageStorm 功率分析被选为精确检验智源的复杂低功耗设计的惟一解决方案。

此外,VoltageStorm 分析和Cadence SoC Encounter™ RTL-to-GDSII 系统(智源所选的设计实现方案)的结合,带来了一个卓越的解决方案,能够在实现过程中优化电源开关和去耦合电容,它被证明对智源有着极高的价值。

“我们对65 纳米高级低功耗设计的功率分析的精确性非常关注,”智原SoC 开发及服务部副总裁C. J. Hsieh 说。

“经过我们的严格评估,VoltageStorm 分析清楚地表现了它的功能性、精确性、容量和性能都符合我们未来的生产需要。

能够从SoC Encounter 系统直接进行VoltageStorm 分析的能力为我们的后端设计工程师大大提高了易用性。

”VoltageStorm 的静态和动态功率分析是Cadence 低功耗解决方案的一个关键构成,也是Encounter® IC 设计平台不可或缺的一部分,它可以检验全芯片电压降和电源连线的电迁移。

去耦合电容和电源开关的自动优化也通过与SoC Encounter 系统的紧密结合成为可能。

中芯国际采用Cadence公司DFM 和低功耗硅技术 全球电子设计创新领先企业Cadence设计系统公司,今天宣布中国最大的半导体晶圆厂中芯国际集成电路制造有限公司,已经将Cadence® Silicon Realization产品作为其65纳米参考流程4.1版本(Reference Flow 4.1)可制造性设计(DFM)以及低功耗技术的核心。

以Cadence Encounter Digital Implementation System为基础,两家公司合作为65纳米系统级芯片(SoC)设计提供了一个完整的端到端的Silicon Realization流程。

经过严格评估,中芯国际选择了Cadence Silicon Realization产品,基于其强大的层次化流程(hierarchical flow),应用于大规模和高质量的设计。

中芯国际认为此紧凑结合了功能性、物理和电气领域的整合流程,可用于评估、逻辑设计、验证、物理实现与设计内签收,并大大提高设计师的效率、易用性,及获得更具确定性的结果(deterministic results)。

中芯国际流程中包含的Cadence Silicon Realization技术包括Incisive® Enterprise Simulator、Encounter® RTL Compiler、Encounter Test、Encounter Conformal® Low Power、Encounter Conformal Equivalence Checker、Encounter Digital Implementation System、QRC Extraction、Encounter Timing System、Encounter Power System、Litho Physical Analyzer、Litho Electrical Analyzer、Cadence CMP Predictor 和Assura® Physical Verification。

Cadence扩大其在低功耗领域的领先地位,实现早期动态功耗分析与Pre-RTL探索

全球设计创新领先企业Cadence设计系统公司(纳斯达克:CDNS)已经扩大其在低功耗低功耗领域的领先地位,推出了系统级系统级功率分析功率分析与探索的突破性技术。

Cadence 低功耗解决方案目前已经在高级低功耗芯片的设计、实现与验证系统方面建立了领先地位,现在Cadence正在解决设计师们的下一个重要需求——在产品设计周期初期尽早进行更快的功耗的探索与估算。

Incisive Palladium Dynamic Power Analysis能够让SoC设计师、架构师与验证工程师在设计阶段迅速估算他们的系统功耗,分析运行多种真实软件堆栈与其它现实激励的影响。

该新技术方案还包含了Cadence InCyte Chip Estimator,它现在可以通过不同低功耗技术低功耗技术的探索提供假设式功率分析。

InCyte Chip Estimator还可以自动生成Si2通用功率格式(CPF),它有助于推动架构性功耗规格与意图贯穿于实现与验证过程。

Palladium Dynamic Power Analysis对有系统级关联的电子设备的功耗预算提出了一种创新的方法学变化。

Palladium Dynamic Power Analysis围绕生产力的提升,有助于迅速识别在不同运作环境中运行真实软件的SoC设计的平均功耗与峰值功耗。

利用Palladium III内置的存储器与RTL 编译器功率估算引擎,Cadence提供了第一款高性能、周期精确型的综合解决方案,提供了硬件和软件设计的全系统功率分析。

“作为一个产业,我们才刚刚开始认识到节能型设计带来的好处。

”Forward Concepts首席无线分析师Will Strauss 说,“与此同时,消费者需要更多的功能和更高的性能,同时又要保持相同甚至更长的电池寿命和信号覆盖率。

Cadence提供了独特的能力,在硬件和软件设计汇合点找到功耗分析与验证的权衡——在系统级上,芯片设计可能会影响系统软件性能,反之亦然。

在这个层面上,更快、更简单和更高效的功率设计非常必要。

”Cadence InCyte Chip Estimator满足客户所需,可以更早地进行功耗探索和估算,现在它还提供了低功耗规划能力,其中包括通用功率格式的自动创建。

这就允许设计师对盘片尺寸、性能和成本实现精确的预RTL估算,对于各种低功耗技术的设计影响及早进行探索。

InCyte Chip Estimator可以用于认可和探索CPF环境和界面,应用于下游Cadence实现、RTL模拟和仿真工具,在整个设计方法学中推动低功耗战略。

“投片前系统级功耗分析与探索需要对功率要求有一个广阔的视野,同时对现实环境下的功耗有具体的认识。

”Cadence设计系统公司系统设计与验证产品营销部主管Ran Avinun说,“Palladium Dynamic Power Analysis和InCyte Chip Estimator结合,在设计过程初期就能提供自动化流程与能力,能够将技术库、嵌入式软件和真实的激励计算在内,确保在第一个第一个工作软件阶段第一个芯片的真实环境就能符合系统功率预算限制。

”InCyte Chip Estimator与Palladium Dynamic Power Analysis现已推出,将会在2008年9月9日当周于圣荷塞举办的CDNLive中展出。

Palladium Dynamic Power Analysis产品被作为Palladium III系统的一个可选部分进行销售。

关于Cadence Cadence公司成就全球电子设计技术创新,并在创建当今集成电路和电子产品中发挥核心作用。

我们的客户采用Cadence的软件、硬件、设计方法和服务,来设计和验证用于消费电子产品、网络和通讯设备以及计算机系统中的尖端半导体器件、印刷电路板和电子系统。

Cadence 2007年全球公司收入约16亿美元,现拥有员工约5100名,公司总部位于美国加州圣荷塞市,公司在世界各地均设有销售办事处、设计中心和研究设施,以服务于全球电子产业。

关于公司、产品及服务的更多信息,敬请浏览公司网站 .cn。