基于74HC175的Gold伪随机序列发生器设计[开题报告]

- 格式:doc

- 大小:26.04 KB

- 文档页数:4

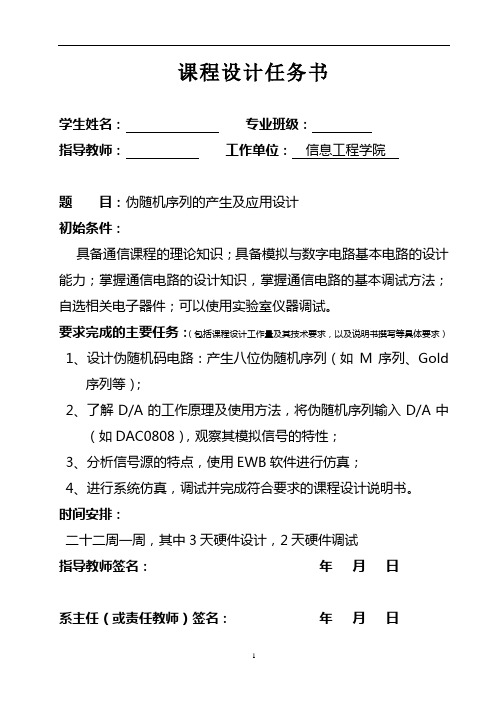

课程设计任务书学生姓名:专业班级:指导教师:工作单位:信息工程学院题目:伪随机序列的产生及应用设计初始条件:具备通信课程的理论知识;具备模拟与数字电路基本电路的设计能力;掌握通信电路的设计知识,掌握通信电路的基本调试方法;自选相关电子器件;可以使用实验室仪器调试。

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、设计伪随机码电路:产生八位伪随机序列(如M序列、Gold序列等);2、了解D/A的工作原理及使用方法,将伪随机序列输入D/A中(如DAC0808),观察其模拟信号的特性;3、分析信号源的特点,使用EWB软件进行仿真;4、进行系统仿真,调试并完成符合要求的课程设计说明书。

时间安排:二十二周一周,其中3天硬件设计,2天硬件调试指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (I)1理论基础知识 (1)1.1伪随机序列 (1)1.1.1伪随机序列定义及应用 (1)1.1.2 m序列产生器 (2)1.2芯片介绍 (4)1.2.1移位寄存器74LS194. (4)1.2.2移位寄存器74LS164 (5)1.2.3 D/A转换器DAC0808 (6)2 EWB软件介绍 (8)3设计方案 (9)4 EWB仿真 (11)5电路的安装焊接与调试 (13)6课程设计心得体会 (14)参考文献 (15)附录1 (16)摘要伪随机序列具有良好的随机性和接近于白噪声的相关函数,使其易于从信号或干扰中分离出来。

伪随机序列的可确定性和可重复性,使其易于实现相关接收或匹配接收,因此有良好的抗干扰性能。

伪随机序列的这些特性使得它在伪码测距、导航、遥控遥测、扩频通信、多址通信、分离多径、数据加扰、信号同步、误码测试、线性系统、各种噪声源等方面得到了广泛的应用,特别是作为扩频码在CDMA系统中的应用已成为其中的关键问题。

此次课设根据m序列的产生原理,利用74LS164加少量门电路方法设计了8位m序列发生器。

基于74LS175芯片的四人抢答器设计西安电子科技大学长安学院课程设计论文课题名称:基于74LS175芯片的四人抢答器设计姓名: 李渊学号: 11211019专业: 电子信息工程日期: 2013年12月目录摘要 (2)Abstract (3)第一章引言 (4)1.1 设计要求 (5)第2章功能介绍 (5)第3章抢答器设计模块 (6)3.1 总体设计模块 (6)3.2 四路抢答器的简介 (6)3.3 四路抢答器的原理 (6)3.4 单元模块设计 (10)3.5 实验设备与器件 (10)3.6 74LS175芯片 (10)第4章实验步骤与要求 (11)4.1 电路图设计 (11)4.2 电路仿真 (13)4.3 检测与查阅器件 (14)4.4 连接电路 (14)4.5 电路调试 (14)4.6 电路功能试验 (14)4.7 电路分析 (14)结束语 (15)参考文献 (16)致谢 (17)基于74LS175芯片四人抢答器的设计摘要:随着电子技术的发展,它在各个领域的应用也越来越广泛。

人们对它的认识也逐步加深。

人们也利用了电子技术以及相关的知识解决了一些实际问题。

如:智能抢答器的设计与制作。

抢答器是竞赛问题中一种常用的必备装置,从原理上讲,它是一种典型的数字电路。

触发器是数字电路中的基本逻辑记忆单元,具有两个稳定状态用以表示逻辑状态“l”和“0”。

在电路中它具有记忆信号的功能,是构成各种时序电路的最基本逻辑单元.本文通过对枪答器电路设计的详细分析,以加深对触发器的功能以及其应用的认识和理解。

数字抢答器由主体电路与扩展电路组成。

触发器电路将参赛队的输入信号在显示器上输出;主持人按开始按钮示意开始,以上两部分组成主体电路。

通过两个与门电路实现屏蔽功能,构成扩展电路。

经过布线、焊接、调试等工作后数字抢答器成形。

供四人用的竞赛抢答器装置线路,用以判断抢答优先权。

它有三部分构成:1个D触发器74LS175,它具有置0端,置1端和CP端;1个4输入与门,1个二输入与门;四个轻触开关,它们组成抢答电路中的CP时钟脉冲源,抢答开始时,由主持人清除信号,按下复位开关S,74LS175的输出Q 1非~Q 4非全为1,所有发光二极管LED均熄灭,当主持人宣布“抢答开始”后,首先作出判断的参赛者立即按下开关,对应的发光二极管点亮,同时,通过与门送出信号锁住其余三个抢答者的电路,不再接受其它信号,直到主持人再次清除信号为止.关键词:数字电路设计;触发器;优先抢答Based on the 74 LS175 chip of the design of vies to answer first four peopleAbstract :With the development of electronic technology, its application in all fields more and more widely. People the knowledge of it also deepened step by step. People use electronic technology and relevant knowledge to resolve some problems. Such as: intelligent vies to answer first is the design and manufacture. The problem is a competition vies to answer first used the necessary device, from the principle of speaking, it is a kind of typical digital circuits. Flip-flop is in digital circuits basic logic memory unit, with two steady state is used to represent the logical state "l" and "0". In a circuit it has the function of memory signals, it is to make the most of the sequential circuits basic logic unit. This article through to the gun a processor circuit design detailed analysis, in order to deepen our understanding of the function of the application and trigger the understanding and the understanding. Digital vies to answer first is composed of main circuit and expanding the circuit. Trigger circuit will be the team's input signal on a display output; Press the start button beckoned to start the, the above two parts subject circuit. Through the two gate and realize the shielding function, constitute expansion circuit. After wiring, welding, commissioning work digital vies to answer first is forming.For four of the competition with the device vies to answer first line to determine vies to answer first priority. It is composed of three parts: 1 D flip-flop 74 LS175, it has to buy the 0, buy 1 end and the CP end; A 4 input to the door, a second input and the door; Four light touch switch, they constitute the CP clock pulse vies to answer first circuit source, vies to answer first began, the host clear signal, press the reset switch S, 74 LS175 output Q and the ~ Q and the total for the 1, all leds are LED to put out, when the host announced "vies to answer first start", first to judge the press the switch immediately, the corresponding leds light, and at the same time, through the door and send out signals to lock the three who vies to answer first the circuit, no longer accept other signals until the host again so clear signal.第1章引言随着经济水平的不断提高,当今的社会竞争日益激烈,选拔人才,评选优胜,知识竞赛之类的活动愈加频繁,智力竞赛是一种生动活泼的教育方式,人们在物质文明得到满足的同时更注重精神文明的追求,各种节目不断涌现,提高节目的质量尤为重要。

伪随机序列仿真仿真实验报告报告时间:2013年5月13日姓名:刘梦曦学号:2010101012电子邮件:604417989@一、实验目的1、熟悉MATLAB 仿真的应用;2、掌握伪随机序列的原理、软件产生,并仿真分析其相关特性。

二、实验内容1、MATLAB中产生127位gold序列,并分析其自相关和互相关特性。

2、采用MATLAB的伪随机函数,生成127位二进制伪随机序列,并分析其自相关和互相关特性。

3、收集学习技术资料,列举五种以上通信系统中采用的伪随机序列。

三、实验过程记录根据搜集的资料在matlab中编写代码,然后运行,得到相应的特性图。

1、产生127位的gold序列2、gold序列的自相关性在MATLAB中编写的代码如下:close all;clear all;clc;n=7;%移位寄存器级数P=2^n-1%m列的周期%产生m1序列%c1=[1 0 1 0 0 1 1];%反馈系数==211 reg1=[zeros(1,n-1) 1];%初始化移位寄存器m1(1)=reg1(n);for i=2:P new_reg1(1)=mod(sum(c1.*reg1),2) ;for j=2:nnew_reg1(j)=reg1(j-1); endreg1=new_reg1;m1(i)=reg1(n);endsubplot(311);stairs(m1);xlabel('k');title('m1序列');%产生m2序列%c2=[1 0 1 1 0 0 1];%反馈系数==217 reg2=[zeros(1,n-1) 1];%初始化移位寄存器m2(1)=reg2(n);for i=2:Pnew_reg2(1)=mod(sum(c2.*reg2),2) ;for j=2:nnew_reg2(j)=reg2(j-1);endreg2=new_reg2;m2(i)=reg2(n);endsubplot(312);stairs(m2);xlabel('k');title('m2序列');%产生gold序列%for i=0:P-1shift_m2=[m2(i+1:P)m2(1:i)];%m2g(i+1,:)=mod(m1+shift_m2,2);%模2加endsubplot(313)stairs(g(1,:));xlabel('k');title('gold序列的第1行');%gold序列的自相关特性和互相关特性%g1=g(1,:);g2=g(2,:);%取gold序列的第2行% for i=-P+1:-1% shift=[g1(i+P+1:P) g1(1:i+P)];%r1(P+i)=sum(g1(P+i).*shift(P+i)) ;% end% for i=0:P-1% shift=[g1(i+1:P) g1(1:i)]; %r1(P+i)=sum(g1(i+1).*shift(i+1)) ;% endr1=conv(g1,g1);figure(2)subplot(211)stem(r1/P);xlabel('k');title('g1的自相关特性');% for i=-P+1:-1% shift=[g1(i+P+1:P) g1(1:i+P)];%r2(P+i)=g2(P+i).*shift(P+i);% end% for i=0:P-1% shift=[g1(i+1:P) g1(1:i)]; %r2(P+i)=g2(i+1).*shift(i+1);% endr2=conv(g1,g2);subplot(212);stem(r2/P);xlabel('k');title('g1与g2的互相关特性');(产生图形见附录)四、分析及结论由这个实验我们可以看出,Gold序列间不仅有良好的互相关性能,而且个数远比m序列多。

基于FPGA的伪随机序列发生器设计方案1基本概念与应用1)1FSR:线性反馈移位寄存器(1inear feedbackshiftregister,1FSR)是指给定前一状态的输出,将该输出的线性的薮再用作输入的移位寄存器。

异或运算是最常见的单比特线性函数:对寄存器的某些位进行异或操作后作为输入,再对寄存器中的各比特进行整体移位。

1FSR产生的两种形式为伽罗瓦(Ga1ois)和斐波那契(FibonaCCi)两种形式。

也有成为外部(Ex隹rna1)执行方式和内部(Interna1)执行方式。

(1)伽罗瓦方式(Interna1)X0X4X17! ! TepCount ,-Θ□□EF-Γ>4300000000Θ{3B0-*~*DaiaFtowW>)∙ι.x4.χ“(Ga1oisImp1ementation)Ga1ois方式特征数据的方向从左至右,反馈线路是从右至左。

其中XCo项(本原多项式里面的T'这一项)作为起始项。

按照本原多项式的指示确定异或门(XOR)在移位寄存器电路上的位置。

如上图所示XM。

因此Ga1ois方式也有人称作线内或模类型(M-型)1FSRo(2)斐波那契方式(Externa1)TapCountB*0;E3t3-⅛QEHIH30GHZHHDGIFSHpcivncrTMrig(M)-X14.X,>♦X n»1(Fibonacciimp1ementation)从图中我们可以看到Fibonacci方式的数学流向和反馈形式是恰好跟Ga1ois方式相反的,按照本原多项式,其中XCO这一项作为最后一项,这里需要一个XOR∏,将本原多项式中所给的taps来设定它的异或方式。

因此Fibonacci方式也被叫做线外或者简型(S-型)1FSR。

2)本原多项式本原多项式是近世代数中的一个概念,是唯一分解整环上满足所有系数的最大公因数为1的多项式。

本原多项式不等于零,与本原多项式相伴的多项式仍为本原多项式。

真伪结合的随机数发生器算法研究

随机数生成器是计算机科学中一个重要的算法,其应用范围广泛,比

如密码学、模拟器、游戏等等。

然而,随机数生成器的可靠性和安全

性成为了一个亟待解决的问题。

因此,真伪结合的随机数发生器算法

研究成为了研究热点之一。

真伪结合的随机数发生器算法,简称TRNG算法,是一种不依赖于计

算机的随机数发生器,它是一种通过测量物理过程的随机变化,产生

真随机数的算法。

与之相对的是伪随机数发生器算法,它是一种基于

计算机算法来生成随机数的方法。

伪随机数的生成过程是按照某种固

定的计算方式来生成一串看似随机的数字序列,并不是真正的随机数。

TRNG的核心技术基于不可预测的自然随机事件,比如光电效应、热

噪声、放射性衰变等等。

使用TRNG算法产生真随机数的过程比使用

伪随机数发生器要更加安全可靠。

因为TRNG算法不依赖于固定的计

算方式,而是根据物理过程的随机性变化来生成随机数。

TRNG算法可以广泛应用于密码学、模拟器、游戏等领域,并且可以

在保证安全性的同时提高计算机系统的效率。

在密码学中,真随机数

可以用于生成加密密钥,保证密钥的安全性;在模拟器中,真随机数

可以用于模拟物理实验,提高模拟器的准确性;在游戏中,真随机数

可以用于生成随机道具、随机奖励等等,增加游戏的趣味性。

总的来说,随机数生成器是计算机科学中一个重要的算法,而TRNG 算法作为一种真随机数发生器,在保证安全性和可靠性的前提下,可以应用于密码学、模拟器、游戏等领域。

因此,TRNG算法的研究具有重要的理论及实践意义。

伪随机序列发生器设计伪随机序列发生器(PRNG)是一种通过算法生成的看似随机的数字序列。

与真随机序列不同,伪随机序列是在一定条件下按照确定性算法生成的。

在计算机系统中,PRNG具有广泛的应用,包括密码学、模拟、游戏等领域。

本文将讨论如何设计一个伪随机序列发生器。

1.随机性的度量:在设计PRNG之前,我们需要了解随机性的度量。

一个好的伪随机序列发生器应该具有高周期性(周期长度大),均匀性(数字出现的频率相似)和不相关性(序列中的数字之间没有明显的关联)。

周期指的是序列重复之前所产生的数字数量。

均匀性可以通过观察数字出现的频率和统计分析来评估。

不相关性指的是序列中的任意两个数字之间没有明显的关联。

2.线性反馈移位寄存器(LFSR):LFSR是一种常见的PRNG设计方法。

它由一个位寄存器和一些异或门组成。

位寄存器中的每个位都线性地与寄存器中的其他位进行异或运算,并且每次循环位寄存器向右移位。

输入位是通过将一些位与1或0常量进行异或来确定的。

3.LFSR的优化:为了改善LFSR的性能,在设计中可以考虑一些优化措施。

一种常见的优化措施是增加反馈函数的复杂性。

通过使用非线性函数,可以在相同的位数下获得更长的周期。

另一个优化措施是根据需要选取适当的位数。

位数越大,周期越长,但计算成本也增加。

4.添加非线性元素:为了进一步提高伪随机序列的质量,我们可以添加一些非线性元素。

一种方法是使用置换函数。

置换函数将输入映射到不同的输出,从而增加了数字之间的不相关性。

另一种方法是使用哈希函数。

哈希函数将输入的随机性扩展到更大的空间中,并通过混淆输入来减少数字之间的关联。

5.分析和测试:设计一个PRNG后,我们需要对其进行分析和测试。

常用的测试方法包括统计测试、重复序列测试和关联测试。

统计测试可以用于检查输出数字的频率。

重复序列测试可以用于验证序列中是否存在重复数字。

关联测试则是用于检查序列中数字之间的关联性。

总结:设计一个高质量的伪随机序列发生器需要考虑随机性度量、LFSR和优化、非线性元素的添加以及分析和测试的步骤。

基于FPGA的伪随机序列发生器设计随着通信理论的发展,早在20世纪40年代末,香农(Shannon)就曾指出,在某些情况下,为了实现最有效的通信,应采用具有白噪声的统计特性的信号。

目前广泛应用的伪随机噪声由数字电路产生的周期序列(经滤波等处理后)得到的。

我们将这种周期序列称为伪随机序列。

伪随机序列概述伪随机序列发展及应用随着通信技术的发展,在某些情况下,为了实现最有效的通信应采用具有白噪声统计特性的信号;为了实现高可靠的保密通信,也希望利用随机噪声;另外在测试领域,大量的需要使用随机噪声来作为检测系统性能的测试信号。

然而,利用随机噪声的最大困难是它难以重复再生和处理。

伪随机序列的出现为人们解决了这一难题。

伪随机序列具有类似于随机噪声的一些统计特性,同时又便于重复产生和处理,有预先的可确定性和可重复性。

由于它的这些优点,在通信、雷达、导航以及密码学等重要的技术领域中伪随机序列获得了广泛的应用。

而在近年来的发展中,它的应用范围远远超出了上述的领域,如计算机系统模拟、数字系统中的误码测试、声学和光学测量、数值式跟踪和测距系统等也都有着广阔的使用。

伪随机序列通常由反馈移位寄存器产生,又可分为线性反馈移位寄存器和非线性反馈移位寄存器两类。

由线性反馈移位寄存器产生出的周期最长的二进制数字序列称为最大长度线性反馈移位寄存器,即为通常说的m序列,因其理论成熟,实现简单,应用较为广泛。

伪随机序列的特点决定了它有着重要并且广泛的应用,这里仅举出一些有代表性的用途。

误码率测量。

在数字通信中误码率是一项重要的质量指标,在实际测量数字通信系统的误码率时,一般来说,测量结果与信源发出信号的统计特性有关。

通常认为二进制信号0和1是以等概率随机出现的。

所以测量误码率时最理想的信源应是伪随机序列产生器。

这样测量的结果,我们认为是符合实际运用时的情况。

时延测量。

有时我们需要测量信号经过某一传输路径所收到的时间延迟,例如,需要测量某一延迟线的时间延迟。

Gold码发生器的设计与仿真作者:魏瑞来源:《电脑知识与技术》2014年第30期摘要:Gold(戈尔德)码是伪随机码的一种,伪随机码在扩展频谱通信系统中起着十分关键的作用,伪随机序列发生器是扩频通信系统中重要的组成部分。

本设计主要介绍m序列和Gold序列的生成原理,提出了采用EDA实现Gold序列的一般方法,本方法通过模块化m序列发生器,用原理图的方式设计了一个码长为25-1=31的Gold序列,通过QuartuII编译仿真并成功下载测试。

关键词:Gold码; m序列;伪随机码中图分类号:TP313 文献标识码:A 文章编号:1009-3044(2014)30-7039-02扩频通信因其具有保密性好、截获概率低、抗干扰性能强以及多址复用等优点,目前已经在现代军事通信、卫星通信、移动通信以及指挥控制通信中得到了广泛应用。

Gold码是扩频通信中应用较多的一种扩频码。

该文重点研究了基于EDA的Gold码发生器的设计与仿真。

1 Gold码Gold码是R·Gold为了解决m序列个数不多且m序列之间的互相关函数值不理想而提出的提出了一种基于一对周期和速率均相同的m序列优选对模2加后得到的码序列。

他的特点是随着级数n的增加,Gold码序列的数量远超过同级数的m序列的数量,且Gold码序列具有良好的自相关特性和互相关特性,因此在扩频通信得到了广泛的应用。

2 Gold码的产生原理及设计1) Gold码的产生原理Gold序列具有良好的自、互相关特性,且地址数远远大于m序列地址数。

如有两个m序列,它们的互相关函数的绝对值有界,且满足以下条件:[R(τ)=2n+12+1,2n+22+1,][][n为奇数n为偶数,n不是4的倍数] (1)我们称这一对m序列为优选对。

每改变两个m序列相对位移就可得到一个新的Gold序列,当相对位移2n-1位时,就可得到一簇2n-1个Gold序列。

再加上两个m序列,共有2n+1个Gold序列码。

伪随机码脉冲信号发生器电路设计摘要由于伪随机码在CDMA(Code Division Multiple Access)技术中得到了广泛的应用,为更好的利用CDMA技术,需了解伪随机码脉冲信号。

本课题主要是应用CPLD技术,设计一个伪随机码脉冲信号发生器电路,所用到的主要元器件有74LS74、EPM7128SLC84—15 MAX 7000可编程逻辑器件及一些门电路等,并利用MAX+PLUS Ⅱ软件来观察电路波形及CPLD综合实验板来检测电路的功能是否达到设计要求。

关键词伪随机码 CPLD 74LS74 EPM7128SLC-15ABSTRACTPseudorandom code is wide use in CDMA (Code Division Multiple Access)technology, to make use of CDMA technology,we should know Pseudorandom code Pulses. My design is based on CPLD technology ,and design a circuit to produce pseudorandom code. Device I used as follows:74LS74、EPM7128SLC84-15 MAX 7000 progranmable logic device 、some gate circuit and so on .At last ,we can use MAX+PLUSⅡsoftware and the board of CPLD which is comprehensive to inspect the application of this circuit is right or wrong.Keywords pseudorandom code;CPLD;74LS74;EPM7128SLC84-15 MAX 7000 progranmable logic device第1章绪论 (4)1.1伪随机序列的概念 (4)1.2伪随机序列的产生 (4)1..3几种伪随机序列的比较 (4)1.3.1 m序列 (4)1.3.2 M序列 (4)第2章主要元器件说明 (6)2.1 核心模块EPM7128SLC84-15 (6)2.1.1开关模块 (7)2.1.2 LED显示模块 (8)2.1.3 相关资源分配为: (9)2.2 74LS74 (10)2.2.1 74LS74引脚图 (10)2.2.2 74LS74功能表 (10)第3章原理图及逻辑示意图 (11)3.1原理框图 (11)3.1.1四级移位寄存器构成的m序列: (11)3.1.2四级移位寄存器构成的M序列: (11)3.2电路图 (12)3.2.1 四级移位寄存器构成的m序列: (12)3.2.2 四级移位寄存器构成的M序列: (13)第4章电路的时序波形及功能验证 (14)4.1 四级m序列: (14)4.2 四级M序列: (16)4.3 使用CPLD实验板检测电路功能是否达到实验要求: (18)第5章总结 (19)感谢辞 (20)参考文献 (21)第1章绪论在通信系统中,对误码率的测量、通信加密、数据序列的扰码和解码、扩频通信等方面均要用到伪随机序列,伪随机序列的特性对系统的性能有重要的影响,因此有必要了解和掌握伪随机序列的的概念和特性。