Design of crystal oscillators 水晶振荡器电路设计课件

- 格式:pdf

- 大小:2.35 MB

- 文档页数:34

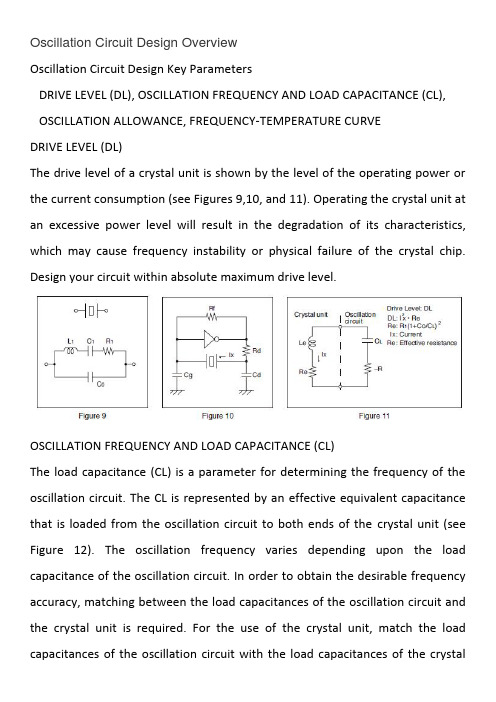

Oscillation Circuit Design OverviewOscillation Circuit Design Key ParametersDRIVE LEVEL (DL), OSCILLATION FREQUENCY AND LOAD CAPACITANCE (CL),OSCILLATION ALLOWANCE, FREQUENCY-TEMPERATURE CURVEDRIVE LEVEL (DL)The drive level of a crystal unit is shown by the level of the operating power or the current consumption (see Figures 9,10, and 11). Operating the crystal unit at an excessive power level will result in the degradation of its characteristics, which may cause frequency instability or physical failure of the crystal chip. Design your circuit within absolute maximum drive level.OSCILLATION FREQUENCY AND LOAD CAPACITANCE (CL)The load capacitance (CL) is a parameter for determining the frequency of the oscillation circuit. The CL is represented by an effective equivalent capacitance that is loaded from the oscillation circuit to both ends of the crystal unit (see Figure 12). The oscillation frequency varies depending upon the load capacitance of the oscillation circuit. In order to obtain the desirable frequency accuracy, matching between the load capacitances of the oscillation circuit and the crystal unit is required. For the use of the crystal unit, match the load capacitances of the oscillation circuit with the load capacitances of the crystalunit.OSCILLATION ALLOWANCETo ensure stable oscillation, the negative resistance of the circuit should be significantly larger than the equivalent series resistance (the oscillation allowance is large). Ensure that the oscillation allowance is at least five times as large as the equivalent series resistance.Oscillation Allowance Evaluation MethodAdd resistor "Rx" to the crystal unit in series and ensure that the oscillation starts or stops. The approximate negative resistance of the circuit is the value obtained by adding the effective resistance "Re" to the maximum resistance "Rx" when the oscillation starts or stops after gradually making Rx value larger. Negative resistance |- R| = Rx + Re|−R| is a value at least five times as large as the maximum equivalent series resistance (R1 max.) of the crystal unit.*Re is the effective resistance value during oscillation.Re = R1 (1 + CO/CL ) 2FREQUENCY-TEMPERATURE CURVEFrequency temperature characteristics of tuning fork crystals is shown by negative quadratic curve which has a peak at 25ºC as per left graph.Please make sure to consider the temperature range and frequency accuracy you need since magnitude of frequency variation becomes larger and larger as the temperature range becomes wider.[Approximation formula of frequency temperature characteristics]f_tem = B(T-Ti) 2B : Parabolic coefficientT : Given temperatureTi : Turnover temperature 。

石英晶体振荡器设计报告陈永平09电子C班0915241009一、设计要求A.晶体振荡器的工作频率在10MHZ以下(可为4MHZ、6MHZ、8MHZ)。

B.振荡器工作点可调,反馈元件可更换。

C.具有3组不同的负载阻抗。

D.电源电压为12V。

E.在10K负载上输出目测不失真电压波形Vopp≥4V。

震荡频率读出5位有效数字。

二、设计方案的论证A.电路形式:串联型石英晶体振荡器B.电路参数:1. 电路电阻:47k电位器一个,4.2k,4.7k,1.5k,620电阻各一个;2. 负载电阻:1k,10k,110k电阻各一个;3. 电容:103电容4个,102电容一个,101电容一个,152电容一个,可变电容一个;4. NPN三极管:9018 一个;5. 晶振:6Mhz一个;6. 电感:330uh,3.3uh各一个;C.参数估算:1.负载电阻变小时,输出电压幅度变小;负载电阻变大时,输出电压幅度变大。

2.调节Ct使谐振回路谐振频率与晶振的 fs 相同。

3.Rp减小时,输出电压幅度变大;Rp增大时,输出电压幅度变小。

D.设计内容的实现情况:负载上所测得的电压如下表:RL 1k 10k 110kVo-pp 3.33V 4.19V 4.19V三、电路图的分析和说明A.原理图:PCB图B.元器件功能1. 石英晶体:振荡回路的工作频率等于石英晶体的谐振频率fs时,石英晶体的高的阻抗近似为零;振荡回路的工作频率偏离石英晶体的频率fs时,石英晶体的阻抗骤然增加,近乎开路;综上,电路只能形成f=fs的振荡。

本实验中,采用的是6MHZ的晶振,因此回路输出6MHZ的振荡信号。

2. 9018高频管:9018是一种常用的高频(可到1.1GHz)小功率三极管。

它是一种小电压,小电流,小信号的NPN型硅三极管,常用在AM及FM放大电路,及FM/VHF调频本振电路中。

3. 电位器:调节电位器可改变静态工作点。

电路的直流通路如下图静态工作点的计算:U BQ=R2/(Rp+R1+R2)*VccI EQ=(UBQ-UBEQ)/R4I BQ=IEQ/(1+B)当Rp减小时,U BQ增大,从而I EQ增大,三级管的放大倍数B一般是固定的,所以I BQ遂I EQ的增大而增大;4. 可调电容:调节电路回路的频率与石英晶体振荡器的fs相同。

晶体Crystal振荡电路原理、分类及设计目录1.文档简介 (3)2.晶体振荡电路的工作原理 (3)2.1石英晶体特性 (3)2.2并联型晶体振荡电路 (4)2.3串联型晶体振荡电路 (6)3.时钟的重要参数 (6)4.晶体振荡器种类 (11)4.1普通晶体振荡器 (11)4.2温度补偿晶体振荡器 (12)4.3恒温晶体振荡器 (14)5.CRYSTAL(晶体)电路设计 (14)5.1晶体电路设计器件说明及选择 (15)5.2PCB布局设计 (16)6.晶体常见问题举例 (16)6.1不起振问题分析与解决 (16)6.2频偏过大 (17)7.总结 (17)附录一相关公式推导一 (18)附录二相关公式推导二 (20)1.文档简介本文主要介绍了晶体振荡电路的工作原理,时钟的重要参数,晶体振荡器的种类,晶体电路设计及晶体常见问题的举例。

2.晶体振荡电路的工作原理晶体(石英晶体)振荡电路主要由主振电路和石英谐振器组成,主振电路将直流能量转换成交流能量,振荡器频率主要取决于石英晶体谐振器。

振荡电路一般采用反馈型电路,按晶体在振荡电路中的作用,又可以分为串联型晶体振荡电路和并联型晶体振荡电路。

本章首先介绍石英晶体的特性,然后分别介绍并联型晶体振荡电路和串联型晶体振荡电路的结构及工作原理。

2.1石英晶体特性晶体(石英晶体)之所以能作为振荡器产生时钟,是基于它的压电效应:所谓的压电效应是指电和力的相互转化,即,如果在晶体的两端施加压缩或拉伸的力,晶体的两端会产生电压信号;同样的,在晶体的两端施加电压信号,晶体会产生形变。

而且这种转化在某特定的频率上效率最高,此频率(由晶片的尺寸和形状决定)即为晶体的谐振频率。

实际应用的晶片是由石英晶体按一定的方向切割而成的,晶片的形状可以各种各样,如方形、矩形或圆形等。

由于晶体的物理性质存在各向差异性,相同的晶体按不同晶格方向切下的晶片,会产生不同的物理特性。

因此,晶体的切割方法是非常重要的,对石英晶体来说,有AT/BT/DT/GT/IT/RT/FC/SC等不同的切法,要根据具体的需求选择相应的切法切割晶片,其中最常用的有AT切和SC切。

晶振电路设计

晶振电路是一种基础的时钟电路,其作用是提供可靠的、稳定的

时钟信号,用于驱动数字电路中的各种功能模块。

晶振电路的基本结

构包括晶振、共振电路和衰减补偿电路。

【晶振】

晶振是晶体振荡器的简称,是一种可以自发振荡的元器件。

晶振

的种类很多,常用的有二极管晶振、石英晶振、陶瓷晶振等。

在电路

设计中,需要根据具体的应用环境选择不同种类的晶振。

【共振电路】

共振电路是一种特殊的电路结构,可以使晶振产生强烈的振荡。

共振电路由电容器和电感器组成,通常称为谐振电路。

在晶振电路中,共振电路的设计非常关键,其参数的选择将直接影响电路的性能。

【衰减补偿电路】

衰减补偿电路是晶振电路中一个非常重要的组成部分,其作用是

为共振电路提供一定程度的电阻性质。

衰减补偿电路主要由电阻和电

容器组成,可以根据所需的衰减程度进行参数的选择。

综上所述,晶振电路的设计需要考虑多种因素,包括晶振的类型、共振电路的参数、衰减补偿电路的设计等。

在进行电路设计时,需要

根据具体的应用需求进行参数选择和优化。

AN2867应用笔记ST微控制器振荡器电路设计指南前言大多数设计者都熟悉基于Pierce(皮尔斯)栅拓扑结构的振荡器,但很少有人真正了解它是如何工作的,更遑论如何正确的设计。

我们经常看到,在振荡器工作不正常之前,多数人是不愿付出太多精力来关注振荡器的设计的,而此时产品通常已经量产;许多系统或项目因为它们的晶振无法正常工作而被推迟部署或运行。

情况不应该是如此。

在设计阶段,以及产品量产前的阶段,振荡器应该得到适当的关注。

设计者应当避免一场恶梦般的情景:发往外地的产品被大批量地送回来。

本应用指南介绍了Pierce振荡器的基本知识,并提供一些指导作法来帮助用户如何规划一个好的振荡器设计,如何确定不同的外部器件的具体参数以及如何为振荡器设计一个良好的印刷电路板。

在本应用指南的结尾处,有一个简易的晶振及外围器件选型指南,其中为STM32推荐了一些晶振型号(针对HSE及LSE),可以帮助用户快速上手。

目录ST微控制器振荡器电路设计指南目录1石英晶振的特性及模型32振荡器原理53Pierce振荡器64Pierce振荡器设计74.1反馈电阻R F74.2负载电容C L74.3振荡器的增益裕量84.4驱动级别DL外部电阻R Ext计算84.4.1驱动级别DL计算84.4.2另一个驱动级别测量方法94.4.3外部电阻R Ext计算 104.5启动时间104.6晶振的牵引度(Pullability) 10 5挑选晶振及外部器件的简易指南 11 6针对STM32™微控制器的一些推荐晶振 126.1HSE部分126.1.1推荐的8MHz晶振型号 126.1.2推荐的8MHz陶瓷振荡器型号 126.2LSE部分12 7关于PCB的提示 13 8结论141 石英晶振的特性及模型石英晶体是一种可将电能和机械能相互转化的压电器件,能量转变发生在共振频率点上。

它可用如下模型表示:图1石英晶体模型C0:等效电路中与串联臂并接的电容(译注:也叫并电容,静电电容,其值一般仅与晶振的尺寸有关)。

有源晶振(Oscillator)和⽆源晶振(Crystal)⽆源晶振有⼀个参数叫做负载电容(Load capacitance),负载电容是指在电路中跨接晶振两端的总的外界有效电容。

负载电容是⼯作条件,即电路设计时要满⾜负载电容等于或接近晶振数据⼿册给出的数值才能使晶振按预期⼯作。

⼀般情况下,增⼤负载电容会使振荡频率下降,⽽减⼩负载电容会使振荡频率升⾼。

通过初步的计算发现CL改变1pF,Fx可以改变⼏百Hz。

相关知识点:⼀、什么是负载电容?负载是指连接在电路中的电源两端的电⼦元件负载包括容性负载、阻性负载和感性负载三种。

电路中不应没有负载⽽直接把电源两极相连,此连接称为短路。

常⽤的负载有电阻、引擎和灯泡等可消耗功率的元件。

不消耗功率的元件,如电容,也可接上去,但此情况为断路。

容性负载的含义是指具有电容的性质(充放电,电压不能突变)即和电源相⽐当负载电流超前负载电压⼀个相位差时负载为容性(如负载为补偿电容)。

负载电容是指晶振的两条引线连接IC块内部及外部所有有效电容之和,可看作晶振在电路中串接了⼀个电容。

图中CI,C2这两个电容就叫晶振的负载电容,分别接在晶振的两个脚上和对地的电容,⼀般在⼏⼗⽪法它会影响到晶振的谐振频率和输出幅度,⼀般订购晶振时候供货⽅会问你负载电容是多少。

晶振的负载电容=[(C1*C2)/(C1+C2)]+Cic+△C式中C1,C2为分别接在晶振的两个脚上和对地的电容,Cic内部电容+△CPCB上电容经验值为3⾄5pf。

因此晶振的数据表中规定12pF的有效负载电容要求在每个引脚XIN 与 XOUT上具有22pF 2 * 12pF = 24pF = 22pF + 2pF 寄⽣电容。

两边电容为C1,C2,负载电容为:Cl,Cl=cg*cd/(cg+cd)+a就是说负载电容15pf的话两边两个接27pf的差不多了。

各种的晶振引脚可以等效为电容三点式。

晶振引脚的内部通常是⼀个反相器, 或者是奇数个反相器串联。

在半導體製程技術的不斷提升下,產品體積大幅縮小,對功能與運算時脈卻更為要求,因此,本文以晶體震盪電路的設計與量測為題,探討相關特性與技術。

由於科技的日新月異,IC內部的複雜度與精確度較從前大幅提升,所需的時脈速度也越來越高,相對的要求時脈的穩定度與精確度也大幅提昇,如何利用晶體(Crystal)來設計與量測所需的振盪電路,已經成為一個重要的課題,以下我們分成幾個部分加以討論。

電氣特性有鑑於其晶體電氣特性的複雜,我們針對晶體的電氣特性或是振盪電路有影響的部分,做一詳細討論,由於陶瓷/晶體的電器特性相似,所以也一併討論。

等效電路陶瓷/晶體雖然在電器特性上有些差異,但是等效電路(圖一)是相同的,雖然陶瓷振動的諧振現像,可以視為與晶體相同,但主要差異在陶瓷振動的振盪頻率,電感L1較小,串聯電容C1相當大,此乃意味著串聯諧振頻率(fs)與並聯諧振頻率(fa)差(即fs-fa)會變得相當寬闊。

圖一Crystal / Ceramic model圖二串聯共振並聯共振當晶體工作在串聯共振時,等效電路(圖二)阻抗在時是趨近於0,好的串聯共振線路設計,與負載電容無關,所以就不需要指定。

當晶體工作在並聯共振時,就像一電感在電路上,因此負載電容就非常重要,因為它可以決定振盪點的位置,如(圖三)所示。

而且電抗改變,頻率也跟隨著改變,所以在不同頻率與間,由、L1決定,在並聯線路的設計上,負載電容是需要指定的,如(圖四)所示。

圖三並聯共振頻率區域圖四並聯共振AT-CUT與BT-CUT典型的AT-CUT曲線是S形,BT-CUT曲線是拋物線形,如(圖五)所示;兩種Cut都對稱於室溫(25℃±3℃)。

在相同的頻率下,BT-CUT的Quartz blank相對的比A-CUT厚,因此提供較好的Yield 與低單價,在選擇適當的切割前,要注意的是他們所擁有的不同移動參數和頻率VS溫度特性。

圖五溫度曲線圖改變負載電容和PullabilityPullability是定義頻率與負載電容的關係,而負載電容是指與晶體串聯或是並聯的電容。

晶振电路的设计原理今天来聊聊晶振电路的设计原理。

咱先从生活中的一个现象说起吧。

不知道你有没有留意过摆钟,摆钟下面那个钟摆一下一下很有规律地摆动,滴答滴答地计时。

晶振电路就有点像这个摆钟的机芯,起着提供精准节拍,让整个系统有条不紊运行的作用呢。

晶振,就是晶体振荡器的简称。

通俗来讲,它能以非常精准且稳定的频率产生振动,这个频率就像是音乐里的节拍一样,在电子设备里十分关键。

我一开始接触晶振电路的时候,心里就直犯嘀咕,这么个小小的元件,是怎么做到这么精确的呢?打个比方,晶振就像是一个训练有素的鼓手,它能一直稳定、精确地敲出同一个节奏。

在晶振电路里有一个石英晶体,这是最重要的部分。

石英晶体具有一种很神奇的特性,叫做压电效应。

就好比是你轻轻按一下那种有弹性的东西,它会发生微小的形变,反过来,当对它施加电压的时候,它也会产生振动。

这个振动的频率非常稳定,比咱们人工能控制的要准确得多。

这就要说到晶振电路的设计了。

在设计的时候,得考虑好多因素,就像盖房子得考虑地基稳不稳、结构牢固不牢固一样。

首先,要根据电路需要的频率来选择合适的晶振。

比如说我们常见的一些电子产品,像手机里的晶振频率可能是几十兆赫兹,不同功能模块可能需要不同的频率晶振协同工作。

另外,电路里的电容、电阻等元件的取值也很讲究。

它们就像鼓手旁边的调音师,调试这个节奏的稳定性。

电容的值不合理,就可能导致这个“鼓手”敲出来的节拍不准。

在实际应用中,晶振电路无处不在。

就拿电脑主板来说吧,上面的晶振电路为CPU、各种芯片以及接口等提供时钟信号。

如果晶振电路出了问题,电脑可能就出现死机、程序无法运行等各种乱七八糟的问题。

老实说,我还在继续学习晶振电路的设计原理。

有时候也会遇到一些很困惑的现象,比如温度对晶振频率的影响。

温度可能会让石英晶体的参数发生一些细微变化,就像天气太热或太冷的时候,鼓手的状态可能也会有一点点不同。

这个时候可能就需要一些更特殊的设计或者矫正措施来保证晶振电路的准确性,不过这部分我还不是特别精通呢。

晶体振荡器设计报告晶体振荡器设计报告班级姓名学号年月日一、设计方案论证振荡器常用于高频发射机和接收机,频率稳定性是衡量振荡器性能的重要参数之一,而石英晶体因其频率的高稳定性得到广泛的应用,依据右图所示的晶体的电抗特性曲线,在串并联谐振频率之间很狭窄的工作频带内,它呈现电感性,因而石英谐振器或者工作在感性区,或者工作于串联谐振频率上,不能工作在容性区,因为此时无法判断晶体是否工作,从而也不能保证频率的稳定度。

因此,根据晶体在电路中的作用原理,振荡器可分为两类:一类是石英晶体在振荡器线路中作为等效电感元件使用,称为并联谐振型晶体振荡器;另一类是把石英晶体作为串联谐振元件使用,使它工作于串联谐振频率上,串联谐振型晶体振荡器。

1. 晶体振荡器连接方式的选取并联谐振c-b型晶体振荡器的典型电路如右图所示。

振荡管的基极对高频接地,晶体管接在集电极和基极之间,C2与C5为回路的另外两个电抗元件,它类似于克拉泼振荡器,晶体振荡器的谐振回路与振荡管之间的耦合电容非常弱,从而使频率稳定性大大提高,因此本设计实验采用这种连接方案。

2. 输出缓冲级设计输出缓冲级主要完成对所产生的振荡信号进行输出,不管是并联谐振晶振电路还是串联谐振晶振电路,它们的带负载能力都不是很强,负载值改变时可能造成振荡器的输出频率变化,也可能影响振荡器的输出幅度,输出缓冲级的作用就是提高整个振荡器的带负载能力,即使得振荡器的输出特性不受负载影响,或影响较小。

常用的输出缓冲级是在电路的输出端加一射极跟随器,从而提高回路的带负载能力。

设计跟随器的特点是输入阻抗高,输出阻抗低,电压放大倍数略低于1,带负载能力强,具有较高的电流放大能力,它可以起到阻抗变换和级间隔离的作用,因而可以减小负载对于振荡回路的影响,射极跟随器的典型电路如右图所示。

3. 系统原理图设计依据各部分的方案设计并结合设计要求,综合考虑各种影响因素,设计系统原理图如下图所示。

图中R1和R2分压为三极管T1提供偏置电压,通过改变Rp1阻值的大小可以改变T1的静态工作点,C1用于在振荡器起振时将R1短路从而可以使振荡器正常振荡,C2、C5组成反馈分压,用于为振荡器提供反馈信号,它们与石英晶振共同构成了电容三点式振荡器电路,此时晶体相当于一等效电感,T2连接成射极跟随器,用于提高系统的带负载能力,RL1、RL2、RL3为三组负载。

石英晶体正弦振荡器电路图

石英晶体正弦振荡器电路图

如图所示电路是由石英谐振晶体SJT和六反相器集成电路CD4069的1个门A构成的正弦波振荡器。

与普通的RC移相振荡器相比,晶体振荡器的频率稳定度可高达10-5或更高。

这是RC移相振荡器无法达到的高指标(RC移相振荡器的频率稳定度只能达到10-2的量级)。

CMOS非门与负反馈偏置电阻Rl构成反相放大电路。

石英晶体SJT与Cl、C2构成7c型正反馈支路。

石英晶体在其固有谐振频率的附近,自身呈感性,此电感与电容Cl、C2构成谐振回路,形成选频移相反馈网络反馈到放大器输入端,产生振荡。

调整电容C2可微调振荡频率。

元器件选择:

六反相器集成块A:CD4069。

电容Cl:20pF,C2:3~22pF,C3:1000pF。

电阻Rl:10MΩ。

石英晶体SJT:32.768kHz。

电路连接方法:

六反相器集成电路CD4069只用了1/6个门,剩余门若无它用可将输入端接VDD或VSS,输出端悬空。

14脚(VDD)接正电源,7脚(VSS)接地。