Quectel_M72-D硬件设计手册

- 格式:pdf

- 大小:1.51 MB

- 文档页数:60

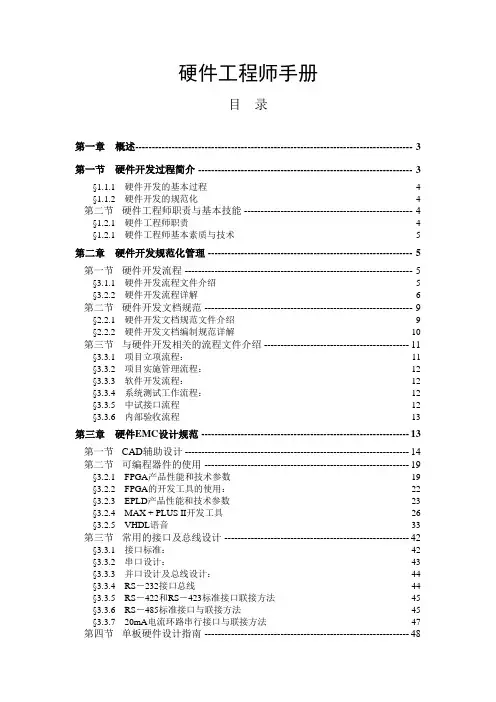

硬件工程师手册目录第一章概述------------------------------------------------------------------------------------ 3第一节硬件开发过程简介 ----------------------------------------------------------------- 3§1.1.1 硬件开发的基本过程 ----------------------------------------------------------------------- 4§1.1.2 硬件开发的规范化 -------------------------------------------------------------------------- 4第二节硬件工程师职责与基本技能 --------------------------------------------------- 4§1.2.1 硬件工程师职责 ----------------------------------------------------------------------------- 4§1.2.1 硬件工程师基本素质与技术-------------------------------------------------------------- 5第二章硬件开发规范化管理 -------------------------------------------------------------- 5第一节硬件开发流程 --------------------------------------------------------------------- 5§3.1.1 硬件开发流程文件介绍 -------------------------------------------------------------------- 5§3.2.2 硬件开发流程详解 -------------------------------------------------------------------------- 6第二节硬件开发文档规范 --------------------------------------------------------------- 9§2.2.1 硬件开发文档规范文件介绍-------------------------------------------------------------- 9§2.2.2 硬件开发文档编制规范详解------------------------------------------------------------ 10第三节与硬件开发相关的流程文件介绍 -------------------------------------------- 11§3.3.1 项目立项流程: ---------------------------------------------------------------------------- 11§3.3.2 项目实施管理流程: --------------------------------------------------------------------- 12§3.3.3 软件开发流程: --------------------------------------------------------------------------- 12§3.3.4 系统测试工作流程: --------------------------------------------------------------------- 12§3.3.5 中试接口流程------------------------------------------------------------------------------- 12§3.3.6 内部验收流程------------------------------------------------------------------------------- 13第三章硬件EMC设计规范 --------------------------------------------------------------- 13第一节CAD辅助设计 -------------------------------------------------------------------- 14第二节可编程器件的使用 -------------------------------------------------------------- 19§3.2.1 FPGA产品性能和技术参数 ------------------------------------------------------------- 19§3.2.2 FPGA的开发工具的使用: ------------------------------------------------------------- 22§3.2.3 EPLD产品性能和技术参数 ------------------------------------------------------------- 23§3.2.4 MAX + PLUS II开发工具---------------------------------------------------------------- 26§3.2.5 VHDL语音 ---------------------------------------------------------------------------------- 33第三节常用的接口及总线设计 -------------------------------------------------------- 42§3.3.1 接口标准:---------------------------------------------------------------------------------- 42§3.3.2 串口设计:---------------------------------------------------------------------------------- 43§3.3.3 并口设计及总线设计: ------------------------------------------------------------------ 44§3.3.4 RS-232接口总线 ------------------------------------------------------------------------- 44§3.3.5 RS-422和RS-423标准接口联接方法---------------------------------------------- 45§3.3.6 RS-485标准接口与联接方法 --------------------------------------------------------- 45§3.3.7 20mA电流环路串行接口与联接方法------------------------------------------------- 47第四节单板硬件设计指南 -------------------------------------------------------------- 48§3.4.1 电源滤波:---------------------------------------------------------------------------------- 48§3.4.2 带电插拔座:------------------------------------------------------------------------------- 48§3.4.3 上下拉电阻:------------------------------------------------------------------------------- 49§3.4.4 ID的标准电路 ------------------------------------------------------------------------------ 49§3.4.5 高速时钟线设计 --------------------------------------------------------------------------- 50§3.4.6 接口驱动及支持芯片 --------------------------------------------------------------------- 51§3.4.7 复位电路------------------------------------------------------------------------------------- 51§3.4.8 Watchdog电路 ------------------------------------------------------------------------------ 52§3.4.9 单板调试端口设计及常用仪器 -------------------------------------------------------- 53第五节逻辑电平设计与转换 ----------------------------------------------------------- 54§3.5.1 TTL、ECL、PECL、CMOS标准 ----------------------------------------------------- 54§3.5.2 TTL、ECL、MOS互连与电平转换 -------------------------------------------------- 66第六节母板设计指南 -------------------------------------------------------------------- 67§3.6.1 公司常用母板简介 ------------------------------------------------------------------------ 67§3.6.2 高速传线理论与设计 --------------------------------------------------------------------- 70§3.6.3 总线阻抗匹配、总线驱动与端接 ----------------------------------------------------- 76§3.6.4 布线策略与电磁干扰 --------------------------------------------------------------------- 79第七节单板软件开发 -------------------------------------------------------------------- 81§3.7.1 常用CPU介绍 -------------------------------------------------------------------------------- 81§3.7.2 开发环境 -------------------------------------------------------------------------------------- 82§3.7.3 单板软件调试 -------------------------------------------------------------------------------- 82§3.7.4 编程规范 -------------------------------------------------------------------------------------- 82第八节硬件整体设计 -------------------------------------------------------------------- 88§3.8.1 接地设计------------------------------------------------------------------------------------- 88§3.8.2 电源设计------------------------------------------------------------------------------------- 91第九节时钟、同步与时钟分配 -------------------------------------------------------- 95§3.9.1 时钟信号的作用 --------------------------------------------------------------------------- 95§3.9.2 时钟原理、性能指标、测试----------------------------------------------------------- 102第十节DSP技术 ------------------------------------------------------------------------- 108§3.10.1 DSP概述----------------------------------------------------------------------------------- 108§3.10.2 DSP的特点与应用 ---------------------------------------------------------------------- 109§3.10.3 TMS320 C54X DSP硬件结构------------------------------------------------------ 110§3.10.4 TMS320C54X的软件编程 ------------------------------------------------------------ 114第四章常用通信协议及标准 ----------------------------------------------------------- 120第一节国际标准化组织 ----------------------------------------------------------------------- 120§4.1.1 ISO ------------------------------------------------------------------------------------ 120§4.1.2 CCITT及ITU-T --------------------------------------------------------------------- 121§4.1.3 IEEE ----------------------------------------------------------------------------------- 121§4.1.4 ETSI ----------------------------------------------------------------------------------- 121§4.1.5 ANSI ---------------------------------------------------------------------------------- 122§4.1.6 TIA/EIA ------------------------------------------------------------------------------ 122§4.1.7 Bellcore ------------------------------------------------------------------------------- 122第二节硬件开发常用通信标准-------------------------------------------------------------- 122§4.2.1 ISO开放系统互联模型 ----------------------------------------------------------- 122§4.2.2 CCITT G系列建议 -------------------------------------------------------------- 123§4.2.3 I系列标准----------------------------------------------------------------------------------- 125§4.2.4 V系列标准 ---------------------------------------------------------------------------- 125§4.2.5 TIA/EIA 系列接口标准---------------------------------------------------------- 128§4.2.5 CCITT X系列建议 -------------------------------------------------------------- 130参考文献 ----------------------------------------------------------------------------------------------- 132第五章物料选型与申购 ----------------------------------------------------------------- 132第一节物料选型的基本原则 -------------------------------------------------------------------- 132第二节IC的选型------------------------------------------------------------------------------------ 134第三节阻容器件的选型 -------------------------------------------------------------------------- 137第四节光器件的选用------------------------------------------------------------------------------ 141第五节物料申购流程------------------------------------------------------------------------------ 144第六节接触供应商须知 -------------------------------------------------------------------------- 145第七节MRPII及BOM基础和使用-------------------------------------------------------------- 146第一章概述第一节硬件开发过程简介§1.1.1 硬件开发的基本过程产品硬件项目的开发,首先是要明确硬件总体需求情况,如CPU处理能力、存储容量及速度,I/O端口的分配、接口要求、电平要求、特殊电路(厚膜等)要求等等。

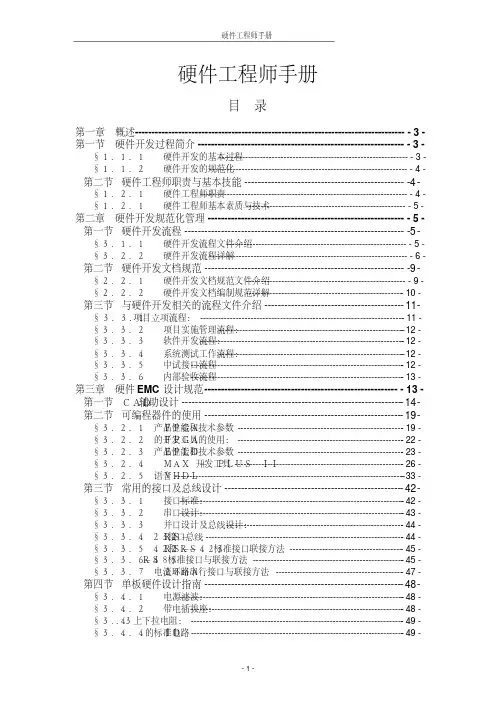

硬件工程师手册 目录第一章概述--------------------------------------------------------------------------------- - 3 -第一节硬件开发过程简介 -------------------------------------------------------------- - 3 ----------------------------------------------------------------- - 3 -§1.1.1 硬件开发的基本过程§1.1.2 硬件开发的规范化------------------------------------------------------------------- - 4 -第二节 硬件工程师职责与基本技能 ------------------------------------------------ -4----------------------------------------------------------------------- - 4 -§1.2.1 硬件工程师职责§1.2.1 硬件工程师基本素质与技术------------------------------------------------------ - 5 -第二章硬件开发规范化管理 ----------------------------------------------------------- - 5 -第一节 硬件开发流程 ------------------------------------------------------------------ -5-§3.1.1 硬件开发流程文件介绍------------------------------------------------------------- - 5 -------------------------------------------------------------------- - 6 -§3.2.2 硬件开发流程详解第二节 硬件开发文档规范 ------------------------------------------------------------ -9-§2.2.1 硬件开发文档规范文件介绍------------------------------------------------------ - 9 ------------------------------------------------------ - 10 -§2.2.2 硬件开发文档编制规范详解第三节 与硬件开发相关的流程文件介绍 ----------------------------------------- -11-§3.3.1 项目立项流程: --------------------------------------------------------------------- - 11 ---------------------------------------------------------------- - 12 -§3.3.2 项目实施管理流程:--------------------------------------------------------------------- - 12 -§3.3.3 软件开发流程:§3.3.4 系统测试工作流程:--------------------------------------------------------------- - 12 ------------------------------------------------------------------------- - 12 -§3.3.5 中试接口流程------------------------------------------------------------------------ - 13 -§3.3.6 内部验收流程第三章硬件EMC设计规范---------------------------------------------------------- - 13 -辅助设计 ------------------------------------------------------------------ -14-第一节 CAD第二节 可编程器件的使用 ----------------------------------------------------------- -19-§3.2.1 FPGA产品性能和技术参数-------------------------------------------------------- - 19 -的开发工具的使用:-------------------------------------------------------- - 22 -§3.2.2 FPGA产品性能和技术参数-------------------------------------------------------- - 23 -§3.2.3 EPLD§3.2.4 MAX + PLUS II开发工具 --------------------------------------------------------- - 26 -语音 ------------------------------------------------------------------------------ - 33 -§3.2.5 VHDL第三节常用的接口及总线设计 ----------------------------------------------------- -42----------------------------------------------------------------------------- - 42 -§3.3.1 接口标准:---------------------------------------------------------------------------- - 43 -§3.3.2 串口设计:§3.3.3 并口设计及总线设计:------------------------------------------------------------ - 44 -232接口总线------------------------------------------------------------------- - 44 -§3.3.4 RS-和RS-423标准接口联接方法 -------------------------------------- - 45 -422§3.3.5 RS-标准接口与联接方法 --------------------------------------------------- - 45 --485§3.3.6 RS电流环路串行接口与联接方法 ------------------------------------------- - 47 -§3.3.7 20mA第四节 单板硬件设计指南 ----------------------------------------------------------- -48----------------------------------------------------------------------------- - 48 -§3.4.1 电源滤波:------------------------------------------------------------------------ - 48 -§3.4.2 带电插拔座:上下拉电阻: ------------------------------------------------------------------------ - 49 -.3 §3.4的标准电路------------------------------------------------------------------------ - 49 -§3.4.4 ID§3.4.5 高速时钟线设计--------------------------------------------------------------------- - 50 ---------------------------------------------------------------- - 51 -§3.4.6 接口驱动及支持芯片------------------------------------------------------------------------------- - 51 -§3.4.7 复位电路§3.4.8 Watchdog电路------------------------------------------------------------------------ - 52 --------------------------------------------------- - 53 -§3.4.9 单板调试端口设计及常用仪器第五节 逻辑电平设计与转换 -------------------------------------------------------- -54-§3.5.1 TTL、、CMOS标准----------------------------------------------------- - 54 -、PECLECL、MOS互连与电平转换 ------------------------------------------------ - 66 -ECL§3.5.2 TTL、第六节 母板设计指南 ----------------------------------------------------------------- -67------------------------------------------------------------------- - 67 -§3.6.1 公司常用母板简介--------------------------------------------------------------- - 70 -§3.6.2 高速传线理论与设计----------------------------------------------- - 76 -§3.6.3 总线阻抗匹配、总线驱动与端接--------------------------------------------------------------- - 79 -§3.6.4 布线策略与电磁干扰第七节 单板软件开发 ----------------------------------------------------------------- -81-介绍 -------------------------------------------------------------------------- - 81 -CPU§3.7.1 常用-------------------------------------------------------------------------------- - 81 -§3.7.2 开发环境§3.7.3 单板软件调试-------------------------------------------------------------------------- - 82 --------------------------------------------------------------------------------- - 82 -§3.7.4 编程规范第八节 硬件整体设计 ----------------------------------------------------------------- -88-§3.8.1 接地设计------------------------------------------------------------------------------- - 88 -------------------------------------------------------------------------------- - 90 -§3.8.2 电源设计第九节 时钟、同步与时钟分配 ----------------------------------------------------- -95---------------------------------------------------------------------- - 95 -§3.9.1 时钟信号的作用--------------------------------------------------- - 102 -§3.9.2 时钟原理、性能指标、测试技术 ---------------------------------------------------------------------- -108-第十节 DSP概述 ---------------------------------------------------------------------------- - 108 -§3.10.1 DSP§3.10.2 DSP的特点与应用 --------------------------------------------------------------- - 109 -硬件结构 ------------------------------------------------- - 110 -§3.10.3 TMS320 C54X DSP的软件编程 ------------------------------------------------------- - 114 -§3.10.4 TMS320C54X第四章常用通信协议及标准 -------------------------------------------------------- - 120 -国际标准化组织 ------------------------------------------------------------------- - 120 -第一节 --------------------------------------------------------------------------------- - 120 -§4.1.1 ISO----------------------------------------------------------------- - 121 -§4.1.2 CCITT及ITU-T------------------------------------------------------------------------------- - 121 -§4.1.3 IEEE------------------------------------------------------------------------------- - 121 -§4.1.4 ETSI§4.1.5 ANSI------------------------------------------------------------------------------- - 122 --------------------------------------------------------------------------- - 122 -§4.1.6 TIA/EIA------------------------------------------------------------------------- - 122 -§4.1.7 Bellcore硬件开发常用通信标准---------------------------------------------------------- - 122 -第二节 开放系统互联模型------------------------------------------------------- - 122 -§4.2.1 ISO系列建议 ----------------------------------------------------------- - 123 -§4.2.2 CCITT G§4.2.3 I系列标准 -------------------------------------------------------------------------- - 125 -§4.2.4 V系列标准 ------------------------------------------------------------------------ - 125 -系列接口标准------------------------------------------------------ - 128 -§4.2.5 TIA/EIA 系列建议 ----------------------------------------------------------- - 130 -§4.2.5 CCITT X参考文献 ------------------------------------------------------------------------------------------- - 132 -第五章物料选型与申购 -------------------------------------------------------------- - 132 -第一节 物料选型的基本原则 ---------------------------------------------------------------- - 132 -第二节 IC的选型 ------------------------------------------------------------------------------- - 134 -第三节 阻容器件的选型 ---------------------------------------------------------------------- - 137 -第四节 光器件的选用-------------------------------------------------------------------------- - 141 -第五节 物料申购流程-------------------------------------------------------------------------- - 144 -第六节 接触供应商须知 ---------------------------------------------------------------------- - 145 -基础和使用----------------------------------------------------------- - 146 -第七节 MRPII及BOM第一章概述第一节硬件开发过程简介硬件开发的基本过程 §1.1.1 产品硬件项目的开发,首先是要明确硬件总体需求情况,如CPU处理能力、存储容量及速度,I/O端口的分配、接口要求、电平要求、特殊电路(厚膜等)要求等等。

FTU硬件详细设计说明书产品线:配电终端产品类别:产品型号:产品版本:批准:审核:初审:编写:1.引言 (4)1.1.前言 (4)1.2.文档术语 (4)1.3.参考文档 (4)2.开发环境 (4)3.硬件详细设计 (5)3.1.系统架构 (5)3.2.主板 (5)3.2.1.主板硬件框图 (6)3.2.2.模块1:CPU核心板 (6)3.2.3.模块2:时钟模块 (18)3.2.4.模块3:无线通讯 (19)3.2.5.模块6 以太网接口 (24)3.2.6.RS232/RS485电路 (26)3.2.7.SD卡模块电路 (27)3.2.8.直流量采集模块 (28)B HOST接口 (30)3.3.遥控遥信板 (31)3.3.1.硬件框图 (31)3.3.2.遥信电路模块 (31)3.3.3.遥控电路模块 (33)3.4.遥测板 (34)3.4.1.遥测板框图 (34)3.4.2.遥测电路模块 (34)3.4.3.电源模块 (38)3.4.4. (40)3.4.5.元器件总成本: (40)3.5.硬件测试方法 (40)4.FPGA逻辑设计 (41)4.1.子板逻辑 (41)4.1.1.架构概述 (42)4.2.主板逻辑 (44)5.结构工艺设计 (45)5.1.外观设计................................................................................... 错误!未定义书签。

5.1.1.外形结构........................................................................... 错误!未定义书签。

5.1.2.铭牌................................................................................... 错误!未定义书签。

中兴通讯 MG3732模块用户硬件设计手册版本:V1.0中兴通讯股份有限公司版权声明Copyright © 2006 by ZTE Corporation本资料著作权属中兴通讯股份有限公司所有。

未经著作权人书面许可,任何单位或个人不得以任何方式摘录、复制或翻译。

为中兴通讯股份有限公司所有商标。

侵权必究。

本手册中出现的其他公司商标,由商标拥有公司所有。

中兴通讯保留修改本手册技术参数及规格的权力,对本手册中的印刷错误及与最新资料不符之处我们会及时改进。

所有这些改动不再事先通知,但会编入新版手册中。

中兴通讯拥有本手册的最终解释权。

中兴通讯拥有雄厚的技术实力,可为CDMA/GPRS等通讯模块客户提供全方位的技术支持,支持内容包括:1、提供完善的技术资料;2、提供可用于研发、测试、生产、售后等环节的开发板;3、提供原理图、PCB、测试方案等评审和技术会诊;4、提供测试环境。

中兴通讯为客户提供现场、电话、网站、即时通讯、E-MAIL等多种支持方式。

中兴通讯模块网站,提供相关的行业信息和模块相关技术资料。

授权的模块客户可以在网站下载模块最新的相关技术资料。

如果您有更多的需求,可发送邮件至module@。

您还可以拨打技术支持热线:0755-********。

概述本文档适用的产品是:MG3732模块。

本文档通过对MG3732模块的介绍,用以指导用户对该模块进行硬件设计,并在该模块基础上更方便快捷的进行各种终端无线产品的设计。

阅读对象本文档主要适用于以下工程师:●系统设计工程师●结构工程师●硬件工程师●软件工程师●测试工程师内容简介本文档包含6章,内容如下:章节内容1 概述介绍MG3732模块的基本技术规格、参考涉及的相关文档和缩略语。

2 产品介绍简要介绍MG3732模块产品的原理图。

3 引脚描述介绍MG3732模块引脚名称和功能。

4 硬件接口描述介绍MG3732模块各部分的硬件接口设计。

5 结构介绍MG3732模块的外观图、装配图和主板PCB布线图。

项目名称:E-DMR数字对讲机芯片文件编号:HR3.002.8008.--项目编号:HR3.002 秘密硬件电路设计说明书V3文档版本号3.0编 写 人:赵 华编写时间:2009-9-17部 门:系统部审 核 人:陈沪东、审核时间:修订历史(Revision History)编号修订内容描述修订日期修订后版本号修订人批准人1 建立硬件电路设计说明书 2009-9-17 1.0赵华陈沪东2 修改音频设计,增加FM 2009-12-3 2.0赵华3 修改AD/DA以及电源设计,去除FM,修改文档格式2010-3-15 3.0 赵华目 录1.引言 (1)1.1.编写目的 (1)1.2.产品背景 (1)1.3.定义 (1)1.4.参考资料 (1)2.硬件系统概述 (3)2.1.功能需求 (3)2.2.总体方案 (3)2.3.系统接口 (4)3.硬件系统详细设计 (6)3.1.处理板详细设计 (6)3.1.1. 处理板指标 (6)3.1.2. 处理板功能模块说明 (6)3.1.3. 关键元器件 (11)3.2.射频板详细设计 (12)3.2.1. 射频板指标: (12)3.2.2. 射频板功能模块说明 (12)3.2.3. 关键元器件 (12)4.开发环境 (13)5.附录 (14)1.引言1.1.编写目的本文档是E-DMR开发板V3.0的硬件设计说明文档,它详细描述了整个硬件模块的设计原理,其主要目的是为E-DMR开发板的原理图设计提供依据,并作为PCB设计、软件驱动设计和上层应用软件设计的参考和设计指导。

1.2.产品背景无线对讲机由于具有即时通信、经济实用、成本低廉、使用方便以及无需通信费等优点,因此广泛应用在民用、紧急事件处理等方面。

尤其在紧急事件处理以及没有手机网络覆盖的情况,对讲机更加显示出它的不可取代的地位。

如今,模拟对讲机仍然占据绝大部分的市场,但是由于数字通信可以提供更丰富的业务种类,更好的业务质量、保密特性和连接性,以及更高的频谱效率,因此数字对讲机的研究、生产和使用是与时俱进的,符合信息化、数字化发展的必然趋势。

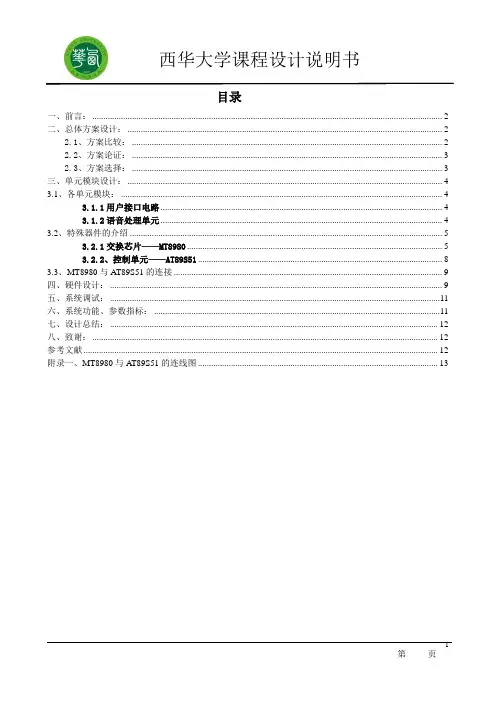

目录一、前言: (2)二、总体方案设计: (2)2.1、方案比较: (2)2.2、方案论证: (3)2.3、方案选择: (3)三、单元模块设计: (4)3.1、各单元模块: (4)3.1.1用户接口电路 (4)3.1.2语音处理单元 (4)3.2、特殊器件的介绍 (5)3.2.1交换芯片——MT8980 (5)3.2.2、控制单元——AT89S51 (8)3.3、MT8980与AT89S51的连接 (9)四、硬件设计: (9)五、系统调试: (11)六、系统功能、参数指标: (11)七、设计总结: (12)八、致谢: (12)参考文献 (12)附录一、MT8980与AT89S51的连线图 (13)一、前言:通信网是由用户终端设备、传输设备和交换设备组成。

它由交换设备完成接续,使网内任一用户可与其他用户通信。

程控交换机是数字电话网、移动电话网及综合业务数字网中的关键设备,在通信网中起着非常重要的作用。

而交换机的基本功能是实现任意入线与任意出线之间的互连,即实现任意两个用户之间的信息交换。

为此,交换机的基本组成应包括接口、交换网络和控制系统玩个部分。

接口的作用是将来自不同终端或其他交换机的各种传输信号转换成统一的交换机内部工作信号,并按信号的性质分别将信令传送给控制系统,将消息传送给交换网络。

交换网络的任务是实现各入、出线上信号的传递或接续。

控制系统负责处理信令,按信令的要求控制交换网络完成接续,通过接口发送必要的信令,并协调整个交换机的工作。

程控就是存储程序控制,程控交换是利用计算机软件进行控制的一种交换方式,故程控交换机是电子计算机控制的交换机。

二、总体方案设计:2.1、方案比较:方案一:小型程控交换机模拟了程控交换网中的电路交换的全过程,其基本结构可分为话路系统和控制系统两部分。

整个系统主要由用户接口电路、语音处理单元和交换网络与中心控制单元组成。

其原理框图如下小型程控交换机原理框图2.1.1所示:图2.1.1:小型程控交换机原理框图方案二:VLAN以太交换机,能够使中小企业的多台电脑,根据按照管理权限而不拘泥于部门自由组成多个小型虚拟局域网(VLAN)接入互联网,同时,VLAN之间彼此可以安全隔离,从根本上提高了网络性能。

Thank You!感谢您购买:消费机。

消费机使用RS485网络通讯技术。

消费机是在总结以往消费机各种缺点和用户需求等的基础上开发的专业消费设备。

专门针对食堂、餐厅、超市、食堂、餐厅、小卖部等消费场所设计,淘汰以往采用的现金、饭票、ID 卡、接触式智能卡等消费结账方式,使用Philips Mifare One S50非接触式IC卡作为电子钱包,提供强大的卡保密性能和更轻松简洁的消费方式。

有效的解决了传统的饭票流通所带来的不卫生、零钱不够找、偷饭票、伪造饭票等一系列让管理者费尽心思的疑难问题。

台式消费机集成了最新的MCU,可以存储10000条感应卡消费记录,使用人数无限制,联网设备无限制,可无限扩展使用人员,无限扩展使用场地。

内置后备电池,断电后能继续使用长达8小时的不间断工作,消费信息不会因电源断电而丢失,确保消费系统良好的运行,保证消费信息的安全。

台式消费机高可靠高稳定,功能强大安装简便,是应用于超市、食堂、餐厅、小卖部及大型消费场所的最好消费设备。

请在使用本机前阅读本说明书,并将其保存好以备将来参考。

感谢您对我司的支持,感谢您选购我们的一卡通系统。

我们将为您提供最优质的服务。

目录一.设备外观 (3)二.消费系统配置表 (4)三.详细参数 (5)四.键盘标识 (9)五.消费、充值及查询 (19)六.网线连接 (3)七.系统拓补示意图 (4)八.系统组成部份 (5)九.硬件菜单操作 (3)十.新机快速操作 (9)十一.维护与保养 (19)一.设备外观出厂默设置二.消费系统配置表标准配置表其它配套设备三.详细参数基本参数设备特性⏹消费机采用RS485 局域网通讯技术;⏹消费机可查询IC卡余额、最近一次消费金额、总消费金额及次数;⏹消费机支持联网和脱网工作,联网时,支持实时采集并显示即时消费记录;⏹消费机支持定额消费模式、不定额消费模式;⏹消费刷卡记录采用固化芯片储存方式储存,掉电数据不丢失;⏹软件系统可扩展考勤、门禁,实现1张IC卡1个数据库1个管理软件进行一卡通管理;⏹支持误操作退款,可退回最近一次的消费金额;⏹使用消费机键盘操作即可轻松统计并显示当天消费记录的总和;⏹支持个人与全体两种折扣功能;⏹支持订餐功能,有效防止食物浪费;⏹支持信息查询机,可查询卡内金额情况、清费记录、持卡人姓名等信息⏹具备日限额、次限额等,有效防止恶意消费⏹具备卡有效期限制功能⏹具备交易回退功能:扣错款的情况下,可回退该笔交易;⏹双面2行数码显示屏,可显示余额、消费额等⏹本机自带后备电源,即使在停电的情况下也能连续工作8小时以上四.键盘标识台式消费机使用键盘操作。

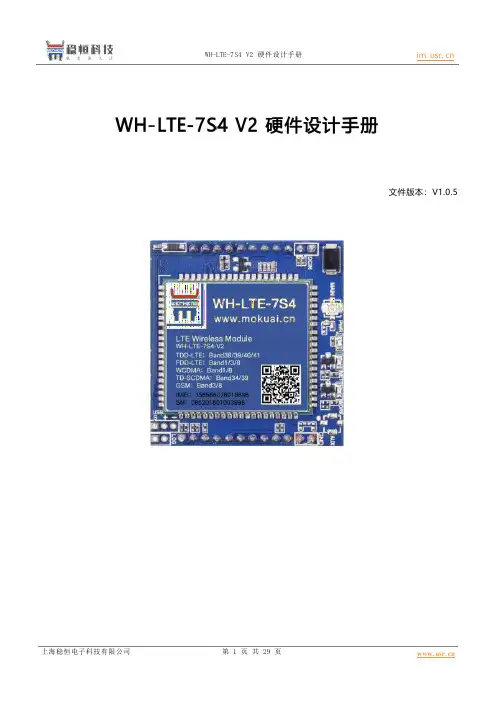

文件版本:V1.0.5WH-LTE-7S4V2硬件设计手册 (1)1.关于文档 (4)1.1.文档目的 (4)1.2.产品外观 (4)1.3.参考文档列表 (4)2.产品简介 (5)2.1.基本参数 (5)2.2.模块应用框图 (6)2.3.引脚定义 (7)2.4.开发套件 (10)3.硬件参考设计 (11)3.1.外围电路框架参考 (11)3.2.电源接口 (11)B接口 (13)3.4.UART接口 (14)3.5.SIM卡接口 (16)3.6.MCU开关机接口 (18)3.7.LED输出控制 (19)3.8.复位控制和恢复出厂设置控制功能 (21)4.电气特性 (22)4.1.工作存储温度 (22)4.2.输入电源 (22)4.3.模块IO口电平 (22)4.4.IO驱动电流 (23)5.机械特性 (24)5.1.回流焊建议 (24)5.2.外形尺寸 (25)6.联系方式 (27)7.免责声明 (28)8.更新历史 (29)本文详细阐述了WH-LTE-7S4V2系列通讯模块的基本功能和主要特点、硬件接口及使用方法、结构特性等电气指标。

通过阅读本文档,用户可以对本产品有整体认识,对产品规格参数有明确了解,顺利将模块嵌入各种终端设计中。

图片1实物图除此硬件开发文档外,我们同时提供了基于本产品的说明书、封装库等资料,方便用户设计参考,客户可到官方网站查看下载:https:///Product/179.html参数列表产品规格项目描述产品名称WH-LTE-7S4V2支持移动2G/3G/4G支持联通2G/3G/4G支持电信4GDIP23pin硬件接口封装形式DIP23pin电源 3.4V~4.2V/5~16VLED模块状态指示灯功能UART TTL3.3V/5VSIM/USIM卡标准6针SIM卡接口,3V/1.8V SIM卡USB协议USB2.0High speed天线IPEX座外形尺寸尺寸(毫米)长*宽*高=44.4mm×41.8mm×12.5mm(含插针高度)重量(克)15g温度范围工作温度-20℃~+70℃存储温度-40℃~+85℃湿度范围工作湿度5%~95%技术规范TD-LTE3GPP R9CAT4下行150Mbps,上行50MbpsFDD-LTE3GPP R9CAT4下行150Mbps,上行50MbpsWCDMA HSPA+下行速率21Mbps上行速率5.76MbpsTD-SCDMA3GPP R9下行速率2.8Mbps上行速率 2.2MbpsGSM下行速率384kbps上行速率128kbps 频段TD-LTE Band38/39/40/41FDD-LTE Band1/3/8WCDMA Band1/8TD-SCDMA Band34/39GSM Band3/8功率等级TD-LTEBand+23dBm(Power class3)38/39/40/41FDD-LTEBand1/3/8+23dBm(Power class3)WCDMABand1/8+23dBm(Power class3TD-SCDMABand34/39+24dBm(Power class2)GSM Band8+33dBm(Power class4)GSM Band3+30dBm(Power class1)软件功能数据业务支持PPPD/RNDIS/ECM拨号短信支持PDU/TEXT短信TCP/IP协议IPv4,IPv6,IPv4/IPv6双堆栈操作系统支持windows/linux/Android数据传输支持简单透传功能,HTTPD功能,UDC功能辅助功能心跳包,注册包,套接字协议,FTP升级,基站定位参数配置串口,网络和短信AT指令配置目前模块开放的接口包括:电源输入,复位重启控制,恢复出厂设置控制,UART,SIM,射频接口。

Quectel 模块模块介绍介绍介绍说明说明Quectel GPS Module FamilyGPS 模块主要有:L10,L20,L30,L10-C (L10的cost down 版)L10:28 PIN SMD 封装,与U-BLOX LEA-5A/S ,LEA-6A/兼容。

采用MTK 平台,22个通道。

电源电压: 3.0V to 4.3VL20:24 PIN SMD 封装,采用SIRF IV 平台,与与U-BLOX NEO-5Q/M ,NEO-6Q/M/兼容。

电源电压: 2.0V to 3.6VL30:21 PIN SMD 封装,采用SIRF IV 平台,不与现有其他家GPS 模块相兼容,体积非常小,9.0mmx9.0mmx1.6mm 。

电源电压较窄, 1.71V to 1.89VL10-C :L10的精简版,基本参数与L10相同,由于该产品尚在研发中,具体细节不清,个人认为推出这个版本主要是基于市场竞争的考虑,降低成本,增强该产品的市场竞争优势。

Quectel GSM Module FamilyGSM 模块主要有:M10,M12,M16,M20,M30,M33,M62,M72,M75。

个人认为:M10,M12,M72这三款为重点市场推广型号,在本文中将重点对这三款型号进行介绍,其他型号进行简单介绍。

M16:与西门子的MC39I ,华为的GTM900B 相兼容。

此模块自带TCP/IP 协议栈,为四频模块,依据QUECTEL 原厂通告,此产品即将与今年的八月份停产。

M20:50 PIN B2B 封装,与西门子的 MC37I/52I/55I ,华为的EM310/MG323相兼容。

此此模块自带TCP/IP 协议栈,为四频模块。

M30:100 PIN B2B 封装,与WA VECOM 的Q2686/2687相兼容。

支持OPEN CPU ,类似WA VECOM 的OPEN AT 。

M33:100 PIN B2B 封装,支持CAMARA ,SD CARD ,带TCP/IP 协议栈,为四频模块。

FT-2000+硬件设计指导手册2018年12月版本号1.0目录目录 (3)1文档介绍 (4)2复用引脚说明 (4)2.1引脚复用 (4)2.2LPC功能说明 (7)2.2.1LPC复用关系与信号说明 (7)2.2.2LPC建议接法 (8)2.3软件关机、重启 (8)2.4配置引脚建议接法 (8)2.5I2C (11)2.5.1SPD I2C (11)2.5.2RTC I2C (12)3PCIE布线要求 (12)4内存布线要求 (12)4.1阻抗要求 (12)4.2交换准则 (12)4.3布线要求 (13)4.3.1间距要求 (13)4.3.2等长要求 (14)4.3.3PCB叠层要求 (14)1文档介绍本文档说明了FT-2000+平台在原理图设计、板级设计阶段需要遵循的基本规则,旨在减少用户在设计阶段的疑惑以及不确定性,增加设计可靠性。

2复用引脚说明在FT-2000+芯片设计中,部分功能模块引脚与普通GPIO口存在复用关系.设计阶段需了解具体的复用关系、引脚的默认功能和特殊用途。

复用关系需通过对应寄存器来配置不同的功能,默认为func0功能。

2.1引脚复用表1引脚功能复用表SigName PIN func0func1func2CLK_REF_50M AR13clk_refRESET_N AN15reset_nPOR_N AP13por_nCRU_SCAN_CLK AP15cru_scan_clkCRU_CLK_SEL AM15cru_clk_selCRU_CLK_STOP AN14cru_clk_stopCRU_SE AM14cru_seCRU_SI AR14cru_siCRU_SO AN13cru_soCRU_RST_OK AP14cru_rst_okCRU_I2C_SCL AM13cru_sclCRU_I2C_SCL AM13cru_sdaTCK AJ15tckSJTAG_TDI AL13sjtag_tdiSJTAG_TMS AL14sjtag_tmsSJTAG_NTRST AK14sjtag_ntrstSJTAG_TDO AK15sjtag_tdoSJTAG_TCK AJ13sjtag_tckFORCE_MB_START AK13force_mb_startLPC_IRQ_N/GPIO_B6BH43hdt_mb_done_state lpc_ext_irq_outen peu1_linkup_0LPC_LAD_OUTEN/PEU1_LINKUP1AJ16hdt_mb_fail_state lpc_ext_lad_outen peu1_linkup_1 INSTANCEID0N21instanceid_0INSTANCEID1N20instanceid_1SWJ_NTRST P22ntrst_swjSWJ_TDI N22tdi_swjSWJ_SWDITMS P20swditms_swjSWJ_SWDO P21swdo_swjSWJ_TCK N19tck_swjSWJ_TDO P19tdo_swjUART0_CTS_N/GPIO_A0AM48cru_ckobv_sel_0gpio_porta_0uart_0_cts_n UART0_DCD_N/GPIO_A1AM47cru_ckobv_sel_1gpio_porta_1uart_0_dcd_n UART0_DSR_N/GPIO_A2AL48cru_ckobv_sel_2gpio_porta_2uart_0_dsr_n UART0_RI_N/GPIO_A3AK47cru_ckobv_sel_3gpio_porta_3uart_0_ri_n UART0_RTS_N/GPIO_A4AL46cru_ckobv_sel_4gpio_porta_4uart_0_rts_n UART0_DTR_N/GPIO_A5/CRU_CLK_OBVAL47cru_clk_obv gpio_porta_5uart_0_dtr_n SPI_CSN2/GPIO_A6AK48spi_ext_csn2gpio_porta_6traceclk_out SPI_CSN3/GPIO_A7AK46spi_ext_csn3gpio_porta_7tracectl_outI2C0_SCL/GPIO_B0AH47i2c_0_scl gpio_portb_0tracedata_out_ 0I2C0_SDA/GPIO_B1AG47i2c_0_sda gpio_portb_1tracedata_out_ 1I2C1_SCL/GPIO_B2AF47i2c_1_scl gpio_portb_2tracedata_out_ 2I2C1_SDA/GPIO_B3AG46i2c_1_sda gpio_portb_3tracedata_out_ 3UART1_RXD/GPIO_B4BG44uart_1_rxd gpio_portb_4tracedata_out_ 4UART1_TXD/GPIO_B5BH44uart_1_txd gpio_portb_5tracedata_out_ 5LPC_IRQ_N/GPIO_B6BH43gpio_portb_6ext_lpc_irq_n tracedata_out_ 6LPC_LAD_0/GPIO_B7BG43gpio_portb_7ext_lpc_lad_0tracedata_out_ 7CRU_RST_FSM0/GPIO_C0BH42cru_rst_fsm_0gpio_portc_0tracedata_out_ 8CRU_RST_FSM1/GPIO_C1BG42cru_rst_fsm_1gpio_portc_1tracedata_out_ 9CRU_RST_FSM2/GPIO_C2BG41cru_rst_fsm_2gpio_portc_2tracedata_out_ 10CRU_RST_FSM3/GPIO_C3BG40cru_rst_fsm_3gpio_portc_3tracedata_out_ 11CRU_RST_FSM4/GPIO_C4BG39cru_rst_fsm_4gpio_portc_4tracedata_out_ 12LPC_LAD_1/GPIO_C5BH40gpio_portc_5ext_lpc_lad_1tracedata_out_ 13LPC_LAD_2/GPIO_C6BH35gpio_portc_6ext_lpc_lad_2tracedata_out_ 14LPC_LAD_3/GPIO_C7BH41gpio_portc_7ext_lpc_lad_3tracedata_out_ 15UART0_RXD/GPIO_D5BH33uart_0_rxd gpio_portd_5 UART0_TXD/GPIO_D6BG33uart_0_txd gpio_portd_6UART2_RXD BG31uart_2_rxd peu0_c0_clk_ob vUART2_TXD BH32uart_2_txd peu0_c1_clk_ob vUART3_RXD BH31uart_3_rxd peu1_c0_clk_ob vUART3_TXD BG32uart_3_txd peu1_c1_clk_ob vSPI_CSN0AJ48spi_ext_csn0SPI_CSN1AJ46spi_ext_csn1SPI_SCK AJ47spi_ext_sckSPI_DO AG48spi_ext_soSPI_WP/GPIO_D7AF48spi_ext_wp gpio_portd_7 SPI_DI AH46ext_spi_siCLK_LPC_33M AH48clk_lpc_inLPC_LDRQ_N/GPIO_D0BH34peu01_phy01_jtag_tdi ext_lpc_ldrq_n gpio_portd_0 LPC_LFRAME_N/GPIO_D1BH39peu01_phy01_jtag_tms lpc_ext_lframe_n gpio_portd_1PEU01_PHY01_JTAG_TRST _N/GPIO_D2BG34peu01_phy01_jtag_trst_ngpio_portd_2PEU0_PHY0_JTAG_TCK P29peu0_phy0_jtag_tck PEU0_PHY1_JTAG_TCK N30peu0_phy1_jtag_tck PEU0_LINKUP0N29peu0_linkup_0PEU0_LINKUP1P30peu0_linkup_1PEU0_C0_CLKREQ_IN_N N28pad_peu0_c0_clkreq_in _nPEU0_C1_CLKREQ_IN_N P28pad_peu0_c1_clkreq_in _nPEU0_C2_CLKREQ_IN_N P26pad_peu0_c2_clkreq_in _nPEU0_C0_CLKREQ_OUT_N P27pad_peu0_c0_clkreq_ou t_nPEU0_C1_CLKREQ_OUT_N N27pad_peu0_c1_clkreq_ou t_nPEU0_C2_CLKREQ_OUT_N N26pad_peu0_c2_clkreq_ou t_nPEU0_PHY0_JTAG_TDO/GPIO_D3N18peu0_phy0_jtag_tdo cru_error_int gpio_portd_3 PEU0_PHY1_JTAG_TDO/GPIO_D4P18peu0_phy1_jtag_tdo gpio_portd_4PEU1_C0_CLKREQ_OUT_N BA15pad_peu1_c0_clkreq_ou t_nPEU1_C1_CLKREQ_OUT_N AV15pad_peu1_c1_clkreq_ou t_nPEU1_PHY0_JTAG_TCK BA17peu1_phy0_jtag_tck PEU1_PHY1_JTAG_TCK AV14peu1_phy1_jtag_tckPEU1_C0_CLKREQ_IN_N BA16pad_peu1_c0_clkreq_in _nPEU1_C1_CLKREQ_IN_N AW13pad_peu1_c1_clkreq_in _nALL_PLL_LOCK AY16pad_all_pll_lockPEU1_PHY0_JTAG_TDO AY17peu1_phy0_jtag_tdoPEU1_PHY1_JTAG_TDO AV13peu1_phy1_jtag_tdo2.2LPC功能说明由于LPC控制器的输入输出引脚与其他功能引脚存在复用关系,而默认的配置方式不是LPC功能,因此当客户需要使用LPC功能时,需要软件配置为LPC功能。

WH-BLE106硬件设计手册文件版本:V1.0.0目录1关于文档 (3)1.1.文档目的 (3)1.2.产品外观 (3)1.3.参考文档列表 (3)2产品简介 (4)2.1.基本参数 (4)2.2.模块应用框图 (4)2.3.引脚定义 (5)2.4.开发套件 (6)3硬件参考设计 (7)3.1.外围电路框架参考 (7)3.2.电源接口 (7)3.3.UART接口 (7)3.4.复位控制和恢复出厂设置控制 (8)3.5.低功耗唤醒引脚 (9)3.6.射频接口 (9)4电气特性 (11)4.1.工作存储温度 (11)4.2.输入电源 (11)4.3.模块IO口电平 (11)4.4.IO驱动电流 (11)5机械特性 (12)5.1.回流焊建议 (12)5.2.外形尺寸 (13)6联系方式 (14)7免责声明 (15)8更新历史 (16)1关于文档1.1.文档目的本文详细阐述了WH-BLE106(支持BLE5.2协议)无线模块的基本功能和主要特点、硬件接口及使用方法、结构特性等电气指标。

通过阅读本文档,用户可以对本产品有整体认识,对产品规格参数有明确了解,顺利将模块嵌入各种终端设计中。

1.2.产品外观图片1实物图1.3.参考文档列表除此硬件开发文档外,我们同时提供了基于本产品的说明书、封装库等资料,方便用户设计参考,客户可到官方网站查看下载:https:///Product/280.html说明书:https:///Download/1126.html封装库:https:///Download/1179.html2产品简介2.1.基本参数表格1参数列表分类参数取值无线参数工作频段2402~2480MHz发射功率-19dBm-+8dBm接收灵敏度-96dBm传输距离模块+模块(max)BLE106(内置天线)170m天线选项内置板载天线、外接引脚焊盘(需要定制生产)硬件参数数据接口UART:1200~1Mbps工作电压 1.7V~3.6V工作电流发射电流(max)22mA@3V3接收电流(max)15mA@3V3休眠电流(avg)0.7u A@3V3工作温度-40℃~+85℃存储温度-40℃~+85℃工作湿度5~95%RH(无凝露)存储湿度5~95%RH(无凝露)尺寸尺寸:10mm x10mm x2.2mm 封装接口SMT表贴2.2.模块应用框图目前模块开放的接口包括:电源、串口、固件下载接口和部分IO口等,如下图所示。

硬件设计说明书一、设计概要本产品主要基于《滴滴标准化电池产品规格书V1.0》《滴滴电池场景和充放电流程图说明》《滴滴电池底仓和NFC的透传协议》等技术规格书设计而成。

满足产品功能需求,具有市场竞争力。

二、BMS功能框图三、功能设计详解1、电源设计①DC-DC设计电源芯片使用TI的LM5164,该芯片具有超低 IQ,100V输入、1A 同步降压直流/直流转换器;空载输入静态电流:10.5µA;关断静态电流:3µA,用以在休眠时降低系统功耗。

电路图如下所示:②LDO设计电源芯片采用TI的TLV70433和TLV70450,分别输出3.3V电源和5V电源。

3.3V电源为BMS系统供电,5V为CAN通信电源供电。

电路如下图所示:另外,部分外设电源采用3V3_Com供电,在休眠状态下关闭3V3_Com,降低功耗。

电路如下图所示:2、主回路设计本产品主回路采用高端驱动的方式,驱动芯片采用TI的BQ76200PWR(bq76200 高压电池组前端充电/放电高侧NFET 驱动器),驱动信号使用中颖的SH367309。

CHG信号控制充电MOS,DCHG信号控制放电MOS,PDCHG 信号控制预充电路。

预充电路如下图所示:主MOS管采用美格纳的MDE1991,Vds最高可达118V,RDS(ON) < 4.4 mΩ @VGS = 10V。

驱动电路和主回路如下图所示3、电压采集,电流采集,温度采集,均衡电路设计前端采集芯片采用中颖的SH367309,13bit VADC用于采集电压/温度/电流/均衡/保护等功能。

采集电路和外围参数配置如下图所示:其中,使用SH367309采集3路电芯温度。

并留有烧写接口。

4、单片机及外围电路设计单片机采用ST的STM32F072RBT6(ARM®-based 32-bit MCU, up to 128 KB Flash,crystal-less USB FS 2.0,CAN,12 timers, ADC,DAC & comm.interfaces,2.0 - 3.6 V)。

F T U硬件详细设计说明书产品线:配电终端产品类别:产品型号:产品版本:批准:审核:初审:编写:.前言..............................................文档术语..........................................参考文档.........................................2.开发环境...............................................3.硬件详细设计............................................系统架构..........................................主板.............................................主板硬件框图..................................模块1:CPU核心板.............................模块2:时钟模块 ..............................模块3:无线通讯 ..............................模块6以太网接口..............................RS232/RS485电路 ..............................SD卡模块电路 .................................直流量采集模块................................USBHOST接口 ...................................遥控遥信板.......................................硬件框图......................................遥信电路模块..................................遥控电路模块...................................遥测板...........................................遥测板框图....................................遥测电路模块..................................电源模块.........................................................................................元器件总成本:.................................硬件测试方法.....................................4.FPGA逻辑设计...........................................子板逻辑.........................................架构概述.......................................主板逻辑.........................................5.结构工艺设计............................................外观设计.........................................外形结构......................................铭牌..........................................终端内部结构.................................. .组屏方案......................................... .其他............................................. ......................................................1.引言1.1.前言1.2.文档术语1.3.参考文档2.开发环境硬件设施:普通个人PC软件:protel99se3.硬件详细设计3.1.系统架构3.2.主板3.2.1.主板硬件框图3.2.2.CPU核心板3.2.2.1.功能:保存各种数据,参数设置等其他需要保存的数据及给各功能模块提供逻辑接口。

第一章 概述第一节 硬件开发过程简介§1.1.1 硬件开发的基本过程产品硬件项目的开发,首先是要明确硬件总体需求情况,如CPU处理能力、存储容量及速度,I/O端口的分配、接口要求、电平要求、特殊电路(厚膜等)要求等等。

其次,根据需求分析制定硬件总体方案,寻求关键器件及电咱的技术资料、技术途径、技术支持,要比较充分地考虑技术可能性、可靠性以及成本控制,并对开发调试工具提出明确的要求。

关键器件索取样品。

第三、总体方案确定后,作硬件和单板软件的详细设计,包括绘制硬件原理图、单板软件功能框图及编码、PCB布线,同时完成开发物料清单、新器件编码申请、物料申领。

第四,领回PCB板及物料后由焊工焊好1~2块单板,作单板调试,对原理设计中的各功能进行调测,必要时修改原理图并作记录。

第五,软硬件系统联调,一般的单板需硬件人员、单板软件人员的配合,特殊的单板(如主机板)需比较大型软件的开发,参与联调的软件人员更多。

一般地,经过单板调试后在原理及PCB 布线方面有些调整,需第二次投板。

第六,内部验收及转中试,硬件项目完成开发过程。

§1.1.2 硬件开发的规范化上节硬件开发的基本过程应遵循硬件开发流程规范文件执行,不仅如此,硬件开发涉及到技术的应用、器件的选择等,必须遵照相应的规范化措施才能达到质量保障的要求。

这主要表现在,技术的采用要经过总体组的评审,器件和厂家的选择要参照物料认证部的相关文件,开发过程完成相应的规定文档,另外,常用的硬件电路(如ID.WDT)要采用通用的标准设计。

第二节 硬件工程师职责与基本技能§1.2.1 硬件工程师职责一个技术领先、运行可靠的硬件平台是公司产品质量的基础,硬件工程师职责神圣,责任重大。

1、硬件工程师应勇于尝试新的先进技术之应用,在产品硬件设计中大胆创新。

2、坚持采用开放式的硬件架构,把握硬件技术的主流和未来发展,在设计中考虑将来的技术升级。

3、充分利用公司现有的成熟技术,保持产品技术上的继承性。