2014数字系统与逻辑设计题目(电自 ) (1)

- 格式:doc

- 大小:221.46 KB

- 文档页数:10

说明:1、除填空题、图解及特要求外一般不留答题空间。

------------------------------------------------装----------------------------------------------订----------------------------------------------------线---------------------------- ----- -------------------------------------------------装----------------------------------------------订----------------------------------------------------线---------------------------- -----2.装订试卷,考生答卷时不得拆开或在框外留写标记,否则按零分计。

说明:1、除填空题、图解及特要求外一般不留答题空间。

------------------------------------------------装----------------------------------------------订----------------------------------------------------线---------------------------- ----- -------------------------------------------------装----------------------------------------------订----------------------------------------------------线---------------------------- -----A. M=0,S3 S2 S1 S0为 1001,COUT 为1E,以上电路均不对2.装订试卷,考生答卷时不得拆开或在框外留写标记,否则安零分计说明:1、除填空题、图解及特要求外一般不留答题空间。

数字电路与逻辑设计(1)班级 学号 姓名 成绩一.单项选择题(每题1分,共10分)1.表示任意两位无符号十进制数需要( )二进制数。

A .6B .7C .8D .9 2.余3码10001000对应的2421码为( )。

A .01010101B 。

10000101 C.10111011 D 。

11101011 3.补码1.1000的真值是( )。

A . +1。

0111 B. —1。

0111 C. -0。

1001 D. -0。

1000 4.标准或-与式是由( )构成的逻辑表达式。

A .与项相或B 。

最小项相或C 。

最大项相与D 。

或项相与 5。

根据反演规则,()()E DE C C AF ++⋅+=的反函数为( ).A 。

E )]E D (C C [A F ⋅++= B. E )E D (C C A F ⋅++=C 。

E )ED C C A (F ⋅++= D 。

E )(D AF ⋅++=E C C 6.下列四种类型的逻辑门中,可以用( )实现三种基本运算。

A. 与门 B 。

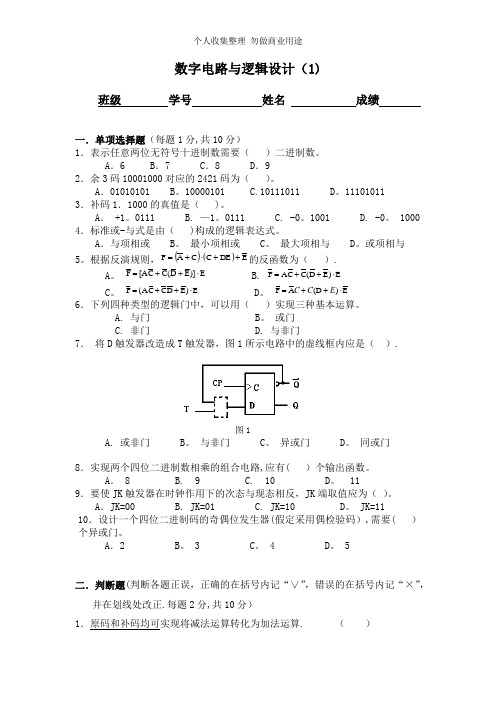

或门 C. 非门 D. 与非门7. 将D 触发器改造成T 触发器,图1所示电路中的虚线框内应是( ).图1A. 或非门 B 。

与非门 C 。

异或门 D 。

同或门8.实现两个四位二进制数相乘的组合电路,应有( )个输出函数。

A . 8 B. 9 C. 10 D 。

11 9.要使JK 触发器在时钟作用下的次态与现态相反,JK 端取值应为( )。

A .JK=00 B. JK=01 C. JK=10 D 。

JK=1110.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要( )个异或门。

A .2B 。

3C 。

4D 。

5二.判断题(判断各题正误,正确的在括号内记“∨”,错误的在括号内记“×”,并在划线处改正.每题2分,共10分)1.原码和补码均可实现将减法运算转化为加法运算. ( )2.逻辑函数7),M(1,3,4,6,C)B,F(A,∏=则m(0,2,5)C)B,(A,F ∑=。

电子科技大学2013-2014学年第二学期“数字逻辑设计及应用”课程考试题(半期)(120分钟)考试日期 2014年 月 日I. To fill the answers in the “( )” ( 2’ X 15 = 30 )1. Given ∑=ABCF )5,4,1(, then ABC F ∏=( 0,2,3,6,7 ),F =A ’∑BC( 1 )+A∑BC( 0,1 ).2. ( 1001 0011 )8421BCD =( 1111 0011 )2421BCD .3. ( 0101 1101 )2=( 0111 0011 )Gray .4. Open-drain output has two states without if there is no pull up resistor: Low and ( Hi-Z ).5. A two’s -complement =0110 1010, C one ’s -complement =1111 1011, [A-C]two’s -complement =( 0110 1110 ). Is it overflow for [A-C]two’s -complement ? (Yes or No) [ No ]6. XOR gate in positive logic level is equivalent to ( XNOR ) gate in negative logic level.7. Five variables can make ( 32 ) minterms. The sum of all the minterms must be ( 1 ).8. If the function ∑=ABCF )6,3,2,1(, then ∑=ABC F '( 0, 4, 5, 7 ).9. If the information bits are 1001 0010, the check bit is ( 0 ) for odd-parity. 10. To make 2014 code-words, ( 11 ) bits should be used at least.11. Given the circuit shown in Figure 1, its output expression F=( (b(a+c)+ac)’ ).Figure 1II. There is only one correct answer in the following questions.( 3’ X 10=30 )1. Which of the following codes has the self-complement property? ( D)A. GrayB. BiquinaryC. 8421BCDD. Excess-32. Which of the following 2-input gates can form a complete set of logic gates? ( B )A. ORB. NORC. XORD. XNOR(或非门构成逻辑门完全集的示意图)3. Which of the following gates is equivalent to XNOR? ( A)A. B. C. D.4. Which of the following connection is correct? ( C)A. B. C. D.5. Which of the following expressions has no hazard? ( B)A. F=W•Y+W’•Z’+X•Y’•ZB. F=W•Y+W’•Z’+Y•Z’C. F=W•Y+W’•Z’+X•Y’•Z+Y•Z’D. F=W•Y+W’•Z’+X•Y’•Z+W’•X•Y’6. Which of the following statements is correct? ( D)A. The duality of the minimal sum expression is its minimal product.B. The minimum sum-of-product expression has no static-1 hazard.C. The canonical sum must have hazard.D. The minimum sum-of-product expression has no static-0 hazard. 7. The minimum sum of product for AB+A ’C+BCDEFGH is ( A ).A. A •B+A ’•CB. A ’•B+A •CC. A •B+A ’•C+B •CD. A •B+A ’•C+B •C8. Given A=(0011 1111 . 0100)2, its equivalent values for A 10 and A 16 are ( B ) A. (96.58)10, (60.94)16 B. (63.25)10, (3F.4)16C. (96.58)10, (60.49)16D. (63.25)10, (3F.94)169. Given the timing diagram as shown in Figure 2, the output function is ( A ). A. ∑=xyzf )7,6,5,3( B. ∑=xyz f )4,2,1,0( C. ∑=xyz f )6,2,1,0( D. ∑=xyz f )7,2,1,0(Figure 210. A self-dual logic function is a function such that F=F D . Which of the following functions is self-dual? ( C )A. ∑=xyzF )7,5,2,1( B. F=X ’•Y •Z ’+X •Y ’•Z ’+X ’•ZC. F=X •Y+X •Z+Y •ZD. )4,3,0(xyz F ∏=III. Combinational Circuit Analysis And Design: [40’]1.Given F(A,B,C,D)= (B⊕C⊙(B•C))+A’•D•(B•C)’, the “Don’t Care”input combinations is=∑. Simplify the logic function F(A,B,C,D) into the F(A,B,C,D)d(10,11,12,13,14,15)minimal sum using Karnaugh map, and write out NAND-NAND logic expression of the minimal sum. (8’)参考评分标准:1.填写F的卡诺图正确4分,d占1分,错一格扣0.5分,扣完为止;2.化简的表达式正确3分,错一个乘积项扣1分;F minimal-sum (A,B,C,D)=B/C/+B/D+C/D3.“与非-与非“表达式正确1分F NAND-NAND (A,B,C,D)= [(B/C/)/(B/D)/(C/D)/]/2. A combinational circuit is shown as below. (8’)(1) Write out the sum-of-product expression of output F(W,X,Y,Z) for the circuit.(2) Analysis all conditions that the static hazard may exit for the circuit, and indicate types of static hazard.(3)Write out the minimal sum of output F(W,X,Y,Z) for the hazard-free.参考评分标准:1. 原始的积之和表达式正确3分 ,只要是积之和形式就算对,不管是否为原始积之和,错一个(多一个或少一个)乘积项扣一分,扣完为止;F(W,X,Y,Z)=WX/Y/+XY/Z+XY2.指出所有静态冒险存在的条件2分,指出静态冒险类型1分。

数字电路与逻辑设计习题及参考答案一、选择题1. 以下表达式中符合逻辑运算法则的是 D 。

A.C ·C=C 2B.1+1=10C.0<1D.A+1=12. 一位十六进制数可以用 C 位二进制数来表示。

A . 1B . 2C . 4D . 163. 当逻辑函数有n 个变量时,共有 D 个变量取值组合?A. nB. 2nC. n 2D. 2n4. 逻辑函数的表示方法中具有唯一性的是 A 。

A .真值表 B.表达式 C.逻辑图 D.状态图5. 在一个8位的存储单元中,能够存储的最大无符号整数是 D 。

A .(256)10B .(127)10C .(128)10D .(255)106.逻辑函数F=B A A ⊕⊕)( = A 。

A.BB.AC.B A ⊕D. B A ⊕7.求一个逻辑函数F 的对偶式,不可将F 中的 B 。

A .“·”换成“+”,“+”换成“·”B.原变量换成反变量,反变量换成原变量C.变量不变D.常数中“0”换成“1”,“1”换成“0”8.A+BC= C 。

A .A+B B.A+C C.(A+B )(A+C ) D.B+C9.在何种输入情况下,“与非”运算的结果是逻辑0。

DA .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是110.在何种输入情况下,“或非”运算的结果是逻辑1。

AA .全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为111.十进制数25用8421BCD 码表示为 B 。

A .10 101B .0010 0101C .100101D .1010112.不与十进制数(53.5)10等值的数或代码为 C 。

A .(0101 0011.0101)8421BCDB .(35.8)16C .(110101.11)2D .(65.4)813.以下参数不是矩形脉冲信号的参数 D 。

A.周期B.占空比C.脉宽D.扫描期14.与八进制数(47.3)8等值的数为: BA. (100111.0101)2B.(27.6)16C.(27.3 )16D. (100111.101)215. 常用的BCD码有 D 。

………密………封………线………以………内………答………题………无………效……电子科技大学2013 -2014学年第 二 学期期 末 考试 A 卷课程名称:_数字逻辑设计及应用__ 考试形式: 闭卷 考试日期: 20 14 年 07 月 10 日 考试时长:_120___分钟课程成绩构成:平时 30 %, 期中 30 %, 实验 0 %, 期末 40 % 本试卷试题由___六__部分构成,共__8___页。

题号 一 二 三 四 五 六 七 八 九 十 合计得分I. Fill out your answers in the blanks (3’ X 10=30’)1. A circuit with 10 flip-flops can store ( 10 ) bit binary numbers, that is, include ( 1024 或 210 ) states at most.2. A 5-bit linear feedback shift-register (LFSR) counter with no self-correction can have ( 31 或 25-1 ) normal states.3. A modulo-24 counter circuit needs ( 5 ) D filp-flops at least. A modulo-500 counter circuit needs ( 3 ) 4-bit counters of 74x163 at least.4. If an 74x148 priority encoder has its 1, 3, 4, and 5 inputs at the active level, the active LOW binary output is ( 010 ) .5. State/output table for a sequential circuit is shown as Table 1. X is input and Z n is output. Assume that the initial state is S 0, if the input sequence is X = 01110101, the output sequence should be ( 11001100 或110011000 ). 【可以确定的输出序列应该有9位】.6. Transition/output table for a sequential circuit is shown in Table 2, X is input and Y is output, the sequential circuit is a modulus ( 3 ) up/down counter.n+1n 21………密………封………线………以………内………答………题………无………效……7. A serial sequence generator by feedback shift registers 74x194 is shown in Figure 1, assume the initial state is Q 2Q 1Q 0 = 100, the feedback function LIN = Q 2’Q 1’ + Q 2Q 0’, the output sequence in Q 2 is ( 100110 循环输出 ).Figure 18. When the input is 01100000 of an 8 bit DAC, the corresponding output voltage is 3.76V . The output voltage range for the DAC is ( 0 ~ 9.99 或 568221276.3+−× 或 9625576.3× )V . 【本题并未对误差范围进行要求,一般可保留2位小数。

《数字系统与逻辑设计》课程设计一、基本要求课程设计的基本任务,是着重提高动手能力及在字集成电路应用方面的实践技能,培养综合运用理论知识解决实际问题的能力。

各组人员可分别通过设计图纸,上网查找资料以及撰写报告这几个过程来锻炼逻辑思维能力及实际动手能力。

从实际操作中学习知识,思考存在的问题以及解决问题。

各班同学可选择以小组为单位完成课设,也可以独立完成,每个小组不超过3个人。

各组可从后面所列22个题目中任选一个,但同一个题目一个班内只允许选择一个,不同班级的同样题目的小组课程设计内容和形式不能相同。

由学习委员负责记录分组及协调。

电自12151在18周周1前完成并提交,提交的文件包括:1、一份用WORD完成的课程设计报告,要求打印,格式见后面的附件,2、设计图纸(A2图纸)手绘或使用相关绘图软件。

设计图纸中所有涉及的元器件要附上元器件明细表。

注:每个小组的电子文档要求汇总打包,由各班团支书、班长、学习委员和科代表4人共同负责提交指导教师处批改备案。

二、题目贵州大学明德学院课程设计报告(一号仿宋GB)课程名称:(三号宋体)系部:(三号宋体)专业班级:(三号宋体)小组成员:(三号宋体)指导教师:(三号宋体)完成时间:(三号宋体)×××课程设计报告(二号黑体)一. 设计要求(三号宋体)说明:指所设计题目的具体要求×××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××(1).××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××(2).××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××(3).××××××××××××××(小四号宋体)二. 设计的作用、目的(三号宋体)掌握××的原理×××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××(小四号宋体)三.设计的具体实现(三号宋体)1.系统概述(小三号宋体)简单介绍系统设计思路与总体方案的可行性论证,各功能块的划分与组成,全面介绍总体工作过程或工作原理。

××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××(小四号宋体)2.电路分析与设计(小三号宋体)详细介绍各单元电路的选择、设计及工作原理分析,并介绍有关参数的计算及元器件参数的选择等。

×××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××(小四号宋体)四.心得体会及建议(三号宋体)×××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××(小四号宋体)五.附录元器件明细表(主要用于列出本次课程设计中所用的全部元器件及模块)。