第12章-封装缺陷分析1

- 格式:ppt

- 大小:2.21 MB

- 文档页数:49

我们经常会碰到LED不亮的情况,封装企业、应用企业以及使用的单位和个人,都有可能碰到,这就是行业内的人说的死灯现象。

究其原因不外是两种情况:其一,LED的漏电流过大造成PN结失效,使LED灯点不亮,这种情况一般不会影响其它的LED灯的工作;其二,LED灯的内部连接引线断开,造成LED无电流通过而产生死灯,这种情况会影响其它的LED灯的正常工作,原因是由于LED灯工作电压低(红黄橙LED工作电压1.8V—2.2V,蓝绿白LED工作电压2.8—3.2V),一般都要用串、并联来联接,来适应不同的工作电压,串联的LED灯越多影响越大,只要其中有一个LED灯内部连线开路,将造成该串联电路的整串LED灯不亮,可见这种情况比第一种情况要严重的多。

LED死灯是影响产品质量、可靠性的关健,如何减少和杜绝死灯,提高产品质量和可靠性,是封装、应用企业需要解决的关键问题。

下面是对造成死灯的一些原因作一些分析探讨1. 静电对LED芯片造成损伤,使LED芯片的PN结失效,漏电流增大,变成一个电阻静电是一种危害极大的魔鬼,全世界因为静电损坏的电子元器件不计其数,造成数千万美元的经济损失。

所以防止静电损坏电子元器件,是电子行业一项很重要的工作,LED 封装、应用的企业千万不要掉以轻心。

任何一个环节出问题,都将造成对LED的损害,使LED性能变坏甚至失效。

我们知道人体(ESD)静电可以达到三千伏左右,足可以将LED 芯片击穿损坏,在LED封装生产线,各类设备的接地电阻是否符合要求,这也是很重要的,一般要求接地电阻为4欧姆,有些要求高的场合其接地电阻甚至要达到≤2欧姆。

这些要求都为电子行业的人们所熟悉,关健是在实际执行时是否到位,是否有记录。

据笔者了解一般的民营企业,防静电措施做得并不到位,这就是大多数企业查不到接地电阻的测试记录,即使做了接地电阻测试也是一年一次,或几年一次,或有问题时检查一下接地电阻,殊不知接地电阻测试这是一项很重要的工作,每年至少4次(每季度测试一次),一些要求高的地方,每月就要作一次接地电阻测试。

先进封装缺陷及失效案例解析

先进封装是一种高度集成、高性能、高可靠性的封装技术,但仍然存

在一些缺陷和失效模式。

1.焊点疲劳:焊点在长期受到温度变化的影响下,容易发生疲劳断裂,导致电气连接失效。

这种失效模式主要影响球格阵列封装(BGA)和无线

通讯模块。

2.器件间隙裂缝:由于先进封装技术的高度集成和微型化,器件之间

的间隙非常小,容易因应力过大而发生裂缝,导致封装失效。

这种失效模

式主要影响焊盘球接触型封装(CSP)和BGA封装。

3.热膨胀不匹配:不同材料的膨胀系数不同,先进封装中各种材料之

间的热膨胀系数不匹配,容易导致封装失效。

这种失效模式主要影响CSP

和BGA封装。

4.气泡:由于先进封装技术采用高温焊接和高压注塑等工艺,容易导

致气泡生成。

气泡会导致器件连接失效,并且会使封装的温度敏感性增加。

这种失效模式主要影响CSP和BGA封装。

5.毛刺:封装过程中,可能会出现毛刺,这些毛刺可能会导致器件的

短路或信号干扰。

这种失效模式主要影响CSP和BGA封装。

6.接地电路不良:由于先进封装技术中,器件的接地通常通过焊盘来

实现,因此焊盘接地不良会导致器件失效。

这种失效模式主要影响CSP和BGA封装。

针对这些失效模式,可以采用一些措施来提高封装的可靠性,例如控

制焊接温度、优化焊接工艺、提高材料匹配度等。

同时,在封装设计和生

产过程中,也需要严格的质量管理和测试,以确保产品的可靠性和稳定性。

半导体封装键合工艺中常见缺陷识别和处理方法南京信息职业技术学院李荣茂 2012-07-13##############2012-07-13######2#0#12-07-13########,摘要,本文叙述了键合工艺的概念、键合工艺设备的改进和其产生的各种缺陷的类别。

重点研究了键合工艺常见缺陷的类型和其产生的根本原因。

通过对各种缺陷类型的识别,探索其产生的根本原因并找出应对方法,从而增加其合格率。

,关键词,键合工艺缺陷处理方法1.引言 FORCE 大 POWER是比较适宜的 ;(3)断点靠我们需要调节参数,小近随着科技发展的日新月异,电子芯片的使用越来越渗透到各行各中间,通常问题已经不再参数上了,我们应当仔细观察设备平台,是否业,而封装技术也应运而生。

所谓封装技术是一种将集成电路用“”有异物例如一些小的残留碎片遗留在产品的底部造成损伤,如果确认绝缘是这样的情况,及时清理平台残留碎片即可。

的塑料或陶瓷材料打包的技术。

封装对于芯片来说不但必须也是至关 4.2 不规则焊球 Defective ball 重要的,它直接影响到了芯片的质量,而 WIRE BOND作为封装技术中的一个重要的步骤,其过程中产生的晶体缺陷也是不容忽视的。

2.WIRE BOND 键合工艺目前主要的芯片连接技术有三种,分别为引线键合,载带焊和倒装焊,其中前者占键合工艺的 80%以上,在 IC 制造也中得到广泛的应用。

引线键合是半导体封装制程的一站,自晶粒 (Die或 Chip)各电极上,以金线或铝线进行各式打线结合,再牵线至脚架(Lead Frame)的各内脚处续行打线以完成回路,这种两端打线的工作称为 WireB ond。

Wire bond 图 2 不规则焊球在芯片封装厂称为前工序,又叫做金属线键合是将 die 的 PAD飞线连如图 2 所示金线打在芯片上的球并非圆形且球与球的大小厚度还接到外部封装的 BALL 的工序。

不一样,表示同一粒芯片上的球是不规则的,一粒芯片大约有百来粒 3.键合工艺为什么会产生缺陷球,有可能只有一到两粒是产生这样异常的,可对质量的影响确是大打 3.1 键合工艺产生缺陷的原因折扣。

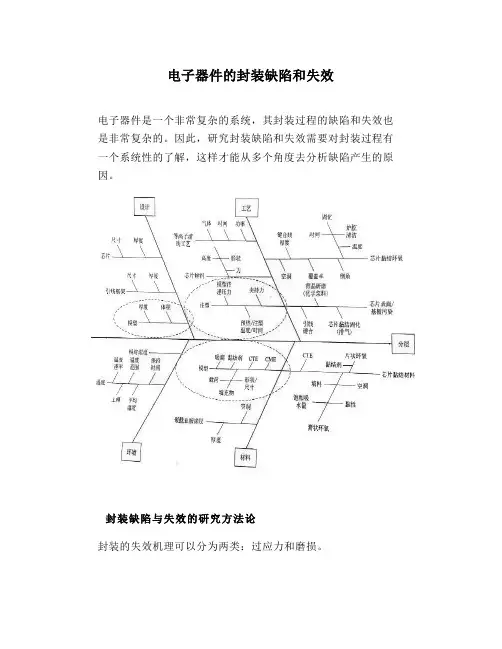

电子器件的封装缺陷和失效电子器件是一个非常复杂的系统,其封装过程的缺陷和失效也是非常复杂的。

因此,研究封装缺陷和失效需要对封装过程有一个系统性的了解,这样才能从多个角度去分析缺陷产生的原因。

封装缺陷与失效的研究方法论封装的失效机理可以分为两类:过应力和磨损。

过应力失效往往是瞬时的、灾难性的;磨损失效是长期的累积损坏,往往首先表示为性能退化,接着才是器件失效。

失效的负载类型又可以分为机械、热、电气、辐射和化学负载等。

影响封装缺陷和失效的因素是多种多样的,材料成分和属性、封装设计、环境条件和工艺参数等都会有所影响。

确定影响因素是预防封装缺陷和失效的基本前提。

影响因素可以通过试验或者模拟仿真的方法来确定,一般多采用物理模型法和数值参数法。

对于更复杂的缺陷和失效机理,常常采用试差法确定关键的影响因素,但是这个方法需要较长的试验时间和设备修正,效率低、花费高。

在分析失效机理的过程中,采用鱼骨图(因果图)展示影响因素是行业通用的方法。

鱼骨图可以说明复杂的原因及影响因素和封装缺陷之间的关系,也可以区分多种原因并将其分门别类。

生产应用中,有一类鱼骨图被称为6Ms:从机器、方法、材料、量度、人力和自然力等六个维度分析影响因素。

这一张图所示的是展示塑封芯片分层原因的鱼骨图,从设计、工艺、环境和材料四个方面进行了分析。

通过鱼骨图,清晰地展现了所有的影响因素,为失效分析奠定了良好基础。

引发失效的负载类型如上一节所述,封装的负载类型可以分为机械、热、电气、辐射和化学负载。

1. 失效机理的分类机械载荷:包括物理冲击、振动、填充颗粒在硅芯片上施加的应力(如收缩应力)和惯性力(如宇宙飞船的巨大加速度)等。

材料对这些载荷的响应可能表现为弹性形变、塑性形变、翘曲、脆性或柔性断裂、界面分层、疲劳裂缝产生和扩展、蠕变以及蠕变开裂等等。

热载荷:包括芯片黏结剂固化时的高温、引线键合前的预加热、成型工艺、后固化、邻近元器件的再加工、浸焊、气相焊接和回流焊接等等。

封装分析报告1. 引言封装是面向对象程序设计中的一种重要概念,它允许将数据和操作封装在一个单元中,通过接口与外界进行交互。

通过封装,我们可以隐藏内部实现细节,并提供对外的抽象接口,从而增强代码的可维护性、可拓展性和可复用性。

本文将对封装进行深入分析,并探讨其应用场景、优点和限制。

2. 封装的概念封装是面向对象程序设计的三大特性之一,它将数据和对数据的操作封装在一个单元中,并通过接口与外界进行交互。

封装的目的在于隐藏内部实现细节,只向外界暴露必要的接口,从而降低了外界对内部实现的依赖性。

通过封装,我们可以将数据和行为组织在一起,形成一个独立的、可复用的模块。

封装可以实现信息隐藏,即将数据对外界隐藏起来,只通过接口提供对数据的访问。

这样做的好处是可以保护数据的一致性和完整性,防止外界直接修改数据,同时还可以有效地控制数据的访问权限。

3. 封装的应用场景3.1 封装和信息隐藏封装提供了对数据的访问权限控制,通过合理地设计接口,可以实现对数据的保护。

一些重要的数据可以被封装在类的私有成员中,只通过接口提供对外访问。

这样做可以防止数据被误用或非法修改,提高了系统的稳定性和安全性。

3.2 封装和模块化封装可以将数据和行为组织在一起,形成一个独立的、可复用的模块。

通过将相关的数据和操作封装在一起,可以提高代码的可维护性和可拓展性。

其他模块可以通过接口使用该模块,而不需要关注具体的实现细节,提高了代码的复用性。

3.3 封装和接口设计封装的一个重要应用是接口设计。

通过合理地设计接口,可以隐藏内部实现细节,将复杂度封装在内部,提供简洁的对外接口。

良好的接口设计可以降低使用成本,提高代码的可读性和可维护性。

4. 封装的优点封装作为面向对象程序设计的重要特性,具有以下优点:4.1 隐藏内部实现细节通过封装,可以将内部实现细节隐藏起来,只向外界暴露必要的接口。

这样做的好处是提高了代码的安全性和稳定性,外界无法直接访问和修改内部数据,从而减少了系统出错的可能性。

第一章集成电路芯片封装技术1. (P1)封装概念:狭义:集成电路芯片封装是利用膜技术及微细加工技术,将芯片及其他要素在框架或基板上布置、粘贴固定及连接,引出接线端子并通过可塑性绝缘介质灌封固定,构成整体结构的工艺。

广义:将封装体与基板连接固定,装配成完整的系统或电子设备,并确保整个系统综合性能的工程。

2. 芯片封装实现的功能:1 传递电能,主要是指电源电压的分配和导通。

2 传递电路信号,主要是将电信号的延迟尽可能减小,在布线时应尽可能使信号线与芯片的互连路径以及通过封装的IO接口引出的路径达到最短。

3 提供散热途径,主要是指各种芯片封装都要考虑元器件、部件长期工作时如何将聚集的热量散出的问题。

4 结构保护与支持,主要是指芯片封装可为芯片和其他连接部件提供牢固可靠的机械支撑,并能适应各种工作环境和条件的变化。

3.在确定集成电路的封装要求时应注意以下儿个因素:1 成本2 外形与结构3 可靠性4 性能4.在选择具体的封装形式时,主要需要考虑4种设计参数:性能、尺寸、重量、可靠性和成本目标。

5.封装工程的技术层次:第一层次(Level1或First Level):该层次又称为芯片层次的封装(Chip Level Packaging),是指把集成电路芯片与封装基板或引脚架(Lead Frame)之间的粘贴固定、电路连线与封装保护的工艺,使之成为易于取放输送,并可与下一层次组装进行连接的模块(组件Module)元件。

第二层次(Level2或Second Level:将数个第一层次完成的封装与其他电子元器件组成个电路卡(Card〉的工艺.第三层次(Level3或Third Level):将数个第二层次完成的封装组装成的电路卡组合成在一个主电路板(Board)上使之成为一个部件或子系(Subsystem)的工艺。

第四层次(Level4或Fourth Level)将数个子系统组装成为一个完整电子产品的工艺过程。

在芯片上的集成电路元器件间的连线工艺也称为零级层次(Level 0)的封装,6.封装的分类:按照封装中组合集成电路芯片的数目,芯片封装可分为:单芯片封装与多芯片封装两大类。

EMC封装是什么?常见的缺陷有哪些?如何解决?本文主要通过对EMC封装成形的过程中常出现的问题(缺陷)一未填充、气孔、麻点、冲丝、开裂、溢料、粘模等进行分析与研究,并提出行之有效的解决办法与对策。

塑料封装以其独特的优势而成为当前微电子封装的主流,约占封装市场的95%以上。

塑封产品的广泛应用,也为塑料封装带来了前所未有的发展,但是几乎所有的塑封产品成形缺陷问题总是普遍存在的,也无论是采用先进的传递模注封装,还是采用传统的单注塑模封装,都是无法完全避免的。

相比较而言,传统塑封模成形缺陷几率较大,种类也较多,尺寸越大,发生的几率也越大。

塑封产品的质量优劣主要由四个方面因素来决定:A、EMC的性能,主要包括胶化时间、黏度、流动性、脱模性、粘接性、耐湿性、耐热性、溢料性、应力、强度、模量等;B、模具,主要包括浇道、浇口、型腔、排气口设计与引线框架设计的匹配程度等;C、封装形式,不同的封装形式往往会出现不同的缺陷,所以优化封装形式的设计,会大大减少不良缺陷的发生;D、工艺参数,主要包括合模压力、注塑压力、注塑速度、预热温度、模具温度、固化时间等。

下面主要对在塑封成形中常见的缺陷问题产生的原因进行分析研究,并提出相应有效可行的解决办法与对策。

1.封装成形未充填及其对策封装成形未充填现象主要有两种情况:一种是有趋向性的未充填,主要是由于封装工艺与EMC的性能参数不匹配造成的;一种是随机性的未充填,主要是由于模具清洗不当、EMC中不溶性杂质太大、模具进料口太小等原因,引起模具浇口堵塞而造成的。

从封装形式上看,在DIP和QFP中比较容易出现未充填现象,而从外形上看,DIP未充填主要表现为完全未充填和部分未充填,QFP主要存在角部未充填。

未充填的主要原因及其对策:(1)由于模具温度过高,或者说封装工艺与EMC的性能参数不匹配而引起的有趋向性的未充填。

预热后的EMC在高温下反应速度加快,致使EMC的胶化时间相对变短,流动性变差,在型腔还未完全充满时,EMC的黏度便会急剧上升,流动阻力也变大,以至于未能得到良好的充填,从而形成有趋向性的未充填。

第12 章Insert molding 成型案例分析12.1 Insert molding 成型原理Inset molding 成型是指在模具型腔内装入预先准备的insert,然后合模进行塑胶的注射。

熔融的塑胶材料充满insert 以外的型腔空间,凝固后和insert 成为一体,开模后作为整体一起被顶出。

从insert molding 的成型工艺可以看出,insert 在塑胶制品内必须有牢固的定位,才不至于从塑胶制品上脱落。

Insert 的材质多为金属。

Inset molding 成型利用塑料的易成型性、弯曲性与金属的刚性、强度及耐热性相互组合补充可结实地制成复杂精巧的金属塑料一体化制品,如图12-1 所示。

本案例中insert材质采用铝合金。

图 12-1 insert molding 成型原理12.2 Insert molding 分析前处理Insert molding成型案例采用3D 网格进行模拟分析。

在生成最终的3D 网格前,系统必须先在产品模型表面生成初始表面网格,并按照修补表面网格的程序消除一切表面网格缺陷,然后再转化成3D网格。

需要注意的是,3D网格不能像表面网格那样可以直接删除再进行修补动作。

如果必须删除模型里的3D 网格,需先删除所有3D 网格,之后将“网格类型”由3D 转换成表面网格,如图12-2 所示,从源档模型重新划分表面网格并修补网格缺陷。

在表面网格完好的情况下再将“网格类型”设置成3D,再次利用“生成网格”指令生成3D 网格。

所以对一个3D 执行删除,就必须对整个模型重新进行网格划分。

一般不建议这么做。

因此建议用户在表面网格段一次性消除网格缺陷,不要遗留问题网格,否则即使不影响3D网格的划分,也会影响3D网格的质量,修改起来很麻烦。

图12-2 转化网格类型12.2.1 导入并添加模在 insert molding 成型分析中,系统不仅分析熔融塑胶在型腔内的流动,同时计算腔内塑胶和insert 及模具这三者之间热量传递对塑胶制品和insert 成型效果的影响。

目录1 引言 (1)1.1智能功率模块概述 (1)1.1.1功率MOSFET发展现状 (1)1.1.2 IGBT发展现状 (3)1.1.3 智能功率模块的特点和发展现状 (5)1.1.4 常用智能功率模块封装结构[8] (8)1.1.5 常用智能功率模块封装材料 (10)1.2低功耗智能功率模块特点与应用简介 (12)1.2.1 低功耗智能功率模块特点 (12)1.2.2 低功耗智能功率模块设计结构 (13)1.2.3 低功耗智能功率模块的应用 (13)1.3本文研究的目的与内容 (13)2 双列直插型低功耗智能功率模块封装结构设计与工艺 (15)2.1模块封装结构 (15)2.2模块封装工艺流程 (16)2.3低功耗智能功率模块封装工艺的主要缺陷 (21)2.4本章小结 (21)3 芯片焊接空洞缺陷形成的机理及其解决措施 (23)3.1芯片焊接空洞缺陷状况 (23)3.2芯片焊接空洞缺陷形成机理分析 (25)3.2.1 工艺材料的影响 (25)3.2.2 工艺夹具的影响 (26)3.2.3 工艺参数的影响 (28)3.3缺陷改善实验设计方案 (30)3.3.1 以DBC为基板的芯片焊接空洞改善实验设计方案 (31)3.3.2 以IMS为基板的芯片焊接空洞改善试验设计方案 (33)3.4试验结果与分析 (36)3.4.1 焊接优化正交试验结果 (36)3.4.2 影响芯片焊接空洞的因素分析 (37)3.4.3 针对温度曲线进行优化的试验设计结果 (40)3.4.4 改善措施 (44)3.5本章小结 (45)4 塑封不完整缺陷形成的机理及其解决措施 (46)4.1塑封缺陷状况 (46)4.2塑封缺陷形成的机理分析 (47)4.2.1 塑封工艺流程分析 (47)4.2.2 材料,工具设备及工艺参数分析 (47)4.2.3 工艺参数的影响 (51)4.2.4 EMC材料本身的影响 (52)4.2.5 模具的影响 (52)4.2.6 模块塑封体设计的影响 (52)4.3缺陷改善试验设计方案 (52)4.3.1 试验设计方案,结果与分析 (53)4.3.2 改善措施 (58)4.4本章小结 (58)5 总结与展望 (60)参考文献 (61)致谢 (63)攻读学位期间发表的学术论文 (64)图片目录图1 功率MOSFET结构和电符号 (2)图2 N沟道增强型垂直式结构的功率MOSFET的结构和功能 (2)图3 三种IGBT芯片厚度的比较 (4)图4 n沟道增强型垂直式IGBT的结构和功能,非穿通结构 (5)图5 功率模块内部结构示意图[9] (9)图6 IMS基板Bergquist 公司提供 (11)图7 DBC基板Curamik 公司提供 (11)图8 采用陶瓷基板的DIP智能功率模块(44mmX27mm) 的剖面图[11] (13)图9 采用DBC基板的SPM模块的接线框架构造图。

电子封装中微观缺陷检测技术研究在当今这个科技飞速发展的时代,电子设备就像我们生活中的小精灵,无处不在,给我们带来各种便利和乐趣。

从手机、电脑到智能家电,它们的背后都离不开电子封装技术。

而在电子封装这个看似神秘的领域里,微观缺陷检测技术可是个超级重要的大角色。

就拿我之前遇到的一件事儿来说吧。

有一次,我去一家电子厂参观,正好赶上他们在检测一批新生产的电子封装产品。

我看到工人们拿着各种仪器,一脸严肃地对着那些小小的芯片和电路板左看右看。

我好奇地凑过去,发现他们正在寻找那些肉眼几乎看不见的微观缺陷。

当时我就在想,这得多难啊!那些微观缺陷就像藏在草丛里的小虫子,不仔细找根本发现不了。

后来我了解到,要是这些微观缺陷没被检测出来,那可就麻烦大了。

比如说,一个小小的裂缝或者气泡,都可能导致整个电子设备出现故障,甚至报废。

咱们先来说说电子封装中为啥会出现微观缺陷。

这就好比盖房子,材料不好、施工不精细,房子就容易有问题。

在电子封装中,材料的纯度不够、工艺不精准、环境不干净等,都可能导致微观缺陷的产生。

比如说,在封装过程中,如果温度控制不好,就可能会产生热应力,从而导致封装材料出现裂缝。

又或者,如果封装环境中有灰尘颗粒,它们可能会夹在封装材料中间,形成微小的空洞。

那怎么检测这些微观缺陷呢?这可真是个技术活儿!目前常用的方法有光学检测、电子显微镜检测、X 射线检测等等。

光学检测就像是用放大镜看东西,通过特殊的光源和镜头,把微观缺陷放大,让我们能看到。

电子显微镜检测那就更厉害了,它能把微观世界放大成千上万倍,让那些小缺陷无处遁形。

X 射线检测则像是给电子封装拍“透视照”,可以穿透封装材料,看到内部的情况。

不过,这些检测技术也不是完美的。

光学检测有时候可能会受到光线的影响,导致检测结果不准确。

电子显微镜检测虽然厉害,但是设备昂贵,检测速度也比较慢。

X 射线检测呢,对人体有一定的辐射,而且对一些细微的缺陷可能不够敏感。

为了提高检测的准确性和效率,科学家们可是绞尽了脑汁。