DSP原理及应用第二章DSP的硬件结构总结(精)

- 格式:doc

- 大小:237.00 KB

- 文档页数:14

DSP原理及应用第二章DSP的硬件结构总结(精)【例2.4.1】累加器A=FF01234567H,执行带移位的STH 和STL指令后,求暂存器T和A的内容。

2.4.3桶形移位寄存器:TMS320C54x的40位桶形移位寄存器主要用于累加器或数据区操作数的定标。

它能将输入数据进行0~31位的左移和0~16位的右移。

所移动的位数可由ST1中的ASM或被指定的暂存器T决定。

1.组成框图①多路选择器MUX:用来选择输入数据。

②符号控制SC:用于对输入数据进行符号位扩展。

③移位寄存器:用来对输入的数据进行定标和移位④写选择电路:用来选择最高有效字和最低有效字。

2.桶形移位寄存器的输入通过多路选择器MUX来选择输入信号。

①取自DB数据总线的16位输入数据;②取自DB和CB扩展数据总线的32位输入数据;③来自累加器A或B的40位输入数据。

3.桶形移位寄存器的输出①输出至ALU的一个输入端;②经写MSW/LSW选择电路输出至EB总线。

4.桶形移位寄存器的功能主要用于格式化操作,为输入的数据定标。

①在进行ALU运算之前,对输入数据进行数据定标;②对累加器进行算术或逻辑移位;③对累加器进行归一化处理;④在累加器的内容存入数据存储器之前,对存储数据进行定标。

2.4.5比较、选择和存储单元CSSUCSSU单元主要完成累加器的高阶位与低阶位之间最大值的比较,即选择累加器中较大的字,并存储在数据存储器中。

工作过程:①比较电路COMP将累加器A或B的高阶位与低阶位进行比较;②比较结果分别送入TRN和TC中,记录比较结果以便程序调试;③比较结果输出至写选择电路,选择较大的数据;④将选择的数据通过总线EB存入指定的存储单元。

例如,CMPS指令可以对累加器的高阶位和低阶位进行比较,并选择较大的数存放在指令所指定的存储单元中。

指令格式:CMPSA,*AR1功能:对累加器A的高16位字(AH)和低16位字(AL)进行比较,若AH>AL,则AH→*AR1,TRN左移1位,0→TRN(0,0→TC;若AH,则AL→*AR1,TRN 左移1位,1→TRN(0,1→TC。

第一章绪论1.1 DSP的基本原理数字信号处理(简称DSP)是一门涉及多门学科并广泛应用于很多科学和工程领域的新兴学科。

数字信号处理是利用计算机或专用处理设备,以数字的形式对信号进行分析、采集、合成、变换、滤波、估算、压缩、识别等加工处理,以便提取有用的信息并进行有效的传输与应用。

数字信号处理是以众多学科为理论基础,它所涉及的范围极其广泛。

如数学领域中的微积分、概率统计、随机过程、数字分析等都是数字信号处理的基础工具。

它与网络理论、信号与系统、控制理论、通信理论、故障诊断等密切相关。

DSP可以代表数字信号处理技术(Digital SignalProcessing),也可以代表数字信号处理器(Digital Signal Processor)。

前者是理论和计算方法上的技术,后者是指实现这些技术的通用或专用可编程微处理器芯片。

数字信号处理包括两个方面的内容:1.法的研究 2.数字信号处理的实现数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。

数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理,以得到符合人们需要的信号形式。

数字信号处理是围绕着数字信号处理的理论、实现和应用等几个方面发展起来的。

数字信号处理在理论上的发展推动了数字信号处理应用的发展。

反过来,数字信号处理的应用又促进了数字信号处理理论的提高。

而数字信号处理的实现则是理论和应用之间的桥梁。

数字信号处理是以众多学科为理论基础的,它所涉及的范围极其广泛。

例如,在数学领域,微积分、概率统计、随机过程、数值分析等都是数字信号处理的基本工具,与网络理论、信号与系统、控制论、通信理论、故障诊断等也密切相关。

上海电力学院题目:DSP原理与应用大报告院系:计算机与信息工程专业年级:2008071学生姓名:王涛学号:20081938TMS320LF240x芯片概述TMS320系列包括:定点、浮点、多处理器数字信号处理器和定点DSP控制器。

TMS320系列DSP的体系结构专为实时信号处理而设计,该系列DSP 控制器将实时处理能力和控制器外设功能集于一身,为控制系统应用提供了一个理想的解决方案。

主要特性:灵活的指令集;内部操作灵活性;高速的运算能力;改进的并行结构;有效的成本。

定点系列TMS320C2000、TMS320C5000,浮点系列TMS320C6000(也有部分是定点DSP)。

TMS320系列同一产品系列中的器件具有相同的CPU结构,但片内存储器和外设的配置不同。

派生的器件集成了新的片内存储器和外设,以满足世界范围内电子市场的不同需求。

通过将存储器和外设集成到控制器内部,TMS320器件减少了系统成本,节省了电路板空间,提高了系统的可靠性。

TMS320LF240x DSP的特点:采用高性能静态CMOS技术,使得供电电压降为3.3V,减小了控制器的功耗;30MIPS的执行速度使得指令周期缩短到33ns(30MHz),提高了控制器的实时控制能力。

基于TMS320C2000 DSP的CPU核,保证了TMS320C240x DSP代码和TMS320系列DSP代码的兼容。

片内有32K字的FLASH程序存储器,1.5K字的数据/程序RAM,544字双口RAM(DARAM)和2K字的单口RAM(SARAM)。

两个事件管理器模块EVA和EVB,每个包括:两个16位通用定时器;8个16位的脉宽调制(PWM)通道。

可扩展的外部存储器(LF2407)总共192K字空间:64K字程序存储器空间;64K字数据存储器空间;64K字I/O寻址空间。

看门狗定时器模块(WDT)。

10位A/D转换器最小转换时间为500ns,可选择由两个事件管理器来触发两个8通道输入A/D转换器或一个16通道输入的A/D转换器。

《DSP芯片原理及应用》实验指导书唐山学院信息工程系DSP实验室2008年9月前言一.DSP原理及应用实验的任务数字信号处理实验是数字信号处理理论课程的一部分,它的任务是:1.通过实验进一步了解和掌握数字信号处理的基本理论及算法、数字信号处理的分析方法和设计方法。

2.学习和掌握数字信号处理的仿真和实现技术。

3.提高应用计算机的能力及水平。

二.实验设备DSP原理及应用实验所使用的设备由计算机、CPU板、语音单元、开关量输入输出单元、液晶显示单元、键盘单元、信号扩展单元、CPLD模块单元、模拟信号源、直流电源单元等组成。

其中计算机是CCS软件的运行环境,是程序编辑和调试的重要工具。

语音单元是语音输入和输出模块,主要完成语音信号的采集和回放。

开关量输入输出单元可以对DSP输入或输出开关量。

液晶显示单元可以对运行结果进行文字和图形的显示。

模拟信号源可以产生频率和幅度可调的正弦波、方波、三角波。

直流电源单元可以提供 3.3V、+5V、-12V和+12V 的直流电源。

装有CCS软件计算机与整个实验系统共同构成整个的DSP软、硬件开发环境。

所有的DSP芯片硬件的实验都是在这套实验装置上完成的。

三.对参加实验学生的要求1.阅读实验指导书,复习与实验有关的理论知识,明确实验目的。

2.按实验指导书要求进行程序设计。

3.在实验中注意观察,记录有关数据和图像,并由指导教师复查后才能结束实验。

4.实验后应断电,整理实验台,恢复到实验前的情况。

5.认真写实验报告,按规定格式做出图表、曲线、并分析实验结果。

字迹要清楚,画曲线要用坐标纸,结论要明确。

爱护实验设备,遵守实验室纪律。

目录第一章DSP原理及应用实验 (3)实验一常用指令实验 (3)实验二数据存储实验 (5)实验三I/O实验 (7)实验四定时器实验 (9)实验五外部中断实验 (11)实验六语音采集回放 (14)实验七语音信号的FFT分析 (18)实验八基于语音信号的IIR算法实验 (20)实验九语音信号的FIR算法实验 (23)第二章DSP CPU挂箱介绍 (26)第一节系统概述 (26)第二节54XB开发模板概述 (26)第一章DSP原理及应用实验实验一常用指令实验一.实验目的1.了解DSP开发系统的组成和结构;2.熟悉DSP开发系统的连接;3.熟悉DSP的开发界面,熟悉CCS的用户界面,学会CCS环境下程序编写、调试、编译、装载,学习如何使用观察窗口。

第2章DSP的硬件结构DSP的硬件结构:DSP与标准微处理器有许多共同的地方,都是由CPU、存储器、总线、外设、接口、时钟组成。

从广义上讲,可以说DSP是一种CPU。

但DSP和一般的CPU 又有不同, DSP有自己的一些独特的特点,比如采用哈佛结构、流水线操作、独立的硬件乘法器、独立的DMA总线和控制器等。

Von Neuman结构与Harvard结构:Harvard结构:程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,从而提高速度,目前的水平已达到90亿次浮点运算/秒(9000MFLOPS)。

MIPS—-Million Instruction Per SecondMFLOPS--Million Floating Operation Per Second流水操作(pipeline):独立的硬件乘法器:在卷积、数字滤波、FFT、相关、矩阵运算等算法中,都有A(kB(n-k一类的运算,大量重复乘法和累加.通用计算机的乘法用软件实现,用若干个机器周期。

DSP有硬件乘法器,用MAC指令(取数、乘法、累加)在单周期内完成。

独立的DMA总线和控制器:有一组或多组独立的DMA总线,与CPU的程序、数据总线并行工作,数据的传递和处理可以独立进行,DMA内部总线与系统总线完全分开,避开了总线使用上的瓶颈。

在不影响CPU工作的条件下,DMA速度已达800Mbyte/s。

CPU:通用微处理器的CPU由ALU和CU组成,其算术运算和逻辑运算通过软件来实现,如加法需要10个机器周期,乘法是一系列的移位和加法,需要数十个机器周期.DSP的CPU设置硬件乘法器,可以在单周期内完成乘法和累加。

移位:通用微处理器的移位,每调用一次移位指令移动1—bitDSP可以在一个机器周期内左移或右移多个bit,可以用来对数字定标,使之放大或缩小,以保证精度和防止溢出;还可以用来作定点数和浮点数之间的转换。

溢出:通用CPU中,溢出发生后,设置溢出标志,不带符号位时回绕,带符号位时反相,带来很大的误差DSP把移位输出的最高位(MSB)存放在一个位检测状态寄存器中,检测到MSB=1时,就通知下一次会发生溢出,可以采取措施防止。

第2章DSP的硬件结构DSP的硬件结构:DSP与标准微处理器有许多共同的地方,都是由CPU、存储器、总线、外设、接口、时钟组成。

从广义上讲,可以说DSP是一种CPU。

但DSP和一般的CPU 又有不同, DSP有自己的一些独特的特点,比如采用哈佛结构、流水线操作、独立的硬件乘法器、独立的DMA总线和控制器等。

Von Neuman结构与Harvard结构:Harvard结构:程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,从而提高速度,目前的水平已达到90亿次浮点运算/秒(9000MFLOPS)。

MIPS--Million Instruction Per SecondMFLOPS--Million Floating Operation Per Second流水操作(pipeline):独立的硬件乘法器:在卷积、数字滤波、FFT、相关、矩阵运算等算法中,都有A(kB(n-k一类的运算,大量重复乘法和累加。

通用计算机的乘法用软件实现,用若干个机器周期。

DSP有硬件乘法器,用MAC指令(取数、乘法、累加)在单周期内完成。

独立的DMA总线和控制器:有一组或多组独立的DMA总线,与CPU的程序、数据总线并行工作,数据的传递和处理可以独立进行,DMA内部总线与系统总线完全分开,避开了总线使用上的瓶颈。

在不影响CPU工作的条件下,DMA速度已达800Mbyte/s。

CPU:通用微处理器的CPU由ALU和CU组成,其算术运算和逻辑运算通过软件来实现,如加法需要10个机器周期,乘法是一系列的移位和加法,需要数十个机器周期。

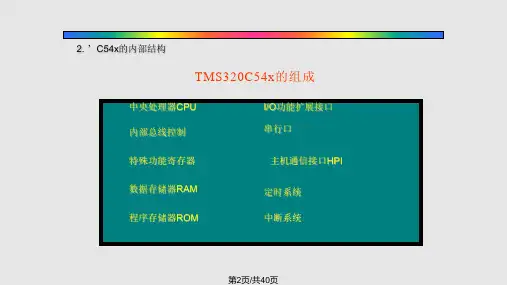

DSP的CPU设置硬件乘法器,可以在单周期内完成乘法和累加.移位:通用微处理器的移位,每调用一次移位指令移动1-bitDSP可以在一个机器周期内左移或右移多个bit,可以用来对数字定标,使之放大或缩小,以保证精度和防止溢出;还可以用来作定点数和浮点数之间的转换.溢出:通用CPU中,溢出发生后,设置溢出标志,不带符号位时回绕,带符号位时反相,带来很大的误差DSP把移位输出的最高位(MSB)存放在一个位检测状态寄存器中,检测到MSB=1时,就通知下一次会发生溢出,可以采取措施防止.数据地址发生器(DAG):在通用CPU中,数据地址的产生和数据的处理都由ALU来完成在DSP中,设置了专门的数据地址发生器(实际上是专门的ALU),来产生所需要的数据地址,节省公共ALU的时间.外设(peripherals):时钟发生器(振荡器与PLL)定时器(Timer)软件可编程等待状态发生器通用I/O同步串口(SSP)与异步串口(ASP)JTAG扫描逻辑电路(IEEE 1149.1标准便于对DSP作片上的在线仿真和多DSP条件下的调试’C54x的内部结构:中央处理器CPU 、内部总线控制、特殊功能寄存器、数据存储器RAM 、程序存储器ROM、I/O功能扩展接口、串行口、、主机通信接口HPI、定时系统、中断系统。

各部分的功能:①中央处理器CPU采用了流水线指令执行结构和相应的并行处理结构,可在一个周期内对数据进行高速的算术运算和逻辑运算。

②内部总线结构由一组程序总线、三组数据总线和四组地址总线组成,可在一个指令周期内产生两个数据存储地址,实现流水线并行数据处理。

③特殊功能寄存器共有26个特殊功能寄存器,位于具有特殊功能的RAM区。

主要用来对片内各功能模块进行管理、控制、监视。

④数据存储器RAMDARAM:在一个指令周期内,可对其进行两次存取操作,即一次读出和一次写入;SARAM:在一个指令周期内,只能进行一次存取操作。

⑤程序存储器ROM可由ROM和RAM配置而成,即程序空间可以定义在ROM上,也可以定义在RAM中。

当需要高速运行的程序时,可将片外ROM中的程序调入到片内RAM中,以提高程序的运行速度,降低对外部ROM的速度要求,增强系统的整体抗干扰性能。

⑥ I/O口’C54x共有两个通用I/O引脚(BIO和XF)。

BIO:主要用来监测外部设备的工作状态;XF:用来给外部设备发送信号。

’C54x芯片还配有主机接口(HPI)、同步串行口和64K字I/O空间。

HPI和串行口可以通过设置,用作通用I/O。

64K字的I/O空间可通过外加缓冲器或锁存电路,配合外部I/O读写控制时序构成片外外设的控制电路。

⑦串行口不同型号的’C54x芯片,所配置的串行口功能不同。

可分为4种:单通道同步串行口SP、带缓冲器单通道同步串行口BSP、并行带缓冲器多通道同步串行口McBSP、时分多通道带缓冲器串行口TMD。

⑧主机接口HPIHPI是一个与主机通信的并行接口,主要用于DSP与其它总线或CPU进行通信。

信息可通过’C54x的片内存储器与主机进行数据交换。

不同型号的器件配置不同HPI口,可分为:8位标准HPI接口、8位增强型HPI接口、 16位增强型HPI接口。

⑨定时器定时器是一个软件可编程的计数器,用来产生定时中断。

可通过设置特定的状态来控制定时器的停止、恢复、复位和禁止。

⑩中断系统’C54x的中断系统具有硬件中断和软件中断。

硬件中断:由外围设备信号引起的中断。

分为:片外外设引起的硬件中断;片内外设引起的硬件中断。

软件中断:由程序指令所引起的中断。

中断管理优先级:11~16个固定级。

TMS320C54x的CPU:(1)采用先进的多总线结构,通过1组程序总线、3组数据总线和4组地址总线来实现。

(2)40位算术逻辑运算单元ALU,包括1个40位桶形移位寄存器和2个独立的40位累加器。

(3)17×17位并行乘法器,与40位专用加法器相连,可用于进行非流水线的单周期乘法-累加运算。

(4)比较、选择、存储单元(CSSU),可用于Viterbi译码器的加法-比较-选择运算。

(5)指数编码器,是一个支持单周期指令EXP的专用硬件。

可以在一个周期内计算40位累加器数值的指数。

(6)配有两个地址生成器,包括8个辅助寄存器和2个辅助寄存器算术运算单元(ARAU)。

TMS320C54x的总线结构:TMS320C54x的结构是以8组16位总线为核心,形成了支持高速指令执行的硬件基础。

总线结构:1组程序总线PB、3组数据总线CB、DB、EB、4组地址总线PAB、CAB、DAB、EAB1.程序总线PB主要用来传送取自程序存储器的指令代码和立即操作数。

PB总线既可以将程序空间的操作数据(如系数表送至数据空间的目标地址中,以实现数据移动,也可以将程序空间的操作数据传送乘法器和加法器中,以便执行乘法-累加操作。

2.数据总线CB 、DB和EB3条数据总线分别与不同功能的内部单元相连接。

如:CPU、程序地址产生逻辑PAGEN、数据地址产生逻辑 DAGEN、片内外设和数据存储器等。

CB和DB用来传送从数据存储器读出的数据;EB用来传送写入存储器的数据。

3.地址总线PAB、CAB、DAB和EAB用来提供执行指令所需的地址。

’C54x读/写操作占用总线情况:(3 ALU输入数据的预处理当16位数据存储器操作数通过数据总线DB或CB输入时,ALU将采用两种方式对操作数进行预处理。

①若数据存储器的16位操作数在低16位时,则当SXM=0时,高24位 ( 39~16位用0填充;当SXM=1时,高24位 ( 39~16位扩展为符号位。

②若数据存储器的16位操作数在高16位时,则当SXM=0时,39~32位和15~0位用0填充;当SXM=1时,39~32位扩展为符号位,15~0位置0。

(4 ALU的输出ALU的输出为40位运算结果,通常被送至累加器A或B。

溢出处理:ALU的饱和逻辑可以对运算结果进行溢出处理。

当发生溢出时,将运算结果调整为最大正数(正向溢出)或最小负数(负向溢出)。

当运算结果发生溢出时:①若OVM=0,则对ALU的运算结果不作任何调整,直接送入累加器;②若OVM=1,则对ALU的运行结果进行调整。

当正向溢出时,将32位最大正数00 7FFFFFFFH装入累加器;当负向溢出时,将32位最小负数FF 80000000H装入累加器。

③状态寄存器ST0中与目标累加器相关的溢出标志OVA或OVB被置1。

累加器A和B :’C54x芯片有两个独立的40位累加器A和B,可以作为ALU或(乘法器/加法器MAC的目标寄存器,存放运算结果,也可以作为ALU或MAC的一个输入。

累加器A和B的差别:累加器A中的31-16位可以作为乘法器的一个输入。

1. 累加器结构【例2.4.1】累加器A=FF 0123 4567H,执行带移位的STH和STL指令后,求暂存器T和A的内容。

2.4.3 桶形移位寄存器:TMS320C54x的40位桶形移位寄存器主要用于累加器或数据区操作数的定标。

它能将输入数据进行0~31位的左移和0~16位的右移。

所移动的位数可由ST1中的ASM或被指定的暂存器T决定。

1. 组成框图①多路选择器MUX:用来选择输入数据。

②符号控制SC:用于对输入数据进行符号位扩展。

③移位寄存器:用来对输入的数据进行定标和移位④写选择电路 :用来选择最高有效字和最低有效字。

2.桶形移位寄存器的输入通过多路选择器MUX来选择输入信号。

①取自DB数据总线的16位输入数据;②取自DB和CB扩展数据总线的32位输入数据;③来自累加器A或B的40位输入数据。

3.桶形移位寄存器的输出①输出至ALU的一个输入端;②经写MSW/LSW选择电路输出至EB总线。

4.桶形移位寄存器的功能主要用于格式化操作,为输入的数据定标。

①在进行ALU运算之前,对输入数据进行数据定标;②对累加器进行算术或逻辑移位;③对累加器进行归一化处理;④在累加器的内容存入数据存储器之前,对存储数据进行定标。

2.4.5 比较、选择和存储单元CSSUCSSU单元主要完成累加器的高阶位与低阶位之间最大值的比较,即选择累加器中较大的字,并存储在数据存储器中。

工作过程:①比较电路COMP将累加器A或B的高阶位与低阶位进行比较;②比较结果分别送入TRN和TC中,记录比较结果以便程序调试;③比较结果输出至写选择电路,选择较大的数据;④将选择的数据通过总线EB存入指定的存储单元。

例如,CMPS指令可以对累加器的高阶位和低阶位进行比较,并选择较大的数存放在指令所指定的存储单元中。

指令格式:CMPS A,*AR1功能:对累加器A的高16位字(AH)和低16位字(AL)进行比较,若AH>AL,则AH→*AR1,TRN左移1位,0→TRN(0,0→TC;若AH ,则AL → *AR1 , TRN 左移 1 位,1 → TRN(0 ,1→TC。

TRN是状态转移寄存器,TC是状态比较寄存器。

指数编码器:指数编码器用于支持单周期指令EXP的专用硬件。

在EXP指令中,求出累加器中的指数值,并能以二进制补码的形式存储在T寄存器中。