MMU详解

- 格式:doc

- 大小:524.50 KB

- 文档页数:46

MMU(Memory Management Units)内存管理单元mmu是处理器的重要组成部分,主要功能是将程序使用的虚拟地址转换为处理器硬件能够直接访问的物理地址。

mmu为系统软件设立了转换查找表以支持虚实地址的映射。

在这些查找表中将规定虚实地址的对应关系及访问控制等一系列信息。

系统软件将利用处理器提供的查找表完成虚实地址的映射。

E500内核mmu中共使用两个查找表TLB0(translation lookaside buffer)和TLB1来实现虚拟地址和物理地址的转换。

其中TLB0用来进行页式映射,而TLB1用来实现段式映射。

段式映射:采用段式映射可以直接使用硬件提供的TLB1查找表,而不使用在内存中的页表就可以完成虚实地址的转换。

这种虚实地址的转换的效率较高。

我们目前一般只使用TLB1实现虚实地址的转换。

在E500 V1内核中,TLB1中一共有16个Entry,其中每个Entry 能映射4KB~256MB大小的页面。

页式映射:使用TLB0和系统页表完成虚实地址的转换。

其中TLB0存放在E500内核中,而系统页表存放在主存储器中。

在E500 V1内核中,TLB0中一共有256个Entry,其中每个Entry只能固定映射4KB大小的页面。

因此在TLB0中最多只能保存256*4KB=1MB 大小的虚拟地址空间。

对于32位的PowerPC处理器,TLB0能直接映射的虚拟地址空间远远不够,不可避免的会出现TLB Miss异常,即处理器访问的地址空间不在TLB0的Entry 中。

当发生这种异常时,需要查找系统页表,获得与被访问虚拟地址对应的物理地址,并同步TLB0。

E500 V1内核的虚实地址转换:有上图可知,E500内核的41位虚拟地址由1位AS,8位PID和32位的EA组成。

AS位:在E500内核中根据AS位的不同将地址空间分为两种,分别为地址空间0和地址空间1。

AS=0对应地址空间0;AS=1对应地址空间1。

MMU所起的作用

一、名词解释

①逻辑地址(虚拟地址)

用户程序经编译、链接以后形成的每条指令或数据单元的地址,这些地址都是相对于某个基地址来编制的。

②逻辑地址空间

某个用户程序的虚拟地址的集合。

③物理地址(绝对地址)

处理机能直接访问的存储器地址。

④物理地址空间

物理地址空间是指进程在内存中一系列存储信息的物理单元的集合。

物理地址空间也叫存储空间,存储空间与地址空间既相互关联,又相互独立,是内存管理的核心概念。

二、MMU所起的作用

1.内存分配和回收

使各作业或进程各得其所

2.内存保护

内存保护就是确保多个进程都在各自分配到内存区域内操作,互不干扰,防止一个进程破坏其他进程的信息。

3.内存扩充

内存“扩充”包含了存储器利用的提高和扩充两方面的内容。

为用户提供比内存物理空间大得多的地址空间。

比较典型的内存扩充是虚拟存储器。

4.地址映射

地址映射就是将进程的逻辑地址变换为内存中的物理地址。

我们需要实现从逻辑地址到物理地址的变换,即实现从虚地址到实地址的变换。

这种变换就是重定位。

MMU简介1.概念MMU是Memory Management Unit的缩写,中文名是内存管理单元,它是中央处理器(CPU)中用来管理虚拟存储器、物理存储器的控制线路,同时也负责虚拟地址映射为物理地址,以及提供硬件机制的内存访问授权。

虚拟地址映射为物理地址内存访问授权另一个概念:内存管理,是指软件运行时对计算机内存资源的分配和使用的技术。

其最主要的目的是如何高效,快速的分配,并且在适当的时候释放和回收内存资源。

2.术语虚拟地址空间——又称逻辑地址空间,CPU看到的使用的地址空间。

32位CPU可以使用0~0xFFFFFFFF(4G)的地址空间。

物理地址空间——实际的内存空间,例如一个256M的内存,实际地址空间也就是0~0x0FFFFFFF(256M)。

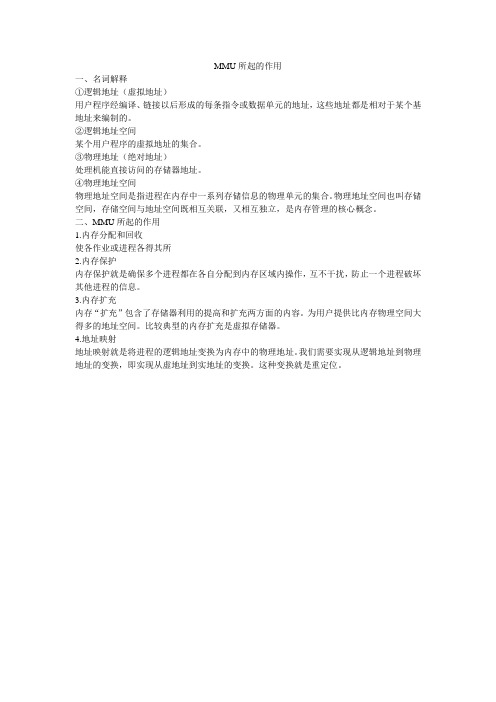

VA——virtual address,虚拟地址PA——physical address,物理地址3.背景内存有限内存保护内存碎片1)内存有限——交换程序很大,而内存不够一次装入太大的程序。

在磁盘中分配虚拟内存。

进程在内存中执行,可以暂时从内存中交换(swap)出去到备份存储上,当需要时再调回到内存中。

2)内存保护不同进程使用不同的物理地址空间,必须防止不同进程使用同一块内存产生冲突。

内存保护最基本的思路是操作系统为不同进程分配不同的地址空间。

可以是逻辑地址,也可以是实际物理地址。

(但如果是实际物理地址,操作系统还要负责实际物理地址的分配调度,任务过重,因此设计MMU减轻操作系统负担,负责逻辑地址到物理地址的映射。

)3)内存碎片最初操作系统的内存是连续分配的,即进程A需要某一大小的内存空间,如200KB,操作系统就需要找出一块至少200KB的连续内存空间给进程A。

随着系统的运行,进程终止时它将释放内存,该内存可以被操作系统分配给输入队列里的其他等待内存资源的进程。

可以想象,随着进程内存的分配和释放,最初的一大块连续内存空间被分成许多小片段,即使总的可用空间足够,但不再连续,因此产生内存碎片。

简单介绍MMU的工作原理

MMU(Memory Management Unit,内存管理单元)是计算机系统中的一种硬件设备,负责将逻辑地址转换为物理地址,实现虚拟内存和物理内存之间的映射和管理。

MMU的工作原理如下:

1. 虚拟地址转换:当CPU访问一个地址时,MMU首先接收到这个地址(即虚拟地址),然后根据内部的地址映射表将其转换为物理地址。

2. 地址映射表:MMU内部有一个地址映射表,它记录了虚拟地址和物理地址之间的对应关系。

这个表中的每一项称为页表项。

通常,虚拟地址被划分为若干个页面,而物理地址也被划分为相同的大小的内存块。

每个页表项记录了虚拟页面和物理页面之间的对应关系。

3. 地址转换:MMU根据地址映射表中的对应关系,将虚拟地址中的页号(Page Number)转换为物理地址中的页号,以及虚拟地址中的页面内偏移(Page Offset)转换为物理地址中的页面内偏移。

4. 访问权限控制:MMU还会根据地址映射表中的附加信息,如权限位,来判断对于特定的虚拟地址,是否允许对其进行读、写、执行等操作。

如果权限不足,则会触发异常或终止进程。

通过MMU的工作,操作系统可以实现虚拟内存的概念。

虚拟内存可以将大于物理内存的程序部分存储在辅助存储设备上,而只将当前需要的部分调入物理内存中,从而实现更高效的内存管理和更大的可用内存空间。

三层交换机之MMU概述MMU介于Ingress和Egress之间,被所有端⼝共享。

MMU同时⽀持内部和外部缓存。

⼀个⼊⼝报⽂,可以缓存到内部缓存、外部缓存或者both,取决于报⽂转发到哪个端⼝(Egress Port)。

每个Egress Port要么指定内部缓存,要么指定外部缓存,not both。

对于组播报⽂这种转发到多个Egress Ports的情况,则可能报⽂会根据Egress Port同时缓存到内部和外部缓存中。

MMU包含以下功能组件:(buffer blocks⽤来缓存报⽂,queue blocks⽤来缓存控制结构和转发数据)Admission Control:根据⼊端⼝和优先级、出端⼝、队列和缓存占⽤情况,决定转发还是丢弃报⽂Internal Buffer:2MB⽚内SRAM,EMA(External Memory Access) buffer pool也在其中External Buffer:外部DRAM(外接DDR)EMA Queues:访问External Buffer的队列,即Ingress和外部DRAM之间的缓冲区Replication Engine Work Queues:组播、镜像包和copy_to_cpu报⽂的队列Egress Port Queues:每个Egress Port⼀组队列,包括Internal Buffer Queues和External Buffer Queues,总共有256K条egress queuesLife of a Packet Inside the MMUMMU内部报⽂转发流程如下图,主要分为控制路径和数据路径:控制路径上报⽂头(packet header)缓存在Replication Engine Queues和Egress Queues中;数据路径上报⽂负载(packet payload)缓存到Internal Buffers、EMA和External Buffers。

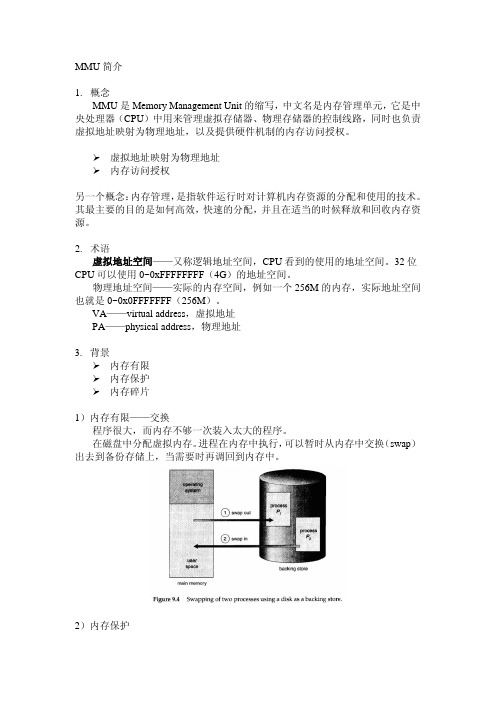

MMU 技术理解MMU 支持三种地址转换:1.页地址转换(每页4K )2.块地址转换(每块128K -256M )3.实地址转换(无地址转换-物理地址与虚地址一一对应)CPU 实现地址转换的机制:MMU 在关闭时,CPU 处理地址就走蓝线所示路线,程序的逻辑地址就与物理地址一一对应,这地址包括CPU 的4G 的地址空间,不仅仅指内存部分。

当MMU 打开后CPU 处理地址就走红、黄两条路线,黄色路线是块地址转换,优先于页地址转换执行,逻辑地址到物理地址的转换是通过与BAT 表比较实现的,BAT 表一共有8组表项,4个指令BAT 表项,4个数据BAT 表项。

这个表存放在SPR (特殊用途寄存器)528-SPR543中。

在BSP 中对于这个BAT 表的设置是在sysLib.c 中通过sysBatDesc 数组实现的。

根据VxWorks 的内存管理的建议,虽然将内存地址同时映射成块地址和页地址是CPU 允许的,但由于VxWorsk 的缘故,这种做法会导致出错,所以块地址映射一般用于I/O 地址映射,PROM ,FLASH 地址映射,由于BAT 表无法不激活,所以不管在BAT 表中放什么值都将会有一段地址空间被作为块地址寻址,这很容易与页地址映射造成冲突,所以在sp8240的BSP 中8个BAT 表项被全部用作FLASH 地址空间的映射,避开了作为页地址映射的内存地址空间。

31逻辑地址MMU 关闭实地址模式逻辑地址=物理地址物理地址31与BAT 寄存器比较块地址转换物理地址31段地址描述符T =0T =1直接存取段转换与硬件相关31页地址转换虚拟地址51查找页表物理地址31早期CPU 用于访问外部总线的方式,建议不用块地址转换优先页地址转换块地址转换MMU 打开上图中的红线部分是逻辑地址到物理地址的页映射方式,页映射方式首先通过段描述符,确定逻辑地址是访问页地址还是直接存取段地址(建议不用),若是访问页地址,则根据页描述符中的内容生成一个52位的虚拟地址,MMU根据8240提供的TLB缓冲(内部寄存器)用于快速确定与52位虚拟地址对应的32位物理地址,若TLB缓冲中没有对应关系则根据内存中的页表确定。

MMU(⼀)4. MMU现代操作系统普遍采⽤虚拟内存管理(Virtual Memory Management)机制,这需要处理器中的MMU(Memory Management Unit,内存管理单元)提供⽀持,本节简要介绍MMU的作⽤。

⾸先引⼊两个概念,虚拟地址和物理地址。

如果处理器没有MMU,或者有MMU但没有启⽤,CPU执⾏单元发出的内存地址将直接传到芯⽚引脚上,被内存芯⽚(以下称为物理内存,以便与虚拟内存区分)接收,这称为物理地址(Physical Address,以下简称PA),如下图所⽰。

图 17.5. 物理地址如果处理器启⽤了MMU,CPU执⾏单元发出的内存地址将被MMU截获,从CPU到MMU的地址称为虚拟地址(Virtual Address,以下简称VA),⽽MMU将这个地址翻译成另⼀个地址发到CPU芯⽚的外部地址引脚上,也就是将VA映射成PA,如下图所⽰。

图 17.6. 虚拟地址如果是32位处理器,则内地址总线是32位的,与CPU执⾏单元相连(图中只是⽰意性地画了4条地址线),⽽经过MMU转换之后的外地址总线则不⼀定是32位的。

也就是说,虚拟地址空间和物理地址空间是独⽴的,32位处理器的虚拟地址空间是4GB,⽽物理地址空间既可以⼤于也可以⼩于4GB。

MMU将VA映射到PA是以页(Page)为单位的,32位处理器的页尺⼨通常是4KB。

例如,MMU可以通过⼀个映射项将VA的⼀页0xb7001000~0xb7001fff映射到PA的⼀页0x2000~0x2fff,如果CPU执⾏单元要访问虚拟地址0xb7001008,则实际访问到的物理地址是0x2008。

物理内存中的页称为物理页⾯或者页帧(Page Frame)。

虚拟内存的哪个页⾯映射到物理内存的哪个页帧是通过页表(Page Table)来描述的,页表保存在物理内存中,MMU会查找页表来确定⼀个VA应该映射到什么PA。

操作系统和MMU是这样配合的:1. 操作系统在初始化或分配、释放内存时会执⾏⼀些指令在物理内存中填写页表,然后⽤指令设置MMU,告诉MMU页表在物理内存中的什么位置。

mmu 原理MMU原理。

MMU(Memory Management Unit)是计算机系统中的一个重要组成部分,它负责处理内存管理的相关工作。

在现代计算机系统中,MMU扮演着至关重要的角色,它通过地址转换、内存保护和虚拟内存等功能,为计算机系统提供了高效、安全和灵活的内存管理机制。

首先,MMU通过地址转换的方式实现了虚拟内存的概念。

在计算机系统中,每个进程都拥有自己的虚拟地址空间,而实际的物理内存是有限的。

MMU通过将虚拟地址映射到物理地址的方式,实现了对内存的透明管理。

这种虚拟内存的管理方式,使得每个进程都可以拥有独立的地址空间,从而提高了系统的安全性和稳定性。

其次,MMU还负责内存保护的工作。

在多道程序设计的环境下,不同的进程可能会同时运行在计算机系统中。

为了防止进程之间相互干扰,MMU通过设置访问权限位和地址空间标识符等机制,实现了对内存的保护。

这样一来,即使有恶意程序或者错误程序的存在,也不会对系统的整体稳定性造成影响。

最后,MMU还实现了虚拟内存到物理内存的映射。

在实际的计算机系统中,物理内存的容量是有限的,而虚拟内存的容量是可以无限扩展的。

MMU通过页表、页目录等数据结构,实现了虚拟内存到物理内存的映射,从而为系统提供了更大的地址空间。

这种虚拟内存的管理方式,使得系统可以运行更多的进程,提高了系统的并发性能。

综上所述,MMU作为计算机系统中的重要组成部分,扮演着至关重要的角色。

它通过地址转换、内存保护和虚拟内存等功能,为计算机系统提供了高效、安全和灵活的内存管理机制。

在今后的计算机系统设计中,MMU仍然会扮演着重要的角色,为系统的性能和稳定性提供保障。

mmu原理MMU原理。

MMU(Memory Management Unit)是计算机系统中的一个重要组成部分,它负责将逻辑地址转换为物理地址,实现内存管理和地址映射。

在现代计算机系统中,MMU扮演着至关重要的角色,它的工作原理对于理解计算机内存管理和操作系统设计都至关重要。

MMU的工作原理可以简单概括为地址转换和访问权限控制两个方面。

首先,当CPU发出一个访存请求时,MMU会将逻辑地址转换为对应的物理地址,这样就能够准确地访问到内存中的数据。

其次,MMU还负责对内存的访问权限进行控制,确保程序只能访问到其拥有权限的内存区域,从而提高系统的安全性和稳定性。

在实际的计算机系统中,MMU通常通过页表来实现地址转换和访问权限控制。

页表是一个存储在内存中的数据结构,它记录了逻辑地址和物理地址之间的映射关系,以及每个页面的访问权限信息。

当CPU发出访存请求时,MMU会根据页表中的映射关系将逻辑地址转换为物理地址,并检查访问权限是否合法。

除了页表,MMU还可以通过地址变换缓冲器(TLB)来提高地址转换的效率。

TLB是一个高速缓存,它存储了最近使用过的页表项,可以加速逻辑地址到物理地址的转换过程。

当CPU发出访存请求时,MMU会首先在TLB中查找对应的页表项,如果找到则直接进行地址转换,否则再去访问页表。

总的来说,MMU的工作原理可以概括为地址转换和访问权限控制两个方面,通过页表和TLB来实现逻辑地址到物理地址的转换,并对内存的访问权限进行控制。

理解MMU的工作原理对于深入理解计算机系统和操作系统设计都至关重要,它是计算机系统中一个不可或缺的组成部分。

MMU解读mmu页表也是放在内存中,mmu⾥有⼀个寄存器存放页表⾸地址,从⽽找到页表(地址为物理地址)。

当我们执⾏⼀个程序时,会把这个进程的mmu页表地址放到该寄存器中,跳转找到mmu页表执⾏。

TLB是MMU内部的缓存,页表是每个进程都有的⼀段保存虚拟地址到物理地址对应映射关系的数组,此数据在内存中(TLB---Translation Lookaside Buffers,转译查找缓存):由于从MVA到PA的转换需要访问多次内存,⼤⼤降低了CPU的性能,故提出TLB办法改进。

当CPU发出⼀个虚拟地址时,MMU⾸先访问TLB。

如果TLB中含有能转换这个虚拟地址的描述符,则直接利⽤此描述符进⾏地址转换和权限检查,否则MMU访问页表找到描述符后再进⾏地址转换和权限检查,并将这个描述符填⼊TLB中,下次再使⽤这个虚拟地址时就直接使⽤TLB⽤的描述符。

使⽤TLB需要保证TLB中的内容与页表⼀致,在启动MMU之前,页表中的内容发⽣变化后,尤其要注意。

⼀般的做法是在启动MMU之前使整个TLB⽆效,改变页表时,使所涉及的虚拟地址对应的TLB中条⽬⽆效。

不同进程切换时,通过CR3(x86时)寄存器把页表缓存地址传递给MMU模块,进⽽时MMU的TLB更新为对应进程的页表内容程序的⼤部分代码都可以在必要的时候才加载到内存去执⾏,运⾏完后可以被直接丢弃或者被其他代码覆盖。

我们PC上同时跑着很多的应⽤程序,每个应⽤程序使⽤的虚拟地址空间⼏乎可以整个线性地址空间(除了部分留给操作系统或者预留它⽤),可以认为每个应⽤程序都独占了整个虚拟地址空间(字长是32的CPU是4G的虚拟地址空间),但我们的物理内存只是1G或者2G。

即多个应⽤程序在同时竞争使⽤这块物理内存,其必然会导致某个时刻只存在程序的某个⽚段在执⾏,也即是所有程序代码和数据分时复⽤物理内存空间—这就是内存管理单元(MMU)⼯作核⼼作⽤所在。

处理器系列的芯⽚(如X86、ARM7以上、MIPS)⼀般都会有MMU,跟操作系统⼀块实现虚拟内存管理,MMU也是Linux、Wince等操作系统的硬件要求。

1-3、ARM开发步步深入之MMU初窥实验目的:启用MMU,映射SDRAM的地址空间,操作虚拟地址实现“点灯大法”,借此掌握MMU的使用。

实验环境及说明:恒颐S3C2410开发板H2410。

H2410核心板扩展有64MB的K4S561632 SDRAM(4M*16bit*4BANK),地址范围是0x30000000~0x33FFFFFF。

GPIO端口的地址范围是0x56000000~0X560000B0。

实验思路:开发板上电启动后,自动将NandFlash开始的4K数据复制到SRAM中,然后跳转到0地址开始执行,然后初始化存储控制器SDRAM,把2K后的代码从SRAM中复制到SDRAM中(存放在0x30004000,前16KB用来存放页表)、设置页表、启动MMU 实现虚拟地址映射GPIO寄存器和SDRAM,最后跳转到SDRAM中(地址0xB0004000)运行。

重新设置栈指针,跳到点灯代码的入口点实现点灯操作。

知识掌握:MMU地址转换、内存访问权限检查、TLB及Cache的使用一、MMU地址转换:1.首先弄清除为什么要使用MMU纳?MMU即内存管理单元,直白一点的讲,就像食堂的餐具,所有的学生一起吃饭时不够用,但食堂又不想再出资购买新的餐具(原因很明显:一方面要成本,另一方面又占地方。

这就像增加内存一样),那么有没有解决办法?根据以往经验得知不可能全学校的学习一起都到食堂吃饭,于是食堂就找几个人负责餐具的管理(相当于MMU),他们一方面发放餐具,保证来的同学有餐具可用,另一方面又回收用完的餐具(这就相当于虚拟地址到物理地址之间建立了一个映射一样,内存还是那么多,但从任意单个程序角度都好像用不完一样)。

当然如果有同学一个人拿好几套餐具肯定不允许的(这就相当于内存的权限检查)。

MMU在地址转换过程中涉及到三种地址:(VA---Virtual Address,虚拟地址)---这个就相当于餐具存放的地方(大家都可以领到餐具)。

CPU核心看到和用到的只是虚拟地址VA,至于VA如果去对应物理地址PA,CPU 核心不理会,大家也不会去关心总共有多少餐具吧;(MVA---Modified Virtual Address,变换后的虚拟地址)---这个相当于放假的时候,人很少,只发餐具好了,用过的就不先回收了,节省人员了。

Caches和MMU看不到VA,他们利用MVA转换得到PA,放假了回收餐具的人也不需要一直寻找用完的餐具;(PA---Physical Address,物理地址)---实际的餐具量,就那些。

实际设备看不到VA、MVA,读写它们使用的是物理地址PA,同学们就餐一般会领到餐具。

2.虚拟地址到物理地址的转换过程。

ARM使用页表来进行转换,S3C2410最多会用到两级页表,以段(Section,1M)的方式进行转换时只用到一级页表,以页(Page)的方式进行转换时用到两级页表。

页的大小有3种:大页(64KB)、小页(4KB)和极小页(1KB)。

本文只是以段地址转换过程为例来讲解一下,页的转换大同小异。

★首先有个页表基址寄存器(位置为协处理器CP15的寄存器C2),它里面写入的就是一级页表的地址,通过读取它就可以找到一级页表存放的起始位置。

一级页表的地址是16K对齐(所以[13:0]为0,使用[31:14]存储页表基址)。

一级页表使用4096个描述符来表示4GB空间,所以每个描述符对应1MB的虚拟地址,存储它对应的1MB物理空间的起始地址,或者存储下一级页表的地址。

使用MVA[31:20]来索引一级页表(31-20一共12位,2^12=4096,所以是4096个描述符),得到一个描述符,每个描述符占4个字节。

★描述符最后两位为0B10时,即是段的方式映射。

[31:20]为段基址,此描述符低20位填充0后就是一块1MB物理地址空间的起始地址。

MVA[19:0]用来在这1MB空间中寻址。

描述符的位[31:20]和MVA[19:0]构成了这个虚拟地址MVA对应的物理地址。

以段的方式进行映射时,虚拟地址MVA到物理地址PA的转换过程如下:①页表基址寄存器位[31:14]和MVA[31:20]组成一个低两位为0的32位地址,MMU利用这个地址找到段描述符;②取出段描述符的位[31:20](段基址),它和MVA[19:0]组成一个32位的物理地址(这就是MVA对应的PA)。

二、内存的访问权限检查内存的访问权限检查决定一块内存是否允许读/写。

这由CP15寄存器C3(域访问控制)、描述符的域(Domain)、CP15寄存器C1的R/S/A位和描述符的AP位共同决定。

“域”决定是否对某块内存进行权限检查,"AP"决定如何对某块内容进行权限检查。

S3C2440有16个域,CP15寄存器C3中每两位对应一个域(一共32位),用来表示这个域是否进行权限检查。

每两位数据的含义:00---无访问权限(任何访问都将导致"Domain fault"异常);01---客户模式(使用段描述符、页描述符进行权限检查);10---保留(保留,目前相当于“无访问权限”);11---管理模式(不进行权限检查,允许任何访问)。

"Domain"占用4位,用来表示内存属于0-15哪一个域。

三、TLB和Cache首先说两者都是利用程序访问的局部性原理,通过设置高速、小容量的存储器来提高性能。

1.(TLB---Translation Lookaside Buffers,转译查找缓存):由于从MVA到PA的转换需要访问多次内存,大大降低了CPU的性能,故提出TLB办法改进。

当CPU发出一个虚拟地址时,MMU首先访问TLB。

如果TLB中含有能转换这个虚拟地址的描述符,则直接利用此描述符进行地址转换和权限检查,否则MMU访问页表找到描述符后再进行地址转换和权限检查,并将这个描述符填入TLB中,下次再使用这个虚拟地址时就直接使用TLB用的描述符。

使用TLB需要保证TLB中的内容与页表一致,在启动MMU之前,页表中的内容发生变化后,尤其要注意。

一般的做法是在启动MMU之前使整个TLB无效,改变页表时,使所涉及的虚拟地址对应的TLB中条目无效。

2.(Cache,高速缓存):为提高程序的运行速度,在主存和CPU通用寄存器之间设置一个高速的、容量相对较小的存储器,把正在执行的指令地址附近的一部分指令或数据从主存调入这个存储器,供CPU 在一段时间内使用。

★写数据的两种方式:①(Write Through,写穿式)---任一CPU发出写信号送到Cache的同时,也写入主存,保证主存的数据同步更新。

优点是操作简单,但由于主存速度慢,降低了系统的写速度并占用了总线的时间。

②(Write Back,回写式)---数据一般只写到Cache,这样可能出现Cache中的数据得到更新而主存中的数据不变(数据陈旧)的情况。

此时可在Cache中设一个标志地址及数据陈旧的信息,只有当Cache中的数据被换出或强制进行”清空“操作时,才将原更新的数据写入主存响应的单元中,保证了Cache和主存中数据一致。

★Cache有以下两个操作:①(Clean,清空)---把Cache或Write buffer中已经脏的(修改过,但未写入主存)数据写入主存。

②(Invalidate,使无效)---使之不能再使用,并不将脏的数据写入主存。

★S2C2440内置了(ICaches,指令Cache)、(DCaches,数据Cache)和(Write buffer,写缓存),操作时需要用到描述符中的C 位(Ctt)和B位(Btt)。

①(ICaches,指令Cache)---系统刚上电或复位时,ICaches中的内容是无效的,并且ICaches功能关闭。

往Icr位(CP15协处理器中寄存器1的第12位)写1可以启动ICaches,写0停止ICaches。

ICaches一般在MMU开启后使用,此时描述符的C位用来表示一段内存是否可以被Cache。

若Ctt=1,允许Cache,否则不允许。

如果MMU没有开启,ICaches也可以被使用,此时CPU读取指令时所涉及的内存都被当做允许Cache。

ICaches关闭时,CPU每次取指都要读取主存,性能低,所以通常尽早启动ICaches。

ICaches开启后,CPU每次取指时都会先在ICaches中查看是否能找到所用指令,而不管Ctt是0还是1。

如果找到成为Cache命中,找不到称为Cache丢失,ICaches被开启后,CPU的取指有如下三种情况:Cache命中且Ctt为1时,从ICaches中取指,返回CPU;Cache丢失且Ctt为1时,CPU从主存中取指,并且把指令缓存到Cache中;Ctt为0时,CPU从主存中取指。

②(DCaches,数据Cache)---与ICaches相似,系统刚上电或复位时,DCaches中的内容无效,并且DCaches功能关闭,Write buffer中的内容也是被废弃不用的。

往Ccr位(CP15协处理器中寄存器1的第二位)写1启动DCaches,写0停止DCaches。

Write buffer和DCaches紧密结合,额米有专门的控制来开启和停止它。

与ICaches不同,DCaches功能必须在MMU 开启之后才能被使用。

DCaches被关闭时,CPU每次都去内存取数据。

DCaches被开启后,CPU每次读写数据时都会先在DCaches 中查看是否能找到所要的数据,不管Ctt是0还是1,找到了称为Cache命中,找不到称为Cache丢失。

★使用Cache时需要保证Cache、Write buffer的内容和主存内容一致,保证下面两个原则:①清空DCaches,使主存数据得到更新。

②使无效ICaches,使CPU取指时重新读取主存。

在实际编写程序时,要注意如下几点:①开启MMU前,使无效ICaches,DCaches和Write buffer。

②关闭MMU前,清空ICaches、DCaches,即将“脏”数据写到主存上。

③如果代码有变,使无效ICaches,这样CPU取指时会从新读取主存。

④使用DMA 操作可以被Cache的内存时:将内存的数据发送出去时,要清空Cache;将内存的数据读入时,要使无效Cache。

⑤改变页表中地址映射关系时也要慎重考虑。

⑥开启ICaches或DCaches时,要考虑ICaches或DCaches中的内容是否与主存保持一致。

⑦对于I/O地址空间,不使用Cache和Write buffer。

四、MMU、TLB及Cache的控制指令S3C2410除了ARM920T的CPU核心外,还有若干个协处理器,用来帮助主CPU完成一些特殊功能,对MMU、TLB及Cache等的操作就涉及到协处理器。