数字逻辑——PLA

- 格式:ppt

- 大小:861.50 KB

- 文档页数:9

可编程逻辑器件的设计与优化可编程逻辑器件(Programmable Logic Device,PLD)是一种可以根据用户需求重新编程的数字电路器件。

它具有灵活性高、适应性强的特点,被广泛应用于数字电路设计和嵌入式系统中。

本文将探讨可编程逻辑器件的设计与优化。

一、可编程逻辑器件的基本原理可编程逻辑器件是一种数字电路芯片,它由可编程逻辑阵列(PLA)和输入/输出引脚组成。

PLA是由多个可编程逻辑门和可编程连接器组成的,通过编程可以实现不同的逻辑功能。

输入/输出引脚用于与外部设备进行数据交换。

二、可编程逻辑器件的设计流程1.需求分析:根据系统的功能需求,确定逻辑电路的功能和性能指标。

这包括逻辑门的类型和数量、输入/输出引脚的数量和功能等。

2.逻辑设计:根据需求分析的结果,进行逻辑电路的设计。

这包括逻辑门的选择和连接方式、输入/输出引脚的分配等。

在设计过程中,需要考虑电路的可靠性、功耗和面积等因素。

3.编程:设计完成后,需要将逻辑电路的功能编程到可编程逻辑器件中。

编程可以通过硬件编程器或软件工具实现。

编程的过程包括逻辑门的配置和连接器的设置。

4.验证与测试:编程完成后,需要对可编程逻辑器件进行验证和测试。

这包括逻辑电路的功能验证和性能测试。

验证可以通过仿真软件或实际硬件平台进行。

三、可编程逻辑器件的优化方法1.面积优化:可编程逻辑器件的面积是指芯片所占的物理空间。

面积优化是通过减少逻辑门的数量和优化逻辑门的布局来实现的。

可以采用逻辑合并、逻辑共享和逻辑分解等方法来减少逻辑门的数量。

优化逻辑门的布局可以减少信号传输的延迟和功耗。

2.功耗优化:功耗是可编程逻辑器件在工作过程中所消耗的能量。

功耗优化可以通过减少逻辑门的开关次数和优化电路结构来实现。

可以采用时钟门控、时钟频率调节和动态电压调节等方法来减少逻辑门的开关次数。

优化电路结构可以减少信号传输的功耗。

3.时序优化:时序是指电路中信号的传输时间。

时序优化可以通过减少信号传输的延迟和优化时钟信号的分配来实现。

pld名词解释

PLD,全称为可编程序逻辑器件(Programmable Logic Device),

是一种可以根据用户需求进行逻辑功能定制的集成电路。

它是一种非

常常见的数字电路设计器件,常用于数字电路设计中。

PLD主要有两种:可编程逻辑阵列(PAL)和可编程数组逻辑器件(PLA)。

可编程逻辑阵列(PAL)是一种基于石英门阵列的PLD。

它采用布尔逻辑和存储单元来构建逻辑门,并可以通过编程关闭或打开某些逻

辑门,以达到不同的逻辑功能。

PAL在设计时需要根据应用需求进行定制,可以达到相对较高的性能和速度。

可编程数组逻辑器件(PLA)也是一种常用的PLD。

它由多个可编程门阵列(PGA)和输出逻辑阵列(OLA)组成。

PGA主要用于组合逻辑功能的实现,而OLA用于时序逻辑的实现。

PLA的优点在于可以实现复杂的逻辑功能,并可以在运行时修改逻辑功能,同时具有较高的灵活

性和易设计性。

PLD的优点在于可以提高数字电路的可重复用性、可维护性和可

扩展性。

它们比较便宜,同时也比较简单,可以轻松地在现有的电路

板上添加或调整逻辑功能。

由于PLD的配置和设计可以在软件中完成,可以方便地集成到大型系统和嵌入式系统中。

PLD已经成为了设计数字逻辑的有力工具,广泛应用于数字通信、计算机硬件、工业自动化、

汽车电子等领域。

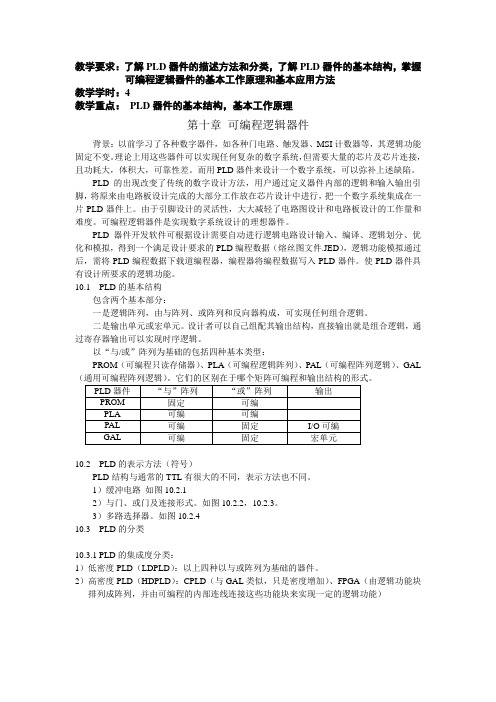

教学要求:了解PLD器件的描述方法和分类,了解PLD器件的基本结构,掌握可编程逻辑器件的基本工作原理和基本应用方法教学学时:4教学重点:PLD器件的基本结构,基本工作原理第十章可编程逻辑器件背景:以前学习了各种数字器件,如各种门电路、触发器、MSI计数器等,其逻辑功能固定不变。

理论上用这些器件可以实现任何复杂的数字系统,但需要大量的芯片及芯片连接,且功耗大,体积大,可靠性差。

而用PLD器件来设计一个数字系统,可以弥补上述缺陷。

PLD的出现改变了传统的数字设计方法,用户通过定义器件内部的逻辑和输入输出引脚,将原来由电路板设计完成的大部分工作放在芯片设计中进行,把一个数字系统集成在一片PLD器件上。

由于引脚设计的灵活性,大大减轻了电路图设计和电路板设计的工作量和难度。

可编程逻辑器件是实现数字系统设计的理想器件。

PLD器件开发软件可根据设计需要自动进行逻辑电路设计输入、编译、逻辑划分、优化和模拟,得到一个满足设计要求的PLD编程数据(熔丝图文件.JED),逻辑功能模拟通过后,需将PLD编程数据下载道编程器,编程器将编程数据写入PLD器件。

使PLD器件具有设计所要求的逻辑功能。

10.1PLD的基本结构包含两个基本部分:一是逻辑阵列,由与阵列、或阵列和反向器构成,可实现任何组合逻辑。

二是输出单元或宏单元。

设计者可以自己组配其输出结构,直接输出就是组合逻辑,通过寄存器输出可以实现时序逻辑。

以“与/或”阵列为基础的包括四种基本类型:PROM(可编程只读存储器)、PLA(可编程逻辑阵列)、PAL(可编程阵列逻辑)、GAL10.2PLD的表示方法(符号)PLD结构与通常的TTL有很大的不同,表示方法也不同。

1)缓冲电路如图10.2.12)与门、或门及连接形式。

如图10.2.2,10.2.3。

3)多路选择器。

如图10.2.410.3PLD的分类10.3.1 PLD的集成度分类:1)低密度PLD(LDPLD):以上四种以与或阵列为基础的器件。

pla技术步骤PLA技术步骤PLA(Programmable Logic Array)技术是一种可编程逻辑阵列技术,用于实现数字电路的设计与实现。

下面将介绍PLA技术的具体步骤。

1. 问题定义在使用PLA技术前,首先需要明确问题的定义。

这包括明确所需实现的功能、输入输出要求以及性能需求等。

只有明确了问题的定义,才能有针对性地进行后续的设计与实现。

2. 逻辑设计在PLA技术中,逻辑设计是一个关键步骤。

它包括对所需功能进行逻辑分析、逻辑方程的建立以及逻辑电路的设计等。

在逻辑设计过程中,需要使用逻辑门、触发器等基本逻辑元件,通过逻辑门的组合和触发器的时序控制来实现所需的功能。

3. PLA编程PLA编程是PLA技术的核心步骤之一。

在编程过程中,需要将逻辑设计中得到的逻辑方程转化为PLA的编程语言。

PLA的编程语言通常是一种类似于硬件描述语言的语言,可以通过编程语言对PLA进行配置和控制。

4. PLA配置PLA配置是将编程语言翻译为PLA硬件电路的过程。

在PLA配置过程中,需要根据编程语言的指令,对PLA内部的逻辑电路进行配置和连接。

这样,PLA才能按照预定的逻辑功能进行工作。

5. 逻辑验证在PLA配置完成后,需要进行逻辑验证。

逻辑验证是通过输入不同的测试数据,检查PLA输出是否符合预期结果的过程。

逻辑验证可以通过仿真软件进行,也可以通过实际硬件电路进行。

只有通过了逻辑验证,才能保证PLA的逻辑功能是正确的。

6. 性能评估在逻辑验证通过后,还需要对PLA的性能进行评估。

性能评估主要包括时序性能和功耗评估。

时序性能评估是检查PLA的最大工作频率,以确保PLA能够满足实际应用的要求。

功耗评估是评估PLA在工作过程中的功耗消耗,以便优化电路设计和减少功耗。

7. 优化设计根据性能评估的结果,可以对PLA的设计进行优化。

优化设计包括减小电路延迟、减少功耗消耗以及提高电路可靠性等方面。

通过优化设计,可以使PLA在实际应用中更好地发挥作用。

数字电路与系统东南大学信息科学与工程学院

第九章可编程逻辑器件

可编程逻辑器件的基本结构和电路表示方法 可编程逻辑阵列PLA

可编程阵列逻辑PAL

通用阵列逻辑GAL

复杂可编程逻辑器件CPLD

现场可编程门阵列FPGA

◆特点:与阵列和或阵列均可编程◆PLA的结构:

◆特点:或阵列固定,与阵列可编程

◆优点:工作速度高、成本低、使用灵活、可加密

9.3.1 基本的PAL电路——PAL16L8

◆与阵列有16个输入

◆其中10个来自输入引脚

◆另6个由输出端反馈而来

◆与阵列含64个与门

◆64个与项被分成8组,每一组中,7个与项供给一个或门

◆另一个与项用来控制输出---三态非门的使能。

◆使用PAL16L8实现4位二进制码奇校验位产生电路

◆奇校验位的逻辑表达式为:

9.3.2 带触发器输出的PAL电路——PAL16R8

PAL16R8的结构与PAL16L8类似,所不同的是该电路输出端有8个D触发器,每个触发器的D 输入端用一个或门激励。

8个触发器的时钟连在一起,用统一的时钟信号控制,每个触发器的反相输出端各通过一个缓冲器反馈到与阵列,因而可以用来实现同步时序逻辑电路

使用PAL16R8实现序列发生器的逻辑图

9.3可编程阵列逻辑PAL ◆设三个触发器输出分别为Q 1、Q 2和Q 3,可得3个触发器的激励方程分别

◆分析可知,该电路是个00010111序列发生器。

2016/10/12111

23131233

22

1Q Q Q Q Q Q Q D Q D Q D ++===。

fpga中pla名词解释

在FPGA(现场可编程门阵列)中,PLA(可编程逻辑阵列)是

一种重要的逻辑电路结构。

PLA由两个主要部分组成,AND阵列和

OR阵列。

AND阵列由可编程的输入和内部存储器组成,用于实现逻

辑功能的乘积项。

OR阵列由可编程的输出和输入连接组成,用于实

现逻辑功能的和项。

PLA的主要特点是其灵活性和可编程性,可以

根据特定的设计需求来配置逻辑功能。

在FPGA中,PLA通常用于实

现复杂的逻辑功能和算法,是FPGA实现灵活性和可编程性的关键组

成部分。

从另一个角度来看,PLA还可以被视为一种基于矩阵结构的逻

辑电路,其中输入和输出都是向量。

在FPGA中,PLA通常用于实现

逻辑功能和算法,通过配置其内部的逻辑单元和连接来实现不同的

逻辑功能。

PLA的可编程性使得它可以适应不同的应用需求,从简

单的逻辑运算到复杂的算法实现都可以通过PLA来完成。

总的来说,FPGA中的PLA是一种灵活、可编程的逻辑电路结构,通过配置其内部的逻辑单元和连接来实现不同的逻辑功能和算法。

它是FPGA实现灵活性和可编程性的重要组成部分,也是实现复杂逻

辑功能和算法的关键技术之一。

习题六6.1 可编程逻辑器件有哪些主要特点?PLD作为一种通用型可编程逻辑器件,而它的逻辑功能又是由用户通过对器件编程来自行设定的。

它可以把一个数字系统集成在一片PLD上,而不必由芯片制造厂商去设计和制作专用集成芯片。

采用PLD设计数字系统和中小规模相比具有如下特点:(1) 减小系统体积:单片PLD有很高的密度,可容纳中小规模集成电路的几片到十几片。

(低密度PLD小于700门/片,高密度PLD每片达数万门,最高达25万门)。

(2) 增强逻辑设计的灵活性:使用PLD器件设计的系统,可以不受标准系列器件在逻辑功能上的限制;用户可随时修改。

(3) 缩短设计周期:由于可完全由用户编程,用PLD设计一个系统所需时间比传统方式大为缩短;(4) 用PLD与或两级结构实现任何逻辑功能,比用中小规模器件所需的逻辑级数少。

这不仅简化了系统设计,而且减少了级间延迟,提高了系统的处理速度;(5) 由于PLD集成度高,测试与装配的量大大减少。

PLD可多次编程,这就使多次改变逻辑设计简单易行,从而有效地降低了成本;(6) 提高系统的可靠性:用PLD器件设计的系统减少了芯片数量和印制板面积,减少相互间的连线,增加了平均寿命, 提高抗干扰能力,从而增加了系统的可靠性;(7) 系统具有加密功能:多数PLD器件,如GAL或高密度可编程逻辑器件,本身具有加密功能。

设计者在设计时选中加密项,可编程逻辑器件就被加密。

器件的逻辑功能无法被读出,有效地防止电路被抄袭。

6.2 常见PLD器件有哪些主要类型?常见PLD器件根据可编程逻辑器件问世的时间,我们把PLA、PAL和GAL称为早期的可编程逻辑器件,把CPLD及FPGA称为近代的可编程逻辑器件。

也有人把它们分别称为低密度PLD和高密度PLD。

6.3 简述PAL和PLA在结构上的主要区别。

PAL是由可编程的与阵列、固定的或阵列和输出电路三部分组成。

有些PAL器件中,输出电路包含触发器和从触发器输出端到与阵列的反馈线,便于实现时序逻辑电路。