TMS320VC5410在语音信号中的应用

- 格式:docx

- 大小:223.59 KB

- 文档页数:16

TMS320VC5410在线并行自举的实现TMS320VC5410是公司(TI)2000年推出的一款性价比极高的16位定点数字信号处理器,其操作速率最高可达100。

他采纳先进的修正哈佛结构,片内有8条、CPU、在片存储器和在片外围等硬件,加上高度专业的命令系统,使其具有功耗小、高度并行等优点,可以满足电信等众多领域的实时处理要求,但是TMS320VC5410片上的只读存储器(ROM)只能采纳掩模编程的方式并且必需把代码交给厂家,成本较高,因此普通用户在用法时需要外部扩展程序存储器,E2PROM可以在线擦写,且掉电后数据不会走失,具有体积小、功耗低等特点,是作为TMS320VC5410外扩程序存储器的一种较好挑选。

通常状况下,要把CCS编译生成的COFF格式的文件通过Hex500转换成Hex格式的文件,并终于通过编程器把转换过的代码烧写进E2PROM(或FLASH等),本文提出了一种挺直在CCS环境下通过在线编程来完成片外存储器烧写,实现并行引导的新办法。

1 TMS320VC5410 DSP的自举原理DSP上电复位后从片外存储器读入程序的过程叫做自举(Bootloader)。

TMS320VC54XX DSP芯片内部设置有Bootloader程序,其主要作用是在系统上电复位后,将用户程序从外部存储器装载到DSP的内部随机存储器并运行程序,有多种Bootloader方式可将外部程序装入DSP中,这些方式包括串口方式,HPI方式,并行方式和W方式,此外DSP还支持8位或16位数据总线的外部存储器件及多块外部存储器件的Dootloader方式,上电复位后,如其MP/MC引脚为低电平,则TMS320VC5410进入Bootloader模式,从0xff80单元开头执行片内引导装载程序,进入引导程序后,如有INT2哀求中断,则进入HPI引导方式;如有INT3哀求中断,则进入串口引导模式;若没有中断哀求,系统进入并行引导模式,当进入并行引导模式后,TMS320VC5410首先在I/O空间Oxffff单元(若I/O为空则跳到数据存储器空间)读取一个地址,然而跳转到这一地址,按照地址单元的数据推断是16位并行第1页共3页。

收稿日期:2004-12-14基金项目:太原科技大学青年科技研究基金资助项目(200307)。

作者简介:乔建华(1975-),女,讲师,主要从事信号处理和计算机控制的研究。

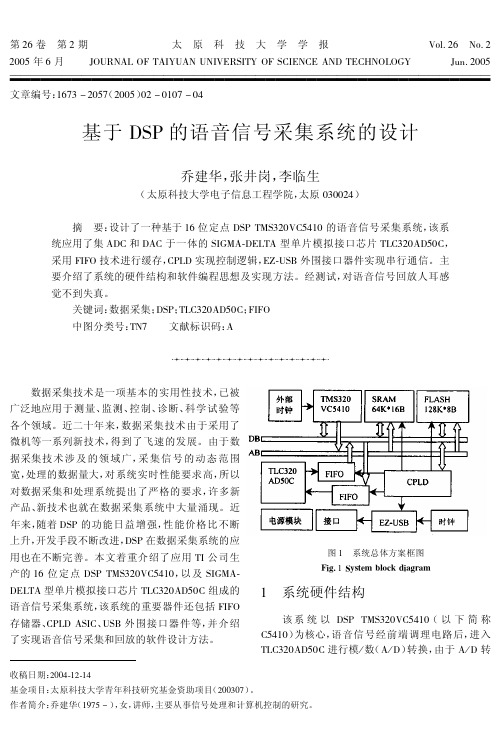

第26卷 第2期太原科技大学学报Vol.26 No.22005年6月JOURNAL OF TAIYUAN UNIVERSITY OF SCIENCE AND T ===============================================ECHNOLOGYJun.2005文章编号:1673-2057(2005)02-0107-04基于DSP 的语音信号采集系统的设计乔建华,张井岗,李临生(太原科技大学电子信息工程学院,太原030024)摘 要:设计了一种基于16位定点DSP TMS320VC5410的语音信号采集系统,该系统应用了集ADC 和DAC 于一体的SIGMA-DELTA 型单片模拟接口芯片TLC320AD50C ,采用FIFO 技术进行缓存,CPLD 实现控制逻辑,EZ-USB 外围接口器件实现串行通信。

主要介绍了系统的硬件结构和软件编程思想及实现方法。

经测试,对语音信号回放人耳感觉不到失真。

关键词:数据采集;DSP ;TLC320AD50C ;FIFO中图分类号:TN7 文献标识码:***************A 数据采集技术是一项基本的实用性技术,已被广泛地应用于测量、监测、控制、诊断、科学试验等各个领域。

近二十年来,数据采集技术由于采用了微机等一系列新技术,得到了飞速的发展。

由于数据采集技术涉及的领域广,采集信号的动态范围宽,处理的数据量大,对系统实时性能要求高,所以对数据采集和处理系统提出了严格的要求,许多新产品、新技术也就在数据采集系统中大量涌现。

近年来,随着DSP 的功能日益增强,性能价格比不断上升,开发手段不断改进,DSP 在数据采集系统的应用也在不断完善。

本文着重介绍了应用TI 公司生产的16位定点DSP TMS320VC5410,以及SIGMA-DELTA 型单片模拟接口芯片TLC320AD50C 组成的语音信号采集系统,该系统的重要器件还包括FIFO 存储器、CPLD ASIC 、USB 外围接口器件等,并介绍了实现语音信号采集和回放的软件设计方法。

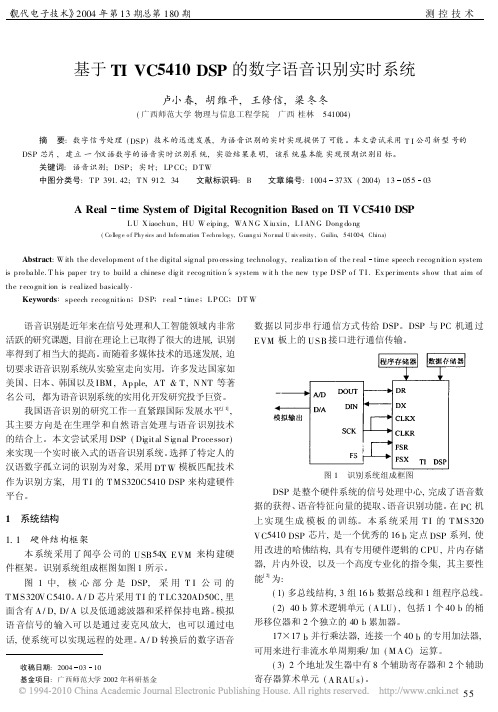

基于TI VC 5410DSP 的数字语音识别实时系统卢小春,胡维平,王修信,梁冬冬(广西师范大学物理与信息工程学院 广西桂林 541004)摘 要:数字信号处理(DSP )技术的迅速发展,为语音识别的实时实现提供了可能。

本文尝试采用T I 公司新型号的DSP 芯片,建立一个汉语数字的语音实时识别系统,实验结果表明,该系统基本能实现预期识别目标。

关键词:语音识别;DSP ;实时;LP CC;D T W中图分类号:T P 391.42;T N 912.34 文献标识码:B 文章编号:1004373X (2004)1305503A Real time System of Digital Recognition Based on TI VC5410DSPL U X iaochun,HU W eiping,WA N G X iuxin,L I AN G Dong do ng(Co l leg e o f Phy sics and Info rm ation T echno log y,Guang xi No rmal U niv ersity ,Guilin,541004,China)Abstract :W ith the development o f t he digital sig nal pro cessing technolog y,r ealiza tio n of the r eal time speech r ecog nitio n system is pro ba ble.T his paper tr y to build a chinese dig it r ecog nitio n ′s system w it h the new ty pe D SP o f T I.Ex per iments show that aim of the r eco gnit ion is r ealized basically .Keywords :speech r ecog nitio n ;D SP ;r eal time ;L P CC ;DT W收稿日期:20040310基金项目:广西师范大学2002年科研基金 语音识别是近年来在信号处理和人工智能领域内非常活跃的研究课题,目前在理论上已取得了很大的进展,识别率得到了相当大的提高。

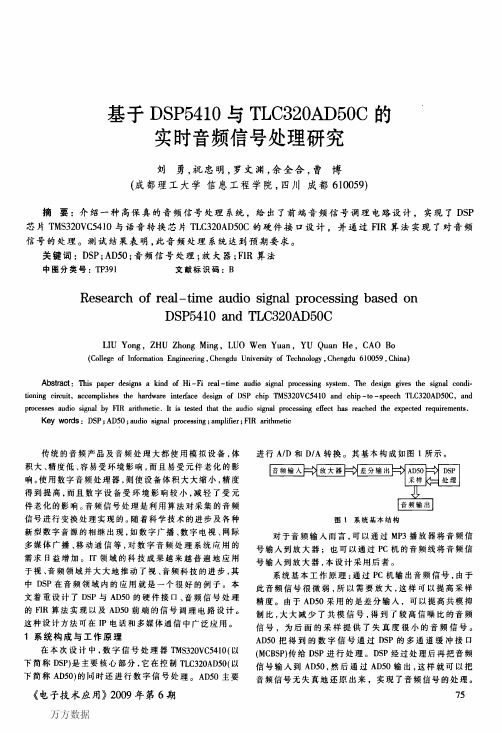

CLKOUTMCLKBDXDINBDRDOUTBFSXIFsBFSRBCLKRSCLKBCLI()(.j广M/S图5DSP与AD50的硬件接口兀R滤波器的差分方程为:Ⅳ一l’一,,(凡)=2。

啦茹(,l—f)(3)i=0对上式进行Z变换,整理后就得到传输函数为:酢)=器=委∥1(4)式(3)中:算(n)是输入序列;),(n)是输出序列;儡是滤波器的系数;Ⅳ是滤波器的阶数,其横向滤波结构图如图6所示。

Ⅳ+11图6nR滤波器结构图”1取音频信号的采样频率为10kHz,Ⅳ=64,利用MATLAB得到低通滤波器,其函数为:曰=兀R(,v,形)(5)式中:曰是滤波器的系数;Ⅳ是滤波器的阶数;形是滤波器的截止频率【2J。

由式(3)可知:不断地输入样本,经过延时一个单位,再和滤波器的系数进行乘法累加运算,最后得到输出序列,,(乃)。

程序流程图如图7所示。

在CCS5000开发平台下创建源文件。

本软件采用C语言和汇编语言混合编写,经过编译、调试,生成可执行文件奉.out。

最后把串.out文件下载到芯片运行,部分源代码如下:开始系统初始化,开中断初始化AD50等待中断读取DSP接收缓冲区进入滤波程序从发送缓冲区输出音频信号到AD50图7程序流程图《电子技术应用》2009年第6期S1LA,牛FlR.DATA—P+%;更新数据NOP:MVMDnR—DA’I’A-P,B2—pRPIZA.拍3MAC木兀R—DATJ5L.P十0%,奉nR—COFF-P+O%,A;滤波NOPNOPSrHA,枣(一sample)4实验结果在CCS5000开发平台下,为了便于分析,采用探针,把带纹波的方波信号作为信号输入,经过ccS仿真后输入信号与输出信号的时域和频域的对比结果如图8所示。

图8晋频信号处理前后的对比从以上处理的效果来看,方波信号由基波信号和高次谐波组成,由于采用了低通滤波器处理,高频信号(叠加在方波信号上面的纹波)得到有效抑制,低频信号得到保留(音频信号的带宽主要在低频),最后输出比较平滑的信号(主要是基波信号),由此证明了系统的低通性能,验证了此音频处理系统的正确性。

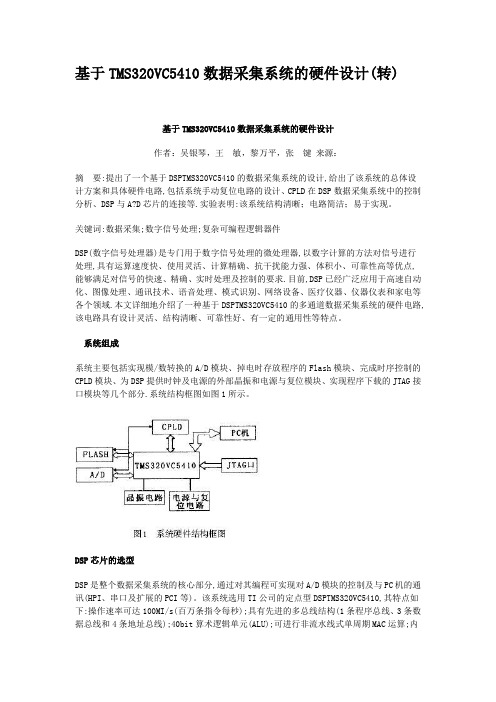

基于TMS320VC5410数据采集系统的硬件设计(转)基于TMS320VC5410数据采集系统的硬件设计作者:吴银琴,王敏,黎万平,张键来源:摘要:提出了一个基于DSPTMS320VC5410的数据采集系统的设计,给出了该系统的总体设计方案和具体硬件电路,包括系统手动复位电路的设计、CPLD在DSP数据采集系统中的控制分析、DSP与A?D芯片的连接等.实验表明:该系统结构清晰;电路简洁;易于实现。

关键词:数据采集;数字信号处理;复杂可编程逻辑器件DSP(数字信号处理器)是专门用于数字信号处理的微处理器,以数字计算的方法对信号进行处理,具有运算速度快、使用灵活、计算精确、抗干扰能力强、体积小、可靠性高等优点,能够满足对信号的快速、精确、实时处理及控制的要求.目前,DSP已经广泛应用于高速自动化、图像处理、通讯技术、语音处理、模式识别、网络设备、医疗仪器、仪器仪表和家电等各个领域.本文详细地介绍了一种基于DSPTMS320VC5410的多通道数据采集系统的硬件电路,该电路具有设计灵活、结构清晰、可靠性好、有一定的通用性等特点。

系统组成系统主要包括实现模/数转换的A/D模块、掉电时存放程序的Flash模块、完成时序控制的CPLD模块、为DSP提供时钟及电源的外部晶振和电源与复位模块、实现程序下载的JTAG接口模块等几个部分.系统结构框图如图1所示。

DSP芯片的选型DSP是整个数据采集系统的核心部分,通过对其编程可实现对A/D模块的控制及与PC机的通讯(HPI、串口及扩展的PCI等)。

该系统选用TI公司的定点型DSPTMS320VC5410,其特点如下:操作速率可达100MI/s(百万条指令每秒);具有先进的多总线结构(1条程序总线、3条数据总线和4条地址总线);40bit算术逻辑单元(ALU);可进行非流水线式单周期MAC运算;内置64KRAM、16KROM;带有软件可编程等待状态发生器、锁相环PLL时钟发生器;一个8位并行主机接口、3个多通道缓冲串行口等。

TMS320VC54x处理器McBSP接口的设计和实现以低速语音编解码系统为例,介绍了TMS320VC54x数字信号处理器的多通道缓冲串口的软硬件设计,给出了具体的设计思想和实现方法。

关键词:数字信号处理;语音编解码;接口;TMS320VC54x模数接口是数字信号处理(DSP)系统中一个重要的组成部分,其设计和实现直接影响到信号处理的质量,许多A/D、D/A转换芯片都采用并行的数字接口,与DSP接口时需要设计相应的译码电路。

TMS320VC54x系列芯片配备了多通道带缓冲能力的串行口(MultichannelBuffered SerialPort,McBSP),为设计模数接口提供了极大的便利。

McBSP具有双向的自动缓冲单元,缓冲单元有自己的循环寻址寄存器组,用来将串行口和C54x内部存储器之间数据传输的缓存。

同时McBSP的功能非常强大,除具有一般DSP串口功能之外,还可以支持T1/E1,ST-BUS,IOM2,SPI,HS等不同标准;为便于进行多通道的数字信号处理,McBSP最多支持128个通道;支持多种数据格式(8/12/16/20/24/32 b)的传输;可自动进行语音的μ律、A律压扩;其工作速率可达到1/2 CPU时钟速率。

这些特性为设计A/D,D/A接口电路提供了很大的灵活性。

下面具体以语音编解码器为例来说明McBSP的设计和实现。

1 语音编解码系统及McBSP接口的硬件设计低速率语音编解码器是一种能够将传统的模拟语音信号(带宽为0.3~3.4 kHz)实时压缩编码成1.2~9.6 kb/s数据比特流,而保持相当语音质量的语音编解码系统。

由于他大大压缩了传输数字语音所需的带宽,便于实现高保密度的语音通信,因此在语音的保密通信、多媒体通信和移动通信系统中应用十分广泛。

如图1所示,语音采样芯片TP3067和数字信号处理器TMS320VC5409组成了一个语音编解码系统。

在模拟端口一侧,模拟语音输入采用同相输入,经过话筒前置放大器(microphone preamplifier)放大后,从VFxI+管脚输入;模拟语音的输出也采用同相输出,经过两级放大后由VPO+输出,输出端可以驱动阻抗为600Ω的扬声器。

dsp语音处理系统设计论文+答辩PPT+英文文献翻译dsp语音处理系统设计论文+答辩PPT+英文文献翻译TMS320VC5410数字信号处理器,是本设计的核心。

TMS320VC5410硬件结构基本上可分为3大部分:(1)CPU。

包括算数逻辑单元,乘法器,累加器,移位寄存器,各种专门用途的寄存器,地址生成器以及内部总线;(2)存储器系统。

包括16~24位外接存储器接口,片内的程序ROM,片内单访问的数据RAM和双访问的数据RAM;(3)片内的外设与专用硬件电路。

包括片内的定时器,各种类型的串口,主机接口,片内的锁相环(PLL)时钟发生器以及各种控制电路。

TMS320VC5410的主要特性:(1)CPU部分。

先进的多总线结构,具有1条程序存储器总线,3条数据存储器总线和4条地址总线。

40位算数逻辑单元(ALU),包括40位的桶形移位寄存器和2个独立的40位的累加器。

并行加法器与一个40位的专用加法器结合在一起,用于非流水线的单周期乘/累加操作。

比较,选择和存储单元(CSSU),用于VITERBI操作中的加/比较选择。

指数编码器用于在单周期内计算40位累加器的指数值。

2个地址生成器,包括8个辅助寄存器和2个辅助寄存器单元。

(2)存储器系统。

具有16位192K字的可寻址空间:64K字程序空间,64K字数据和64K字的I/O空间,同时还具有多达256K字~8M字的扩展地址空间。

片内的存储器结构及容量,根据型号有所不同。

(3)在片外设和专用电路。

软件可编程等待状态寄存器。

可编程的存储器。

片内的锁相环(PLL)时钟发生器,可采用内部震荡器或外部的时钟源。

外部总线关断控制电路可用来断开外部数据总线,地址总线和控制信号。

数据总线具有数据保持特性。

可编程的定时器。

可与主机直接连接的8位并行主机接口(HPI),有的还包本文源自六维论文网括扩展的8位并行的主机接口(HPI8)和16位并行主机接口(HPI16)。

片内的串口根据型号不同可分为全双工的标准串口,支持8位和16位数据传送,时分多路(TDM)串口,缓冲串口(BSP)以及多通道缓冲串口(McBSP).设计中主要使用:64K/32K片上RAM,8M程序寻址空间,3个多通道自动缓冲串口(McBSP),6通道直接内存存储功能(DMA),8比特并行HPI接口。

论文题目摘要20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术(DSP)应运而生并得到迅速的发展。

数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理,以得到符合人们需要的信号形式。

自从20世纪80年代第一片SP芯片诞生至今,其性能得到了极大的提高应用,领域取得了不断的拓展。

目前己经成为通信、计算机、网络、工业控制以及家用电器等电子产品不可或缺的基础器件,尤其在通信领域,数字信号处理器以其能快速地实现各种数字信号处理算法的优点从而得到了广泛的应用。

随着超大规模集成电路技术(vLS)I的高速发展.DSP的性价比也在不断提高。

针对数字信号处理器以及其在通信系统中的应用特点,具体讨论了16片TMS320VC5410和CPLD相结合构成的一种语音信号处理硬件平台,同时就设计中要处理的各种复位和各种接口的具体实现方案给出了相应的原理框图关键词:DSP;TMS320VC5410;通信AbstractSince the 1960 s, with the rapid development of computer and information technology, digital signal processing technology arises at the historic moment and has a flourish development. Digital signal processing uses the computer or dedicated processing equipment, with the form of digital collection, after the transformation, filtering, valuation, enhancement, compression, the signals are analyzed, and finally can get this signal meeting people's needs. Since the 1980s, the first piece of SP is born, its performance has been greatly improved and chip applications achieved continuously expanding. It become an indispensable basic devices of the communication, computer, network, industrial control, and electrical products such as home appliances at present, especially in the field of communications, digital signal processor can quicklyrealize all kinds of digital signal processing algorithm, it has been widely used because of this advantage. With the development of integrated circuit technology (vLS) , DSP’s co mbination property has enhanced.For digital signal processor and its application characteristics in the communication system, there is a deep study on a speech signal processing hardware platform which is combining of 16 slices of TMS320VC5410 and CPLD constitute. To deal with the design of all kinds of reset and all kinds of the concrete implementation plan of the interface, this paper gives the corresponding principle block diagram at the same time.Keywords : DSP ;TMS320VC5410;communication前言DSP也称作数字信号处理器,是一种具有特殊结构的微处理器。

DSP芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器.广泛采用流水线操作.提供特殊的DSP指令,可以用来快速地实现各种数字信号处理算法。

DSP芯片已经在通信与电子系统、信号与信息处理、自动控制、留达军事、航空航天、医疗、家用电器在等许多领域得到广泛的应用。

而这种广泛的应用又成为促进DSP 芯片飞速发展的动力。

DSP芯片的分类有三种不同的方式。

按用途可分为通用型和专用型两大类。

通用型DSP芯片是一种软件可编程的DSP芯片,可适用于各种DSP应用。

专用型OSP芯片则将FFT、数字滤波和卷积等算法集成到DSP芯片内部.一般适用于某些专用的场合.便于提高信号处理的速度。

按照数据格式可分为定点和浮点度两种.它代表了DSP芯片工作的数据格式,值得注意的是,不同浮点DSP所采用的浮点格式也不完全一样.有的浮点DSP采用自定义的格式。

按照基础特性分类,则可分出静态DSP芯片和一致性DSP芯片两大类.如果在某时钟频率范围内的任何时钟频率上, DSP芯片都能正常工作,没有性能上的下降,这类DSP芯片一般称为静态DSP芯片:如果两种或互兼容则这类芯片称为一致性DSP芯片。

1.DSP系统特点以及设计过程数字信号处理系统以数字信号处理理论为基础,具有数字信号处理全部优点:●接口方便:D S P系统与其它以数字技术为基础的系统或设备都是相互兼的比模拟系统与这些系统接口要容易的多。

●编程方便:D S P系统中的可编程,DSP芯片可以使设计人员在开发过程中灵活方便的进行修改和升级,可以将C语言与汇编语言结合使用。

●具有高速性:DSP系统的运行较高,最新DSP芯片运行速度高达10GMIPS以上。

●稳定性好:D S P系统以数字处理为基础,受周围环境,如噪声、温度等的影响小、可靠性高;●精度高:例如16位数字系统可以达到的精度。

●可重复性好:模拟系统的性能受元件参数性能变化影响大,而数字系统基本不受影响,更便于测试、调试和大规模生产。

●集成方便:DSP系统中的数字部件有高度的规范性,便于大规模生一般来说,DSP的设计过程应遵循一定的设计流程,如图示:图1 DSP设计过程2.TMS320VC5410性能介绍TI公司DSP种类多,品种齐全,适合各种需要。

目前,使用较为广泛的主要有三个系列:C2000,C5000和C6000。

其他系列产品应用较少或已经淘汰。

每个系列又有多种DSP可供选择。

同一系列的DSP具有相同的内核、相同或兼容的汇编指令集;它们之间的差别是具有不同大小的片内存储器、不同的片内外设和外部接口等,工作电压和速度也有所区别。

以上3大系列DSP实现功能的侧重点不同,就是说应用领域有所不同:●C2000系列是16位定点DSP。

它是一个控制器系列,主要应用于工业控制领域,它除了具有一个DSP内核外,还有大量的片内外设资源,如A/D、定时器、各种同步和异步串口、看门狗、CAN总线接口等;加上其价格低廉,速度更高,可靠性更强,可以取代传统单片机。

内部具有Flash,方便固化程序,而其他系列DSP都没有内部Flash。

● C5000系列DSP是16位定点低功耗DSP,性价比极高,主要应用于无线通信系统及手持式通讯产品,如手机,PDA和GPS等。

C5000又分为C54X和C55X两个系列。

相对C2000系列来说,其内部存储更大,运行速度更快,更适合执行较为复杂的数字信号处理任务,但控制功能相对较弱。

一般由核心电压和I/O电压两种电压供电。

核心电压较低,所以功耗很低,且体积很小,方便集成。

●C6000系列是32位的DSP系列。

在TI的所有系列DSP中运行速度最快。

其中C62XX是定点DSP,而C64XX和C67XX是浮点DSP,它主要应用于需要大量快速运算的场合,如数字视频处理、无线基站等。

由于速度很高,所以功耗也很大。

在本设计中使用的DSP是TMS320VC5410。

它属于TI C5000系列中的C54X 系列,正如前面所说,同一系列的DSP具有相同的内核、相同或兼容的汇编指令集,差别仅在于内存储器的大小,片内外设等等,所以就首先介绍一下C54系列DSP普遍具有的特点和性能。

54X具有改进的哈佛结构,使其处理能力达到最大。

分开的程序空间和地址空间提供了高度的并行性,可以同时访问程序指令和数据,例如三次读操作和一次写操作可以在一个周期内完成。

带并行存储的指令和具有特殊应用的指令充分利用了这种结构。

这种并行性支持一套强大的算术运算、逻辑运算和位操作运算,所以使得这些运算可以在单个机周期内完成。

而且54X的运行机制还支持中断处理、重复操作和函数调用等等。

对于任意通用可编程芯片来说,一般都具备以下几个部分:●部存储器:主要用来存储程序、执行程序、存储数据等;●中央处理单元(CPU):用来实现各种运算功能;●片内外设:用来实现一些特定功能,如时钟发生器、硬件定时器等等;●外部总线接口:用来和其他芯片接口,协同工作;●通信接口:用来从外围芯片获得数据或者将处理完的数据传输出去;●内部总线:用来连接芯片中不同的单元,上各个部分的通信是通过内部总线来完成的3. TMS320VC5410在通信中的应用3.1芯片在通信中的应用目前,在通信系统中,为实现系统性能的最优化,在许多情况下利用数字信号处理器(DSP)来完成系统中的一部分重要功能,如第3代移动通信(3G)系统中所要求的回声消除、维特比译码、主叫号码识别等。

但就目前的一般情况而言,往往是单个DSP的处理能力有限且DSP的接口与其它器件的接口不能直接兼容,而整个系统需求的处理容量较大且要求接口灵活,因此,在一个通信系统中,多个DSP 之间及其与其它器件之间的接口的协调处理就显得尤为重要,而完成这样的工作主要是靠可编程逻辑器件来完成。

本文以TMS320VC5410(以下简称C5410)和复杂可编程逻辑器件(CPLD)的结合为例,简述它在一种通信语音信号处理系统中的硬件平台设计要点,同时就各种软接口的实现机理和复位的协调处理给出了原理框图。