PCM编解码芯片中低成本低功耗SAR ADC设计

- 格式:pdf

- 大小:4.03 MB

- 文档页数:87

基于新型电容阵列切换方式的10位低功耗SAR ADC孙甜甜【摘要】文中提出了一种10位低功耗逐次逼近(Successive-Approximation-Register,SAR)模/数转换器(Analog-to-Digital Converter,ADC),内部数/模转换网络采用一种新型的电容阵列开关切换方式,通过分段电容阵列、时序初始化和子参考电压来降低能耗,相比传统结构电容阵列的转换能耗减小了97.6%,单位电容数量减小了87%.整个ADC采用65 nm CMOS工艺进行设计,当采样频率为50 KS/s,输入正弦波信号频率为1.5 kHz左右时,ADC的有效位数(Effective Number of Bits,ENOB)为9.91位,总功耗低于450 nW,面积为136μm×176μm,非常适合植入式生物医疗电子的应用.%A 10-bit low power SAR (Successive-Approximation-Register, SAR) ADC (Analog-to-Digital Converter, ADC) is proposed in this paper. The internal digital-to-analog conversion is designed with an improved capacitive switching scheme. By using split-capacitor array, sequence initialization and sub-reference voltage, the switching energy is reduced by 97.6% and the number of the unit capacitor is reduced by 87%, compared with the traditional structure. The 10-bit ADC is designed based on a 65nm CMOS process. When 1.5 kHz fully-differential input signals are sampled at 50 KS/s sampling rate , the ENOB of the ADC is 9.91. The power consumption of this ADC is less than 450nW , and the area is 136μm × 176μm, making this proposed ADC very suitable to implantable bioelectronics.【期刊名称】《电子设计工程》【年(卷),期】2017(025)002【总页数】5页(P80-84)【关键词】模/数转换器;逐次逼近;新型电容开关切换技术;分段电容;低功耗【作者】孙甜甜【作者单位】西安邮电大学电子工程学院,陕西西安 710121【正文语种】中文【中图分类】TP302目前集成电路特征尺寸已经减小到纳米级,片上系统(System-on-Chip,SoC)的集成度也大幅提高。

基于CMOS工艺的低功耗SAR ADC设计基于CMOS工艺的低功耗SAR ADC设计摘要:随着物联网、5G通信等应用不断发展,对于低功耗高精度的模拟-数字转换器(ADC)需求也日益增加。

本文主要研究了基于CMOS工艺的低功耗逐次逼近型(SAR)ADC设计。

首先介绍了ADC的基本原理和工作模式,然后详细讲解了SAR ADC的原理及其与其他ADC的对比。

接着提出了低功耗的设计方法,包括降低比较器功耗、减小电容和最优控制电压等。

最后,以55nm CMOS工艺为例,设计了一个12位分辨率、采样率100kS/s的SAR ADC,并进行了仿真验证。

结果表明,该ADC的功耗仅为305nW,相较于传统的SAR ADC设计,具有显著的功耗优势。

因此,该设计方法可为减少ADC功耗提供一个重要的思路。

关键词:ADC;SAR ADC;CMOS工艺;低功耗;比较器;电容1. 引言模拟-数字转换器是一类重要的电路,主要用于将模拟信号转换为数字信号。

在现代电子技术应用中,模拟-数字转换器广泛应用于通信、控制、传感等领域。

其目的是将不同方法和源产生的不同物理变量转化为统一的数字信号,实现数字化处理和信息通信。

随着技术的发展,对于低功耗高精度的模拟-数字转换器(ADC)需求也越来越大。

低功耗的ADC不仅能延长电池寿命,还能减少热的产生,从而有利于系统可靠性和稳定性。

而逐次逼近型(SAR)ADC则是一种逐步逼近法的ADC,具有采样速度快、抗噪声能力强、结构简单等优点,因此成为了低功耗ADC设计的主流。

本文的主要研究内容是基于CMOS工艺的低功耗SAR ADC设计。

首先介绍了ADC的基本原理和工作模式,然后详细讲解了SAR ADC的原理及其与其他ADC的对比。

接着提出了低功耗的设计方法,包括降低比较器功耗、减小电容和最优控制电压等。

最后,以55nm CMOS工艺为例,设计了一个12位分辨率、采样率100kS/s的SAR ADC,并进行了仿真验证。

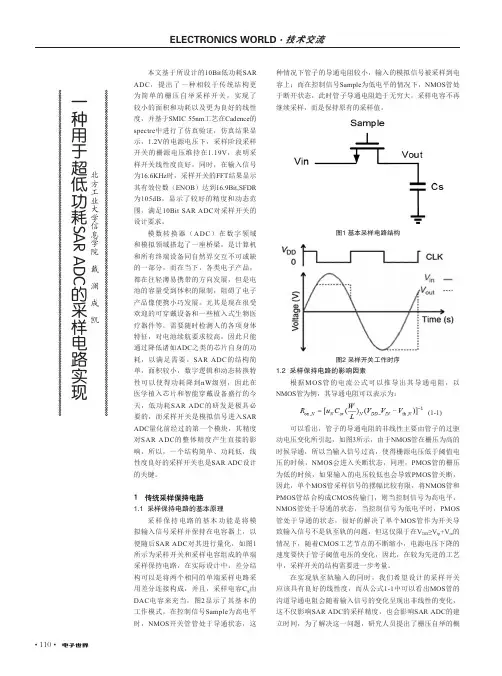

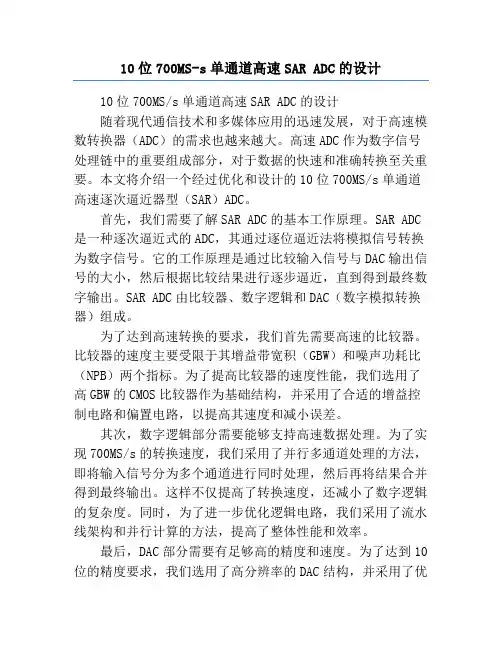

• 110•本文基于所设计的10Bit 低功耗SAR ADC ,提出了一种相较于传统结构更为简单的栅压自举采样开关,实现了较小的面积和功耗以及更为良好的线性度,并基于SMIC 55nm 工艺在Cadence 的spectre 中进行了仿真验证,仿真结果显示,1.2V 的电源电压下,采样阶段采样开关的栅源电压维持在1.19V ,表明采样开关线性度良好,同时,在输入信号为16.6KHz 时,采样开关的FFT 结果显示其有效位数(ENOB )达到16.9Bit,SFDR 为105dB ,显示了较好的精度和动态范围,满足10Bit SAR ADC 对采样开关的设计要求。

模数转换器(ADC )在数字领域和模拟领域搭起了一座桥梁,是计算机和所有终端设备同自然界交互不可或缺的一部分,而在当下,各类电子产品,都在往轻薄易携带的方向发展,但是电池的容量受到体积的限制,阻碍了电子产品像便携小巧发展。

尤其是现在很受欢迎的可穿戴设备和一些植入式生物医疗器件等,需要随时检测人的各项身体特征,对电池续航要求较高,因此只能通过降低诸如ADC 之类的芯片自身的功耗,以满足需要。

SAR ADC 的结构简单,面积较小,数字逻辑和动态转换特性可以使得功耗降到nW 级别,因此在医学植入芯片和智能穿戴设备盛行的今天,低功耗SAR ADC 的研发是极具必要的,而采样开关是模拟信号进入SAR ADC 量化前经过的第一个模块,其精度对SAR ADC 的整体精度产生直接的影响,所以,一个结构简单、功耗低,线性度良好的采样开关也是SAR ADC 设计的关键。

1 传统采样保持电路1.1 采样保持电路的基本原理采样保持电路的基本功能是将模拟输入信号采样并保持在电容器上,以便随后SAR ADC 对其进行量化,如图1所示为采样开关和采样电容组成的单端采样保持电路,在实际设计中,差分结构可以是将两个相同的单端采样电路采用差分连接构成,并且,采样电容C S 由DAC 电容来充当,图2显示了其基本的工作模式,在控制信号Sample 为高电平时,NMOS 开关管管处于导通状态,这种情况下管子的导通电阻较小,输入的模拟信号被采样到电容上;而在控制信号Sample 为低电平的情况下,NMOS 管处于断开状态,此时管子导通电阻趋于无穷大,采样电容不再继续采样,而是保持原有的采样值。

10位700MS-s单通道高速SAR ADC的设计10位700MS/s单通道高速SAR ADC的设计随着现代通信技术和多媒体应用的迅速发展,对于高速模数转换器(ADC)的需求也越来越大。

高速ADC作为数字信号处理链中的重要组成部分,对于数据的快速和准确转换至关重要。

本文将介绍一个经过优化和设计的10位700MS/s单通道高速逐次逼近器型(SAR)ADC。

首先,我们需要了解SAR ADC的基本工作原理。

SAR ADC 是一种逐次逼近式的ADC,其通过逐位逼近法将模拟信号转换为数字信号。

它的工作原理是通过比较输入信号与DAC输出信号的大小,然后根据比较结果进行逐步逼近,直到得到最终数字输出。

SAR ADC由比较器、数字逻辑和DAC(数字模拟转换器)组成。

为了达到高速转换的要求,我们首先需要高速的比较器。

比较器的速度主要受限于其增益带宽积(GBW)和噪声功耗比(NPB)两个指标。

为了提高比较器的速度性能,我们选用了高GBW的CMOS比较器作为基础结构,并采用了合适的增益控制电路和偏置电路,以提高其速度和减小误差。

其次,数字逻辑部分需要能够支持高速数据处理。

为了实现700MS/s的转换速度,我们采用了并行多通道处理的方法,即将输入信号分为多个通道进行同时处理,然后再将结果合并得到最终输出。

这样不仅提高了转换速度,还减小了数字逻辑的复杂度。

同时,为了进一步优化逻辑电路,我们采用了流水线架构和并行计算的方法,提高了整体性能和效率。

最后,DAC部分需要有足够高的精度和速度。

为了达到10位的精度要求,我们选用了高分辨率的DAC结构,并采用了优化的校准算法和电路设计,以提高传输精度和抗噪性能。

同时,为了减小DAC的开关功耗和电流波动对转换速度的影响,我们采用了低功耗的开关电路和合适的电源管理策略。

在硬件实现方面,我们将所有模块进行了综合布局和优化,以降低集成电路的面积和功耗,并提高整体性能。

为了进一步减小噪声和时序问题,我们采用了合适的线路布局和功率供给策略。

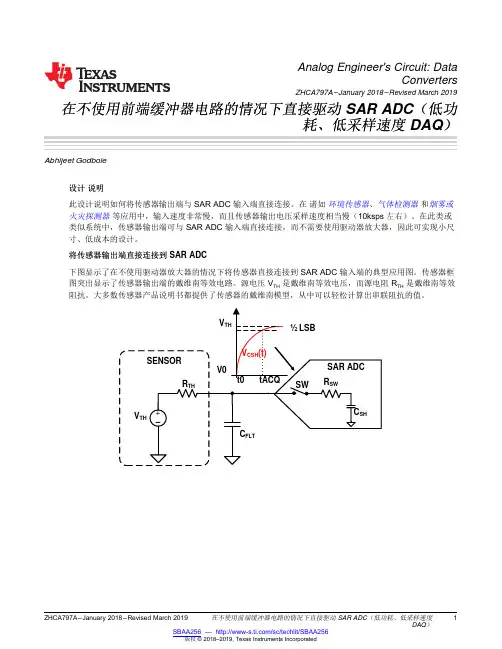

1ZHCA797A–January 2018–Revised March 2019在不使用前端缓冲器电路的情况下直接驱动SAR ADC (低功耗、低采样速度DAQ )Analog Engineer's Circuit:DataConvertersZHCA797A–January 2018–Revised March 2019在不使用前端缓冲器电路的情况下直接驱动SAR ADC (低功耗、低采样速度DAQ )Abhijeet Godbole设计说明此设计说明如何将传感器输出端与SAR ADC 输入端直接连接。

在诸如环境传感器、气体检测器和烟雾或火灾探测器等应用中,输入速度非常慢,而且传感器输出电压采样速度相当慢(10ksps 左右)。

在此类或类似系统中,传感器输出端可与SAR ADC 输入端直接连接,而不需要使用驱动器放大器,因此可实现小尺寸、低成本的设计。

将传感器输出端直接连接到SAR ADC下图显示了在不使用驱动器放大器的情况下将传感器直接连接到SAR ADC 输入端的典型应用图。

传感器框图突出显示了传感器输出端的戴维南等效电路。

源电压V TH 是戴维南等效电压,而源电阻R TH 是戴维南等效阻抗。

大多数传感器产品说明书都提供了传感器的戴维南模型,从中可以轻松计算出串联阻抗的值。

2ZHCA797A–January 2018–Revised March 2019在不使用前端缓冲器电路的情况下直接驱动SAR ADC (低功耗、低采样速度DAQ )规格参数计算值仿真值测得值瞬态ADC 输入趋稳误差<0.5LSB <100.5µV 36.24µV 不适用阶跃输入满量程 3.15V 3.15V 3.14978输入源阻抗(R TH )10k Ω10k Ω10.01k Ω滤波电容值(C FLT )680pF 680pF 不适用ADC 采样速度10ksps10ksps10ksps设计注意事项1.确定输入信号的源阻抗。

面对心率采集的SAR ADC的研究与设计摘要:设计并实现了一个用于植入式心电监测的1 1位低功耗逐次逼近型模数转换器(SAR ADC) o 针对低功耗的应用需求,提出了一种低功耗的电容阵列和开关策略,在保证比拟精度的根底上实现了更低的能量消耗。

关键词:逐次遥近型ADC 电容阵列开关策略面对心率采集的SAR ADC的研究与设计 (1)一、背景和意义背景和意义 (2)二、方案概述2. 1常见SAR ADC实现方式 (3)2.2 SAR ADC工作原理及结构 (4)电压定标型SAR ADC (5)电流定标型SAR ADC (6)电荷定标型SAR ADC (6)2.3 SAR ADC的电容阵列和开关策略 (7)2.3.1 Vcm-based 电容阵歹!] (7)2.3.2 TRI-LEVEL 电容阵列 (8)2.2.4 ENERGY BACK 电容阵歹!] (8)2.3.4 HYBRID 电容阵列 (8)2.3.5 SUB-MERGING DAC 电容阵列 (9)其它局部电路的低功耗设计 (9)彳找耗的电压比拟器 (9)彳W 耗的数字逻辑控制电路 ................................................ 10 存放器阵列 ............................................................... 11 带译码器的开关控制电路 (11)三、模型的搭建验证和功耗的计算验证3.1 SAR ADC 模型的搭建与验证 ............................................. 12 整体结构 ................................................................. 12 搭建过程 ................................................................. 12 子模块原理与作用 ......................................................... 13 仿真结果3.2.1 Vcm-based 电容阵列功耗计算 (18)3.2.2 TRI LEVEL 电容阵列功耗计算 (19)四、 工程完成情况工程完成情况 (20)五、 研究中的困难研究工作中的缺乏和困难 (21)六、 主要成绩和收获主要成绩和收获 (21)一、背景和意义15 低功耗SAR ADC 电容阵列功耗的计算17随着无线传感网技术的快速开展和人们生活水平的日益提高,人们的健康意识不断增强,越来越关注对自身健康状况方便而有效的监测。

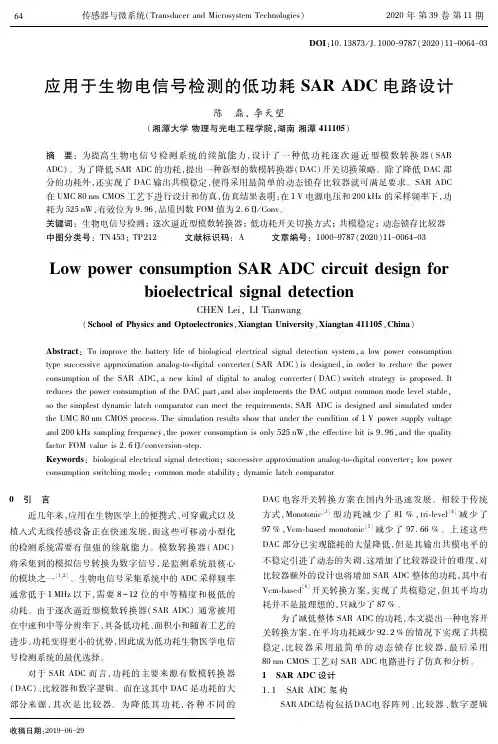

12位高精度低功耗SAR ADC设计李晓兴;杨丽娟;杨靖文【摘要】本文基于华润上华0.18um CMOS工艺,设计了一款200kS/s、12bit 高精度低功耗逐次逼近型模数转换器(Successive Approximation Register ADC,SAR ADC)。

本文采用线性度高的栅压自举开关提高精度;采用改进型分段电容结构,并提出非单调开关切换方案,减小了面积和功耗;采用动态比较器减小功耗;采用改进异步时序,减小关键路径延时。

前仿结果表明:在200kS/s采样速率下有效位数为11.1bit,信号噪声失真比为68.5dB,平均电流11.7uA。

%A 200kS/s, 12bit high precision low power SAR ADC is designed in this paper using CSMC 0.18um process. Bootstrapped switch with high linearity is adopted to improve the accuracy; Improved segmented capacitive structures and non-monotonic switching scheme are proposed in order to reduce the area and power consumption; Dynamic comparator is used to lower the static power consumption; Improved asynchronous timing can reduce the delay of the critical path. The simulation results show that: when sampling speed is 200kS/s, the effective number of bits is 11.1bit, signal to noise and distortion is 68.5dB and the average current is 11.7uA.【期刊名称】《电子世界》【年(卷),期】2016(000)024【总页数】3页(P15-16,18)【关键词】逐次逼近型模数转换器;改进分段电容结构;非单调开关切换;改进异步时序【作者】李晓兴;杨丽娟;杨靖文【作者单位】东南大学信息科学与工程学院;东南大学信息科学与工程学院;东南大学信息科学与工程学院【正文语种】中文逐次逼近型模数转换器(SAR ADC)以其低功耗、小面积、结构简单等优点被广泛应用于现代超大规模集成电路与片上系统中,此外,SAR ADC功耗随采样速率而改变,这对于低功耗应用或者不需要连续采集数据的应用非常有利[1],因而,开展高精度低功耗SAR ADC的研究与设计,对低功耗的系统设计和应用具有重要意义。

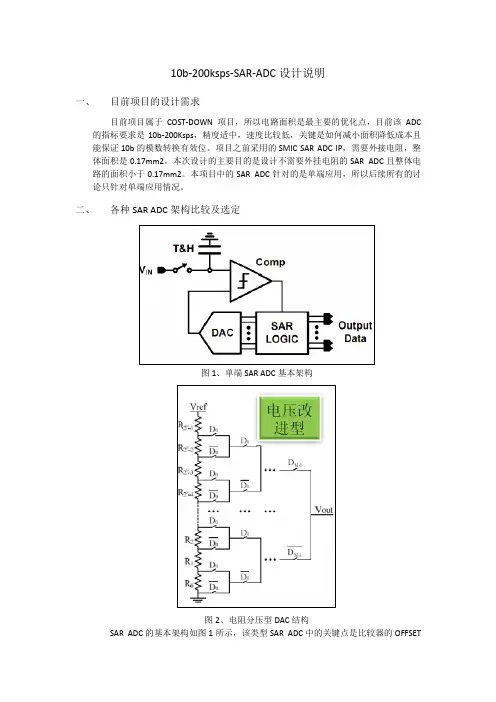

10b-200ksps-SAR-ADC设计说明一、目前项目的设计需求目前项目属于COST-DOWN项目,所以电路面积是最主要的优化点,目前该ADC 的指标要求是10b-200Ksps,精度适中,速度比较低,关键是如何减小面积降低成本且能保证10b的模数转换有效位。

项目之前采用的SMIC SAR ADC IP,需要外接电阻,整体面积是0.17mm2,本次设计的主要目的是设计不需要外挂电阻的SAR ADC且整体电路的面积小于0.17mm2。

本项目中的SAR ADC针对的是单端应用,所以后续所有的讨论只针对单端应用情况。

二、各种SAR ADC架构比较及选定图1、单端SAR ADC基本架构图2、电阻分压型DAC结构SAR ADC的基本架构如图1所示,该类型SAR ADC中的关键点是比较器的OFFSET和DAC的线性度。

比较器的失调对于所有类型的SAR ADC具有共性,最后统一说明。

1、针对不同的DAC架构分别说明其线性度、面积等优缺点。

✓电阻分压实现DAC的传统架构:如图2所示,该类型的由开关电阻阵列构成的电压按比例缩放D/A转换器,由于抽头电压不可能低于下面的抽头,因此保持了很好的单调性。

但是当D/A转换器的位分辨率提高时,开关数和电阻数均呈指数上升,面积难以接受。

而且,由于该DAC不能采样保持输入电压,因此信号输入端需要专门的采样保持电路用于维持ADC转换期间VIN 电压的相对固定,这进一步增加了面积。

此外,此类型的DAC转换精度依赖于电阻的匹配精度,在芯片内部,电阻的匹配精度低于电容的匹配精度。

综合以上因素,该类型的DAC只适合应用于转换位数较小的SAR ADC中。

图3、二进制电流型DAC结构✓二进制电流型DAC架构如图3所示,逐次逼近逻辑产生数字码控制电流源的开关,从而使得不同大小的电流与输入端产生的电流做减法运算,从而得到比较器的输出串行码。

该结构的DAC受限于电阻、MOS管的匹配程度,而且随着位数的增加电流镜结构也会导致比较大的功耗。

基于混合编码DAC的低功耗SAR ADC设计

杨明;赵毅强;夏璠

【期刊名称】《微电子学与计算机》

【年(卷),期】2013(30)7

【摘要】设计了一种基于混合编码DAC的低功耗SAR ADC.其分段电容DAC采用混合编码,减小了短时脉冲波形干扰的影响;为降低DAC寄生效应和电容阵列失配误差的影响,在DAC和比较器的版图设计中考虑了一些匹配技术.采用

GF(Global Foundry)0.35μm CMOS工艺流片验证,该ADC在500KSPS的速度下其INL在-0.6~0.4LSB区间范围内,DNL在-0.2~0.7LSB区间范围内,SNDR为54.13dB,有效位为8.7位.整个电路的功耗为537.9μW.

【总页数】4页(P91-94)

【关键词】逐次逼近模数转换器;混合编码;匹配技术;低功耗

【作者】杨明;赵毅强;夏璠

【作者单位】天津大学电子信息工程学院

【正文语种】中文

【中图分类】TN432

【相关文献】

1.一种应用于10MHz8位SAR ADC的分段式DAC电路设计 [J], 徐韦佳;田俊杰;李延标;许凤慧;

2.一种基于分段电容的低功耗SAR ADC设计 [J], 安胜彪;张琳;王保柱;王书海;杨

瑞霞

3.一种基于开关逻辑结构的低功耗SAR ADC的设计 [J], 赵毅强;耿俊峰;郑淑凤;高静

4.一种应用于10MHz8位SAR ADC的分段式DAC电路设计 [J], 徐韦佳;田俊杰;李延标;许凤慧

5.基于植入式眼压检测应用的低功耗SAR ADC设计 [J], 马志峰;李熙泽;张锋;陈铖颖

因版权原因,仅展示原文概要,查看原文内容请购买。

一种16位110 dB无杂散动态范围的低功耗SAR ADC 邢向龙;王倩;康成;彭姜灵;李清;俞军

【期刊名称】《电子科技大学学报》

【年(卷),期】2024(53)2

【摘要】该文设计了一款16位、转换速率为625 kS/s的逐次逼近寄存器型模数转换器(SAR ADC)。

改进的采样保持电路结构,优化了采样线性度和噪声性能。

采用分段结构设计电容型数模转换器并使用混合方式的电容切换方案,减小面积和能耗。

利用扰动注入技术提升ADC的线性度。

比较器采用两级积分型预放大器减小噪声,利用输出失调存储技术及优化的电路设计减小了比较器失调电压和失调校准引入的噪声,优化并提升了比较器速度。

芯片采用CMOS 0.18μm工艺设计和流片,ADC核心面积为1.15 mm^(2)。

测试结果表明,在1 kHz正弦信号输入下,ADC 差分输入峰峰值幅度达8.8 V,信纳比为85.9 dB,无杂散动态范围为110 dB,微分非线性为-0.27/+0.32 LSB,积分非线性为-0.58/+0.53 LSB,功耗为4.31 mW。

【总页数】9页(P185-193)

【作者】邢向龙;王倩;康成;彭姜灵;李清;俞军

【作者单位】复旦大学微电子学院;上海复旦微电子集团股份有限公司

【正文语种】中文

【中图分类】TN432

【相关文献】

1.一种12位84dB无杂散动态范围的高精度低功耗SAR ADC

2.16位、2.7Gsps DAC提供80dB无杂散动态范围

3.13位高无杂散动态范围的SAR ADC

4.基于量化噪声谱分析的ADC无杂散动态范围

因版权原因,仅展示原文概要,查看原文内容请购买。