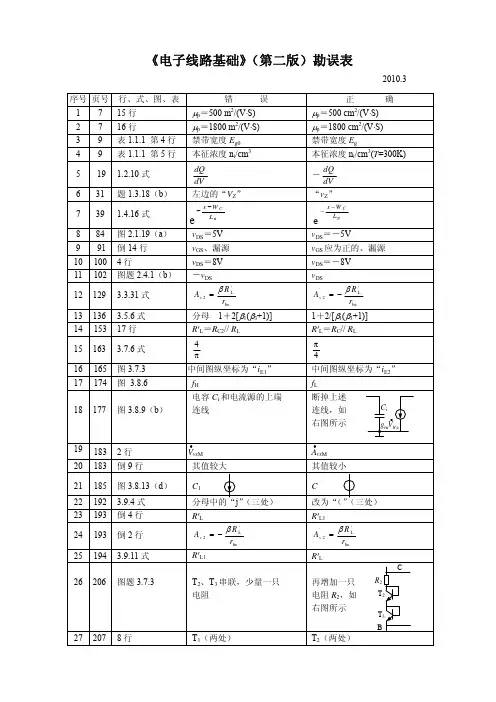

CMOS模拟集成电路设计(第二版)勘误

- 格式:pdf

- 大小:718.54 KB

- 文档页数:11

CMOS模拟集成电路设计第二版课程设计一、设计目标本次课程设计目标是:通过对CMOS模拟集成电路设计第二版中的一个电路设计实例进行仿真分析、电路优化及布局设计,深入理解和掌握CMOS模拟集成电路的基本原理及设计方法,培养学生分析和设计模拟集成电路的能力。

二、课程设计内容1.复习:基本模拟电路的分析和设计方法在进行CMOS模拟集成电路设计前,学生需要具备基本模拟电路的分析和设计方法。

本节将对常见的放大电路(比如共射放大电路,共基放大电路和共集放大电路等)的分析和设计方法进行复习。

2.CMOS反相器设计实例讲解本部分将讲解CMOS反相器的结构及原理,并通过具体的例子进行电路设计分析和仿真。

帮助学生了解CMOS反相器的设计方法、电路特性及其影响因素。

3.电路优化与参数选择在本部分,我们将重点介绍电路优化及参数选择的方法。

从电路的性能和稳定性等方面进行优化选择,并通过仿真结果来证明优化参数的效果。

4.布局设计与模拟验证本部分将介绍CMOS模拟集成电路的布局设计及模拟验证方法。

布局设计不仅可以影响电路的性能,也会影响电路的稳定性和可靠性。

通过模拟验证对电路进行分析验证。

三、设计评分方案本次课程设计采用滚动评分的方式,共计100分,具体评分如下:1.复习及设立问题:10分2.设计实例介绍及分析:20分3.参数选择及电路优化:30分4.布局设计及模拟验证:40分四、设计要求1.学生需要独立完成所有实验任务,不允许抄袭2.电路模拟软件使用HSPICE或者Spectre等,本节课程以HSPICE为例3.学生需要提交电路仿真截图、仿真结果以及电路设计原理图等作为实验报告。

五、总结通过本次课程设计的学习,学生可以深入了解CMOS模拟集成电路设计的基本原理及设计方法,并且培养分析和设计模拟集成电路的能力,为以后的研究或工作打下更好的基础。

同时,通过本次课程设计,学生能进一步加深对学过的知识的理解,增强把理论知识转化为实际工程应用的能力,提高实际应用能力和工程素质。

电子科大集成电路原理实验报告-CMOS模拟集成电路设计与仿真标准实验报告电子科技大学微电子与固体电子学院集成电路原理与设计CMOS模拟集成电路设计与仿真电子科技大学实验报告实验地点:211楼606 实验时间:2014.6.7一、实验室名称:微电子技术实验室二、实验项目名称:CMOS模拟集成电路设计与仿真三、实验学时:4四、实验原理参照实验指导书。

五、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

其目的在于:根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。

学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。

六、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、设计一个运算放大器电路,要求其增益大于40dB, 相位裕度大于60?,功耗小于10mW。

3、根据设计指标要求,选取、确定适合的电路结构,并进行计算分析。

4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析、建立时间小信号特性和压摆率大信号分析,能熟练掌握各种分析的参数设置方法。

5、电路性能的优化与器件参数调试,要求达到预定的技术指标。

6、整理仿真数据与曲线图表,撰写并提交实验报告。

七、实验仪器设备(1)工作站或微机终端一台(2)局域网2(3)EDA仿真软件 1套八、实验步骤1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握Cadence EDA仿真环境的调用。

2、根据设计指标要求,设计出如下图所示的电路结构。

并进行计算分析,确定其中各器件的参数。

3、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析,能熟练掌握各种分析的参数设置方法。

4、电路性能的优化与器件参数调试,要求达到预定的技术指标。

具体计算步骤如下:(参见模拟CMOS集成电路设计)1. 通过额定功耗和片外电容C计算偏置电路电流以及流进M6,M8电流,再通过相关试验得到相关pmos,nmos的Vth和k和λ,得到m6,m8,m9宽长比并计算密勒电容Cc2. 通过cmr计算m4和m0的宽长比3. 通过GB和Cc求出m2和m5宽长比4. 由m6,m8的Ids电流计算m7宽长比5. 进行电路仿真,观察电路是否符合各方面要求。

模拟CMOS集成电路设计第二版课程设计1. 课程设计目标本次课程设计旨在让学生们了解模拟CMOS集成电路设计的基本知识,并通过实践,掌握常用的CMOS电路设计方法。

具体目标如下:1.学习基本的CMOS工艺流程、器件模型和晶体管电路分析方法;2.掌握放大器电路和电压参考电路的设计方法;3.熟悉采样保持电路和模数转换电路的设计方法;4.能够运用所学知识完成一个小型模拟CMOS集成电路设计。

2. 课程设计大纲2.1 基本CMOS工艺流程和器件模型1.CMOS工艺流程简介;2.MOSFET器件的物理模型和参数;3.MOSFET直流分析和交流分析。

2.2 放大器电路设计1.放大器的基本概念和分类;2.差分放大器的设计和分析;3.单端放大器的设计和分析;4.放大器的频率响应分析。

2.3 电压参考电路设计1.电压参考电路的基本概念和分类;2.基准电压源的设计和分析;3.基准电流源的设计和分析。

2.4 采样保持电路和模数转换电路设计1.采样保持电路的基本概念和设计方法;2.SAR ADC的工作原理和设计方法;3.ΔΣ ADC的工作原理和设计方法。

2.5 完整电路设计参照上述的内容,学生根据老师提供的设计要求,完成一个包括放大器、电压参考电路、采样保持电路和模数转换电路的小型模拟CMOS集成电路设计。

3. 课程设计方法本次课程设计采用以下方法:1.理论授课:老师讲解基本理论知识,介绍电路设计方法和常用工具;2.实验练习:学生通过使用模拟电路仿真软件(如Cadence)进行实验练习,掌握具体的设计方法;3.团队合作:建议学生分组完成设计任务,通过合作提高设计效率、解决实际问题;4.报告展示:学生需要撰写设计报告,结合仿真结果和实验数据,说明设计思路、方法和结果。

4. 课程设计评估本次课程设计采用以下评估方法:1.思考题:课程结束后,由老师出一份思考题,学生需要结合实验内容和理论知识进行分析和解答;2.作业:学生需要完成相关课程作业,包括理论、仿真和实验;3.报告:学生需要撰写设计报告,内容包括设计思路、仿真结果、实验数据和总结。

cmos模拟集成电路设计-实验报告————————————————————————————————作者:————————————————————————————————日期:北京邮电大学实验报告实验题目:cmos模拟集成电路实验姓名:何明枢班级:2013211207班内序号:19学号:2013211007指导老师:韩可日期:2016 年 1 月16 日星期六目录实验一:共源级放大器性能分析 (1)一、实验目的 (1)二、实验内容 (1)三、实验结果 (1)四、实验结果分析 (3)实验二:差分放大器设计 (4)一、实验目的 (4)二、实验要求 (4)三、实验原理 (4)四、实验结果 (5)五、思考题 (6)实验三:电流源负载差分放大器设计 (7)一、实验目的 (7)二、实验内容 (7)三、差分放大器的设计方法 (7)四、实验原理 (7)五、实验结果 (9)六、实验分析 (10)实验五:共源共栅电流镜设计 (11)一、实验目的 (11)二、实验题目及要求 (11)三、实验内容 (11)四、实验原理 (11)五、实验结果 (15)六、电路工作状态分析 (15)实验六:两级运算放大器设计 (17)一、实验目的 (17)二、实验要求 (17)三、实验内容 (17)四、实验原理 (22)五、实验结果 (23)六、思考题 (24)七、实验结果分析 (25)实验总结与体会 (26)一、实验中遇到的的问题 (26)二、实验体会 (26)三、对课程的一些建议 (27)实验一:共源级放大器性能分析一、实验目的1、掌握synopsys软件启动和电路原理图(schematic)设计输入方法;2、掌握使用synopsys电路仿真软件custom designer对原理图进行电路特性仿真;3、输入共源级放大器电路并对其进行DC、AC分析,绘制曲线;4、深入理解共源级放大器的工作原理以及mos管参数的改变对放大器性能的影响二、实验内容1、启动synopsys,建立库及Cellview文件。

CMOS集成电路设计基础第二版课程设计概述CMOS集成电路设计基础是半导体工程的重要内容之一,它是电子工程师必须要掌握的技能。

本次课程设计旨在通过实践,让学生更好地了解CMOS集成电路设计的基本理论和方法,并且能够灵活地应用到实际项目中。

设计任务本次课程设计的任务是设计一个基础的CMOS集成电路。

设计要求如下:•根据给定的电路功能需求,设计出电路的逻辑图和布图;•确定所需器件的参数,并进行器件选择;•进行器件级仿真,验证电路性能;•绘制电路的波形图,并对电路性能进行评估;•撰写电路设计报告,详细阐述电路设计思路、仿真结果以及评估结论。

设计流程1. 电路功能需求分析首先,我们需要明确电路的功能需求,该层面主要用于预备设计过程,确定电路表现和性能的要求,例如:•输入电压范围•输出电压范围•电路增益•电路带宽•输出电流2. 电路逻辑图设计电路的逻辑设计阶段,需要根据上一步的功能需求分析确定电路的工作模式,并建立电路的逻辑图。

3. 器件参数确定与器件选择电路的器件参数确定,主要是指确定每个单元电路的器件长度和宽度,在确保满足电路性能需求的基础上进行器件选择。

在本步骤中,可使用器件参数提取工具等辅助工具进行参数验证和器件选型。

4. 器件级仿真经过前三个阶段,我们已经得到了电路的逻辑图和器件选择信息,接下来就可以对电路进行器件级仿真,进行电路性能评估,这将有助于确定器件参数的最终值并进行电路优化。

5. 波形图绘制与性能评估在完成器件级仿真后,我们可以根据仿真结果对电路的性能进行评估,并绘制出电路的波形图,以便进行更详细的分析和评估。

6. 设计报告撰写最后,我们需要将整个设计过程进行总结,并将电路设计思路、仿真结果和评估结论等内容进行详细撰写,以便为后续的电路设计和实际项目工作提供参考。

总结本篇文章简单介绍了CMOS集成电路设计基础的课程设计内容和设计流程,通过实践完成本次课程设计,不仅可以提升学生的基础理论知识,也能够为学生今后从事电路设计和项目实践提供很大的帮助。

实验二CMOS模拟集成电路设计与仿真实验二 CMOS 模拟集成电路设计与仿真CMOS(Complementary Metal-Oxide-Semiconductor)模拟集成电路(Analog Integrated Circuits)是一种基于金属-氧化物-半导体结构的集成电路技术。

在本实验中,我们将学习并实践CMOS模拟集成电路的设计和仿真,以加深对其原理和应用的理解。

通过此实验,我们将能够熟练掌握CMOS模拟集成电路设计与仿真的基本流程与方法。

一、实验目的本实验旨在通过设计和仿真CMOS模拟集成电路,加深对其工作原理的理解,掌握电路设计与仿真的基本方法。

二、实验原理CMOS模拟集成电路是一种基于n型和p型MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)的电路。

通过调节不同MOS管的工作状态,可以实现不同的电路功能。

其中,n型MOS管的主要特点是电导率高,适用于放大增益较大的部分;p型MOS管的主要特点是电导率低,适用于控制电流流动的部分。

三、实验步骤1. 电路设计:根据实际需求,确定设计所需的CMOS模拟集成电路。

在设计前,应先详细了解电路的功能、性能及工作原理,确定所需的器件数目和性能参数。

2. 电路布局:根据设计要求,将设计的各个电路模块在模拟集成电路上进行布局,合理安排电路的位置和空间,以保证电路的稳定性和性能。

3. 电路连接:按照布局图,将所需的电路模块进行连接,确保各个模块之间信号的正确传输和电路功能的正常实现。

4. 电路仿真:使用专业的仿真软件,将设计好的CMOS模拟集成电路进行仿真,验证其电路性能和功能。

在仿真过程中,应注意选择合适的仿真参数和验证方法,以保证仿真结果的准确性和可靠性。

5. 仿真分析:根据仿真结果,对电路的性能和功能进行分析和评估。

如果发现问题或改进的空间,可以根据分析结果进行相应的调整和优化。

6. 总结与展望:根据实验结果和分析,总结实验过程中的经验和教训,提出可能的改进和未来的研究方向。

CMOS Analog Integrated Circuit Design - CourseProject for 2nd Edition (EN)IntroductionCMOS analog integrated circuit design is an important andchallenging topic in modern electronics. With the advancement of integrated circuit technology, the design of analog circuits is becoming increasingly complex and demanding. This course project ms to provide students with hands-on experience in designing, simulating, and optimizing CMOS analog circuits.In this project, students will work on the design of a two-stage operational amplifier (OpAmp), which is a basic building block in many analog circuits. The design process will include the following steps:1.Specification: Defining the requirements for the OpAmp interms of gn, bandwidth, power dissipation, and other key metrics.2.Schematic design: Creating a schematic diagram of the OpAmpusing standard CMOS building blocks such as current mirrors,differential prs, and active loads.3.Simulation: Using software tools such as SPICE to simulatethe performance of the OpAmp under different operating conditions.yout: Translating the schematic diagram into a physicallayout that can be fabricated on a CMOS process.5.Parasitic extraction: Extracting the parasitic effects ofthe layout, such as capacitance and resistance, and incorporating them into the simulation model.6.Optimization: Tweaking the design parameters to optimize theperformance of the OpAmp according to the specified metrics.The project will be conducted using the Cadence Virtuoso software suite, which is widely used in industry for analog circuit design.Learning ObjectivesBy completing this course project, students should be able to: •Understand the basic principles of CMOS analog circuit design•Create a schematic diagram of a two-stage OpAmp using standard CMOS building blocks•Simulate the performance of the OpAmp and analyze the results•Translate the schematic diagram into a physical layout•Extract parasitic effects from the layout and incorporate them into the simulation model•Optimize the design parameters to achieve desired performance metricsProject DeliverablesThe following deliverables are expected from each team of students:1.A project report in IEEE conference paper format, including:–Abstract: A brief summary of the project objectives, methods, and results.–Introduction: A background on the topic and themotivation for the project.–Design methodology: A description of the design process and tools used.–Results and analysis: A presentation of the simulation results and an analysis of the performance metrics.–Conclusion: A summary of the mn findings and future work.–References: A list of relevant sources cited in the report.2.A presentation of the project, including:–Overview of the project objectives and methods.–Discussion of the design process and challenges faced.–Demonstration of the simulation results andoptimization process.–Summary of the performance metrics achieved.3.Design files and simulation data for verification purposes. Evaluation CriteriaThe project will be evaluated based on the following criteria:pliance with the project specifications and requirements.2.Clarity and completeness of the project report andpresentation.3.Quality of the design methodology and simulation results, asdemonstrated in the report and presentation.4.Optimization of the design parameters to achieve desiredperformance metrics.5.Creativity and originality in the design approach andoptimization process.ConclusionThrough this course project, students will gn valuable experience in CMOS analog circuit design and learn how to use industry-standard tools for design, simulation, and optimization. The project will challenge students to think creatively and critically about design challenges, and to work collaboratively to achieve their goals. Ultimately, the project will prepare students for a career in the rapidly evolving field of analog circuit design.。

CMOS模拟集成电路设计与仿真实验指导书模拟集成电路原理实验指导书二零一二年五月实验1 集成电路版图识别与提取一、实验目的随着IT产业的迅速发展,集成电路在国民经济和国防建设中的地位日益突出。

IC设计技术尤显重要。

版图识别与提取是微电子IC逆向设计的关键技术。

一方面可借鉴并消化吸收先进、富有创意的版图设计思想、结构。

建立自己的版图库;另一方面通过分析、优化已有版图可将原有芯片的性能加以改进提高。

本实验是基于微电子技术应用背景和《模拟集成集成电路》课程设置及其特点而设置,目的在于:1增加对塑封、陶瓷封装等不同封装形式的感性认识;2 增加对硅圆片、芯片的感性认识;3 学习并掌握集成电路版图的图形识别、电路拓扑结构提取。

4能对提取得到的电路进行功能分析、确定,并可运用EDA软件展开模拟仿真。

二、实验原理本实验重点放在版图识别、电路拓扑提取、版图编辑三大模块,实验流程如下:三、实验内容1.观察典型集成电路的封装形式;2.观察集成电路成品剖片的电路结构;3.观察硅圆片与未封装的芯片;4.在芯片上找出划片槽、测试单管、分布在芯片边缘的压焊点、对位标记,并测出有关图形的尺寸和间距。

仔细观察芯片图形的总体布局,找出电源线、地线、输入端、输出端以及相应的压焊点;6.判断集成电路的工艺类别;7.根据以上判断、提取芯片上图形所示电路图的拓扑结构;复查、修正,并进行仿真验证。

四、实验步骤1.观察典型集成电路的封装形式;2.对集成电路成品剖片的电路结构进行观察;3.观察测试单管。

仔细观察芯片的布局布线,找出电源线和地线。

4.确定芯片工艺类别,分清单个的元件结构,提取版图电路拓扑结构五、实验报告1.版图识别与提取过程总结2.绘出所提版图的电路拓扑结构六、附:版图照片(含铝线照片):金属1层去铝线照片衬底层课下思考练习: 金属1层去铝线照片衬底层实验2CMOS模拟集成电路设计与仿真一、实验目的与意义随着IT产业的迅猛发展,微电子集成电路在通讯、计算机及其他消费类电子产品中的重要地位日益突出,而IC的生产和设计技术水平是决定IC芯片性能的两大要素。

CMOS模拟集成电路设计第二版教学设计一、教学目的和要求1.1 教学目的本教学设计主要旨在培养学生对于CMOS模拟集成电路的整体设计能力,包括CMOS工艺的基本概念、CMOS模拟电路设计的方法与实现技术,能够对模拟电路进行整体设计,并掌握模拟电路的相关测试技术。

同时也能够了解到目前国内外的最新研究进展和应用领域。

1.2 教学要求学生通过本教学可以了解到模拟电路的基本概念,了解 CMOS工艺的基本演化及其现状,能够深入了解CMOS模拟电路设计的方法与实现技术,包括模拟电路的基本原理,以及模拟电路设计的流程、优化和测试等方面。

同时学生还需要通过实践演练提高自己的综合实际应用解决问题的能力。

二、教学内容2.1 基础教学内容1.CMOS工艺基础2.CMOS模拟电路设计的基本概念3.基本模块设计,如:输入级、放大器、滤波器、振荡器等模块的设计方法4.傅里叶变换和快速傅里叶变换5.相关电路测试技术2.2 拓展教学内容1.建立不确定度计算模型以及进行不确定度分析2.阻止频率的设计和测试3.电源干扰、瞬变和共模干扰等干扰分析4.第一性原理仿真方法5.高性能模拟集成电路在线测试方法三、教学方法3.1 理论课教师会针对每一章节的知识点分别进行详细的讲解和解析,着重强调理论基础及设计实践中的注意点和实际问题。

通过课堂的互动和答疑等形式,帮助学生成长。

3.2 实践课在实践教学环节中,学生将直接使用计算机进行模拟电路设计实践。

在实践后,学生将根据所设计的实验进行分析和评估,将分析和评估结果进行撰写报告。

四、教学评价4.1 课程考核方式1.期中考试:占总成绩30%。

2.实验:占总成绩30%。

3.期末考试:占总成绩40%。

4.2 评价标准1.学生是否掌握了模拟电路的基本概念、设计方法和测试技术。

2.学生是否对于CMOS模拟电路的设计流程、优化和测试等方面有着清晰的认识和实际应用能力。

3.学生是否按照设计流程步骤进行了实际操作和技能的掌握程度。

模拟CMOS集成电路设计课程设计报告--------二级运算放大器的设计信息科学技术学院电子与科学技术系一、概述:运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT 或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二、设计任务:设计一个二级运算放大器,使其满足下列设计指标:工艺Smic40nm电源电压 1.1v负载100fF电容增益20dB 至少40dB3dB带宽20MHz输入小信号幅度5uV 共模电平自己选取输出共模电平自己选取电路结构两级放大器相位裕度60~70度功耗无要求三、电路分析:1.电路结构:最基本的二级运算放大器如下图所示,主要包括四部分:第一级放大电路、第二级放大电路、偏置电路和相位补偿电路。

2.电路描述:输入级放大电路由PM2、PM0、PM1和NM0、NM1组成。

PM0和PM1构成差分输入对,使用差分对可以有效地抑制共模信号干扰;NM0和NM1构成电流镜作为有源负载;PM2作为恒流源为放大器第一级提供恒定的偏置电流。

第二级放大电路由NM2和PM3构成。

NM2为共源放大器;PM3为恒流源作负载。

相位补偿电路由电阻R0和电容C0构成,跨接在第二级输入输出之间,构成RC米勒补偿。

此外从电流电压转换角度来看,PM0和PM1为第一级差分跨导级,将差分输入电压转换为差分电流。

NM0和NM1为第一级负载,将差模电流恢复为差模电压。

NM2为第二级跨导级,将差分电压信号转换为电流,而PM3再次将电流信号转换成电压信号输出。

偏置电压由V0和V2给出。

3.静态特性对第一级放大电路:构成差分对的PM0和PM1完全对称,故有G m1=g mp0=g mp1 (1)第一级输出电阻R out1=r op1||r on1 (2)则第一级电压增益A1=G m1Rout1=g mp0,1(r op1||r on1) (3) 对第二级放大电路:电压增益A2=G m2R out2= -g mn2(r on2||r op3) (4) 故总的直流开环电压增益A0=A1A2= -g mp0,1g mn2(r op1||r on1)(r on2||r op3) (5)由于所有的管子都工作在饱和区,所以对于gm 我们可以用公式 g m =D I L W )/(Cox 2μ (6) 进行计算;而电阻r o 可由下式计算 r o =DI 1λ (7)其中λ为沟道长度调制系数且λ∝1/L 。

模拟CMOS集成电路设计实验报告反相器原理图设计学院机械与电子工程学院班级学号姓名指导老师报告时间 2015.6.2一、实验目的1.学会创建模型库和单元视图2.了解schematic 设计环境3.学会如何画反相器原理图二、实验内容和步骤1 调用candence 软件运行虚拟机直接点击三角形运行的图标然后输入icfb命令调用candence软件,此时会弹出CIW 窗口2 创建工作路径库与单元视图进入candence 后点击CIW 窗口的file—new—library,此时弹出对话窗口如下图,Name栏输入库文件名myfxq,右侧Technology File栏选择第二个。

点击OK 弹出如下窗口,这时让你选择工艺库的我们选择sto2 这个工艺库点击OK 弹出窗口中在library中可以看到我们自己建的模型库myfxq。

选中自己建好的模型库然后点击上面的File—cellview 弹出如下图窗口library name 栏不用改,cell name 栏可以自定义toll栏选择第一个则view name 栏自动为schematic。

点击OK 就弹出Schematic Editing 窗口到此单元视图也建好了。

3 画原理图⑴画原理图之前先了解以下几个快捷键:i----插入元器件w----连线p----插入输入输出引脚q----查看器件属性f----调节合适的窗口c----复制u----撤销m----移动器件del----删除⑵添加元件n管p管的添加在Schematic Editing 窗口中按下快捷键i 弹出窗口如下图点击Browse弹出Library Browse进行p管添加,再对p 管属性设置的窗口如下图,这里Total Width 设为1.4uM其它不变。

点击Hide此时鼠标箭头上就有了p管的symbol,n管的插入和p管类似,把n管的Length 改为550nm,total width为700nm。

目录第一部分.前言第二部分.实验的基础知识第三部分.实验内容1.cadence virtuoso schematic进行电路图的绘制2.cadence virtuoso analog environment电路性能模拟3.cadence virtuoso layout editor进行版图设计4.cadence virtuoso DRC Extract LVS以及后仿真等。

第四部分.附件1.Cadence schematic simple tutorial2.cadence virtuoso layout editor tutorial3.SMIC0.18um library第一部分.前言本实验为微电子系专业选修课程《模拟CMOS集成电路设计》的配套实验。

本实验围绕如何实现一个给定性能参数要求的简单差分运算放大器而展开。

通过该实验,使得学生能够建立模拟集成电路设计的基本概念,了解设计的基本方法,熟悉模拟CMOS集成电路设计的典型流程,了解在每一个流程中所应用的EDA工具,并能较熟练地使用每个流程对应的设计工具。

通过让学生自己分析每个流程中所出现的问题,把课程所学知识联系实际,从而增强学生分析问题、解决问题的能力。

本实验的内容以教材一至十章内容为基础,因此,该实验适合在开课学期的后半部分时间开展。

本实验讲义内容安排如下,首先是前言,其次是基础知识,接下来是实际实验内容,具体分成四个过程,最后是附录。

建议在实际实验开始之前依次浏览三个附件文档。

第二部分.实验的基础知识该实验内容所涉及的基础知识包括两部分:电路方面、流程方面和EDA设计工具使用方面。

1.电路有关的基础知识。

该实验是围绕如何实现基于SMIC0.18um工艺下,一个给定性能参数要求的简单差分运算放大器而展开,因此,以电流镜做负载的基本五管差分运算放大器的性能分析是该实验的理论基础。

具体内容在讲义以及课件相关章节中有详细介绍。

以下用一张图简单重述该电路的有关性能与各元件参数之间的关系分析结论。

模拟CMOS集成电路设计引言在现代电子设备中,集成电路无处不在。

其中,CMOS (Complimentary Metal-Oxide-Semiconductor,互补金属氧化物半导体)是一种常用的集成电路技术。

CMOS集成电路设计是指设计和优化各种模拟电路、数字电路和混合信号电路的过程,以满足特定的应用需求。

在本文档中,我们将介绍模拟CMOS集成电路设计的基本原理、步骤以及常见的设计技巧。

我们将从设计规范的制定开始,一直到电路验证和验证。

通过阅读本文档,读者将了解到在设计模拟CMOS集成电路时应该考虑的各种因素,并具备一定的设计能力。

设计规范在开始模拟CMOS集成电路设计前,制定明确的设计规范非常重要。

设计规范应该包括以下内容:1.电路功能:描述电路的功能和期望的输入输出特性。

2.电路性能:定义电路的性能指标,如增益、带宽、噪声等。

3.技术限制:确定电路设计的技术限制,如制造工艺和电路元件的规格。

4.耗电量:设定电路的功耗要求,包括静态功耗和动态功耗。

5.成本:估计电路设计的成本,包括制造成本和开发成本。

电路拓扑设计电路拓扑设计是指设计模拟CMOS集成电路的基本结构和连接方式,以实现所需的功能。

在设计电路拓扑时,应该考虑以下要点:1.输入输出特性:根据设计规范确定输入输出特性的要求,并选择合适的电路结构。

2.偏置电路:设计合适的偏置电路以提供所需的工作点稳定性。

3.放大电路:根据输入输出特性要求设计放大电路,确定电路的增益和带宽。

4.反馈电路:根据需要添加反馈电路以实现所需的增益、稳定性和线性度。

5.输出级:设计输出级以实现所需的输出电流和电压。

在电路拓扑设计过程中,可以使用各种常见的电路结构,如共射放大器、共基放大器、共集放大器等。

设计优化在完成电路拓扑设计后,需要对电路进行优化以满足设计规范的要求。

设计优化可以根据所需的电路性能采取以下措施:1.尺寸优化:通过调整电路中的晶体管尺寸来改变电路的增益和带宽。

新书推荐《CMOS集成电路EDA技术》(第2版)◆图书简介◆集成电路发展到今天,单芯片内能够集成高达百亿个晶体管,在集成电路的设计中需要依靠电子设计自动化(EDA)工具进行电路仿真、综合、版图设计、寄生参数提取和后仿真。

EDA工具的使用可以使设计者在虚拟的计算机环境中进行早期的设计验证,有效缩短了电路实体迭代验证的时间,提高了芯片设计的成功率。

一款成功的芯片源于无数工程师成功的设计,而成功的设计在很大程度上又取决于有效、成熟的集成电路EDA设计工具。

本书面向微电子学与固体电子学专业相关的课程教学要求和集成电路设计相关的工程应用需求,以提高实际工程设计能力为目的,采取循序渐进的方式,介绍了进行CMOS集成电路设计时所需的EDA工具。

主要分为EDA设计工具概述、模拟集成电路EDA技术、数字集成电路EDA技术与集成电路反向分析技术等部分。

在模拟集成电路方面,依次介绍了电路设计及仿真工具Cadence Spectre、版图设计工具Cadence Virtuoso、版图验证及参数提取工具Mentor Calibre在内的各种工具的基本知识和使用方法。

在数字集成电路方面,在简单介绍硬件描述语言Verilog HDL的基础上,介绍RTL仿真工具Modelsim、逻辑综合工具Design Compiler、数字后端版图工具IC Compiler和Encounter四大类设计工具。

*终对集成电路使用反向EDA技术进行全面的阐述。

书中配以电路设计实例,进一步分析各种EDA工具的设计输入方法和技巧,形成一套完整的CMOS集成电路设计流程。

本书使读者通过实例深刻了解使用CMOS集成电路EDA工具进行设计的基本流程和方法,可作为高等院校微电子学与固体电子学专业本科生与研究生集成电路EDA课程的实验教材和辅导书,或者相关专业技术人员的自学参考书。

点击上方二维码直接购买书籍◆ 目录◆第2版前言第1版前言第1章CMOS集成电路EDA技术 11.1CMOS集成电路EDA技术概述11.2CMOS模拟集成电路设计流程31.3CMOS模拟集成电路EDA工具分类51.4CMOS数字集成电路设计流程91.5CMOS数字集成电路EDA工具分类111.6小结13第2章模拟电路设计及仿真工具Cadence Spectre14 2.1Spectre的特点142.2Spectre的仿真设计方法162.3Spectre与其他EDA软件的连接172.4Spectre的基本操作182.4.1Cadence Spectre启动设置182.4.2Spectre主窗口和选项介绍192.4.3设计库管理器介绍222.4.4电路图编辑器介绍252.4.5模拟设计环境介绍292.4.6波形显示窗口介绍322.4.7波形计算器介绍372.5Spectre库中的基本器件422.5.1无源器件422.5.2有源器件422.5.3信号源432.6低压差线性稳压器的设计与仿真452.7高阶仿真功能与实例532.7.1FFT仿真532.7.2Monte Carlo仿真592.8小结65第3章版图设计工具Cadence Virtuoso663.1Virtuoso界面介绍663.1.1窗口标题栏683.1.2状态栏693.1.3菜单栏693.1.4图标菜单773.1.5设计区域793.1.6光标和指针793.1.7鼠标状态803.1.8提示栏813.1.9层选择窗口813.2Virtuoso基本操作833.2.1创建矩形833.2.2创建多边形843.2.3创建路径853.2.4创建标识名863.2.5创建器件和阵列863.2.6创建接触孔883.2.7创建圆形图形883.2.8移动命令903.2.9复制命令913.2.10拉伸命令913.2.11删除命令923.2.12合并命令923.2.13选择和放弃选择命令93 3.2.14改变层次关系命令94 3.2.15切割命令963.2.16旋转命令973.2.17属性命令983.2.18分离命令993.3运算放大器版图设计实例100 3.3.1NMOS晶体管版图设计1003.3.2运算放大器版图设计1063.4小结114第4章模拟版图验证及参数提取工具Mentor Calibre115 4.1Mentor Calibre版图验证工具调用1154.1.1Virtuoso Layout Editor工具启动1154.1.2采用Calibre图形界面启动1184.1.3采用Calibre View查看器启动1184.2Mentor Calibre DRC验证1204.2.1Calibre DRC验证简介1204.2.2Calibre DRC界面介绍1224.2.3Calibre DRC验证流程举例1284.3Mentor Calibre LVS验证1374.3.1Calibre LVS验证简介1374.3.2Calibre LVS界面介绍1384.3.3Calibre LVS验证流程举例1494.4Mentor Calibre寄生参数提取1584.4.1Calibre PEX验证简介1584.4.2Calibre PEX界面介绍1594.4.3Calibre PEX流程举例1694.5小结175第5章硬件描述语言及仿真工具Modelsim1765.1硬件描述语言及仿真概述1765.2硬件描述语言与应用实例1775.2.1硬件描述语言基础1775.2.2硬件描述语言应用实例1855.2.3硬件描述语言的可综合设计1905.2.4硬件描述语言设计实例1915.3数字电路仿真工具Modelsim1955.3.1Modelsim的特点与应用1965.3.2Modelsim的基本使用1995.3.3Modelsim的进阶使用2085.4小结223第6章数字逻辑综合及Design Compiler224 6.1逻辑综合概述2246.1.1逻辑综合的定义及发展历程2246.1.2逻辑综合的流程2256.2DesignCompiler简介2266.2.1DesignCompiler的功能2266.2.2DesignCompiler的使用模式2276.2.3DC-T cl简介2286.3DesignCompiler综合设计2326.3.1启动工具及初始环境配置2326.3.2综合库2346.3.3DesignCompiler综合流程2356.4静态时序分析与设计约束2436.4.1静态时序分析2436.4.2亚稳态2456.4.3时钟的约束2456.4.4输入输出路径的约束2476.4.5组合逻辑路径的约束2486.4.6时间预算2496.4.7设计环境约束2506.4.8多时钟同步设计约束2536.4.9异步设计约束2556.4.10多时钟的时序约束2566.5基于状态机的交通灯综合2586.6小结262第7章数字电路物理层设计工具IC Compiler263 7.1IC Compiler简介2637.2IC Compiler物理层设计的数据准备2657.2.1逻辑层数据2657.2.2物理层数据2667.2.3设计数据2667.3创建设计数据库与后端数据的设置267 7.3.1逻辑库设置2677.3.2物理库设置2677.3.3其他文件设置2687.3.4创建设计数据库2687.3.5库文件检查2687.3.6网表导入2687.3.7Tlu+文件设置与检查2697.3.8电源网络设置2697.3.9TIE单元设置2707.3.10导入SDC文件并进行时序约束检查270 7.3.11定时序优化参数2717.4不同PVT角下综合优化的设置方法273 7.4.1scenario的建立2747.4.2PVT角设定2747.5宏单元与IO布局2767.5.1IO布局与芯片布局空间创建2767.5.2宏单元的摆放2777.6电源网络的设计与分析2787.6.1设计电源和地环2787.6.2设计电源和地条2787.6.3连接宏单元和标准单元2797.7标准单元的布局与优化2807.7.1检查是否需要添加tap cell2817.7.2spare cell的标识2817.7.3检查设计输入文件与约束2817.7.4确认所有路径已经被正确地设置2817.8时钟树综合与优化2837.8.1综合前的检查2837.8.2时钟树综合设置2837.8.3执行时钟树综合核心命令2867.9芯片布线与优化2877.9.1布线前的检查2877.9.2ICC布线相关设置2877.9.3天线效应简介与设置2897.9.4执行布线命令2907.10芯片ECO与设计文件导出2917.10.1Freeze silicon ECO2917.10.2unconstrained ECO2917.10.3设计结果导出2927.11小结292第8章数字电路物理层设计工具Encounter293 8.1Encounter工具发展历史2938.2Encounter设计流程介绍2948.3数据准备2958.3.1设计数据2958.3.2逻辑库数据2968.3.3物理库数据2978.3.4数据准备常用的指令与流程2978.4布图规划与布局3018.4.1布图与IO排布3018.4.2电源网络设计3038.4.3标准单元的布局与优化 3038.4.4布图规划与布局常用指令与流程3048.5时钟树综合3118.5.1时钟树综合简介3118.5.2时钟树流程与优化3138.6芯片布线3158.6.1芯片布线工具简介3158.6.2特殊布线3158.6.3一般布线3168.6.4芯片布线流程与优化3168.7芯片ECO与DFM3188.7.1ECO流程与优化3188.7.2DFM流程与优化3218.8小结321第9章集成电路反向分析EDA技术322 9.1集成电路反向分析概述3229.1.1反向分析技术的主要应用323 9.1.2反向分析技术的主要流程325 9.1.3反向分析EDA技术3269.2电路网表提取3289.2.1网表提取概述3289.2.2网表提取流程3319.2.3模拟单元提取3369.2.4数字单元提取3449.2.5线网绘制与检查3469.2.6数据的导入和导出3489.3电路层次化分析整理3519.3.1电路分析整理概述3519.3.2层次化整理流程3529.3.3模拟电路的层次化整理3549.3.4数字电路的层次化整理3579.3.5整理数据的导出3609.4小结361参考文献362点击上方二维码直接购买书籍第2版前言集成电路自从产生以来,集成度一直按照“摩尔定律”不断提高。